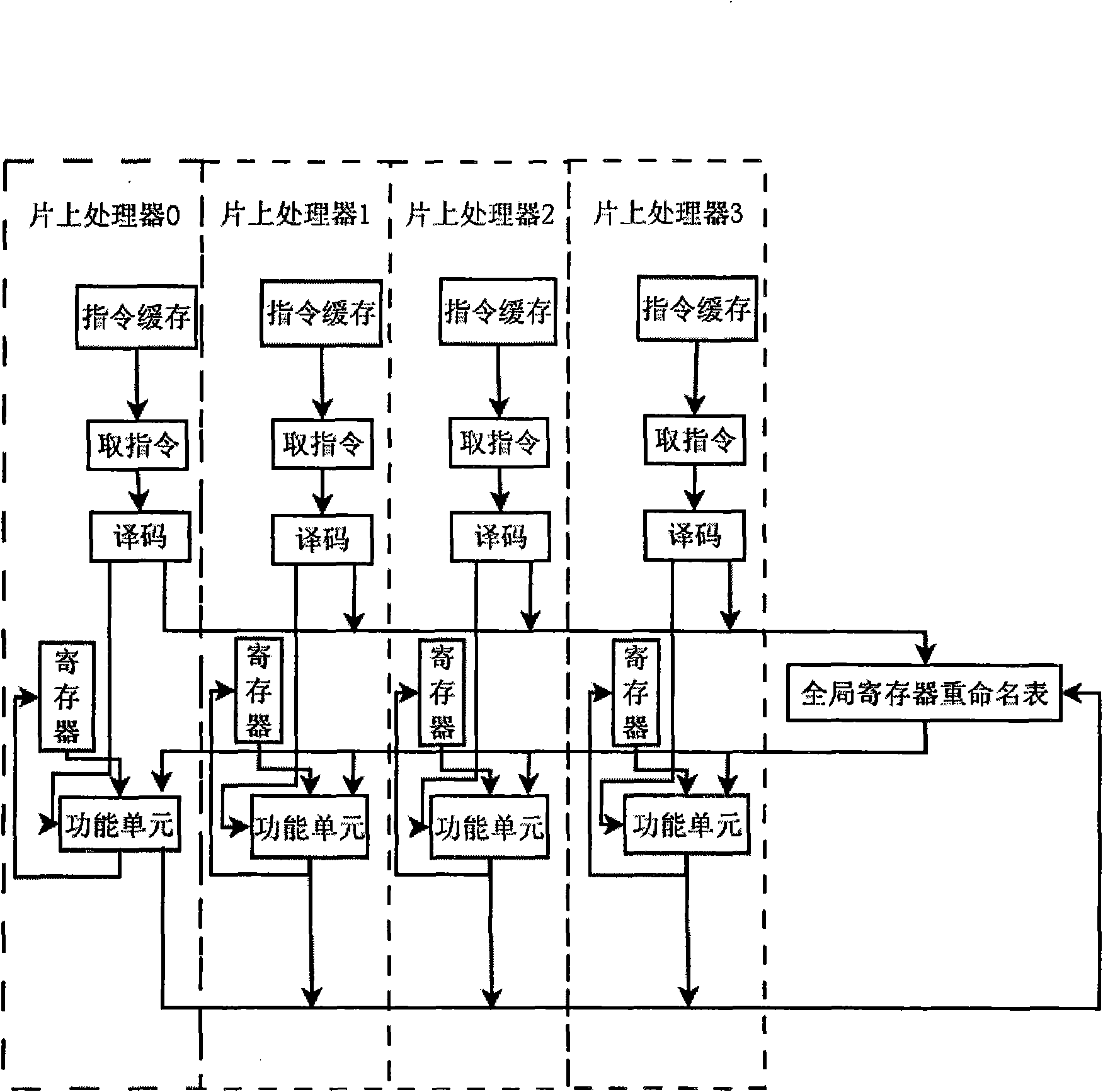

Implementation method of rename table of global register under on-chip multi-processor system framework

A register renaming, on-chip multiprocessor technology, applied in machine execution devices, concurrent instruction execution, etc., can solve the problem of operand transfer, achieve the effect of small area cost, reduce inter-core communication volume, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] When implementing the implementation method of the global register renaming table under the multi-core system architecture, the dependency between instructions is considered.

[0031] Table 1 is an application example of the global register renaming table proposed by this method.

[0032] logic register

physical register

processor number

Busy

ready

data

R0

P3

3

1

1

0x321f6a46

R1

-

-

0

-

-

R2

P13

3

1

0

-

R3

P5

2

1

1

0x2684742a

R4

-

-

0

-

-

R5

P21

0

1

1

0x73128c4e

...

...

...

...

...

...

[0033] 1) Design of register renaming table

[0034] Each of the four on-chip processors has its own list of available physical registers, and jointly has a register renaming table, call...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More