Register renaming system and method for managing and renaming registers

A register renaming and physical register technology, applied in instruments, machine execution devices, electrical digital data processing, etc., can solve the problem of increasing the frequency of microprocessors, increasing the workload of the renaming engine, and affecting the increase of the working frequency of microprocessors. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

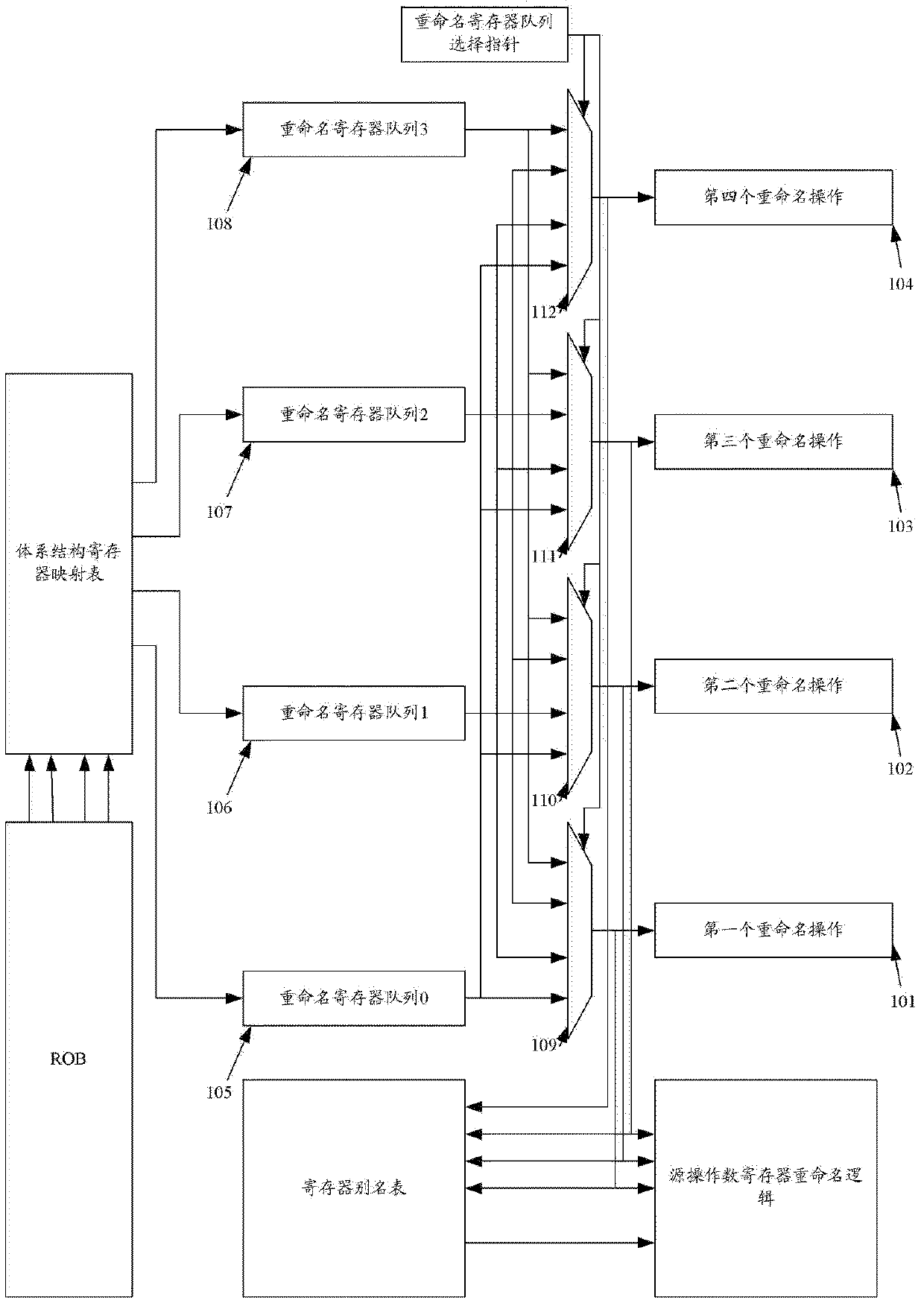

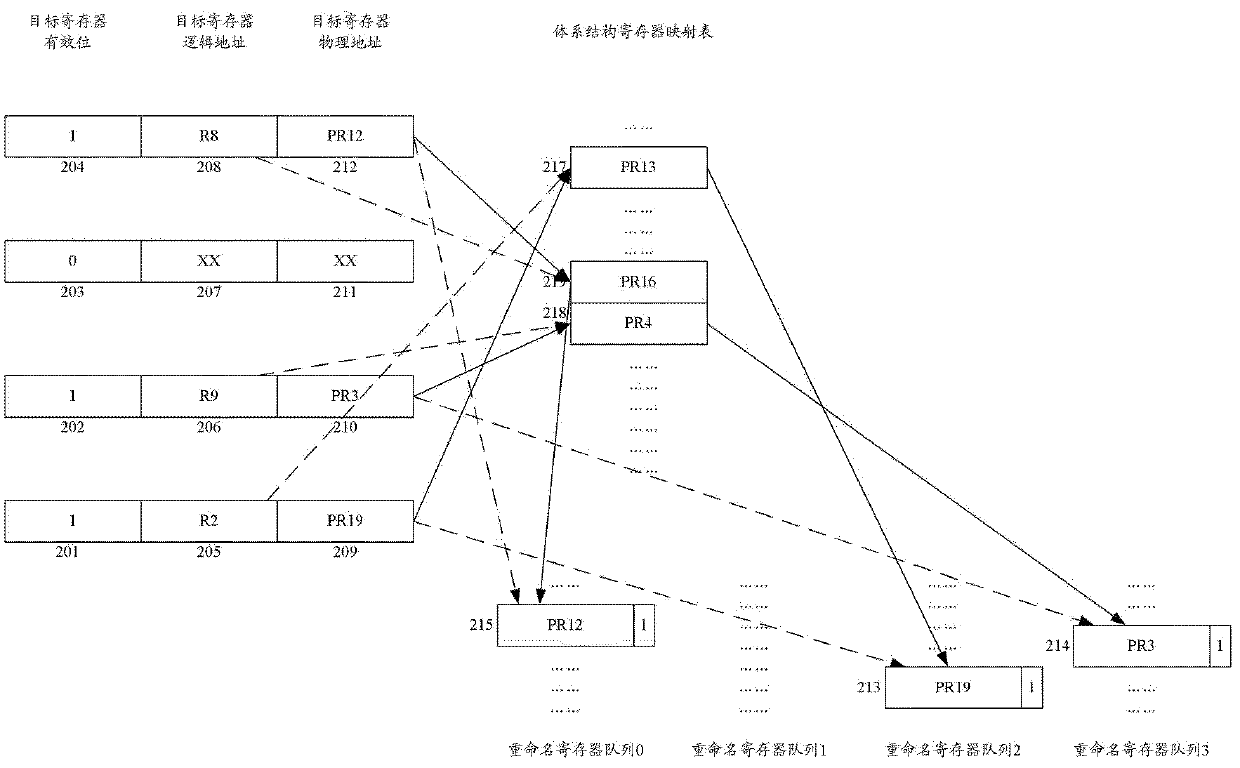

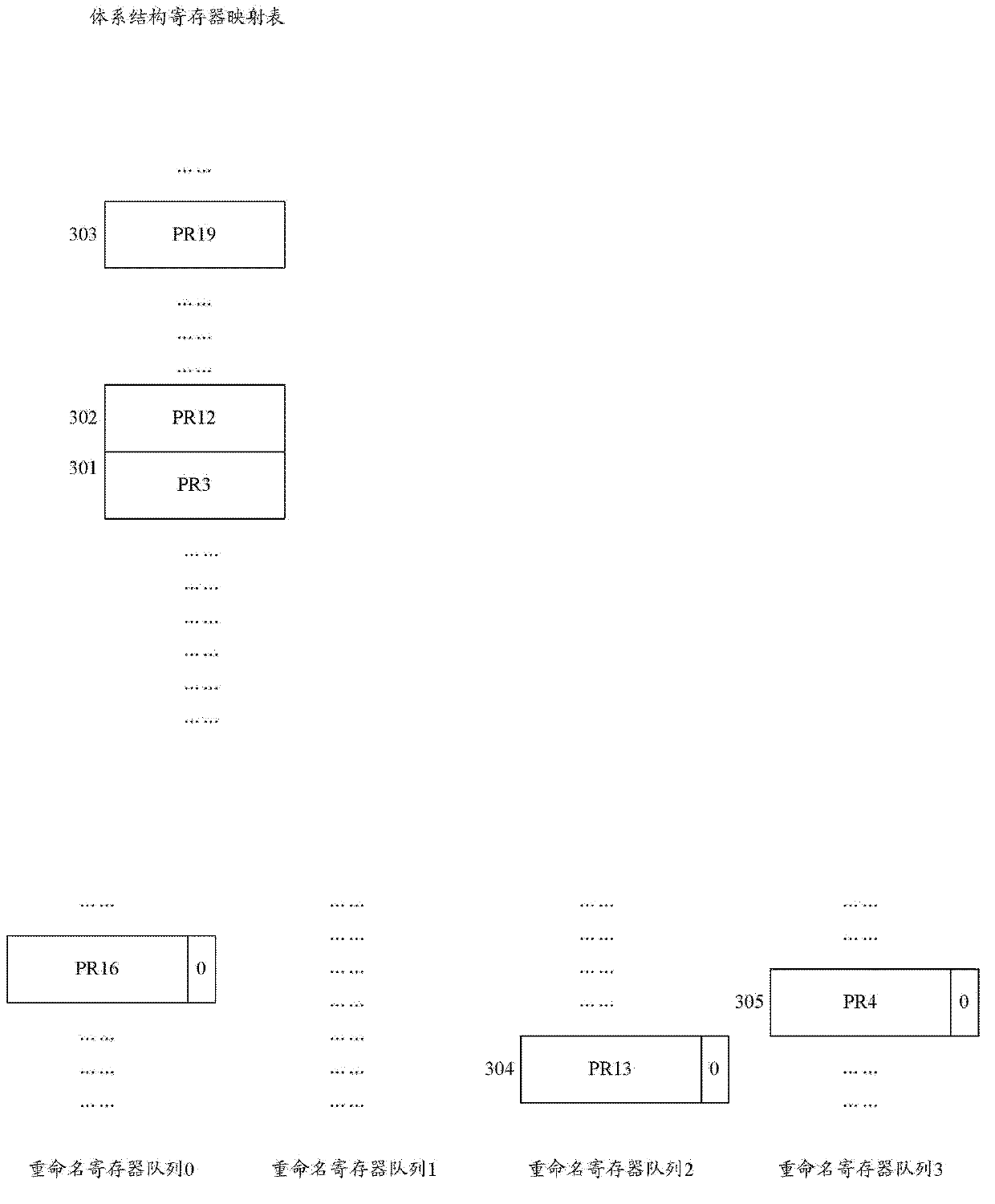

[0089] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments:

[0090] In this embodiment, the physical register group includes 64 physical registers, of which 32 physical registers are mapped as architectural registers. The architectural registers are physical registers that save the contents of the confirmed logical registers, and are one-to-one with the logical registers. Correspondingly, the other 32 physical registers are renaming registers, and the renaming registers are physical registers that temporarily store instruction execution results in order to eliminate data correlation between instructions when the microprocessor is running. In particular, the number of physical registers in the present invention is not limited to 64. Generally speaking, the physical register group may include M+N physical registers, where M is the number of physical registers that are dynamically mapped as archite...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More