Address generator for Turbo code and LDPC (Low Density Parity Check) code decoder

An address generator, LDPC code technology, applied in the direction of error correction/detection using block codes, error detection coding using multi-bit parity bits, machine execution devices, etc., which can solve the problem of limited flexibility and inability to decode Process control and other issues to achieve the effect of high flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The technical scheme of the present invention will be described in detail below in conjunction with the accompanying drawings.

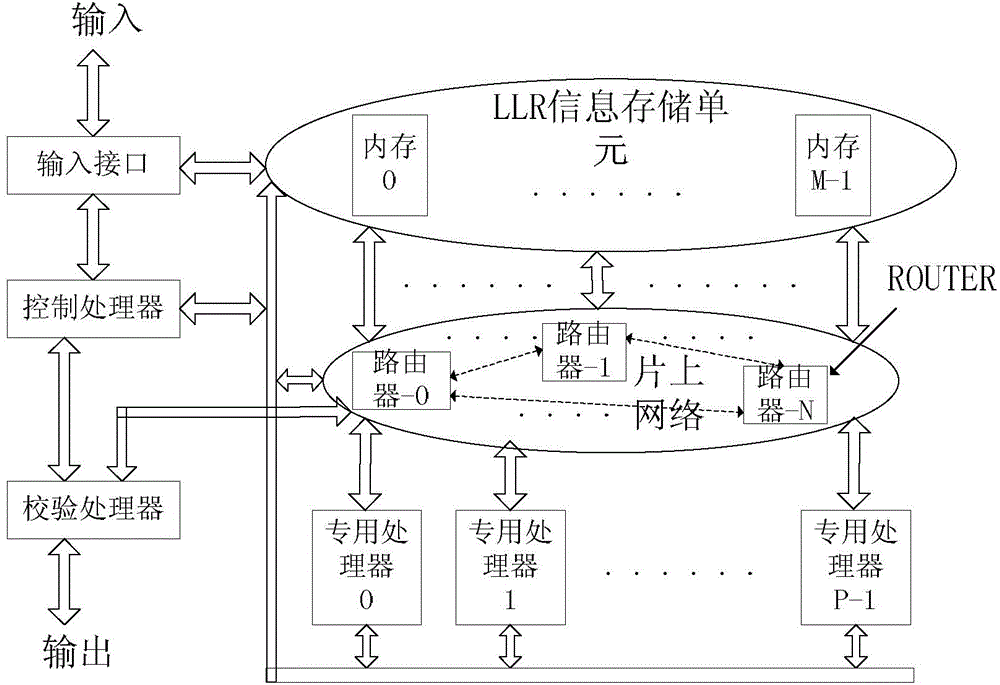

[0022] The address generator proposed by the present invention is used in multi-mode Turbo codes and LDPC code decoders, figure 1 It is the overall architecture diagram of multi-mode Turbo code and LDPC code decoder. The decoder is capable of error correction decoding of Turbo codes and LDPC codes. The input interface is responsible for various data inputs, including the initialization of the instruction / data memory of the control processor and the dedicated processor, the input of the channel LLR in the channel information storage unit, and the input of various error correction code information. The control processor is a RISC processor with a custom instruction set, responsible for monitoring the entire decoding process, calculating configuration information, configuring special processors, etc. The channel information storage unit is used...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More