Patents

Literature

84 results about "Custom instruction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

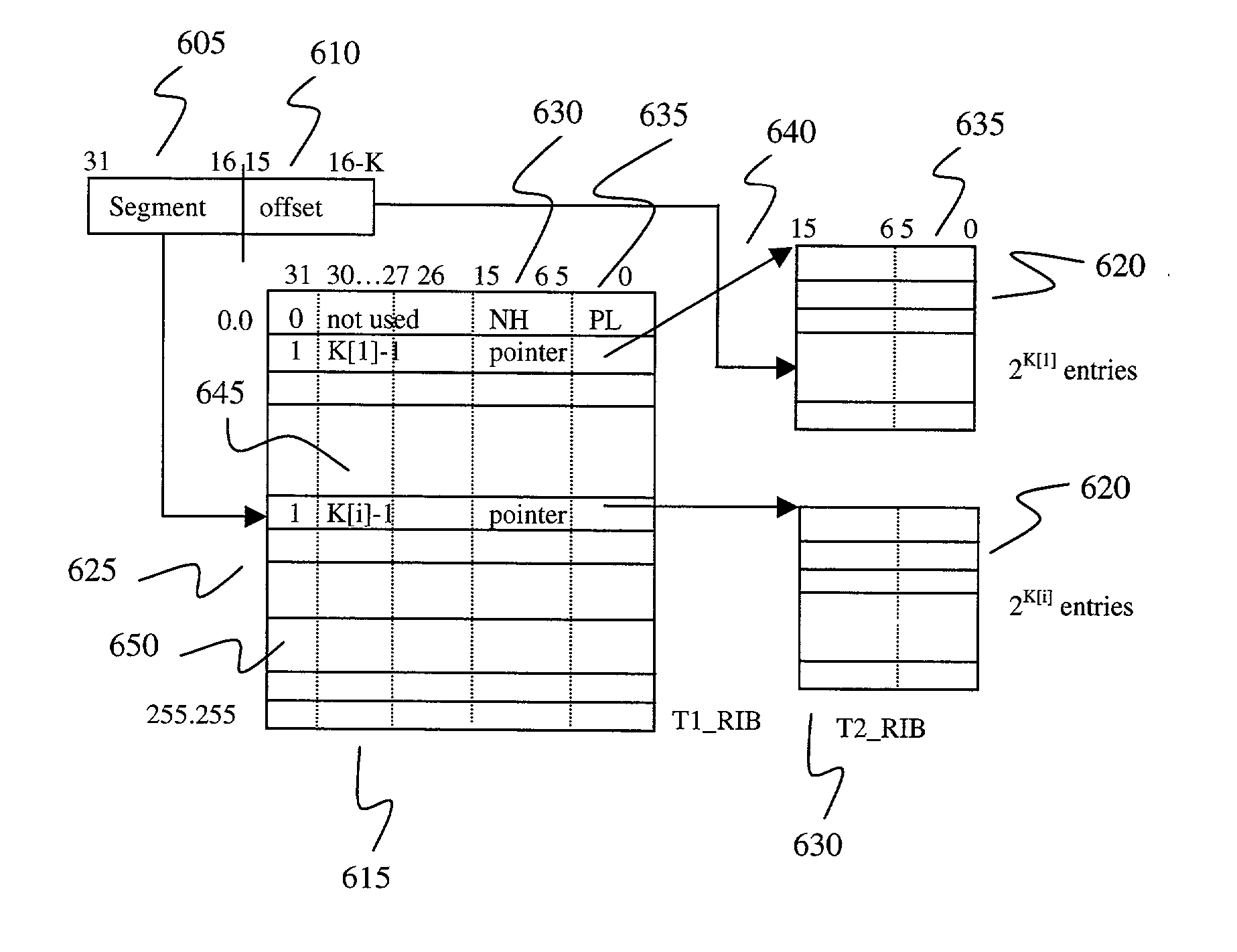

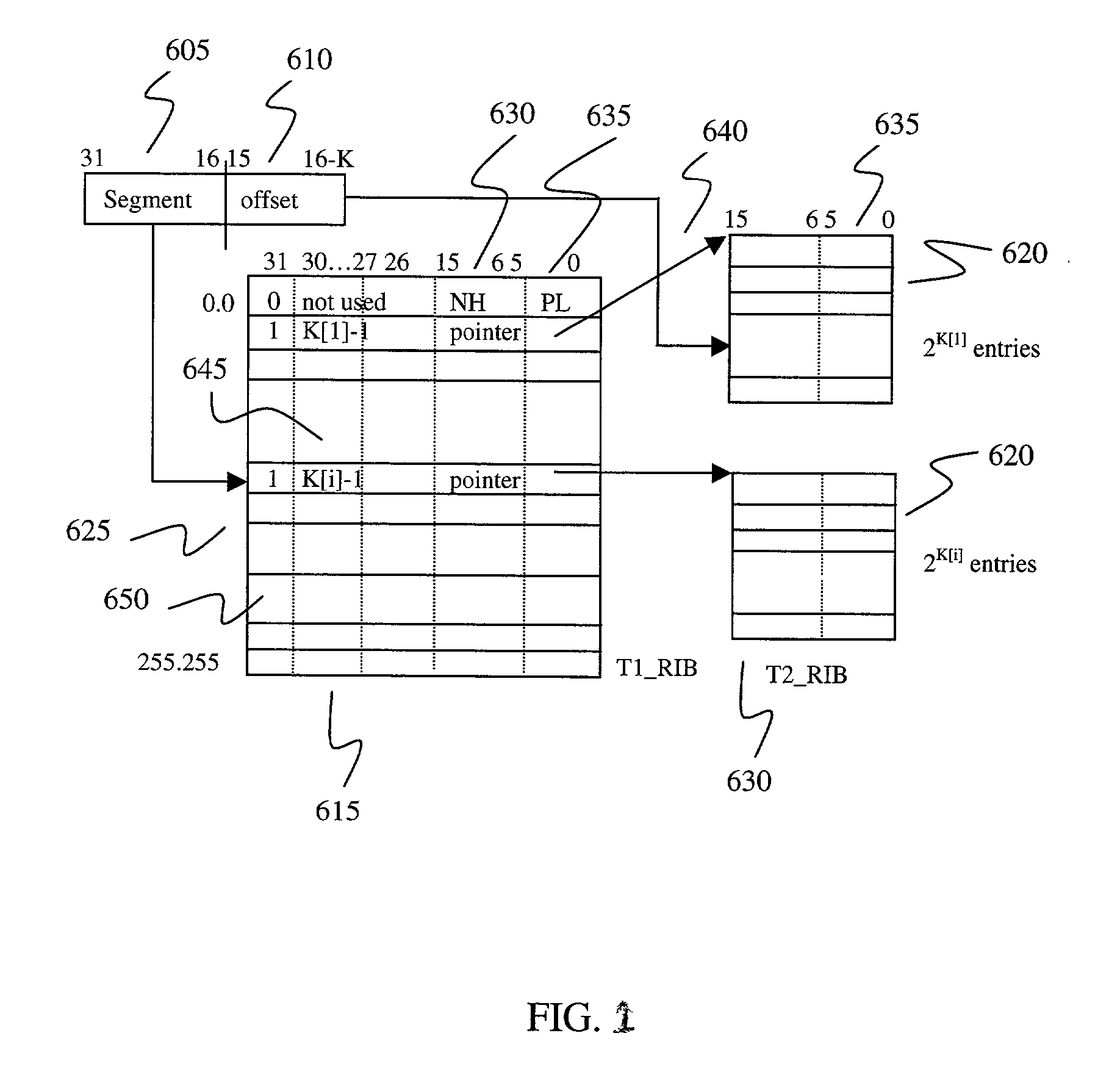

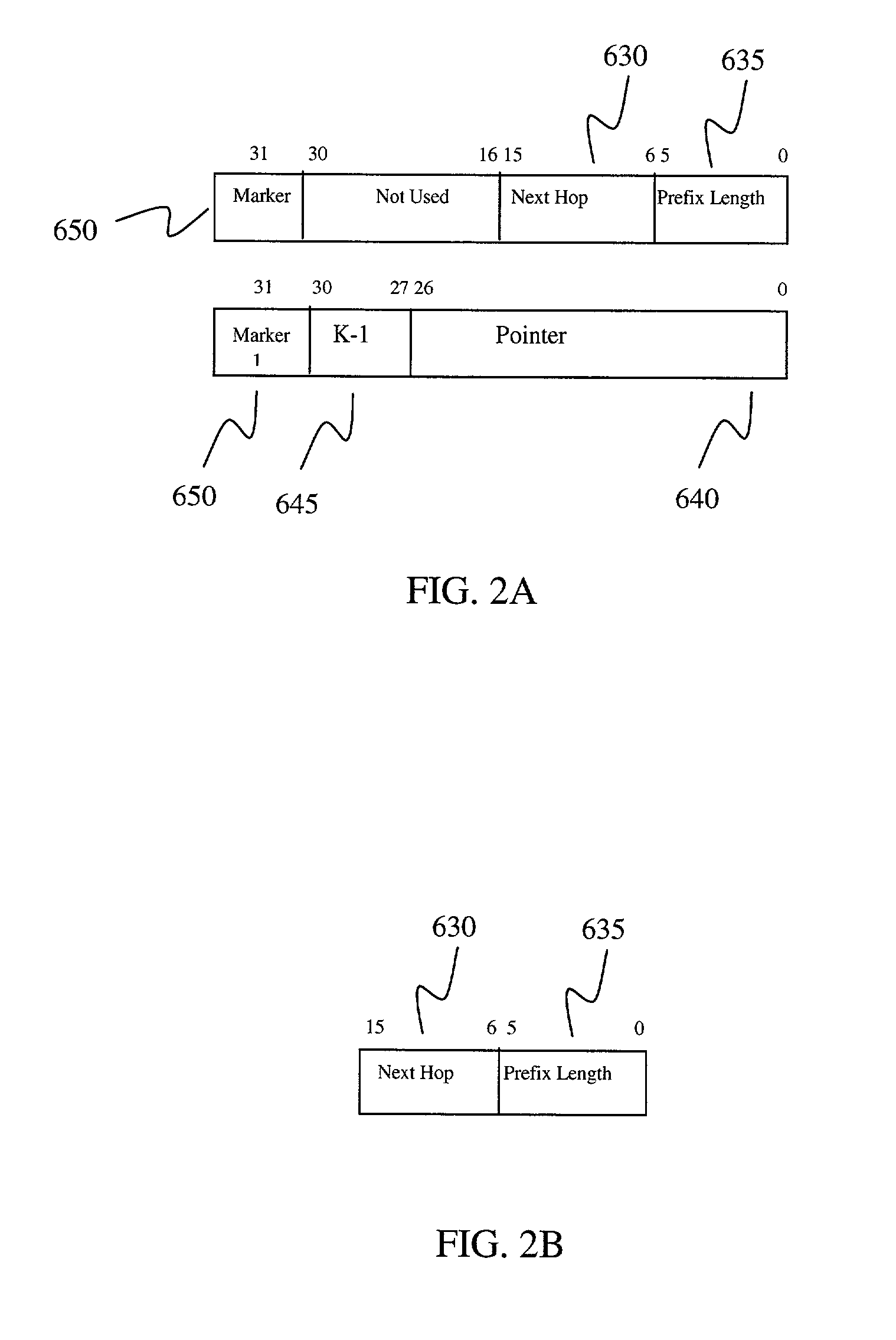

Fast IP route lookup with 16/K and 16/Kc compressed data structures

InactiveUS20020172203A1Data switching by path configurationOther databases indexingPresent dayArray data structure

An advanced data structure allows lookup based upon the most significant 16 bits and the following variable number of K bits of the IP destination address. This 16 / K scheme requires less than 2 MB memory to store the whole routing tables of present day backbone routers. A 16 / Kc version utilizes bitmaps to compress the table to less than 0.5 MB. For the 16 / K data structure each route lookup requires at most 2 memory accesses while the 16 / Kc requires at most 3 memory accesses. By configuring the processor properly and developing a few customized instructions to accelerate route lookup, one can achieve 85 million lookups per second (MLPS) in the typical case with the processor running at 200 MHz. Further, the lookup method can be implemented using pipelining techniques to perform three lookups for three incoming packets simultaneously. Using such techniques, 100 MLPS performance can be achieved.

Owner:TESILICA

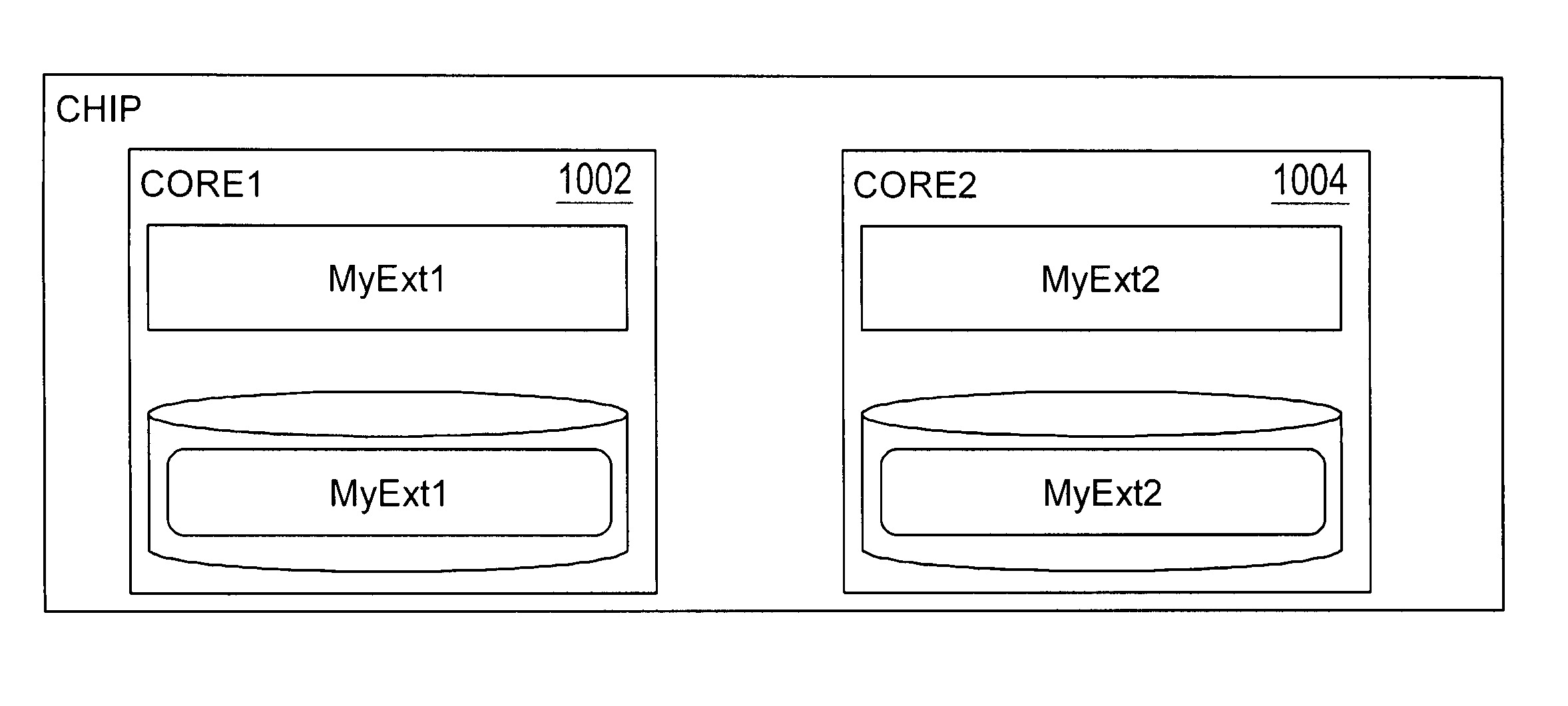

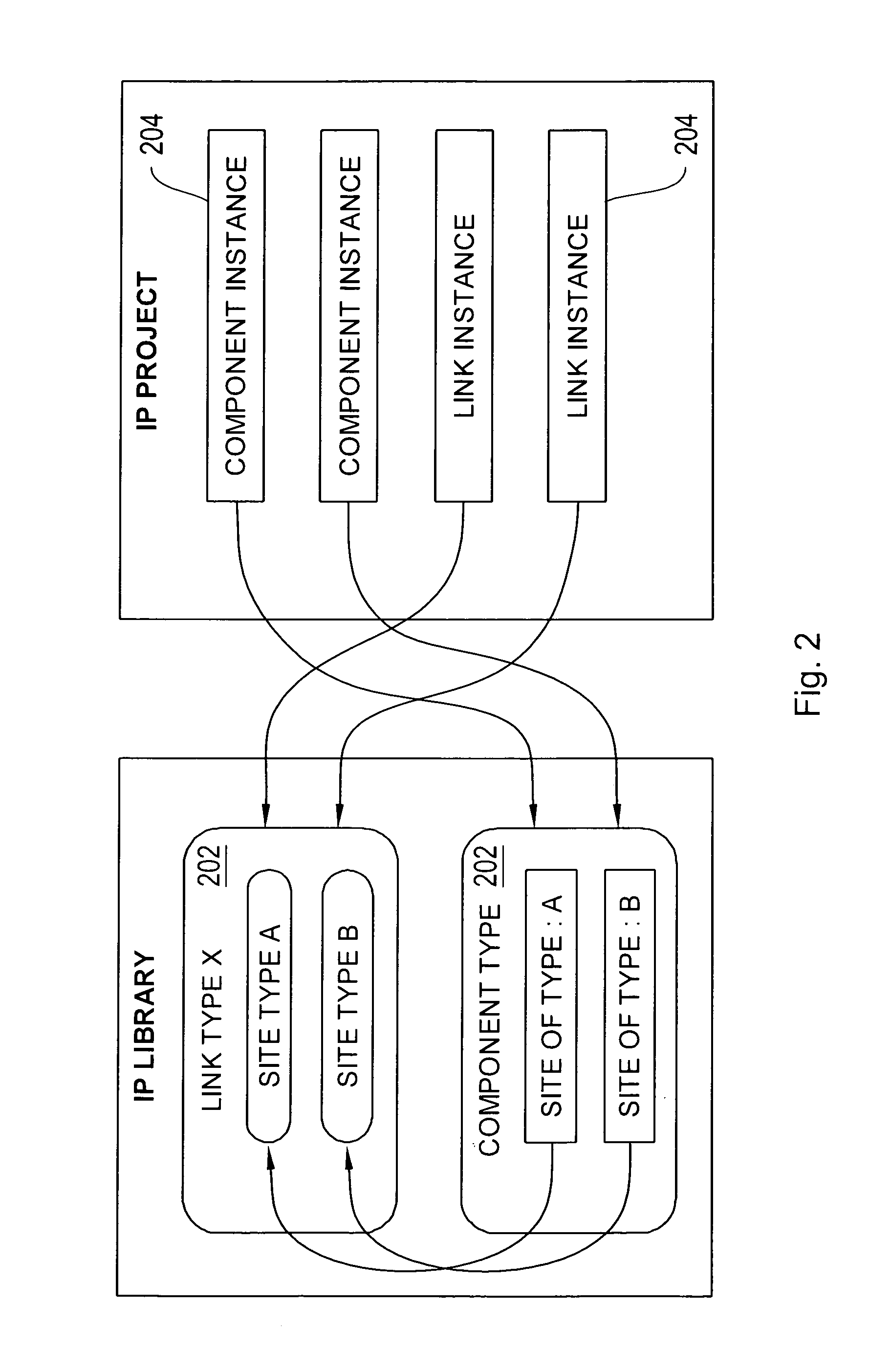

Apparatus and method for managing integrated circuit designs

ActiveUS7475000B2Easy to manageFree of nomenclatureAnalogue computers for electric apparatusCAD circuit designComputer architectureAccessibility

Apparatus and methods for integrated circuit (IC) design, including management of the configuration, design parameters, and functionality of a design in which custom instructions or other design elements may be controlled by the designer. In one exemplary embodiment, a computer program rendered in an object-oriented language implementing the aforementioned methods for designing user-customized digital processors is disclosed. Design iteration, component encapsulation, use of human-readable file formats, extensible dynamic GUIs and tool sets, and other features are employed to enhance the functionality and accessibility of the program. Components within the design environment comprise encapsulated objects which contain information relating to interfaces with other components in the design, hierarchy, and other facets of the design process.

Owner:SYNOPSYS INC

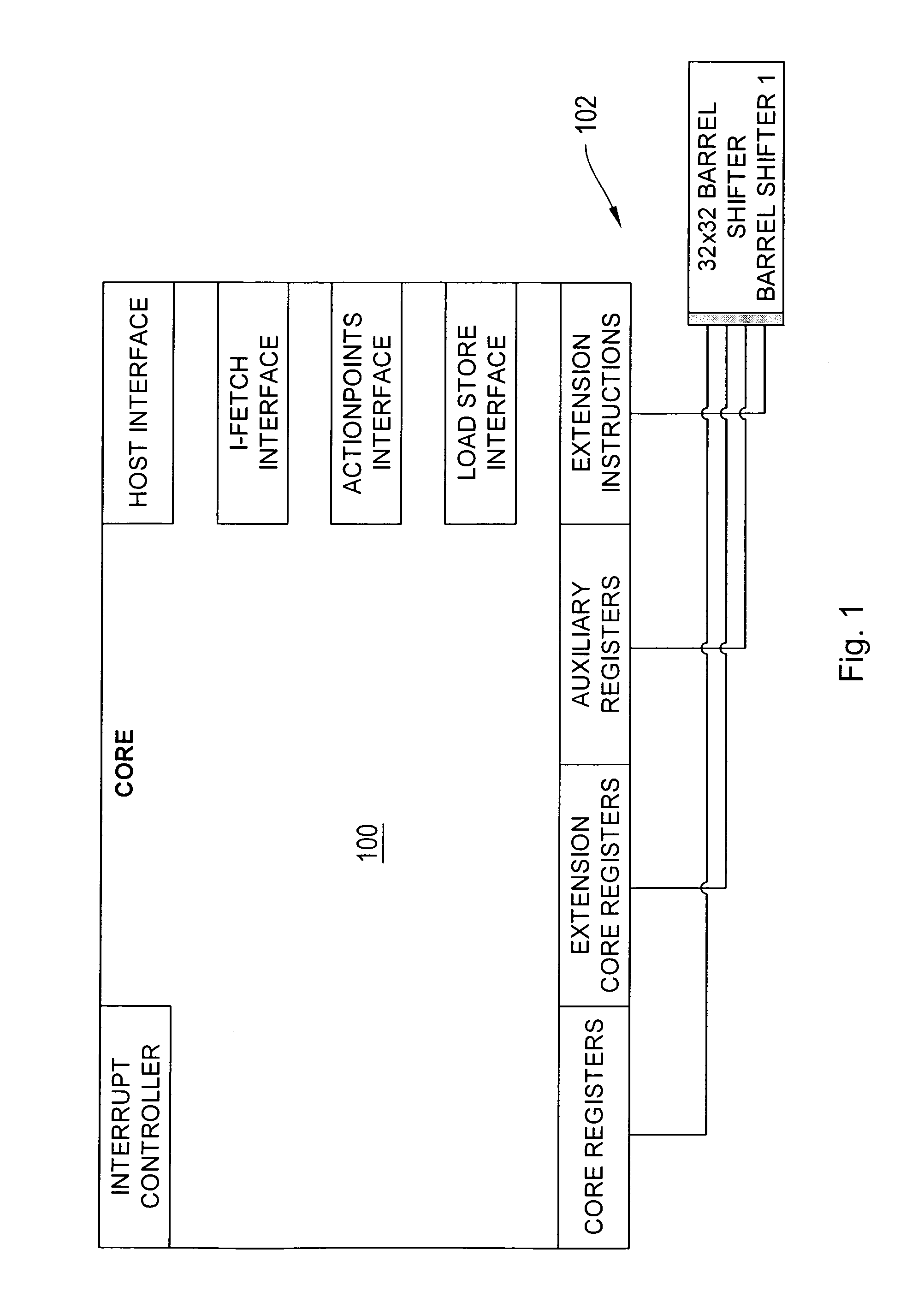

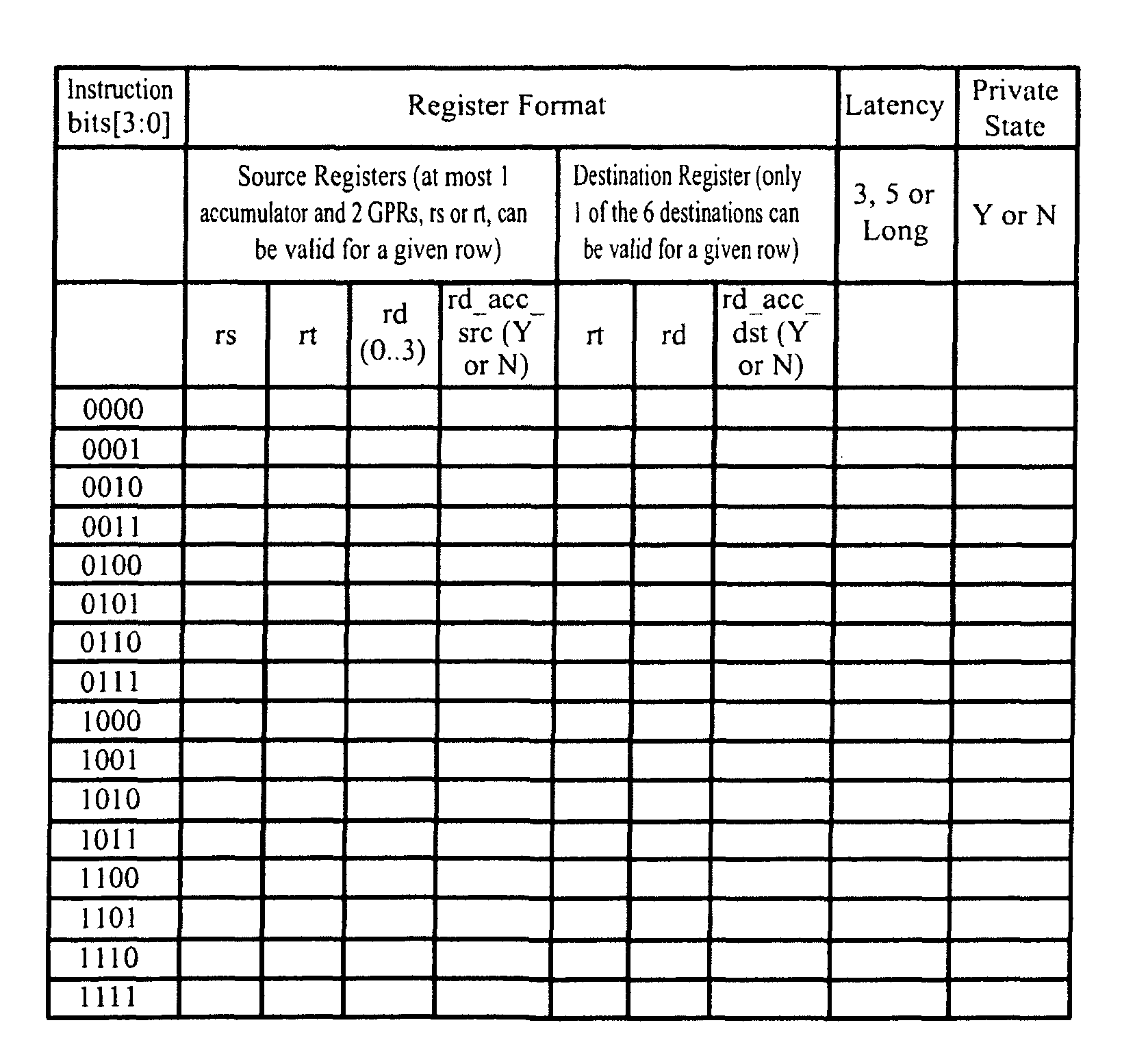

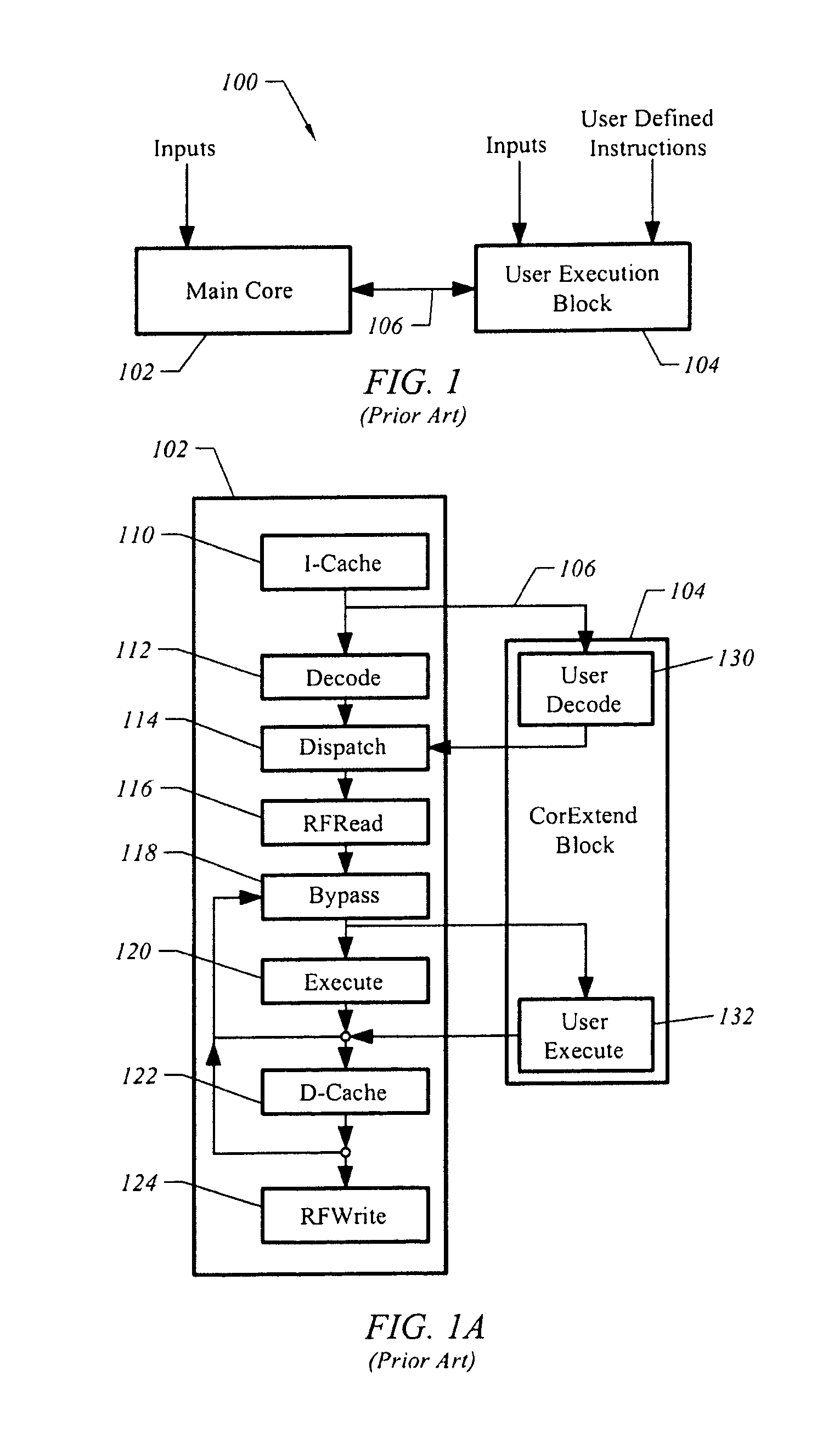

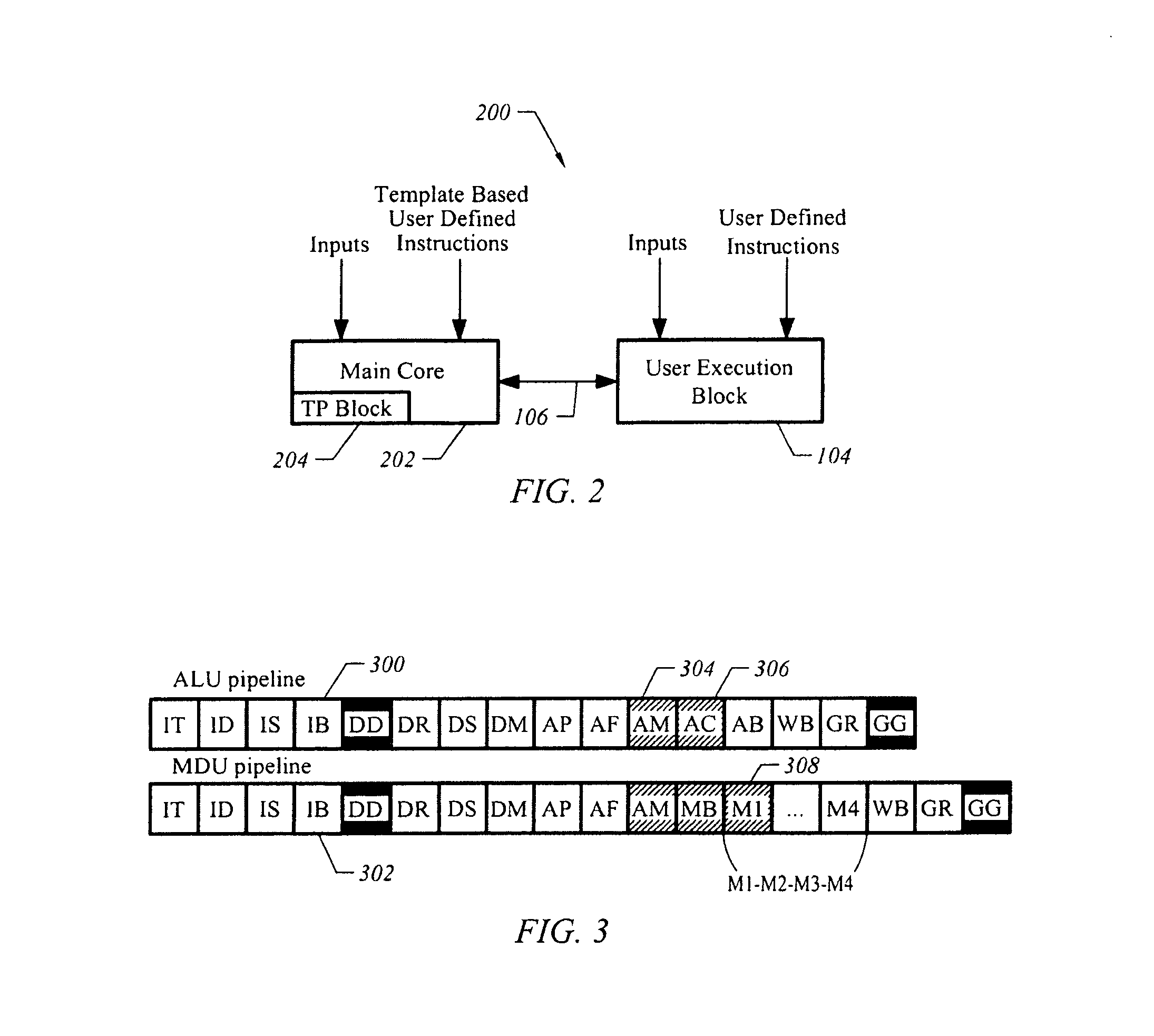

Apparatus and method for processing template based user defined instructions

A system implemented in hardware includes a main processing core decoding instructions for out of order execution. The instructions include template based user defined instructions. A user execution block executes the template based user defined instructions. An interface is positioned between the main processing core and the user execution block. A computer readable medium includes executable instructions to describe a processing core supporting execution of a proprietary instruction set and decoding of customized instructions that adhere to a specified pattern. The specified pattern includes a source, a destination and a latency period. A user execution block is connected to the processing core to execute the customized instructions.

Owner:ARM FINANCE OVERSEAS LTD

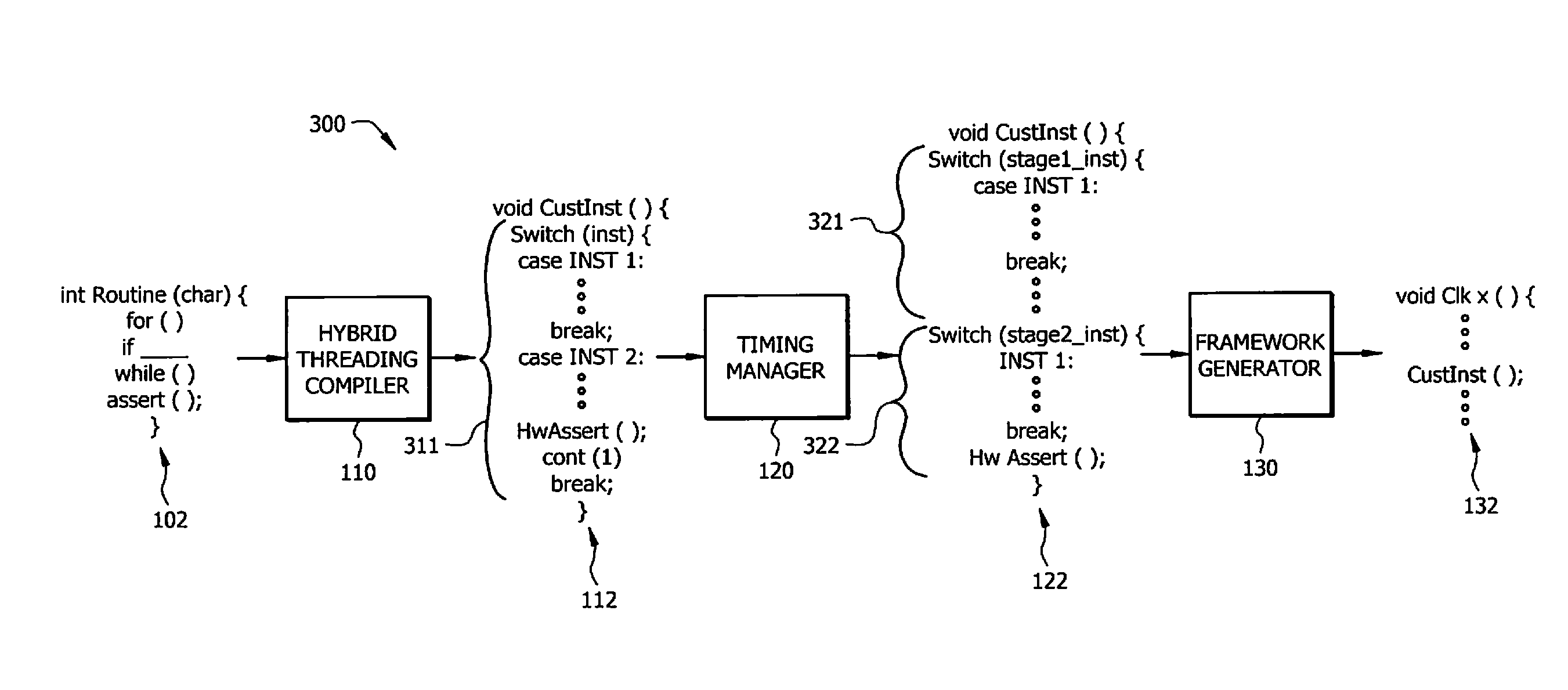

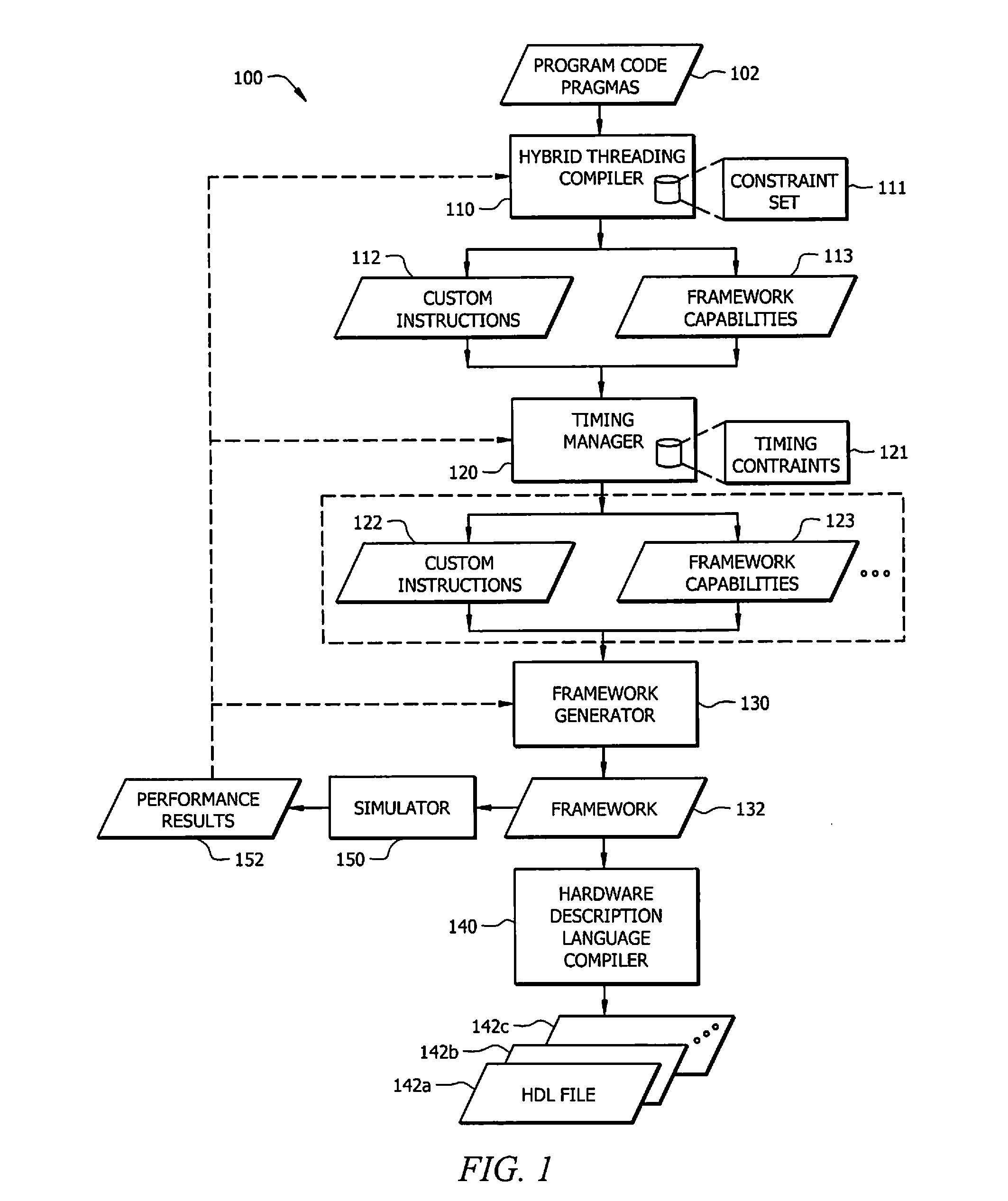

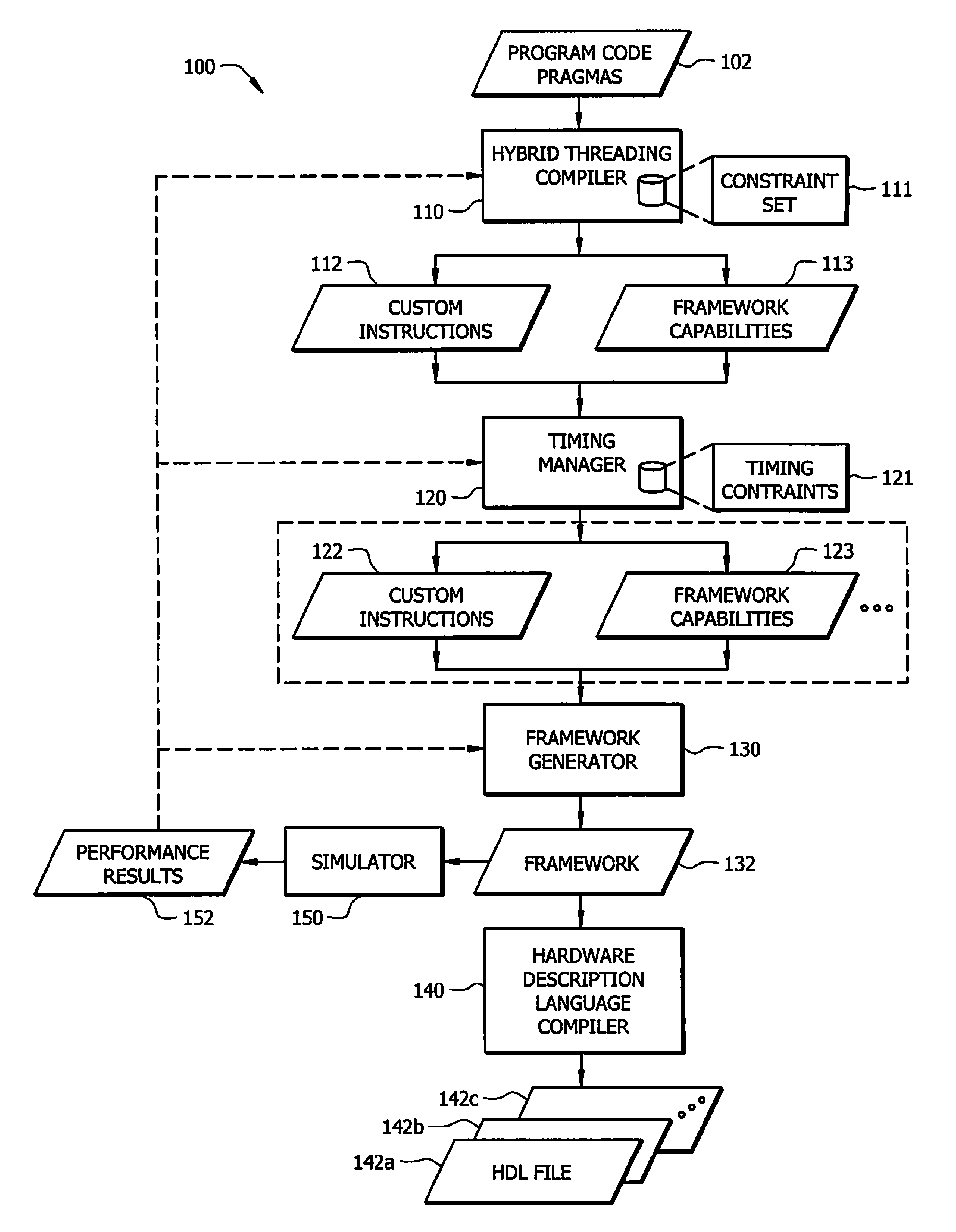

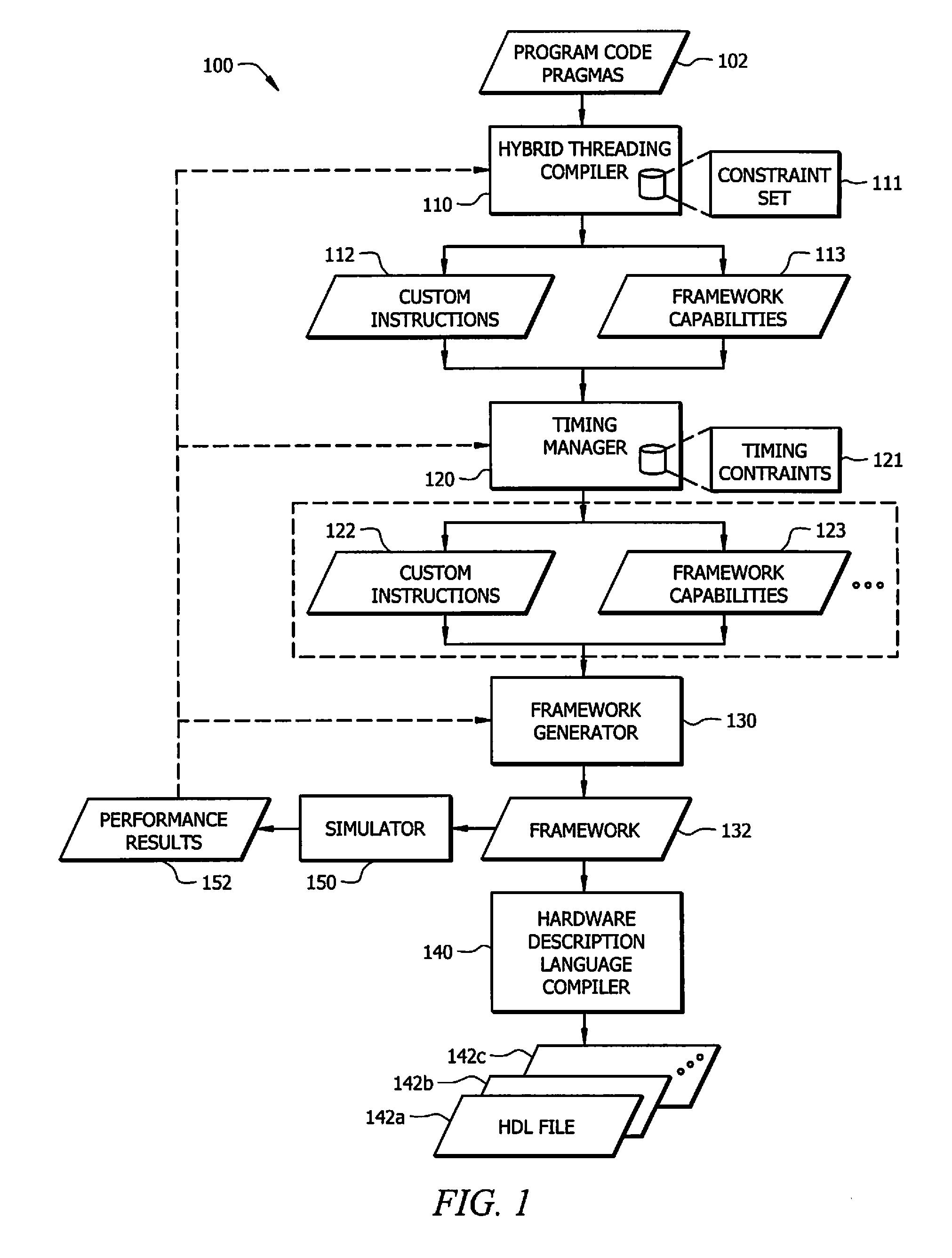

Multistate development workflow for generating a custom instruction set reconfigurable processor

ActiveUS20150143350A1Facilitating development and generationEasy to useMemory systemsCode compilationLoad instructionProgram code

Systems and methods which implement workflows for providing reconfigurable processor core algorithms operable with associated capabilities using description files, thereby facilitating the development and generation of instruction sets for use with reconfigurable processors, are shown. Embodiments implement a multistage workflow in which program code is parsed into custom instructions and corresponding capability descriptions for generating reconfigurable processor loadable instruction sets. The multistage workflow of embodiments includes a hybrid threading complier operable to compile input program code into custom instructions using a hardware timing agnostic approach. A timing manager of the multistage workflow of embodiments utilizes capabilities information provided in association with the custom instructions generated by the hybrid threading complier to impose hardware timing on the custom instructions. A framework generator and hardware description language complier are also included in the multistage workflow of embodiments.

Owner:CONVEY COMP +1

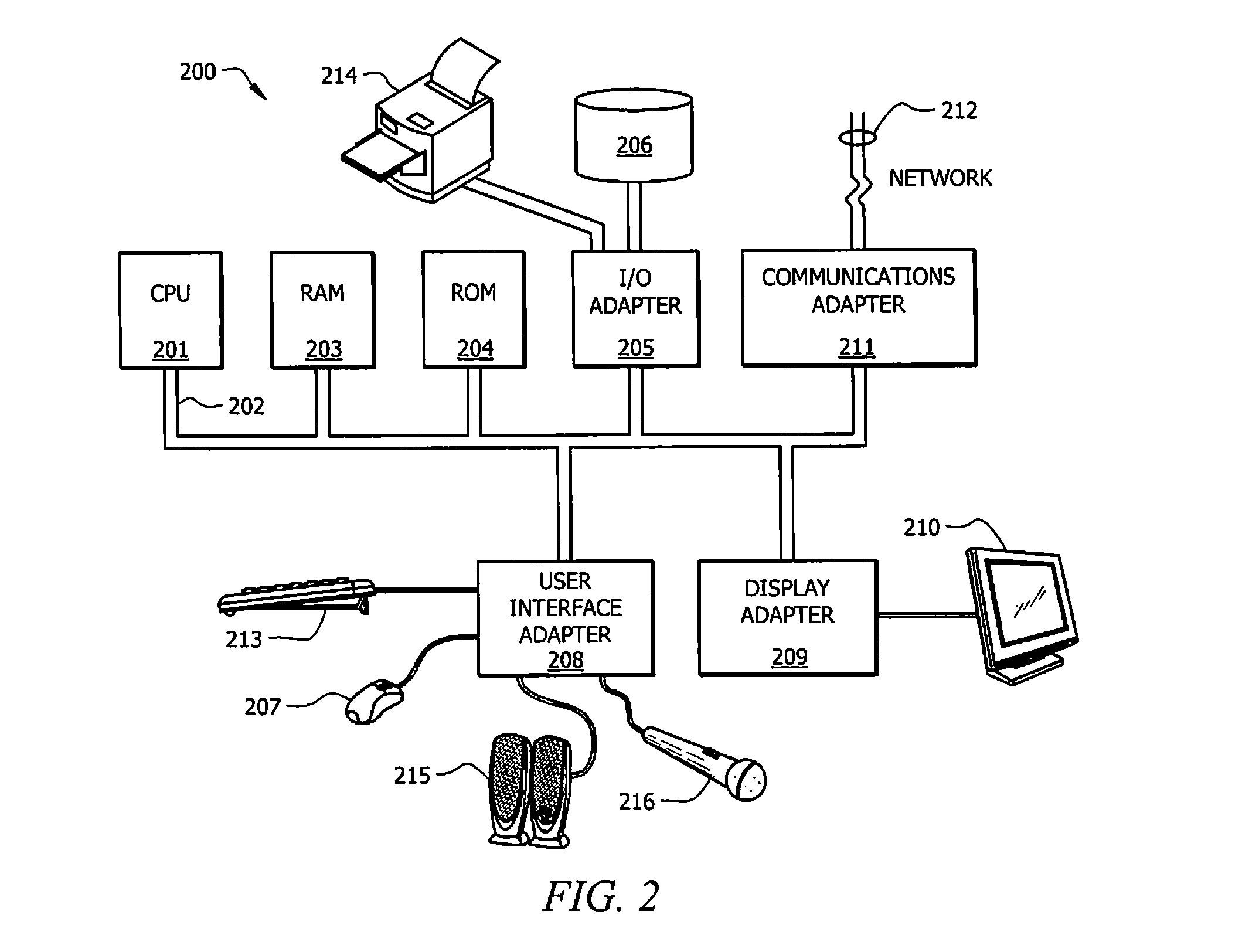

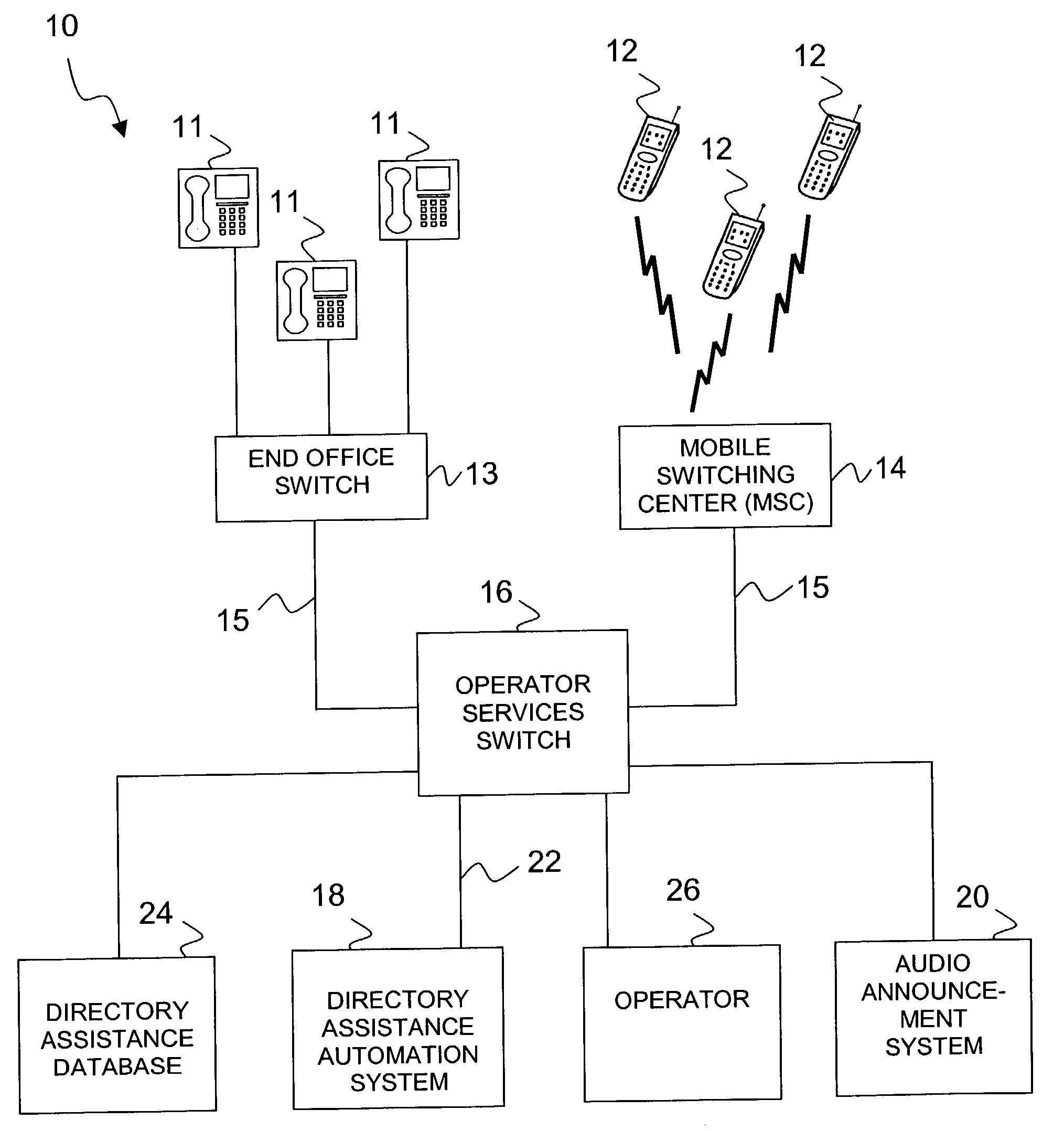

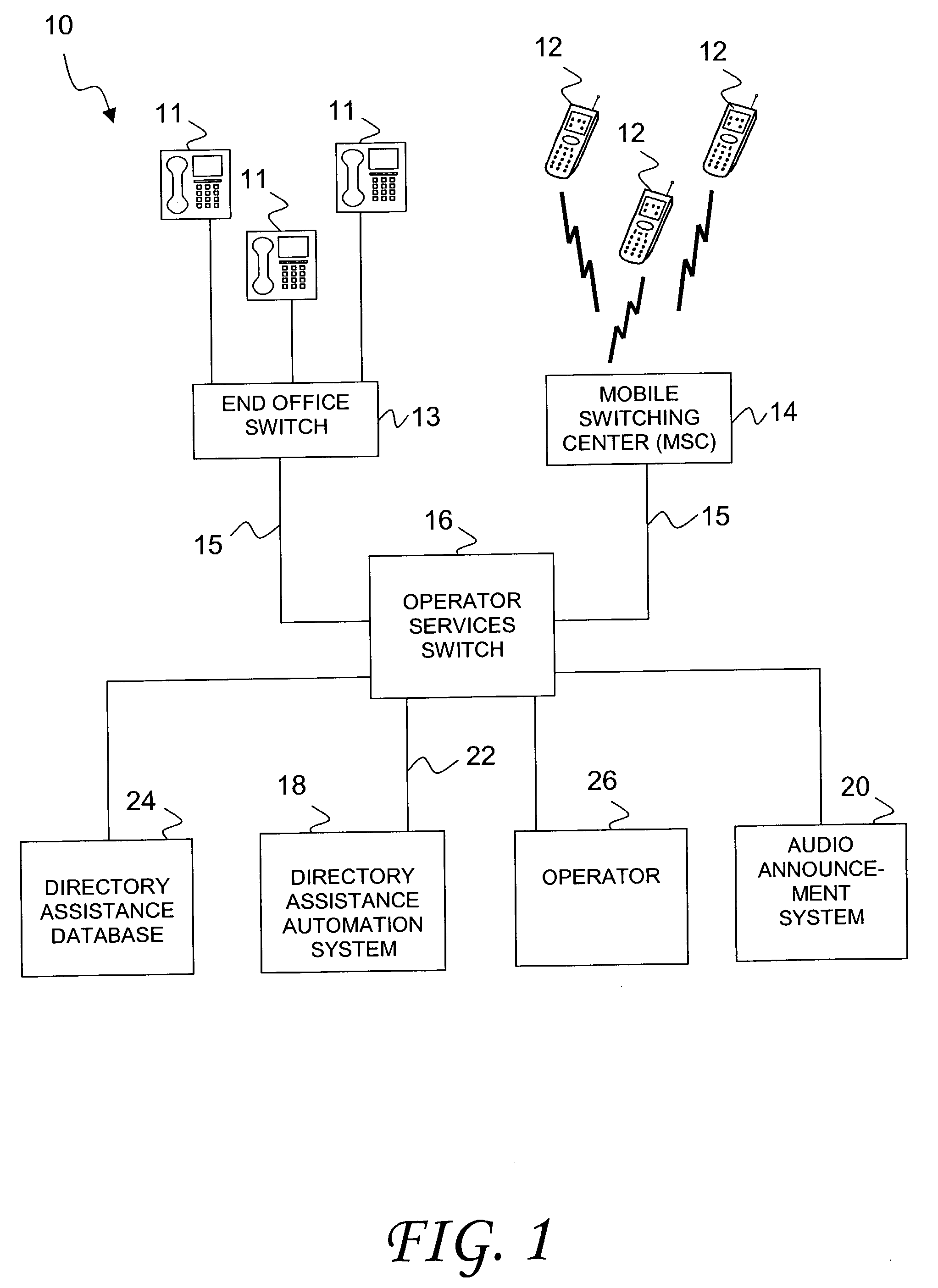

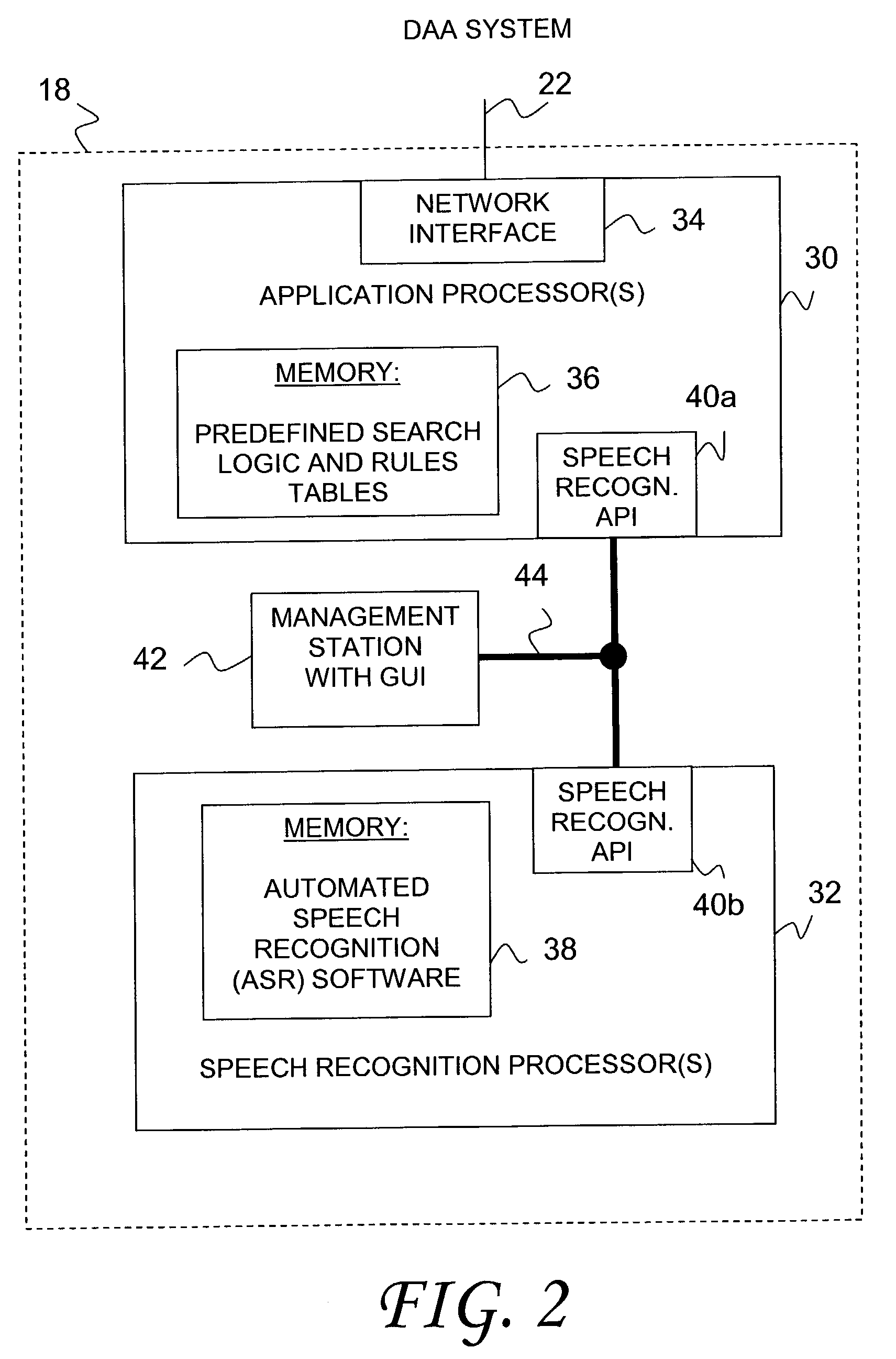

System and method for providing rules-based directory assistance automation

InactiveUS20050240409A1Improve versatilityEasy to processAutomatic exchangesSpeech recognitionGraphicsGraphical user interface

A system and method for providing directory assistance automation to a caller in a telecommunications environment utilizes dedicated processors to convert caller utterances (e.g., corresponding to city, state and listing name) using automated speech recognition technology to grammar strings that are then employed in searching of a listing database. Automation instructions for guiding the database searches are provided via various mapping and rules tables or in separate predefined search logic. Selected rules tables can be programmed by a telecommunications provider to implement customized instructions. Such specialized access may be provided by way of a graphical user interface at the directory assistance automation system.

Owner:VOLT DELTA RESOURCES

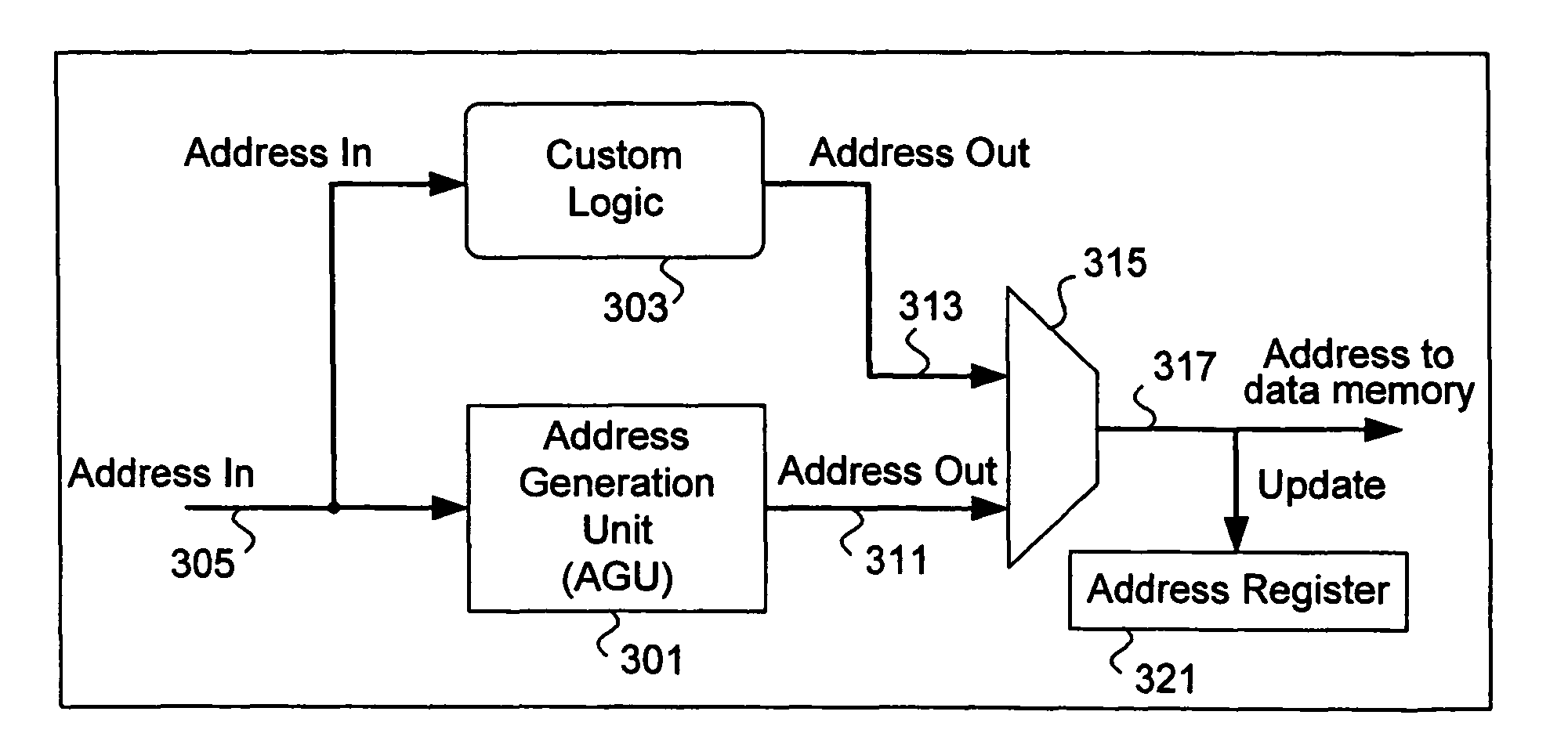

Methods and apparatus for executing extended custom instructions

ActiveUS8006074B1Efficient executionGeneral purpose stored program computerSpecific program execution arrangementsAddress generation unitArithmetic logic unit

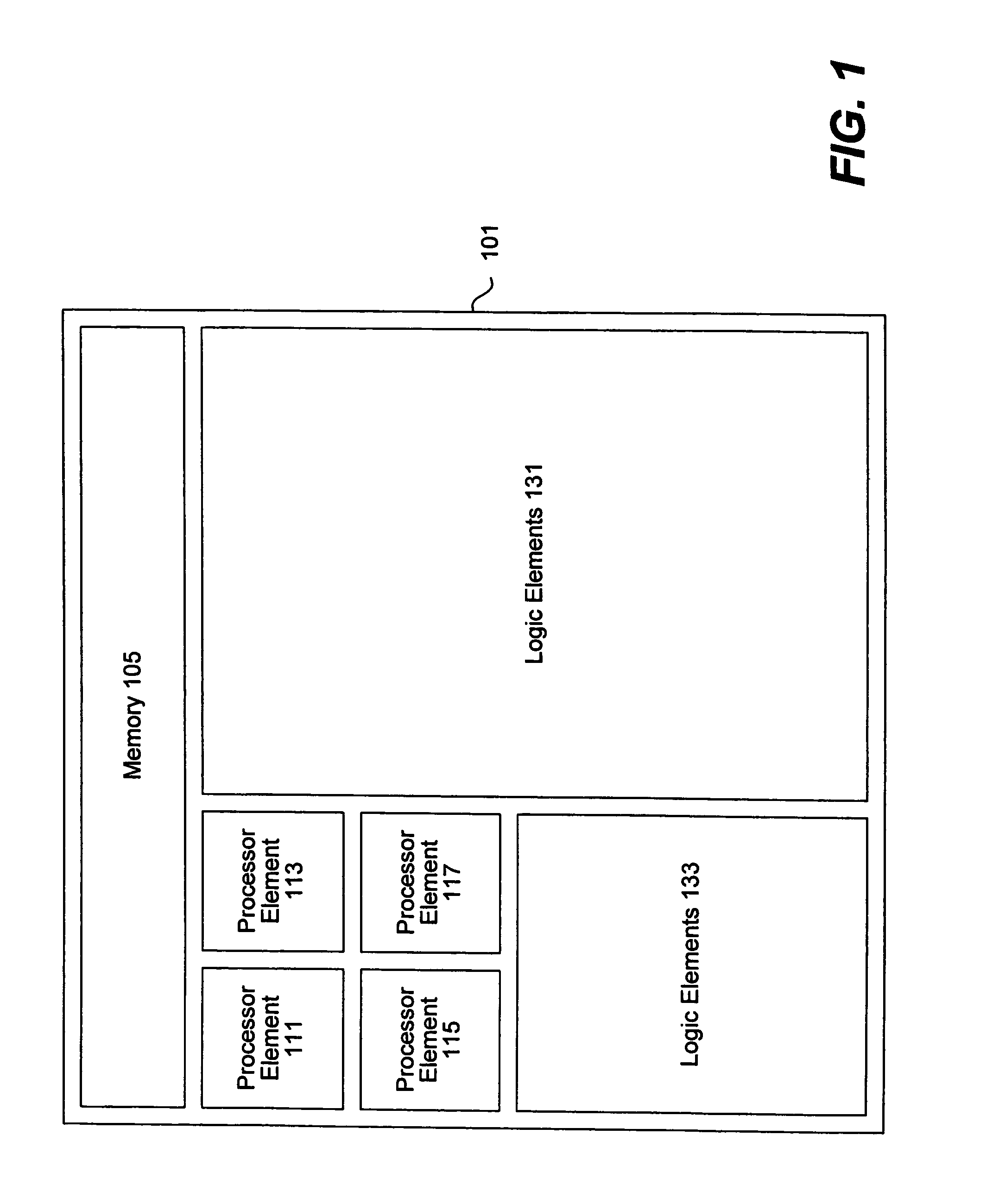

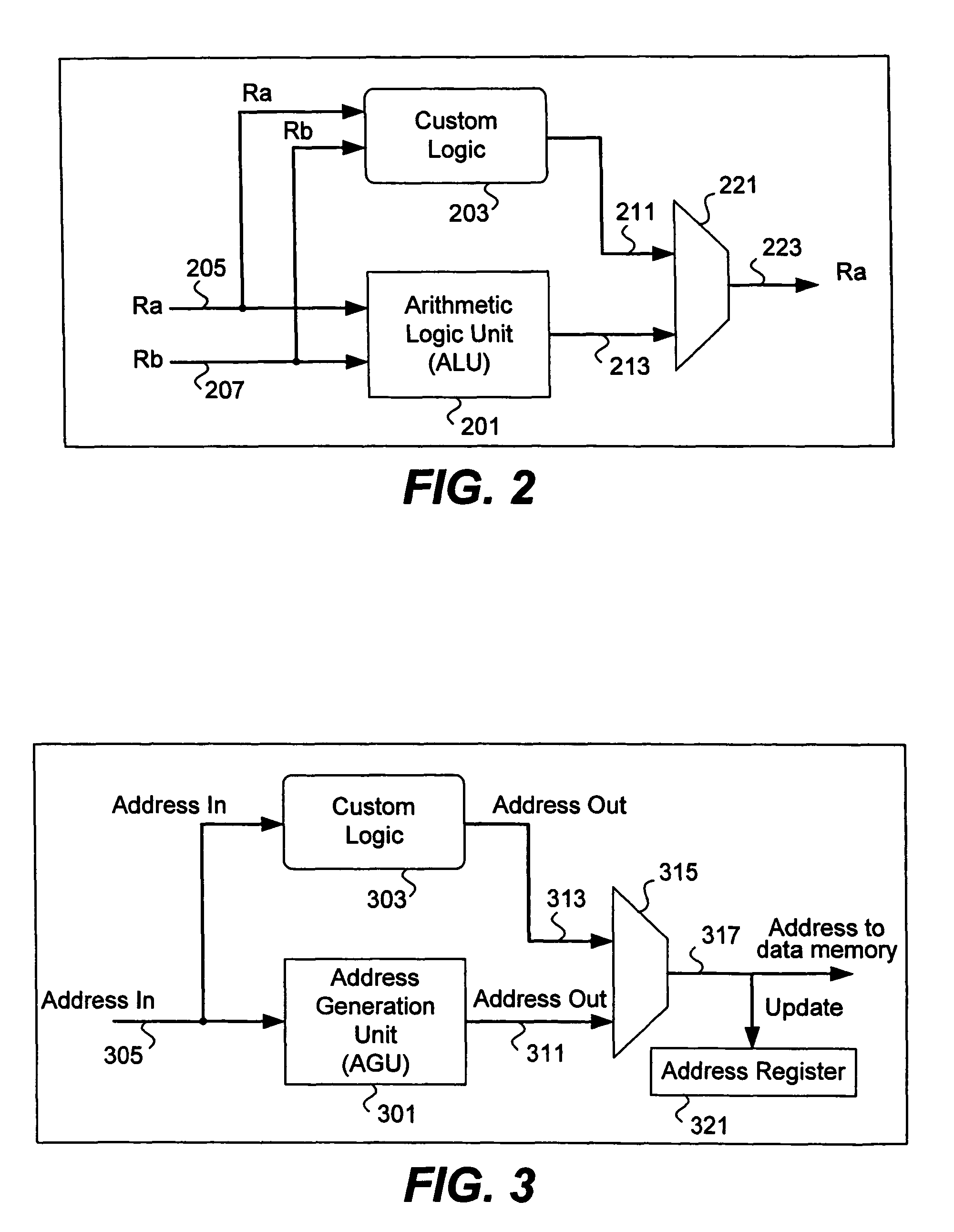

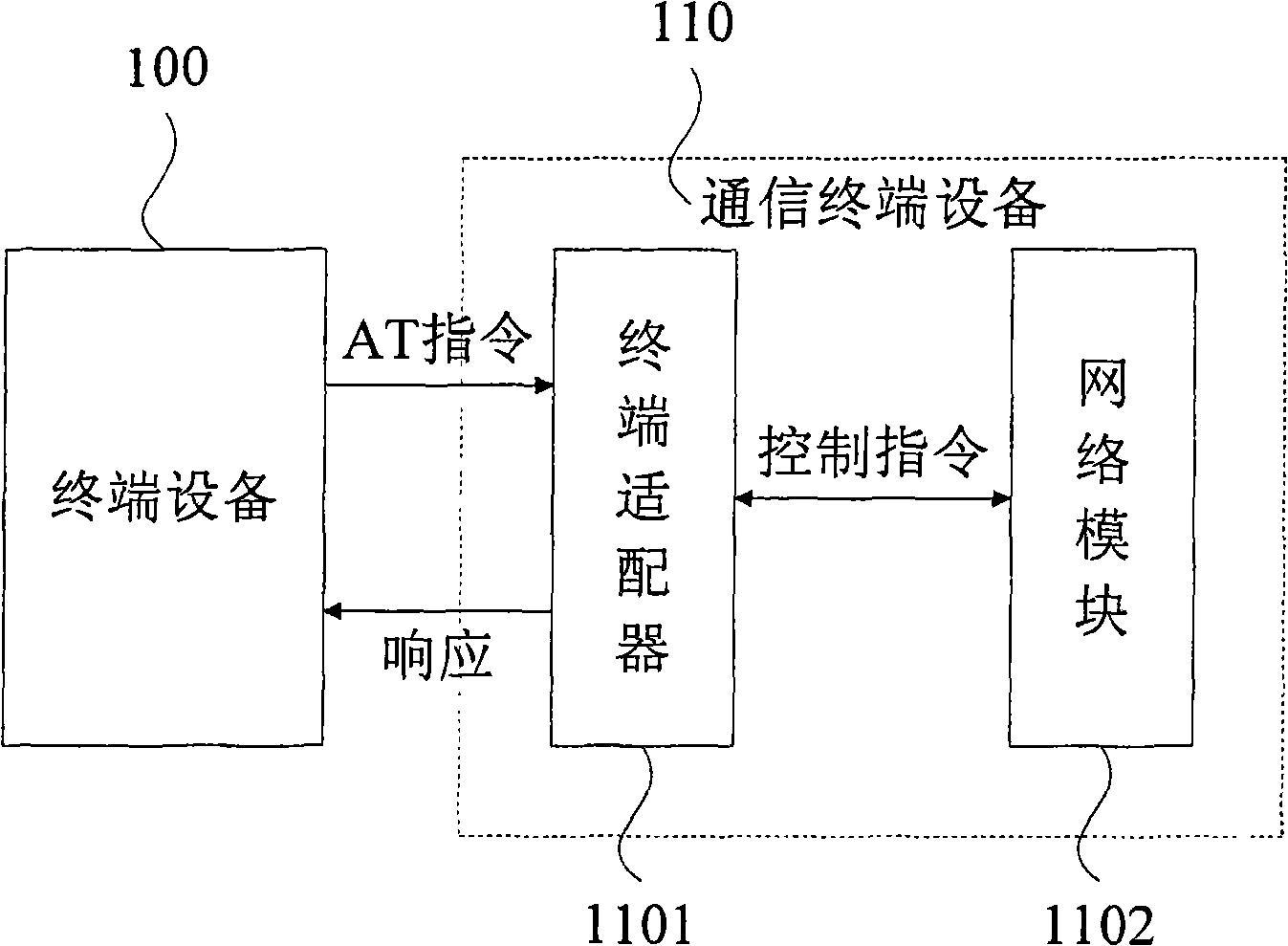

Methods and apparatus are provided for efficiently executing extended custom instructions on a programmable chip. Components of a processor core such as arithmetic logic units, program sequencer units, and address generation units are integrated with customizable logic blocks. Various customizable logic blocks can be invoked in a pipelined manner using an available customized instruction set while allowing a processor to continue simultaneous operation. Program counter snooping is also provided to add custom instruction functionality to a processor with no additional provisions for adding custom instructions.

Owner:ALTERA CORP

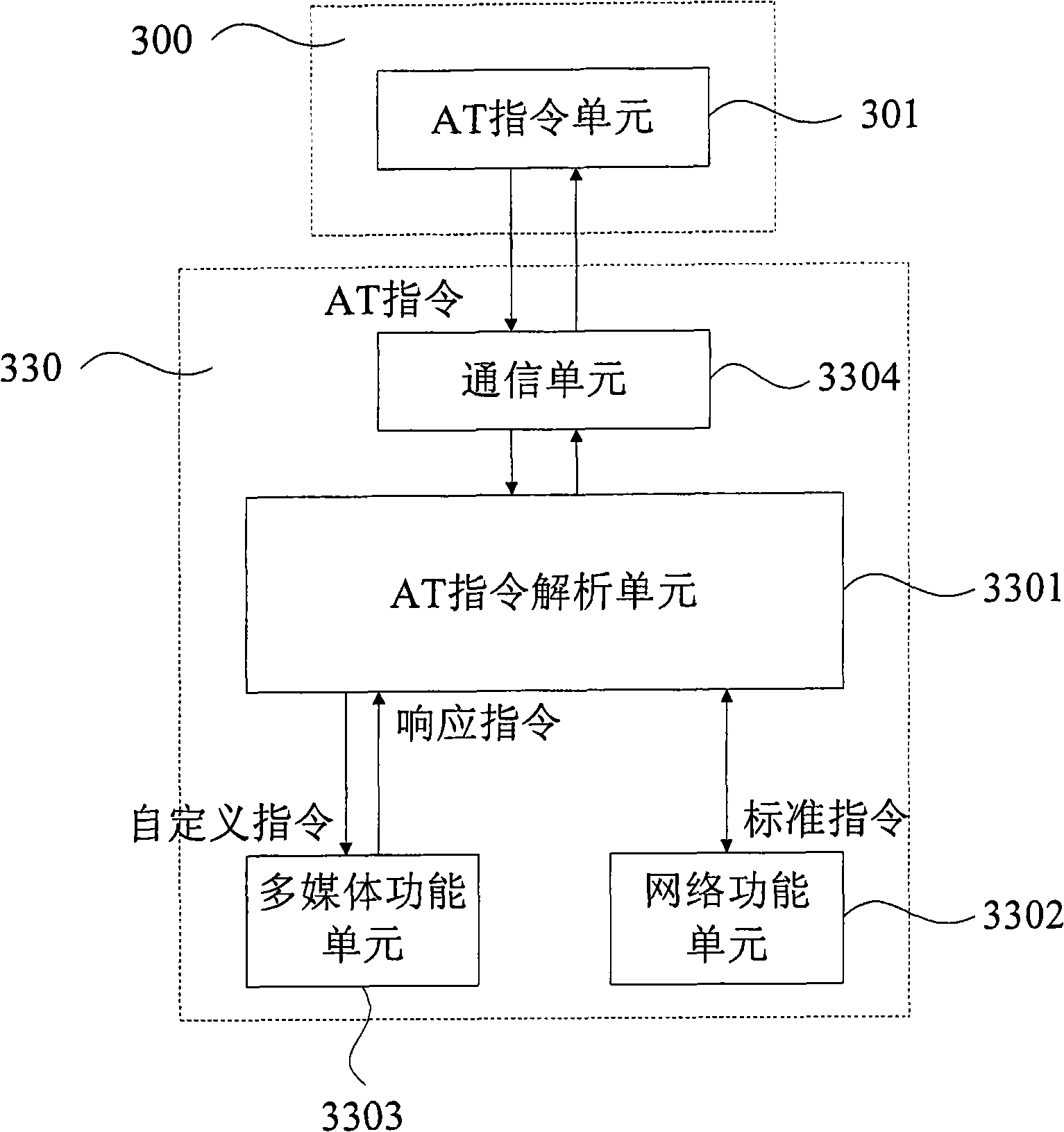

Controlling method and system for mobile communication terminal

InactiveCN101287226AEasy to controlRadio/inductive link selection arrangementsComputer hardwareRemote control

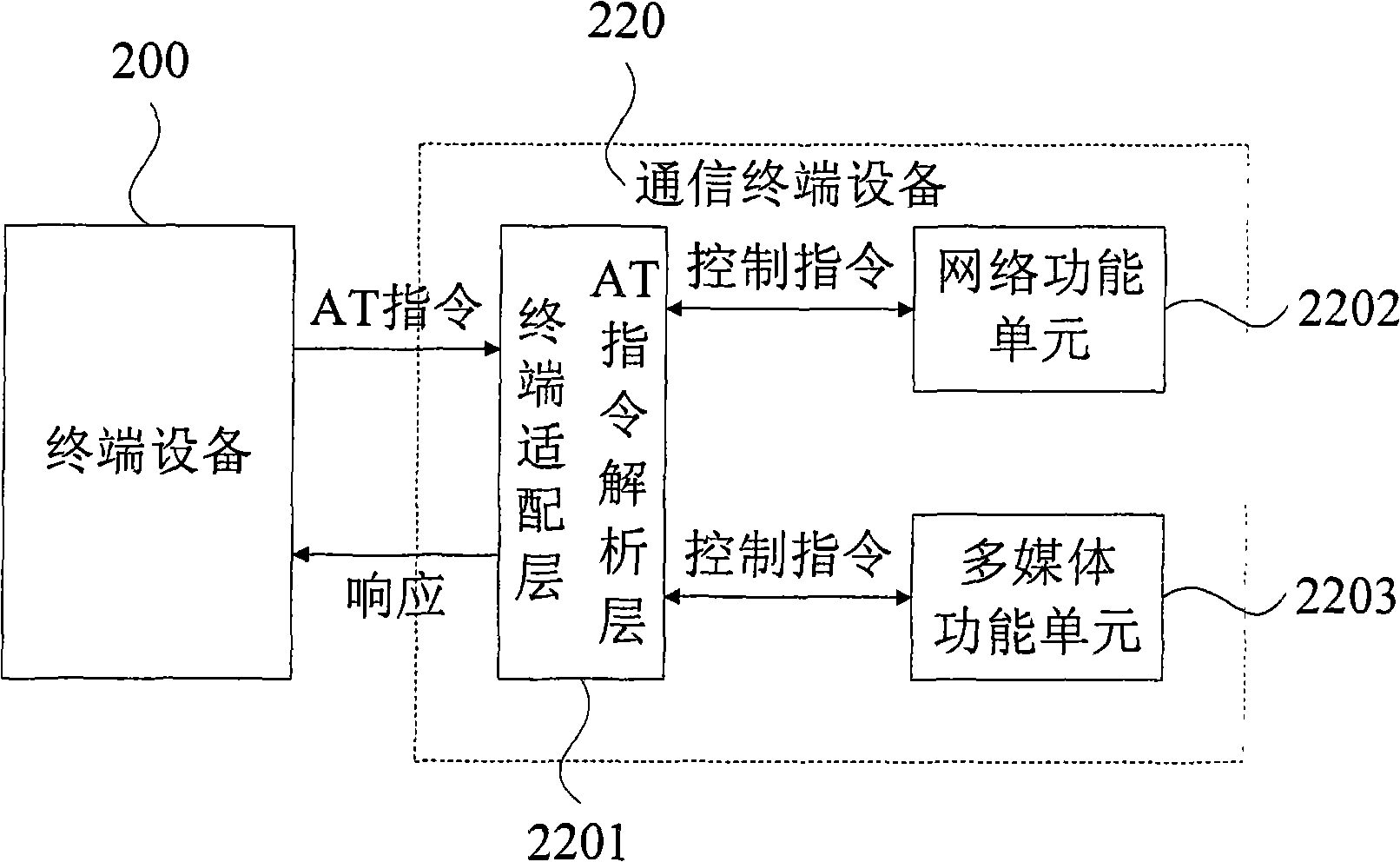

The invention provides a control method of a mobile communication terminal and a system thereof. The system comprises a control terminal and a mobile communication terminal; the control terminal comprises an AT instruction sending unit for sending an AT instruction to control the mobile communication terminal; the mobile communication terminal is connected with the control terminal and used for receiving the AT instruction, and executes the network function or the multimedia function of the mobile communication terminal corresponding to the AT instruction through the analysis of the AT instruction. Through the adding of the codes and the parameters corresponding to custom instructions in an AT instruction analysis unit and a multimedia function unit, the invention expands the control of the control terminal to the mobile communication terminal; the technology is applicable to the test and the remote control of various functions of the mobile phone and can realize more expansion functions by adding more custom instructions.

Owner:TECHFAITH WIRELESS TECH BEIJING

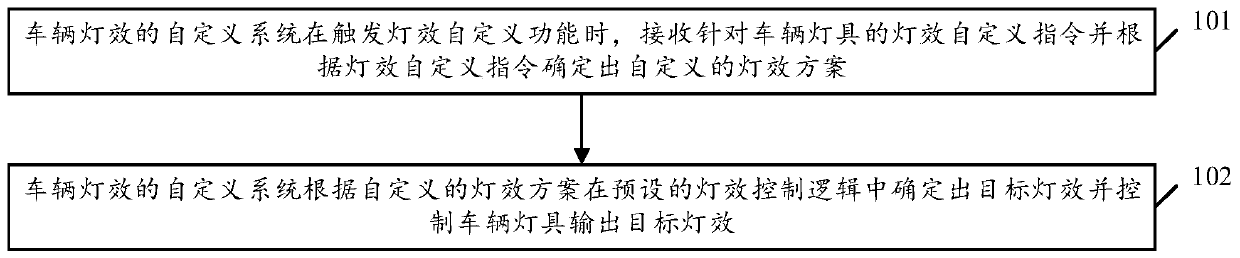

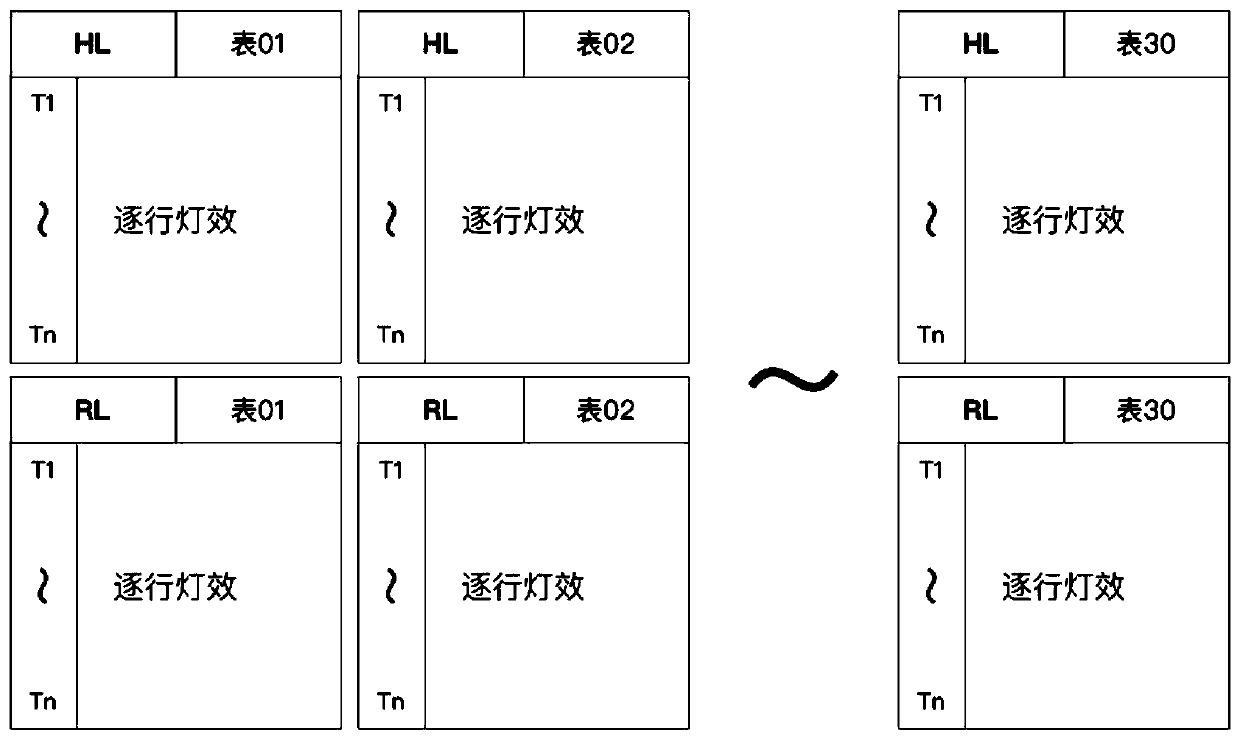

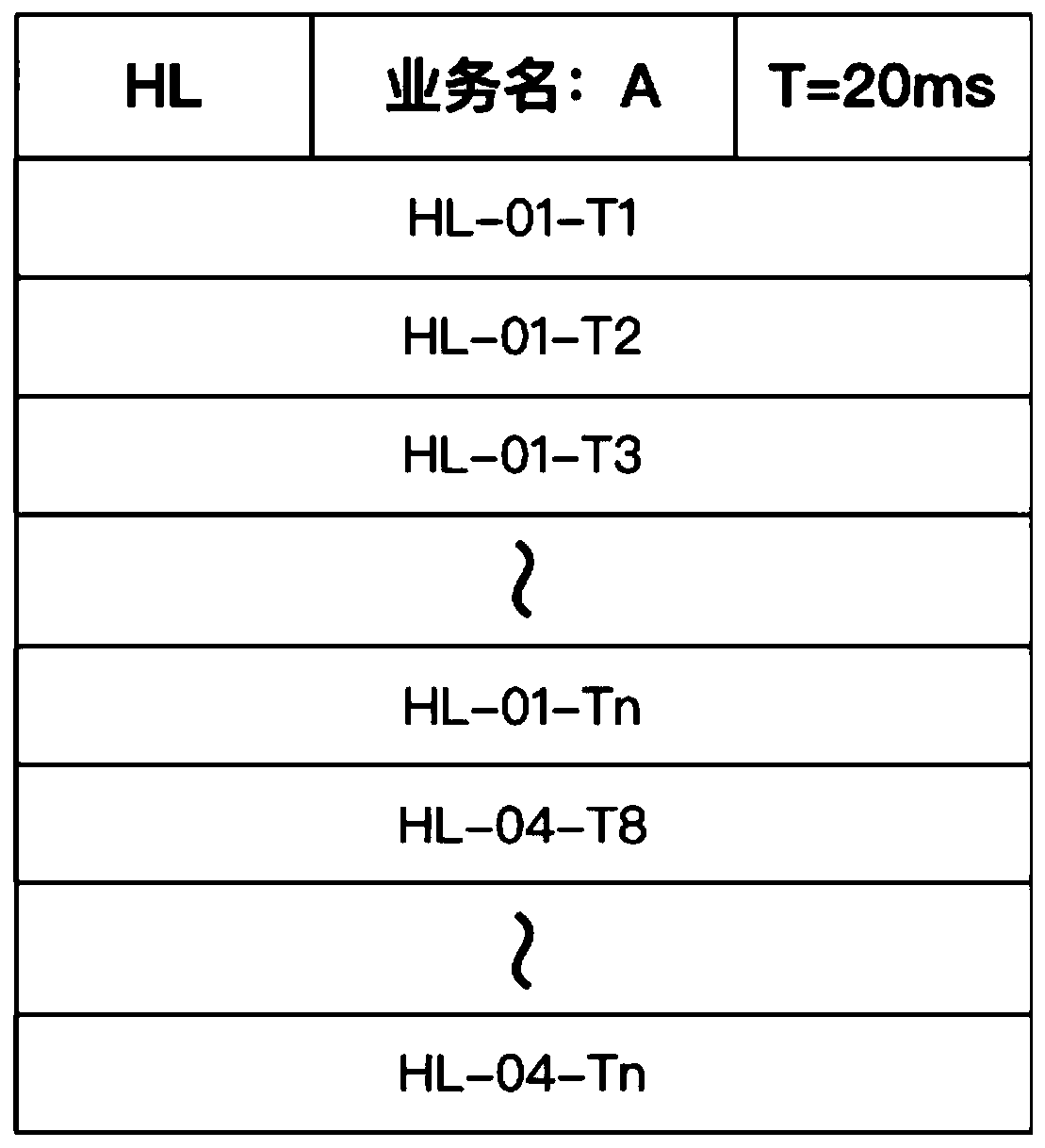

Custom method and system of vehicle lighting effects, and vehicle

InactiveCN110001505AMeet control needsRealize intelligent controlOptical signallingSubstation equipmentEngineeringControl logic

The embodiment of the invention relates to the technical field of vehicles, and discloses a custom method and system of vehicle lighting effects, and a vehicle. The custom method comprises the steps:when a lighting effect custom function is triggered, a lighting effect custom instruction aiming at a vehicle lamp is received, and a custom lighting effect scheme is determined according to the lighting effect custom instruction; and according to the custom lighting effect scheme, the target lighting effect is determined in the preset lighting effect control logic, and the vehicle lamp is controlled to output the target lighting effect. By implementing the custom method, users can intelligently control vehicle lighting effect output, thus the vehicle lamp can output the various different lighting effects in a certain fixed scene, and the increasing control demands of the users for the vehicle lamp are met.

Owner:GUANGZHOU XIAOPENG MOTORS TECH CO LTD

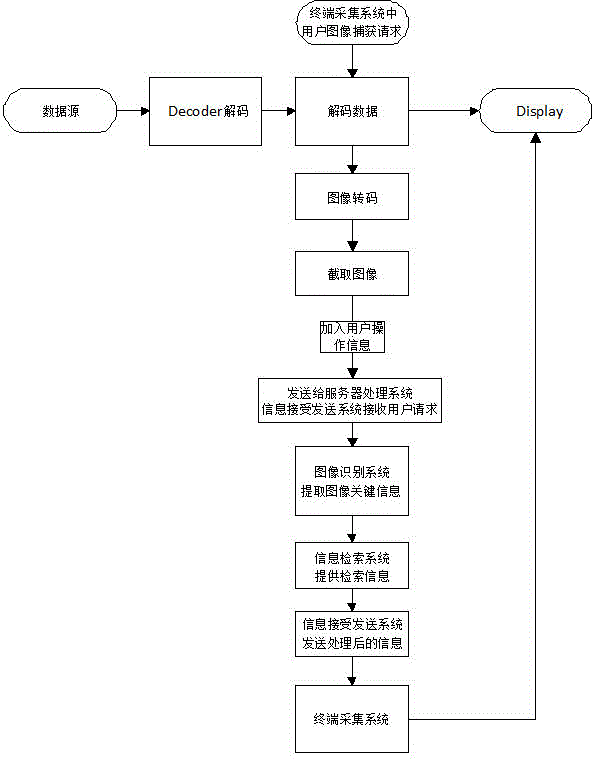

System and method for pushing information based on video content

The invention discloses an information push system and method based on video content, belongs to the technical field of information push and aims at solving the technical problem of how to improve the viewing experience of users. The information push system based on video content comprises a terminal collection system, a server processing system and a public API interface system, wherein the terminal collection system is responsible for video decoding; the server processing system makes corresponding processing according to the data transmitted by the terminal collection system and returns the corresponding data to the terminal collection system; the public API interface system is used for system expansion. According to the information push method based on the video content, images are captured according to custom instructions through the terminal collection system, and the following operations are provided: sharing operation, film review operation, feature spot operation, commodity operation and information code operation; the terminal collection system sends the request of a user to the server processing system; the server processing system processes the sent request of the user and returns the results to the terminal collection system.

Owner:INSPUR QILU SOFTWARE IND

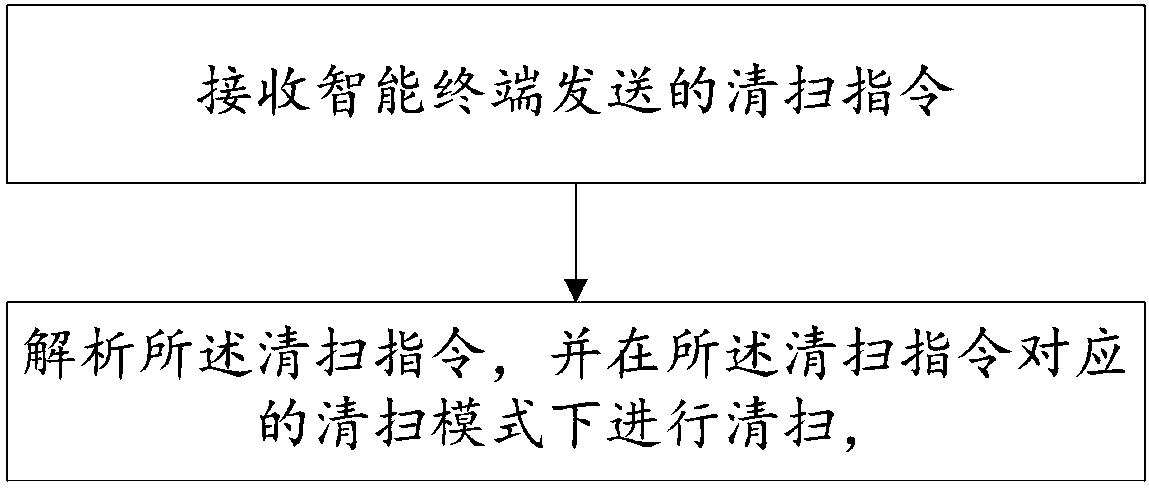

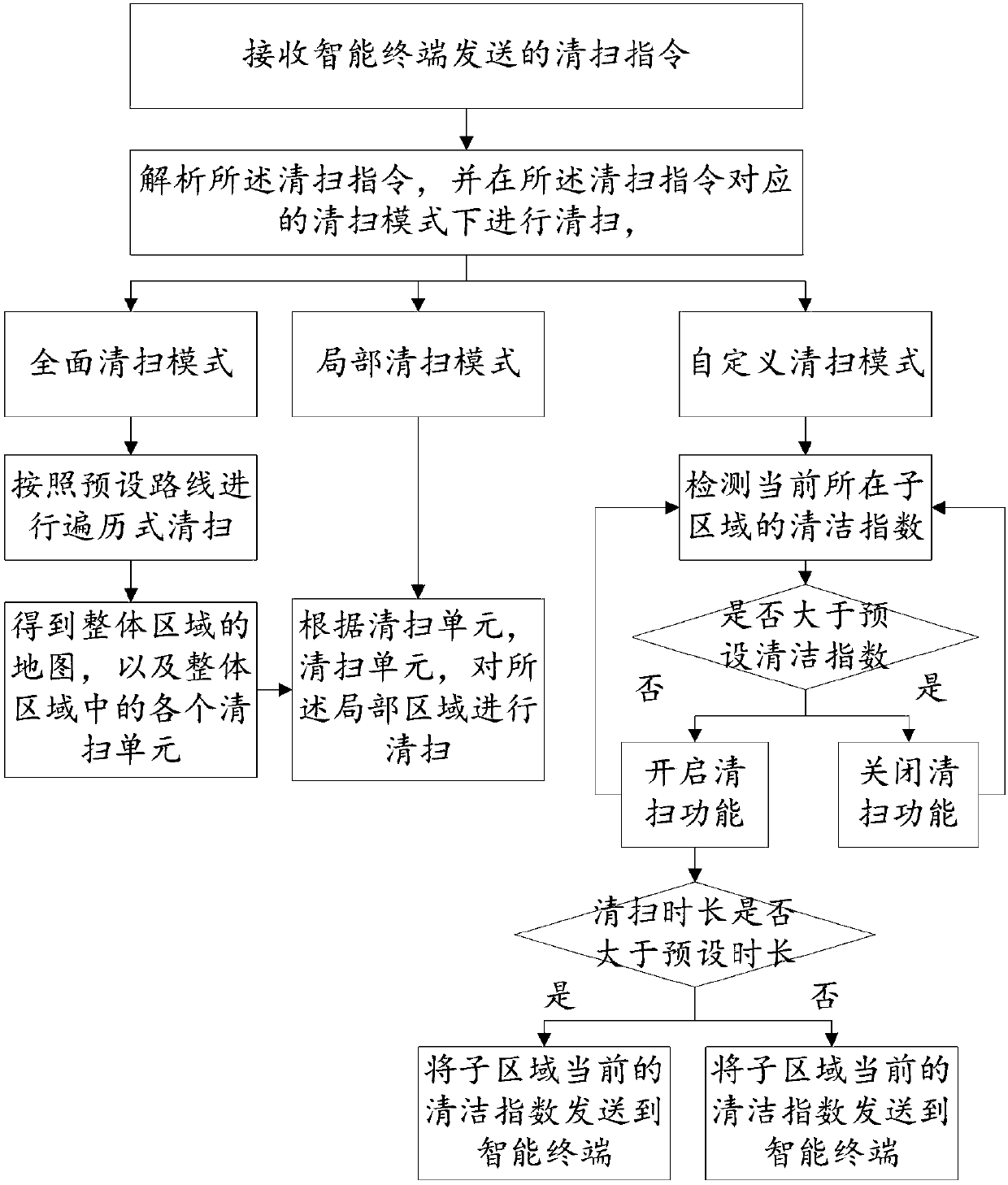

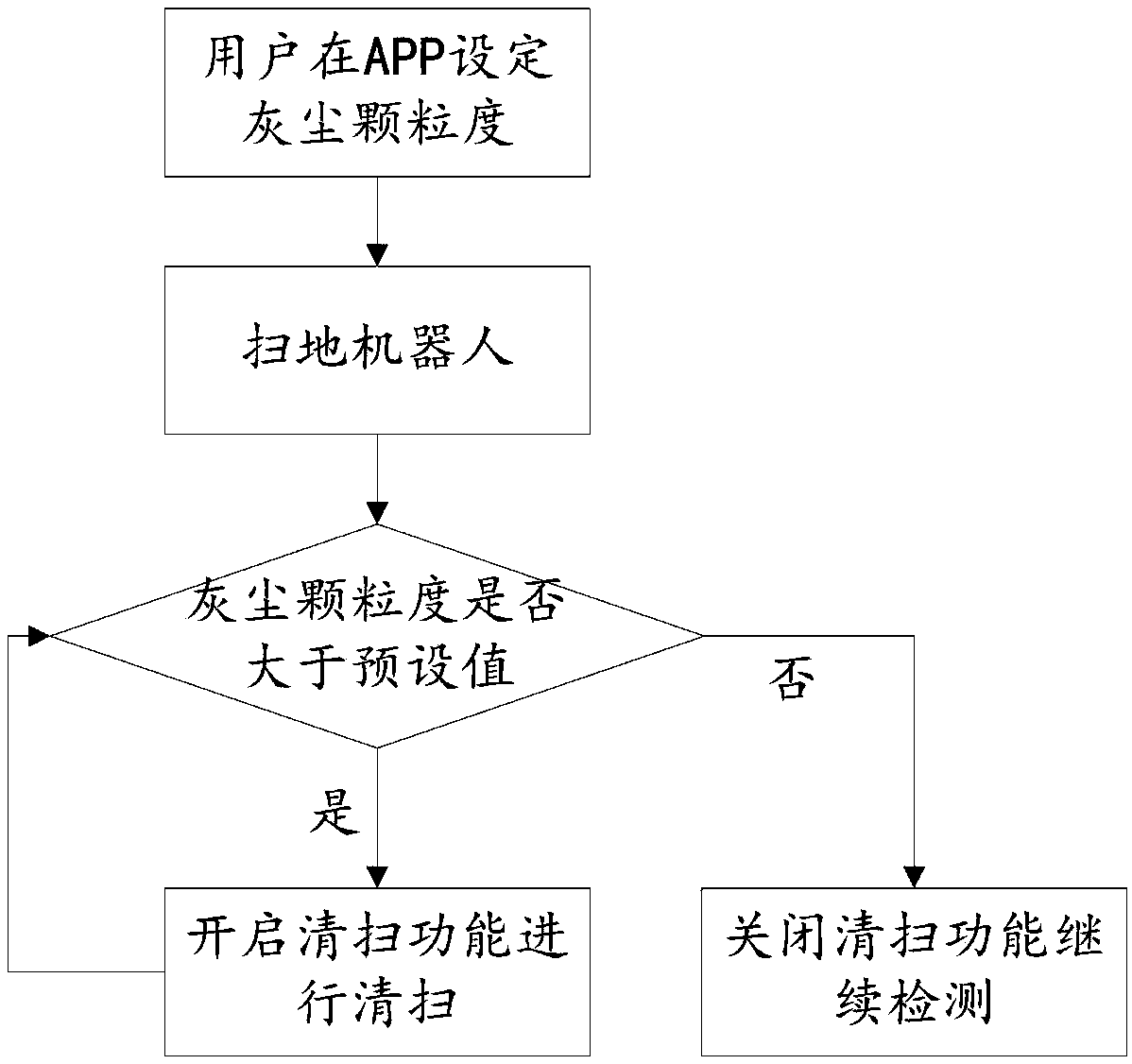

Cleaning method for sweeping robots and sweeping robot

InactiveCN107807647AMeet needsImprove practicalityPosition/course control in two dimensionsEngineeringCustom instruction

The present invention provides a cleaning method and system for a sweeping robot. The method includes: receiving a cleaning instruction sent by an intelligent terminal; the cleaning instruction includes a comprehensive cleaning instruction, a partial cleaning instruction, and a self-defined cleaning instruction; analyzing the cleaning instruction, And perform cleaning in the cleaning mode corresponding to the cleaning instruction, and the cleaning mode includes a comprehensive cleaning mode, a partial cleaning mode, and a custom cleaning mode. In the present invention, the sweeping robot can focus on cleaning the floor in a relatively dusty area by identifying the dust on the floor, thereby improving the practicability and intelligence of the sweeping robot.

Owner:台州市吉吉知识产权运营有限公司

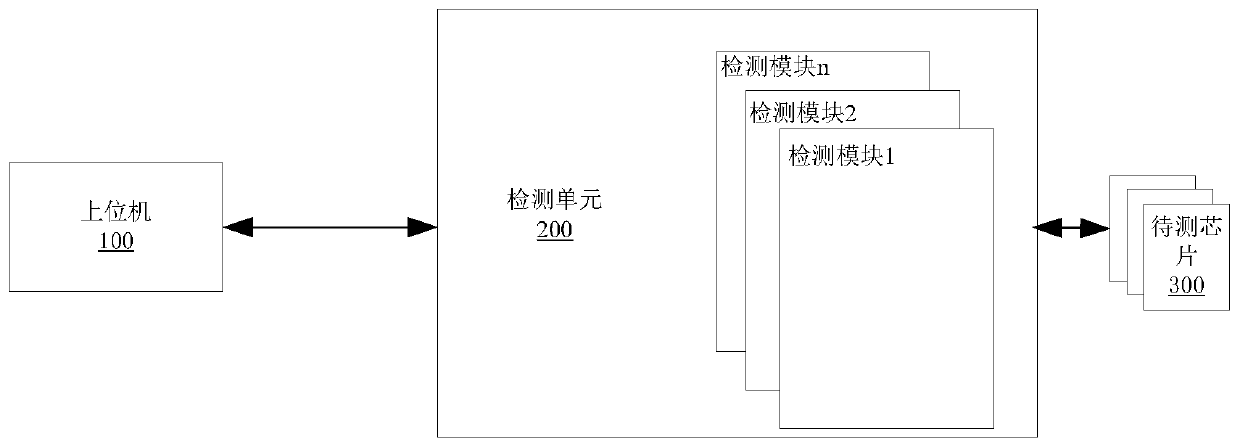

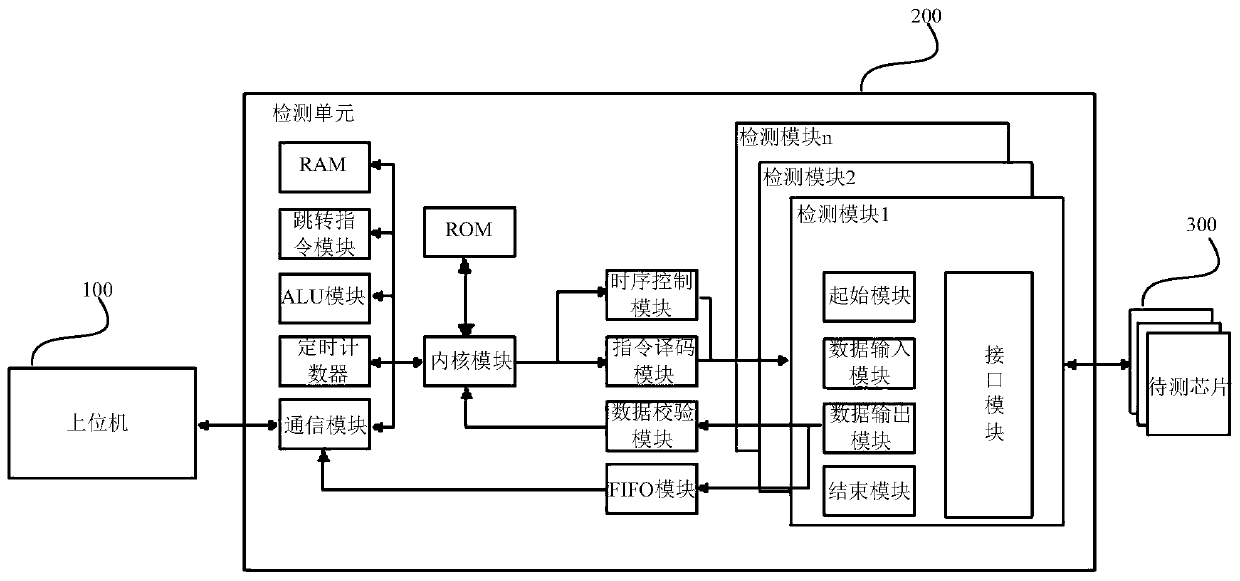

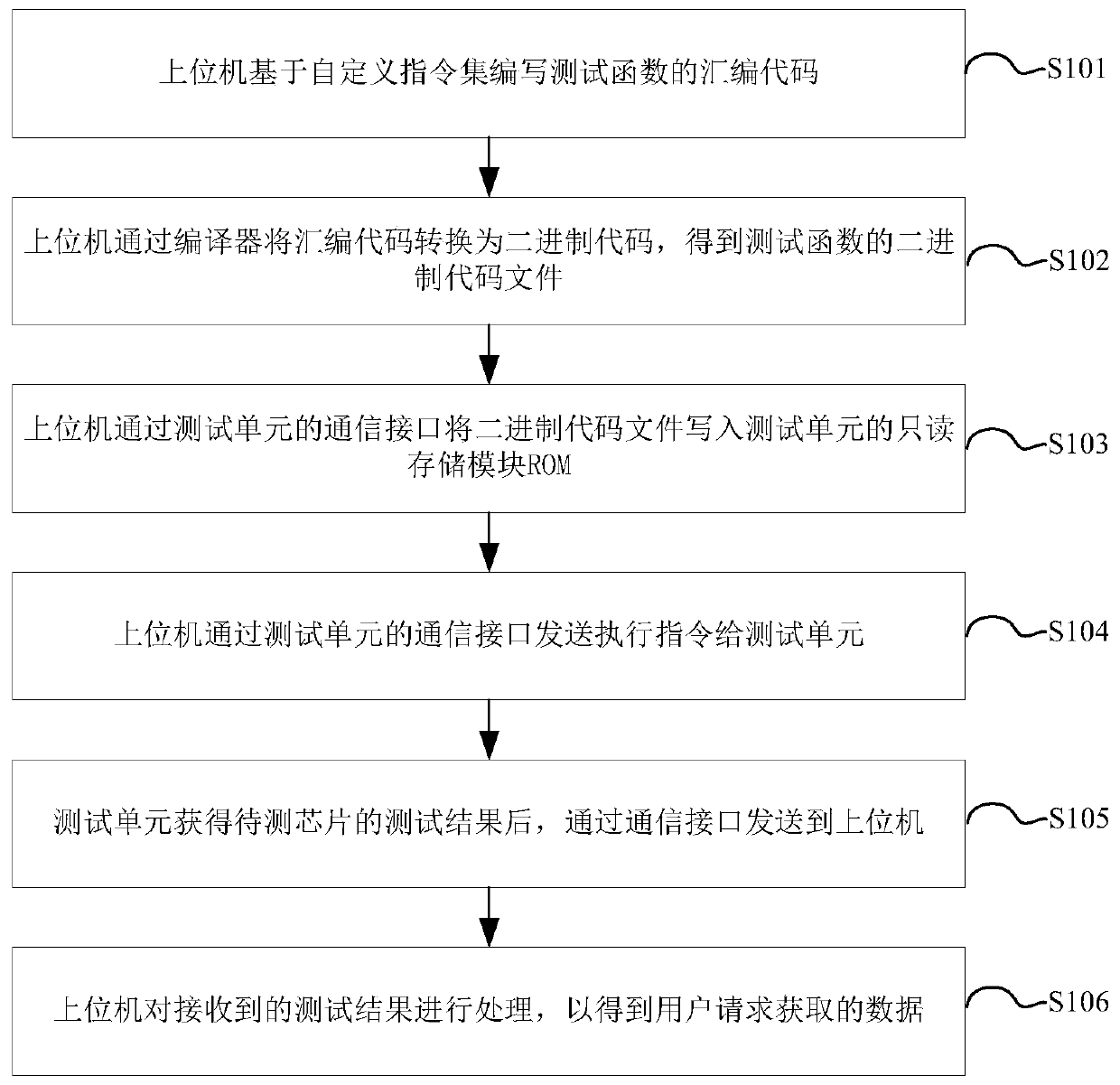

Chip test system and test method

ActiveCN110634530ASolve the small number of simultaneous testsSolve the costStatic storageComputer moduleLab test method

The embodiment of the invention provides a chip test system and test method. The test system comprises an upper computer and a test unit which are in communication connection with each other. The testunit is built by an FPGA chip and is configured with a plurality of parallel test modules, and the test modules are in one-to-one correspondence with to-be-tested chips. The test unit writes a test function through an upper computer, and the test function is a function written based on a custom instruction set; wherein the upper computer sends a start instruction to the test unit, the test unit operates the test function after receiving the start instruction so as to call the plurality of test modules to test the corresponding chips to be tested respectively, and test results obtained based on output data of the chips to be tested are sent to the upper computer. The chip test system and the test method provided by the embodiment of the invention are based on an FPGA hardware system and test is carried out through the test function written by the custom instruction set, so that the technical problems of a small number of chips under the same test and high test cost are solved.

Owner:珠海博雅科技股份有限公司

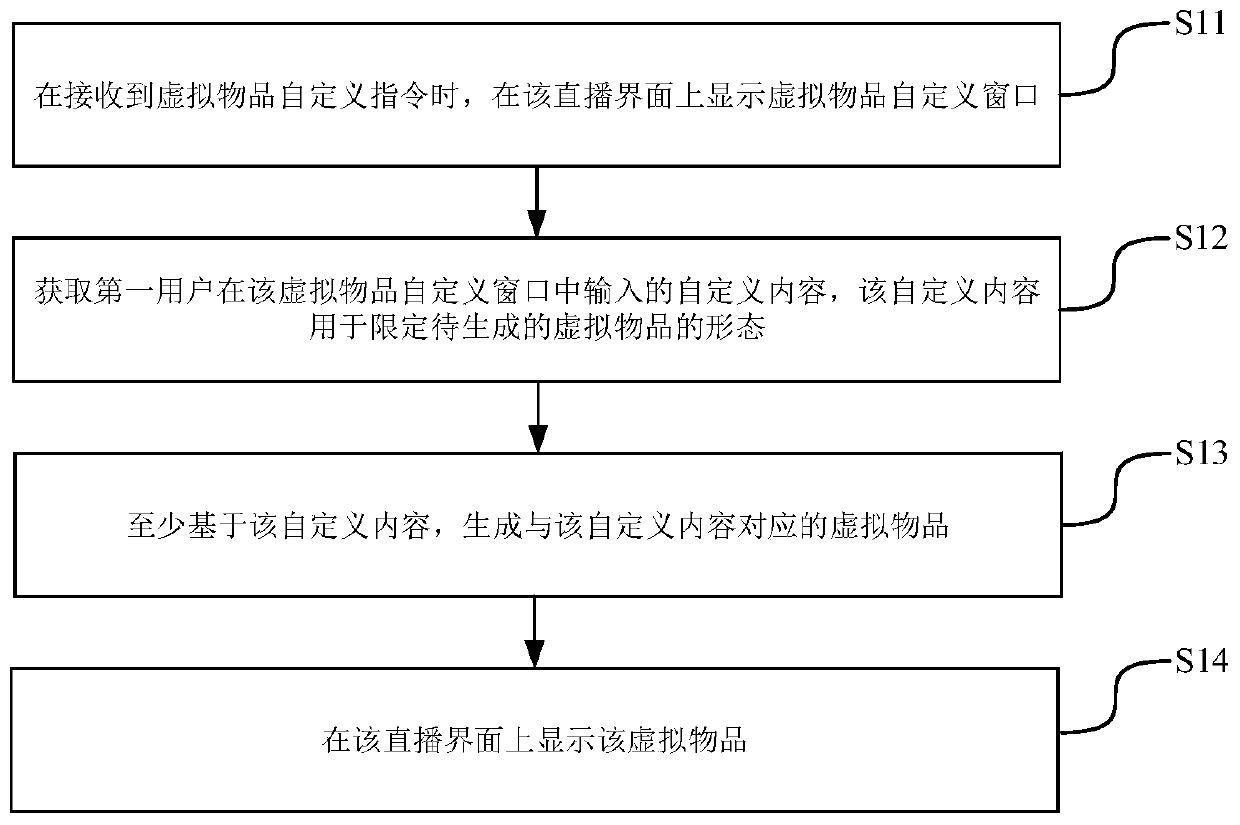

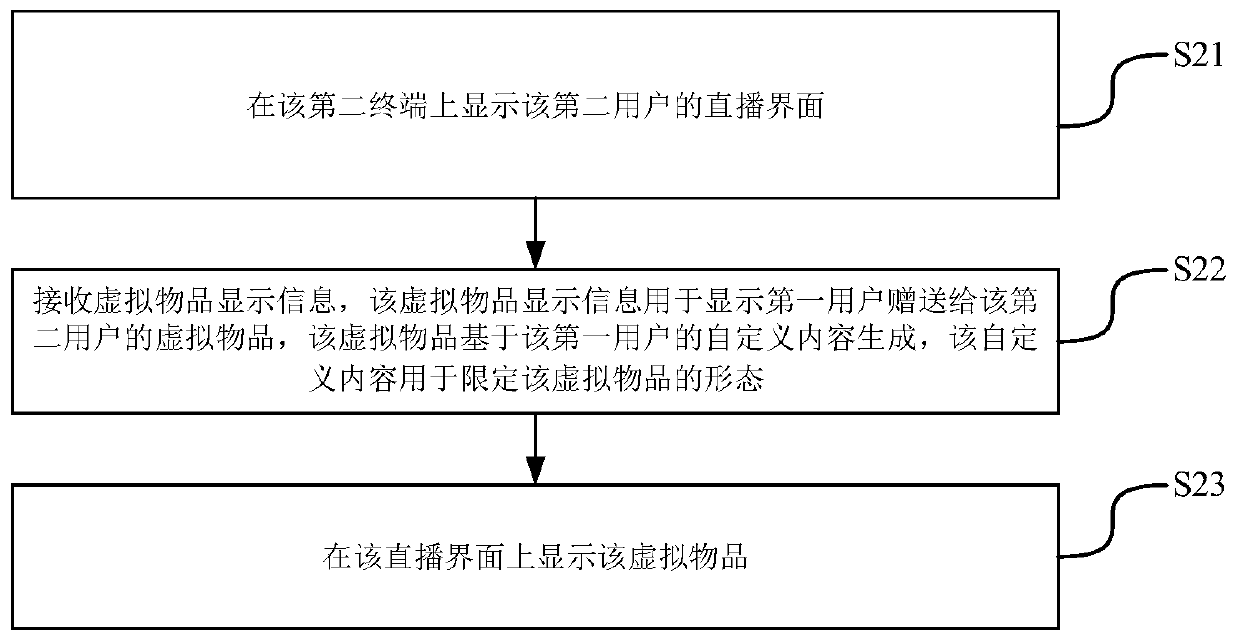

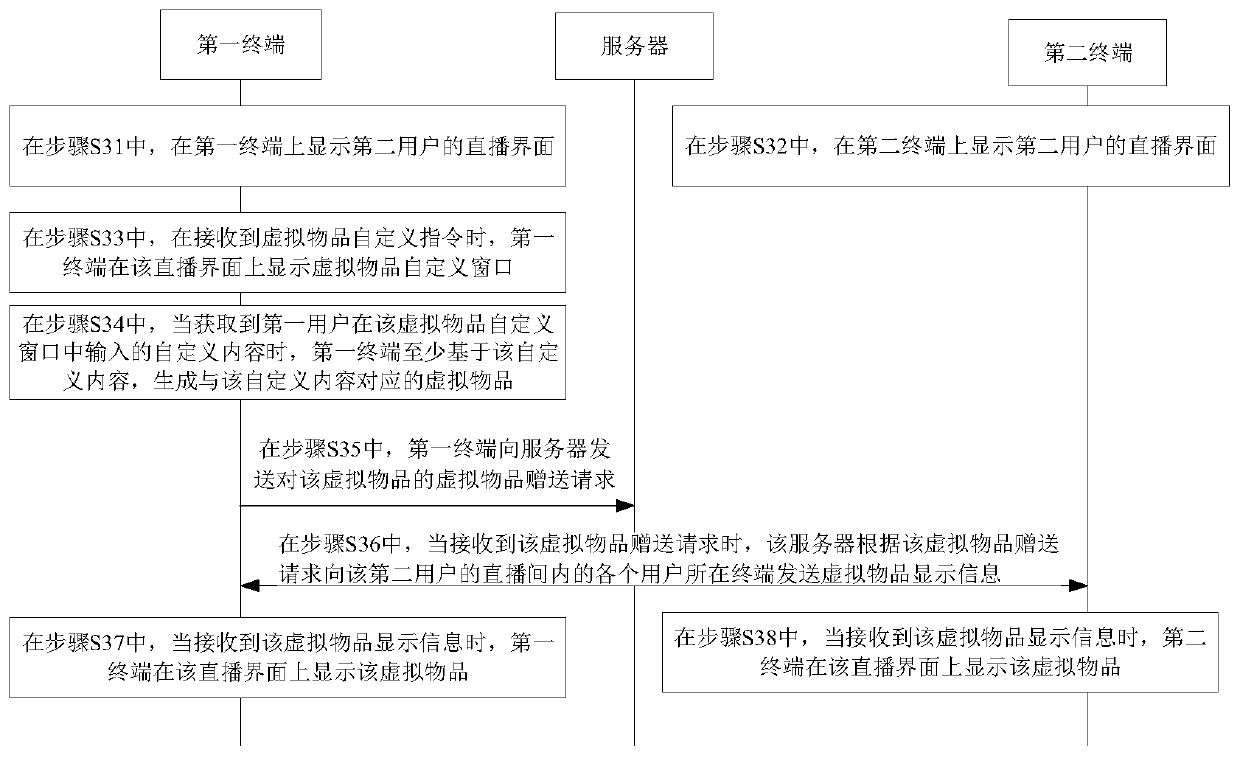

Virtual article display method and device, terminal and storage medium

InactiveCN110139142AMeet the needs of custom virtual itemsImprove the display effectCommerceSelective content distributionComputer terminalUser defined

The invention relates to a virtual article display method and device, a terminal and a storage medium, and belongs to the technical field of networks. The method comprises the steps that when a virtual article custom instruction is received, displaying a virtual article custom window on a live broadcast interface; obtaining custom content input by a first user in the virtual article custom window,wherein the custom content is used for limiting the form of a to-be-generated virtual article; generating a virtual article corresponding to the custom content at least based on the custom content; and displaying the virtual article on the live broadcast interface. According to the invention, the audience user can customize the virtual article for the anchor user, the demand of customizing the virtual article by the audience user can be met, more abundant expression modes are provided for the audience user, the virtual article customized by the audience user can be displayed on the live broadcast interface, and the display effect of the virtual article can be enriched.

Owner:BEIJING DAJIA INTERNET INFORMATION TECH CO LTD

Multistage development workflow for generating a custom instruction set reconfigurable processor

ActiveUS8972958B1Facilitating development and generationEasy to useSpecific program execution arrangementsMemory systemsLoad instructionProgram code

Systems and systems which implement workflows for providing reconfigurable processor core algorithms operable with associated capabilities using description files, thereby facilitating the development and generation of instruction sets for use with reconfigurable processors, are shown. Embodiments implement a multistage workflow in which program code is parsed into custom instructions and corresponding capability descriptions for generating reconfigurable processor loadable instruction sets. The multistage workflow of embodiments includes a hybrid threading complier operable to compile input program code into custom instructions using a hardware timing agnostic approach. A timing manager of the multistage workflow of embodiments utilizes capabilities information provided in association with the custom instructions generated by the hybrid threading complier to impose hardware timing on the custom instructions. A framework generator and hardware description language complier are also included in the multistage workflow of embodiments.

Owner:MICRON TECH INC

Asynchronous data triggering micro-processor architecture

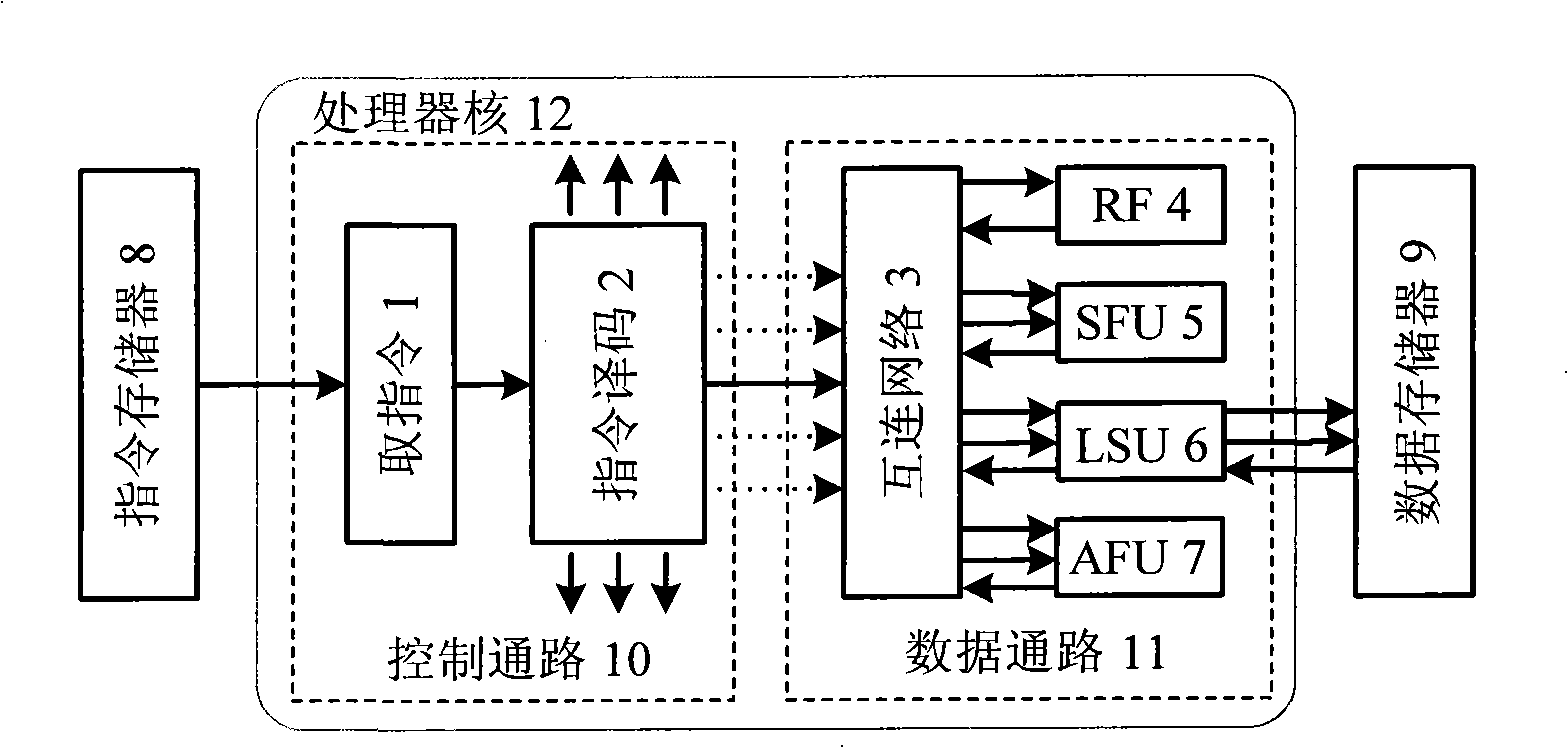

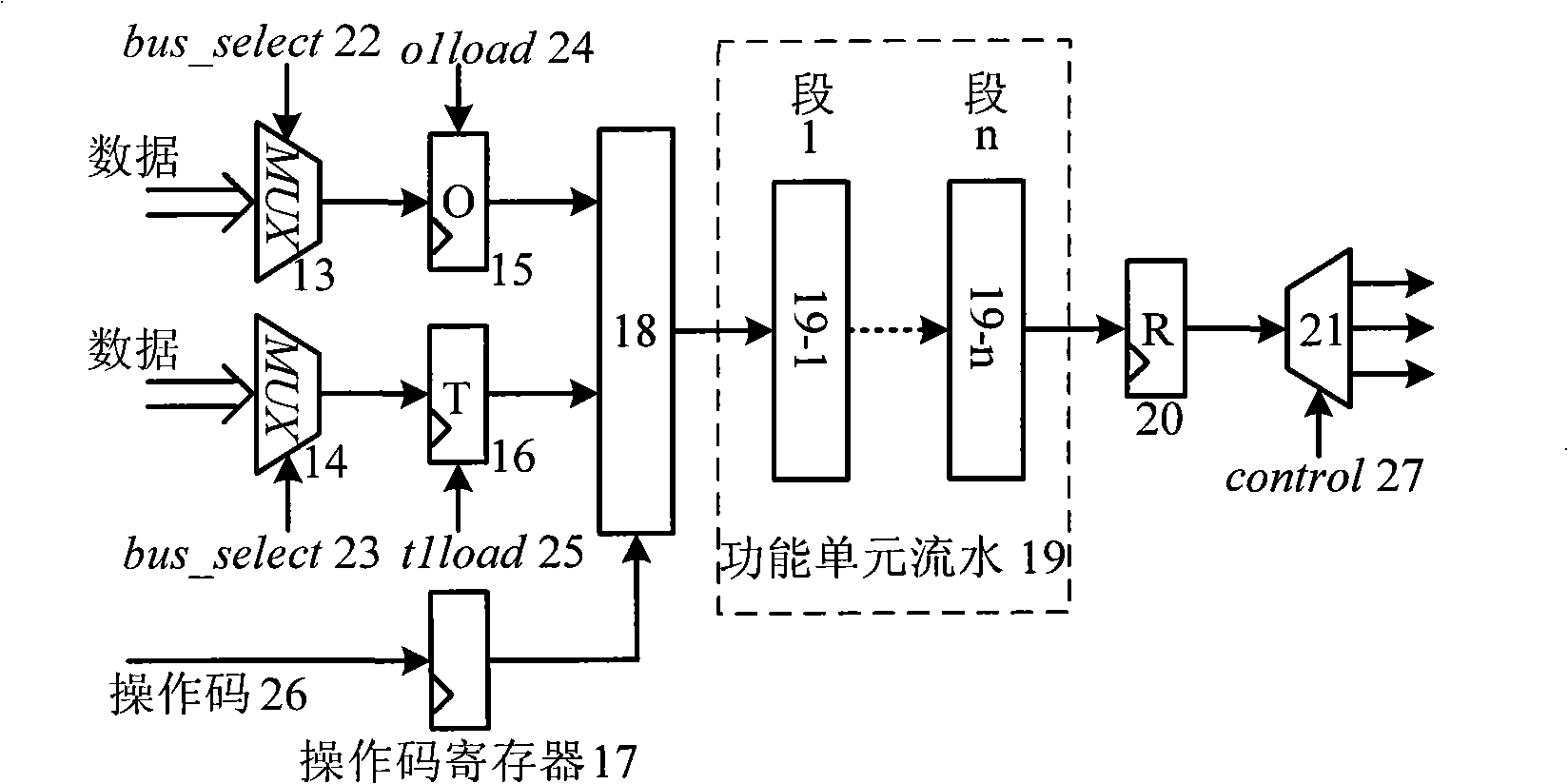

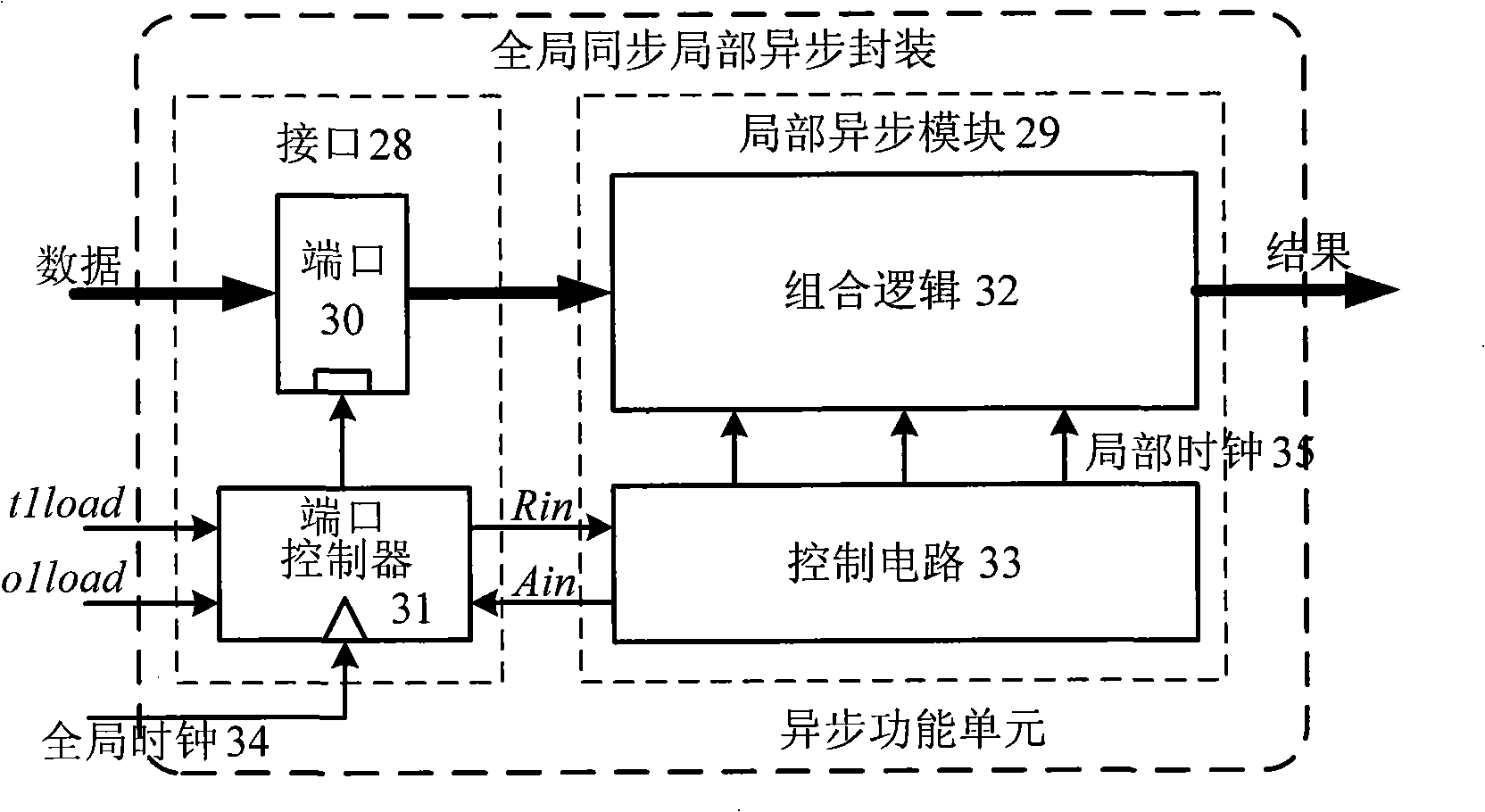

InactiveCN101403963AImprove performanceSimple structureConcurrent instruction executionInstruction memoryComputer architecture

The invention relates to a system structure of an asynchronous data triggered microprocessor, which consists of a data path and a control path; the data path consists of a register file and a functional unit, wherein, the functional unit is connected with a data storage device for carrying out reading and writing on the data storage device; the control path comprises an instruction fetching unit and a coding unit; wherein, the instruction fetching unit is connected with an instruction storage device for reading the instruction from the instruction storage device; meanwhile, the instruction fetching unit is also connected with the coding unit for sending the instruction obtained to the coding unit to carry out coding; the control path and the data path are connected by an interconnecting network, and the coding unit sends the instruction coding result to the needed functional unit by the interconnecting network. The invention combines a plurality of design methods of the microprocessors with the design technologies thereof, which has simpler structure and higher performance; low power consumption of the microprocessors can be realized on the two aspects of the system structure and the circuit in the invention, therefore, the technology of a custom instruction set processor does not need to excessively consider numerous problems which are originally faced.

Owner:戴葵

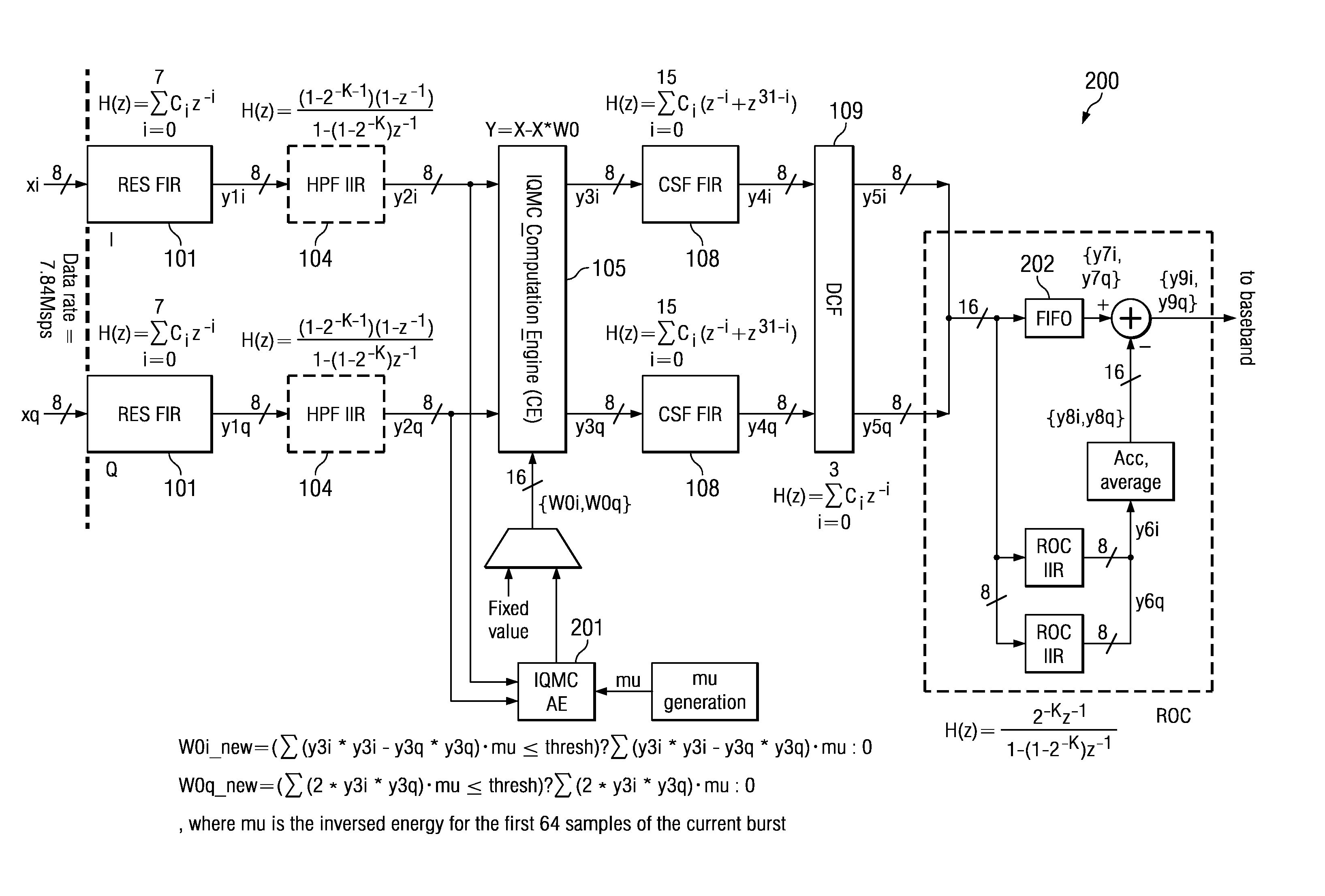

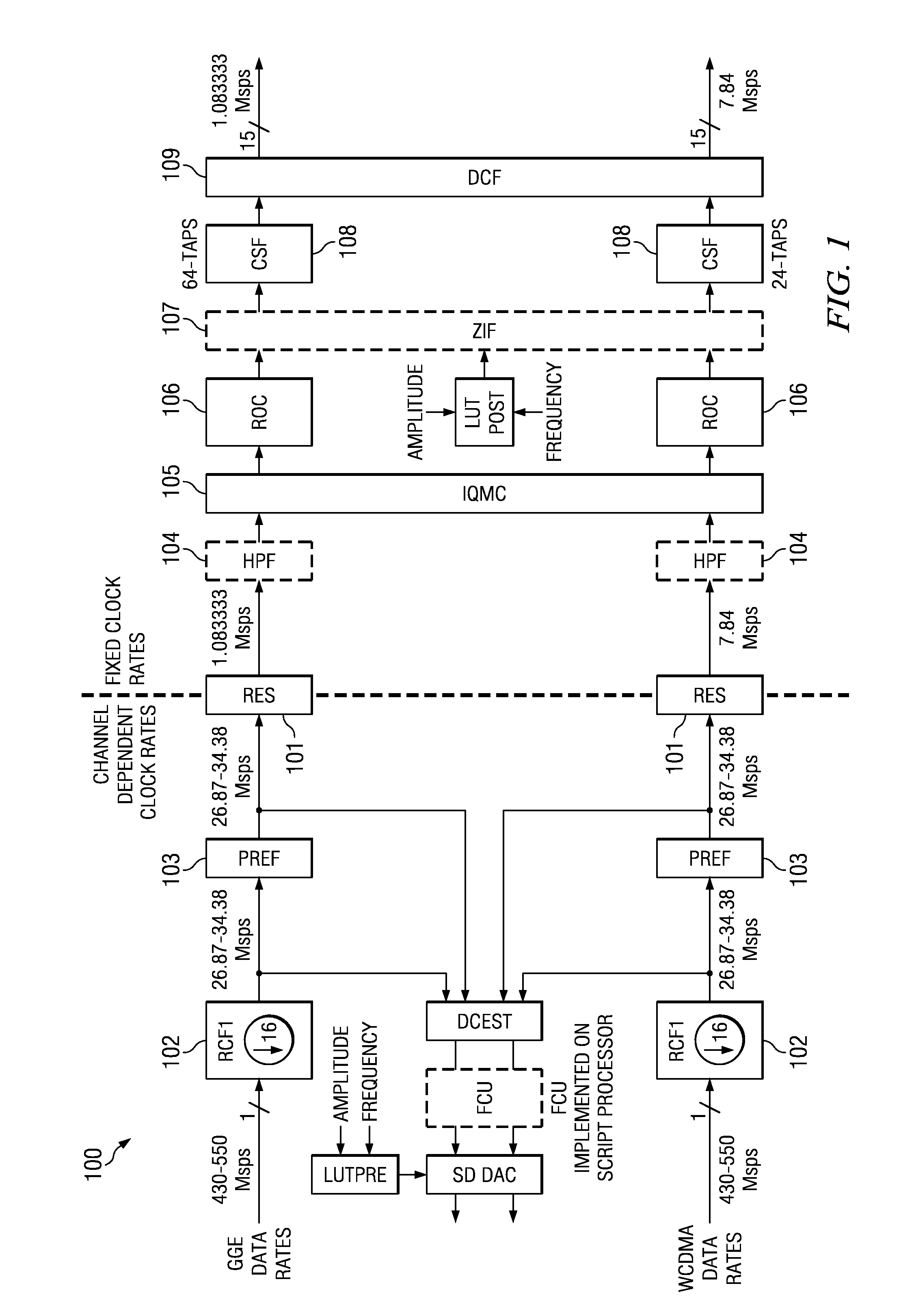

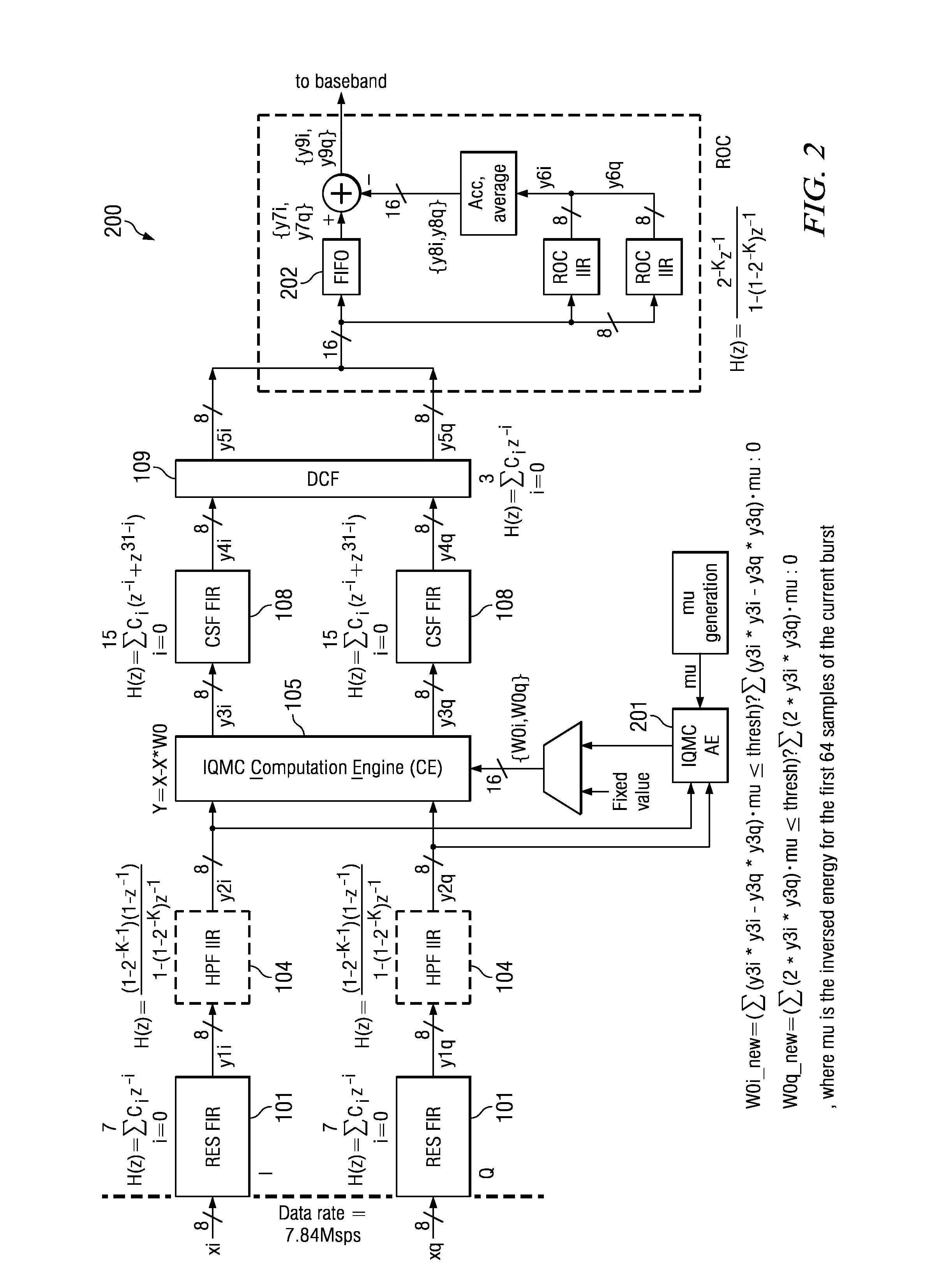

Application specific instruction set processor for digital radio processor receiving chain signal processing

ActiveUS8065506B2Increase chanceImprove customizationGeneral purpose stored program computerSpecial data processing applicationsComputer architectureDatapath

Owner:TEXAS INSTR INC

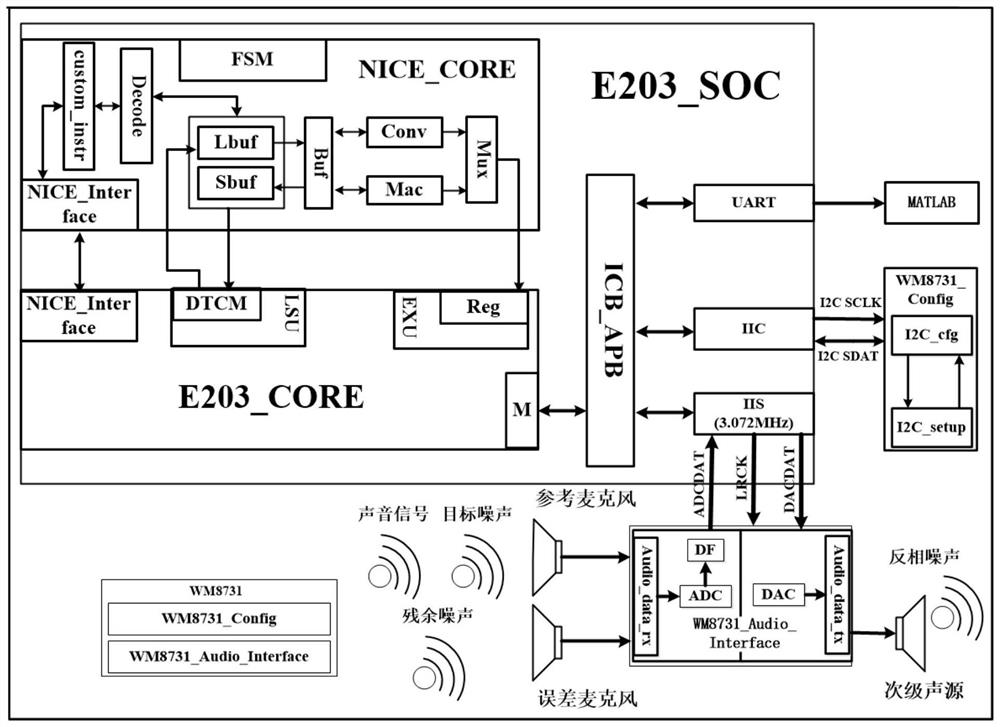

Audio noise reduction accelerator system and method based on RISC v custom instruction set expansion

PendingCN113851103AReduce wasteStrong configurabilitySound producing devicesComputer hardwareComputer architecture

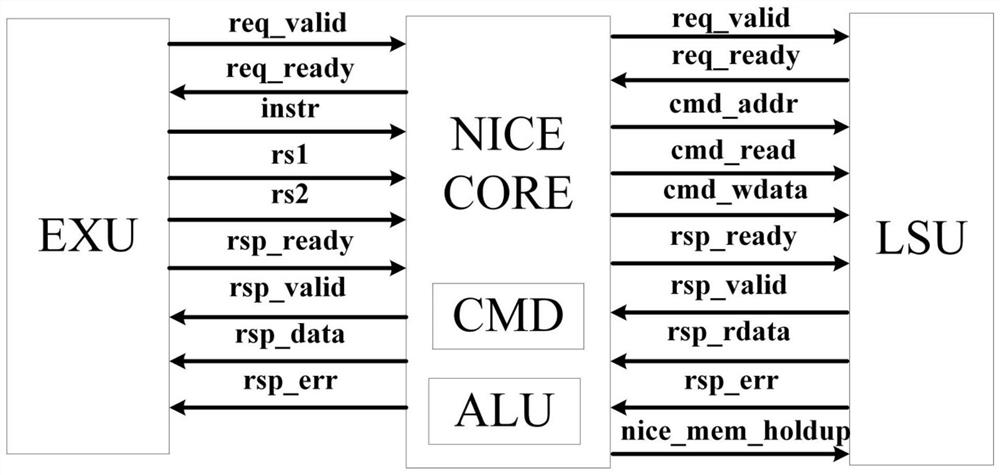

The invention discloses an audio noise reduction accelerator system and method based on RISC v custom instruction set expansion, and belongs to the technical field of integrated circuits. The system mainly comprises an E203_CORE, an NICE_CORE, a NICE_Interface, an E203_SOC, an audio coding and decoding WM8731 module, and an audio noise reduction FxLMS algorithm, wherein the E203_CORE is connected with the NICE_CORE through the NICE_Interface, the E203_CORE, the NICE_CORE and a related peripheral port form the E203_SOC together, the E203_SOC is connected with the audio coding and decoding WM8731 module, and the audio noise reduction FxLMS algorithm is downloaded into a core of the RISC v processor through software programming to run. Compared with a processor of an ARM instruction set architecture, the processor adopting an RISC v custom instruction set can accelerate a specific operation part in the audio noise reduction FxLMS algorithm; and the problems of area, power consumption, granularity and the like can be better optimized, and the flexibility and feasibility of the algorithm are improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Integrated circuit computing device and computing processing system

PendingCN111400986AImprove computing powerFlexible adjustmentCAD circuit designProcessing InstructionComputer architecture

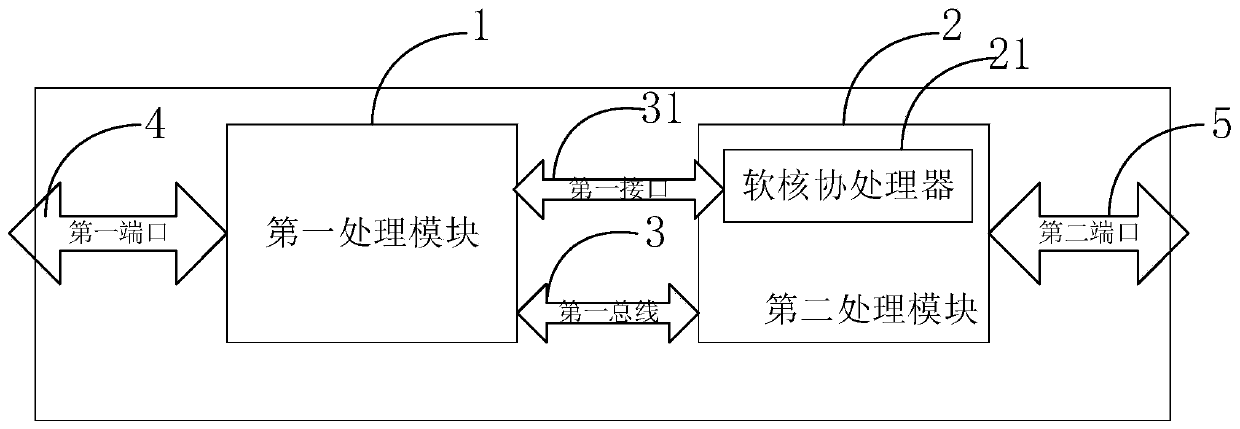

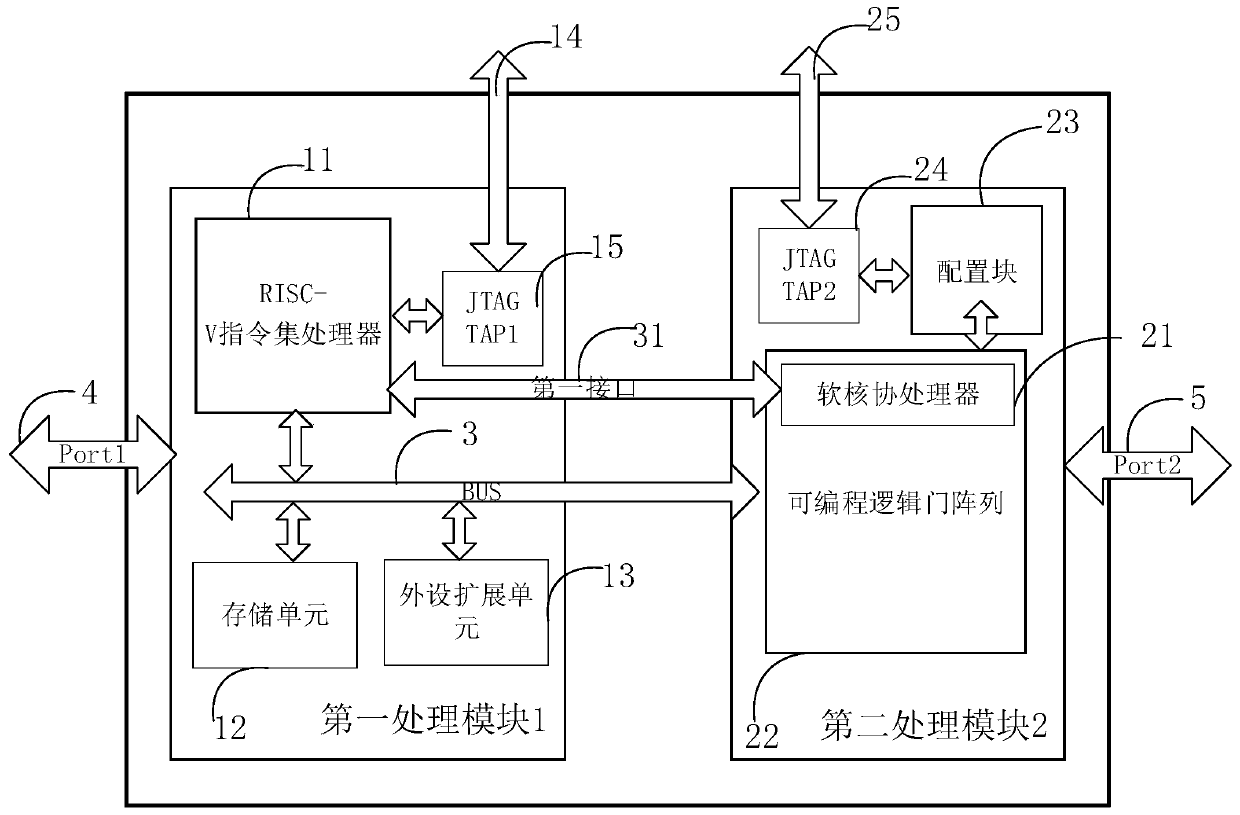

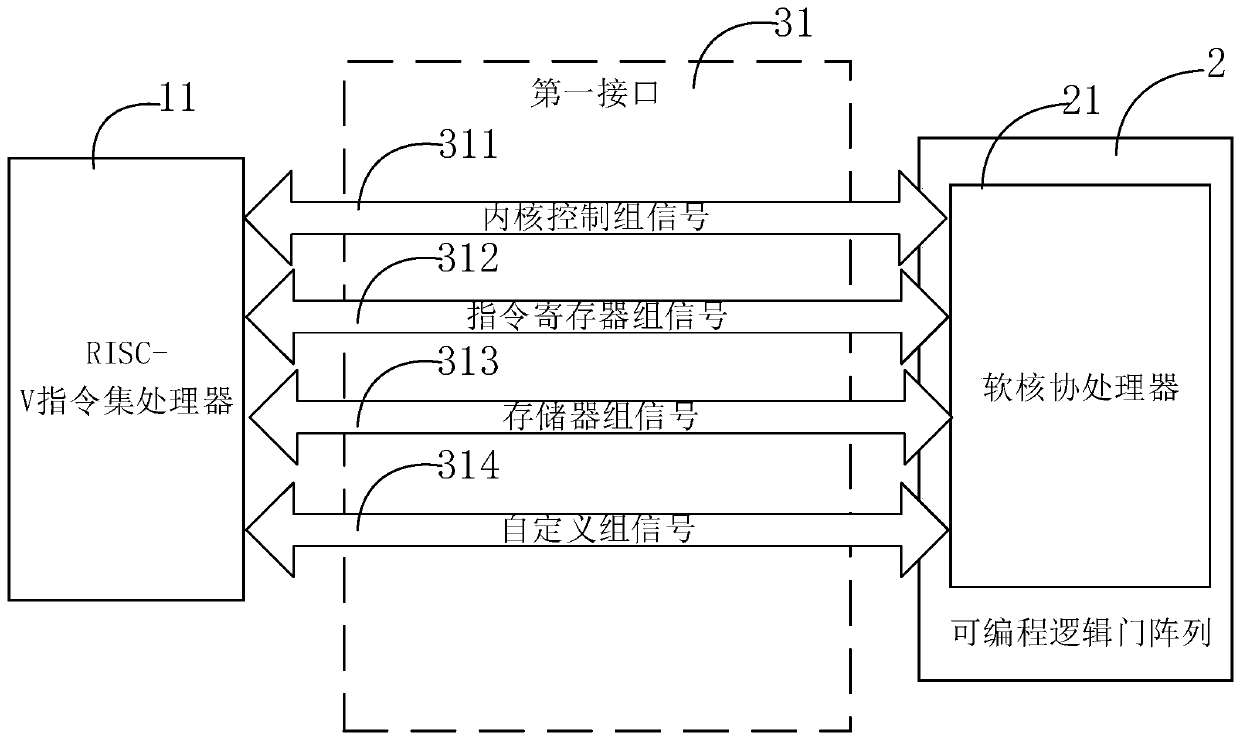

The present invention discloses an integrated circuit computing device, comprising: a first processing module for receiving and processing RISC-V instruction set instructions, the RISC-V instruction set instructions comprising a basic instruction, an extension instruction and a custom instruction; a second processing module which comprises a soft core coprocessor, wherein the soft core coprocessoris connected with the first processing module through a first interface and used for processing the custom instruction sent by the first processing module; a first bus is connected with the first processing module and the second processing module, wherein the first port is connected with the first processing module, and the second port is connected with the second processing module. According tothe invention, the RISC-V architecture hard core processor is embedded into the FPGA chip; a soft core coprocessor is designed at the programmable part of the FPGA chip, so that FPGA chip developers can flexibly adjust the processor core as required, the computing power of the FPGA chip is enhanced, and small equipment area, low power consumption and low manufacturing cost are ensured.

Owner:XIAN INTELLIGENCE SILICON TECH INC

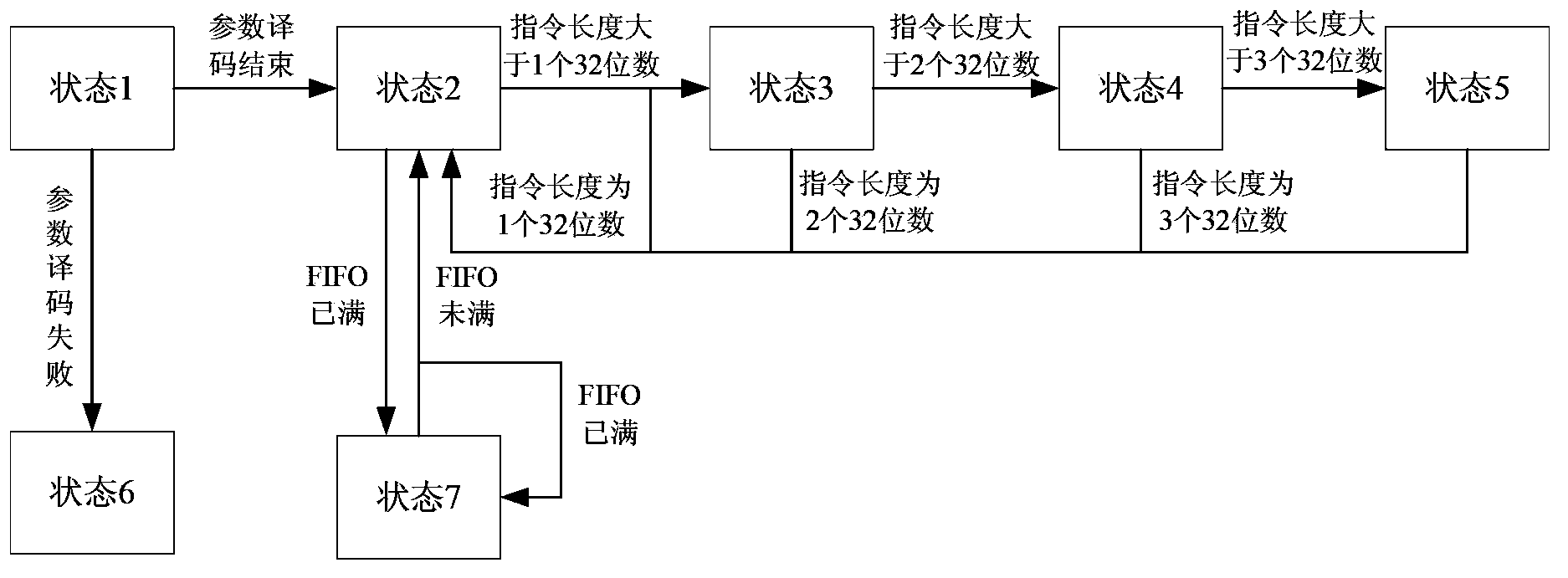

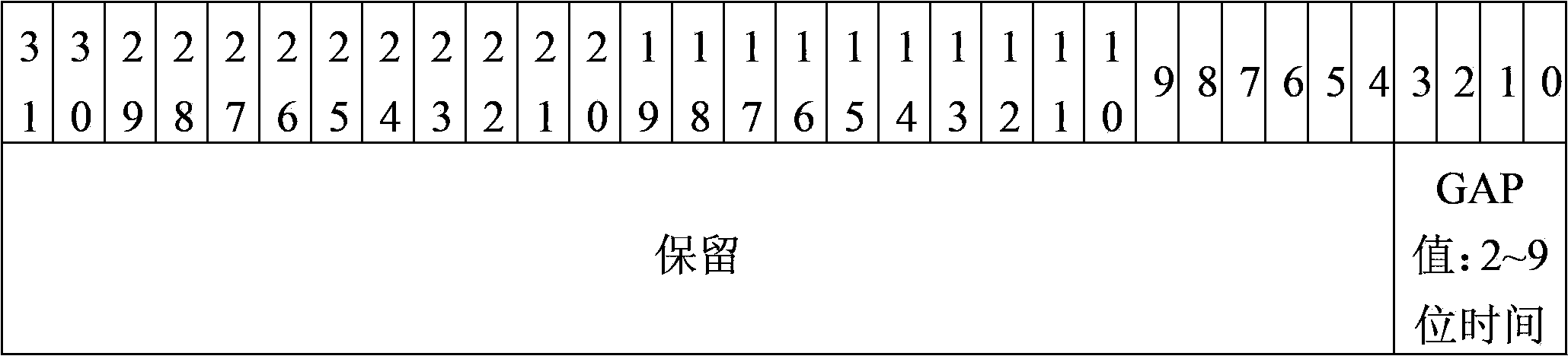

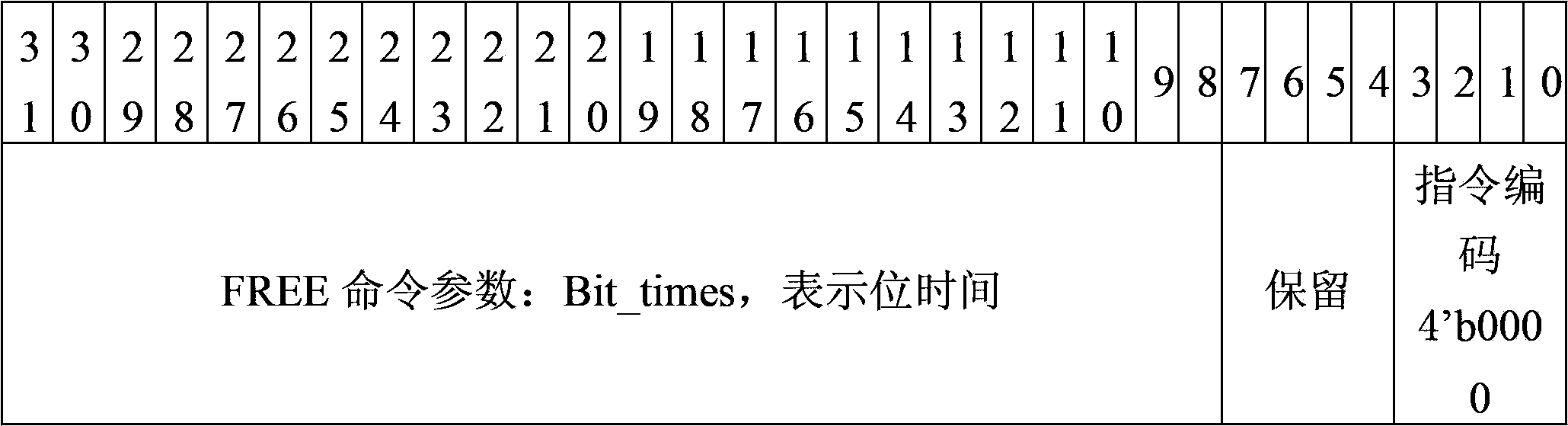

ARINC 659 protocol based instruction decoding method

ActiveCN103577154AImplement frame description language instruction decoding functionMachine execution arrangementsDecoding methodsStatic random-access memory

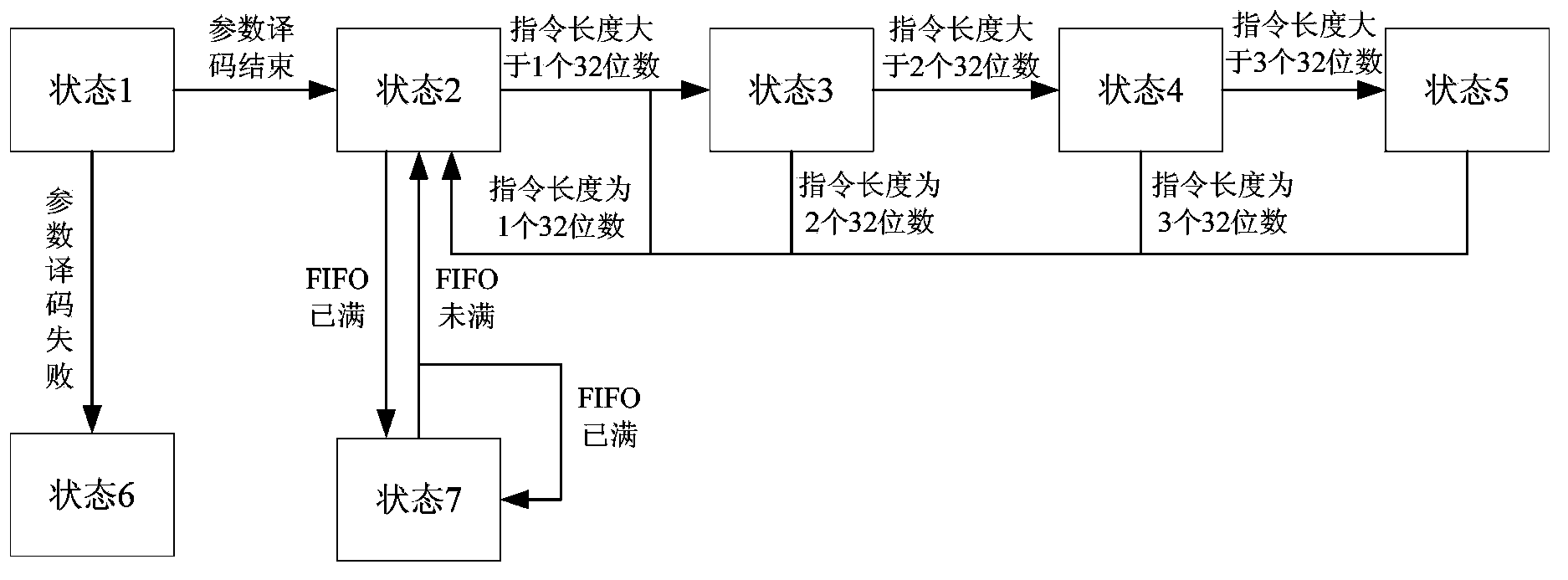

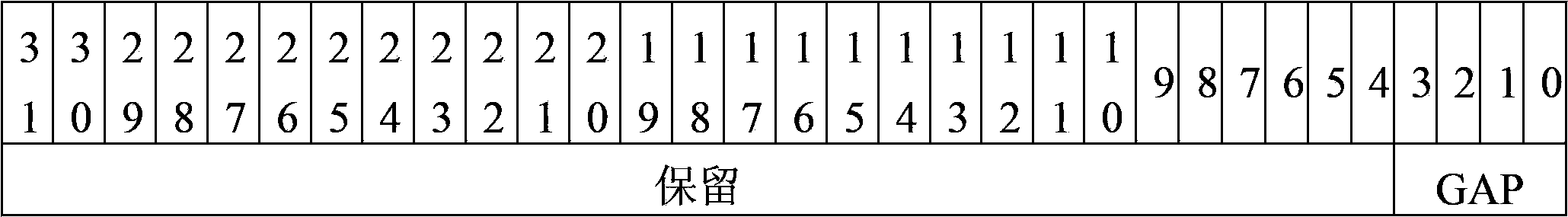

The invention relates to an ARINC 659 protocol based instruction decoding method. The method comprises 1) reading machine codes corresponding to system parameters successively from corresponding initial positions and fixed address space in a general static random access memory (SRAM), and verifying the system parameters required to be verified; continuing to read a next system parameter if verification is successful; assigning 0 to an address pointer value is verification is failed; conducting the step 2) when all the system parameters are verified; 2) determining the general synchronous FIFO state, and keeping the address pointer unchangeable if the general synchronous FIFO is full; conducting the step 3) if the general synchronous FIFO is not full; 3) decoding the machine codes of all instructions according to instruction types. According to the method, the problem of analysis of frame description language instructions by BIU on an ARINC 659 bus is effectively solved, and the method can be promoted to complete works like bus custom instruction set machine code definition, instruction decoding and decoding state indication.

Owner:西安翔腾微电子科技有限公司

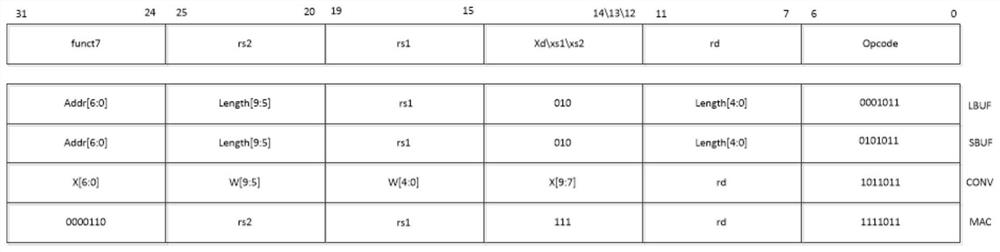

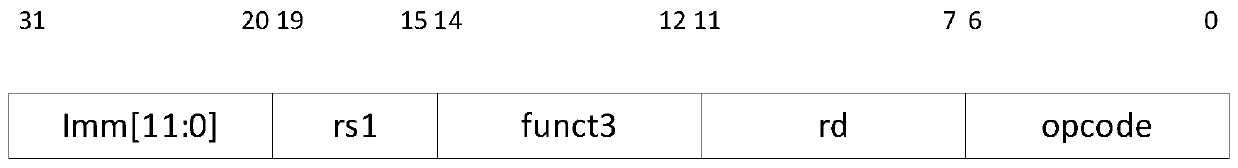

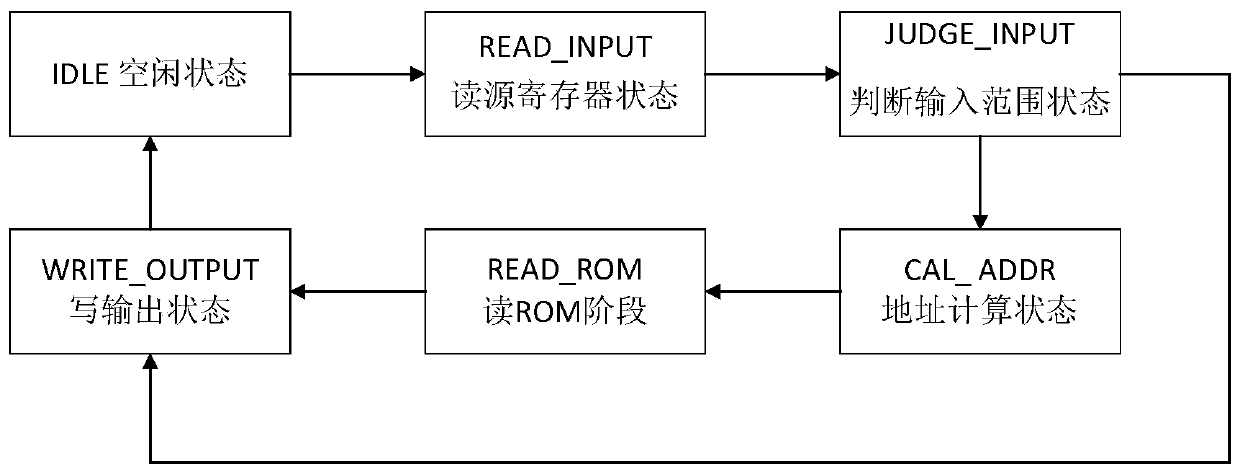

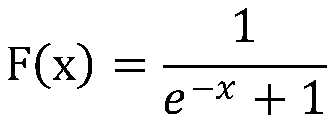

Character recognition method of convolutional neural network based on RISC-V

ActiveCN111507336AAccelerate inference operationsAchieve instruction-level accelerationNeural architecturesNeural learning methodsData setText recognition

The invention discloses a character recognition method of a convolutional neural network based on RISC-V. The method includes: firstly building a neural network training environment, and then designing a six-layer handwritten number recognition network based on an mnist data set; inputting a picture, performing training to set accuracy, and storing a weight and offset parameter file; setting a custom instruction type and format of the RISC-V instruction set, designing an instruction according to a reserved instruction coding space, and designing a specific hardware acceleration circuit according to the set instruction format and an SIGMOD function implementation method; importing a hardware acceleration circuit, a weight and a bias parameter file into the FPGA, building an RISC-V development environment, and completing the addition of a custom instruction; and inputting the picture, and identifying the numbers in the picture by using a hardware acceleration circuit. According to the invention, instruction-level acceleration of specific operation is realized, partial neural network reasoning operation is accelerated, and handwritten numbers in a picture can be quickly identified.

Owner:HANGZHOU DIANZI UNIV

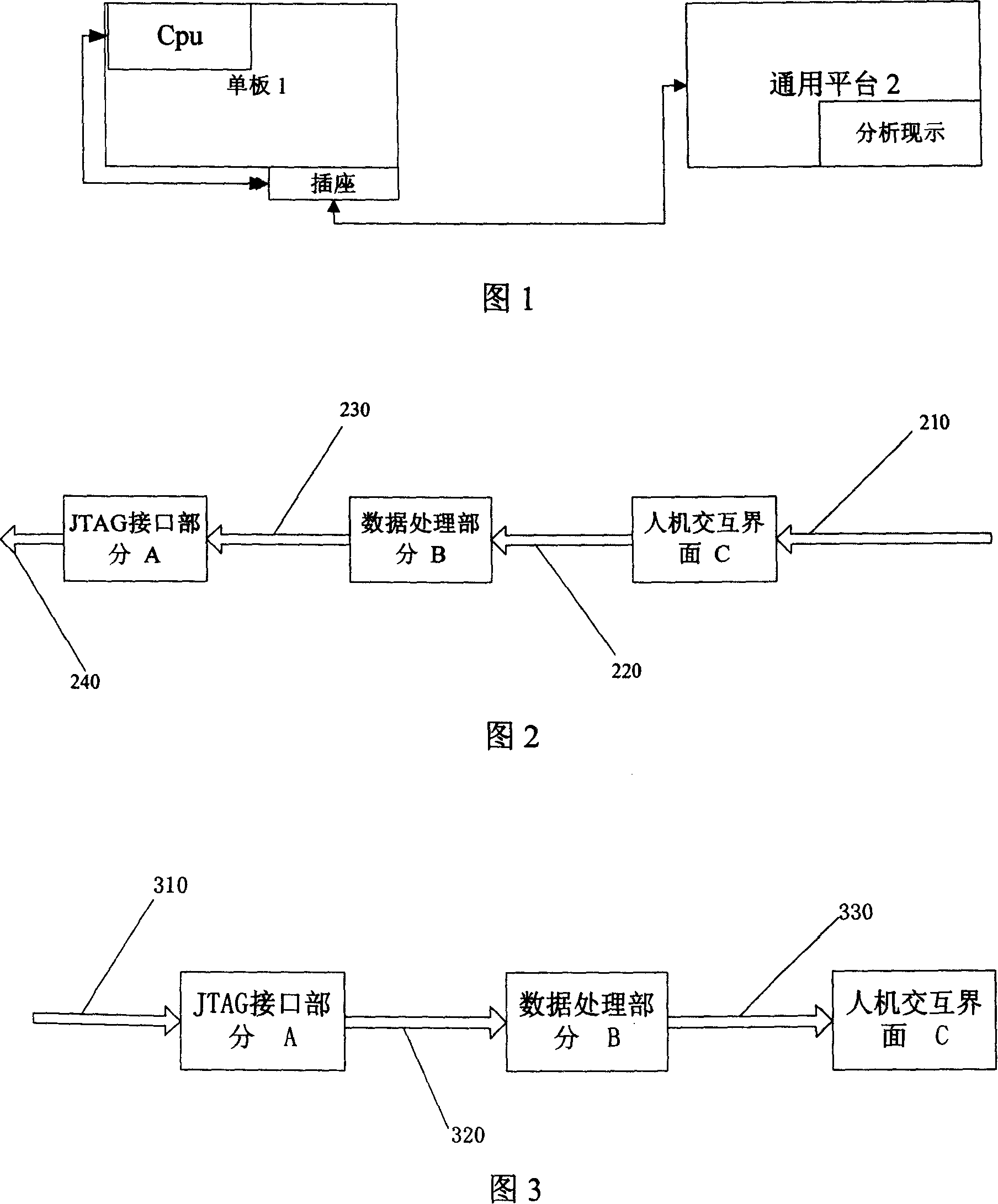

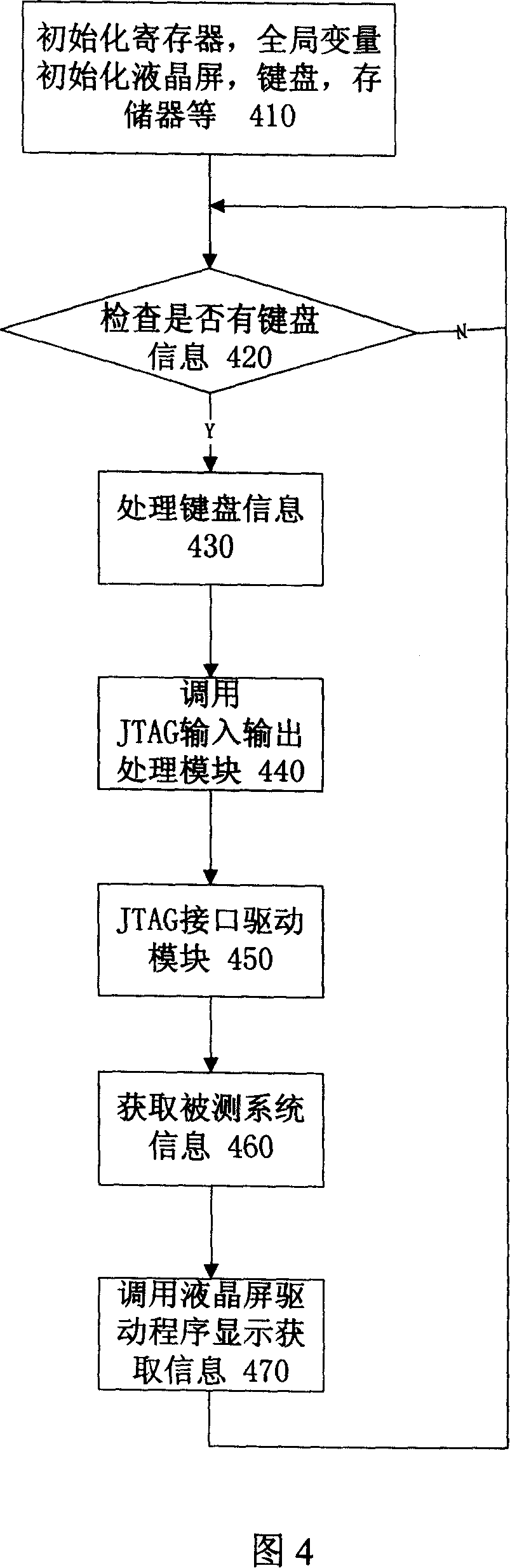

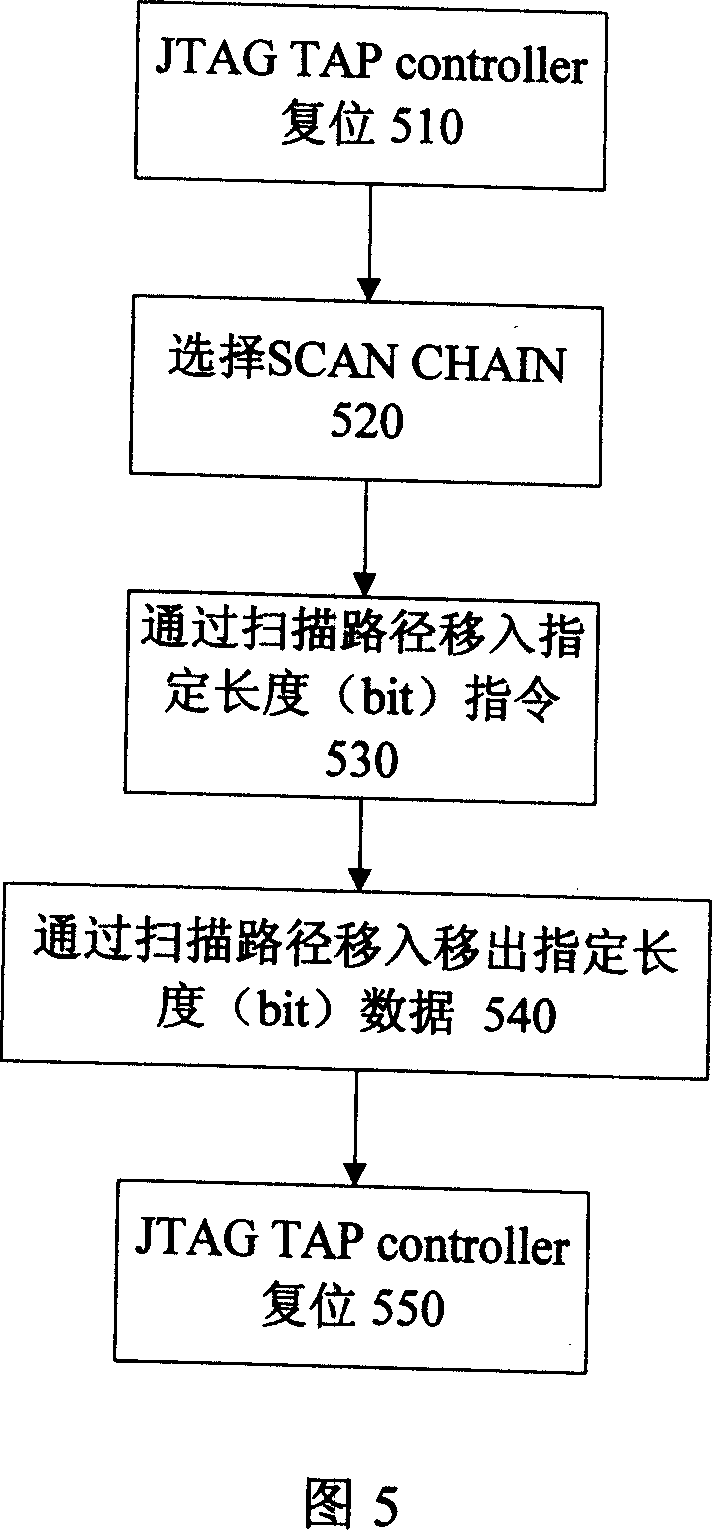

A general platform and method for system debugging and monitoring

InactiveCN101150450AMeet the needs of debugging and monitoring exceptionsDetecting faulty computer hardwareSoftware testing/debuggingCommunication interfaceAfter treatment

The invention relates to a universal platform for a system debugging monitor and a related method, in which, the universal platform (2) includes a JTAG processing host computer adopting JTAG interfaces; the method comprises the following steps: establishing mutual communications junction between the platform and target system chips through respective JTAG interfaces according to communications interface standards of JTAG; transmitting standard JTAG format protocol flows transformed by custom instruction with communications junction and having response of the target system (1) chips; reading standard JTAG format protocol flows transformed by chip debugging information and register state information of the target system with communications junction, and reducing the standard JTAG format protocol flows to computer-readable data for displaying and outputting after treatment. The universal platform and the method thereof, with JTAG standards, can provide a universal tool for different chips with JTAG interfaces to monitor and debug abnormal phenomenon, such as dead loop and memory leakage of the system or a single board under non-debugging conditions, thus satisfying the debugging and monitoring demands of the system or the single board under various environments including on-site situation.

Owner:ZTE CORP

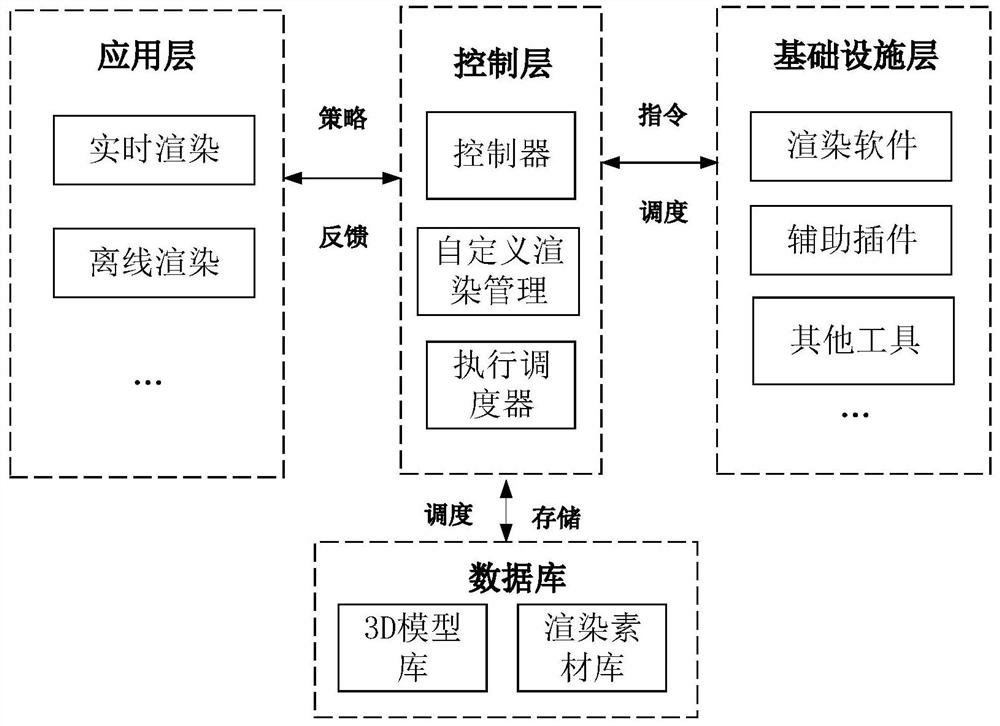

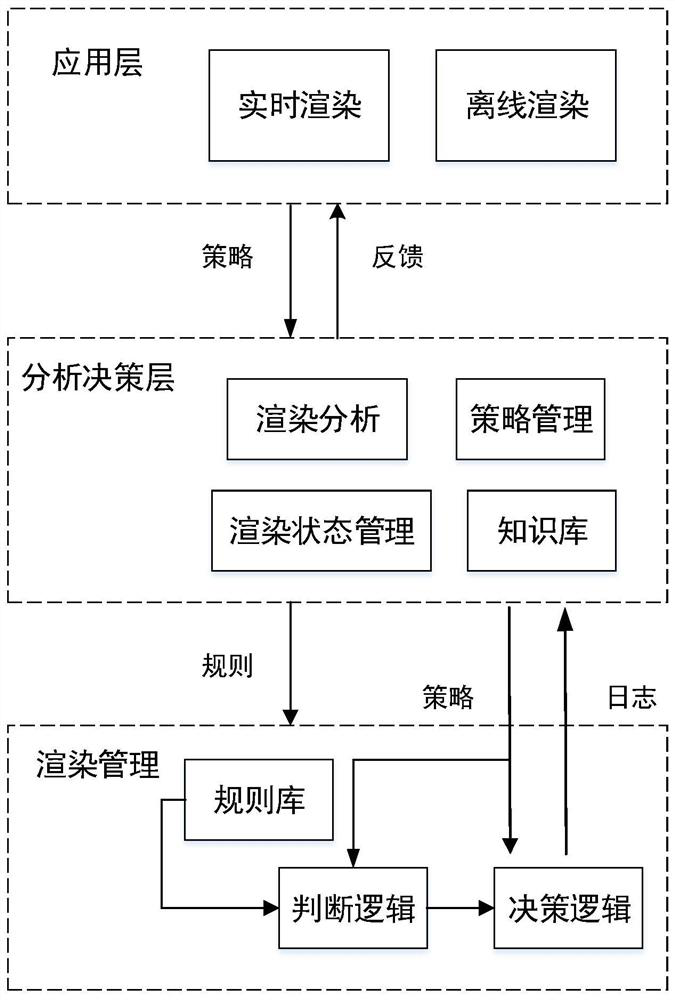

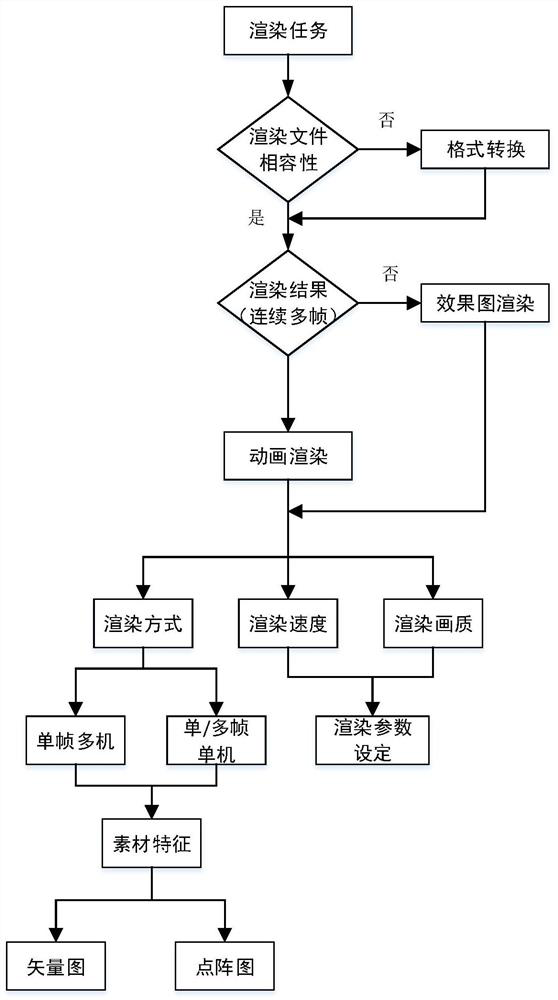

Cloud rendering system based on software definition

PendingCN112581578ALower control costsMeet needsProgram initiation/switchingResource allocationControl layerServer

The invention provides a cloud rendering system based on software definition. The system comprises an application layer, a control layer, an infrastructure layer and a data layer. According to the method, a rendering software resource control method is reconstructed, a corresponding function model is established, and a custom instruction system is provided and comprises an analysis instruction, ajudgment instruction, a resource scheduling instruction, an execution instruction and a communication instruction; and according to the software definition characteristics, the rendering process and the management process are modified, so that the method is more flexible. According to the cloud rendering system, centralization, control and execution are separated, the rendering resources, the access mode, the deployment mode and the implementation function of the rendering resources are decoupled and reconstructed, the functions of the system are optimized while the centralized resources are enhanced, the overall load is reduced, and the system can operate more efficiently and extensively; and the user can set the 3D rendering engine, the plug-in required to be used, the rendering server scale, the rendering cluster management software and the customized rendering environment by himself / herself, and the cost is controllable, so that the requirements of different users in various rendering scenes are met.

Owner:JIANGSU CUDATEC TECH CO LTD

ARINC 659 protocol based instruction decoding circuit implementation method

ActiveCN103577155AImplement frame description language instruction decoding functionMachine execution arrangementsComputer architectureStatic random-access memory

The invention relates to an ARINC 659 protocol based instruction decoding circuit implementation method. The method comprises 1) defining machine codes to different system parameters specified in the ARINC 659 protocol and storing the machine codes corresponding to the different system parameters in a register corresponding to the machine codes in bit wide; 2) encoding the instructions corresponding to instruction definitions specified in the ARINC 659 protocol; 3) storing the machine codes of all instructions by using a general static random access memory (SRAM); 4) decoding all instruction machine codes through a state machine; 5) storing all the decoded instruction machine codes in a general synchronous FIFO, the data bit wide of which is 256 bits. According to the method, the problem of analysis of frame description language instructions by BIU on an ARINC 659 bus is effectively solved, and the method can be promoted to complete works like bus custom instruction set machine code definition, instruction decoding.

Owner:西安翔腾微电子科技有限公司

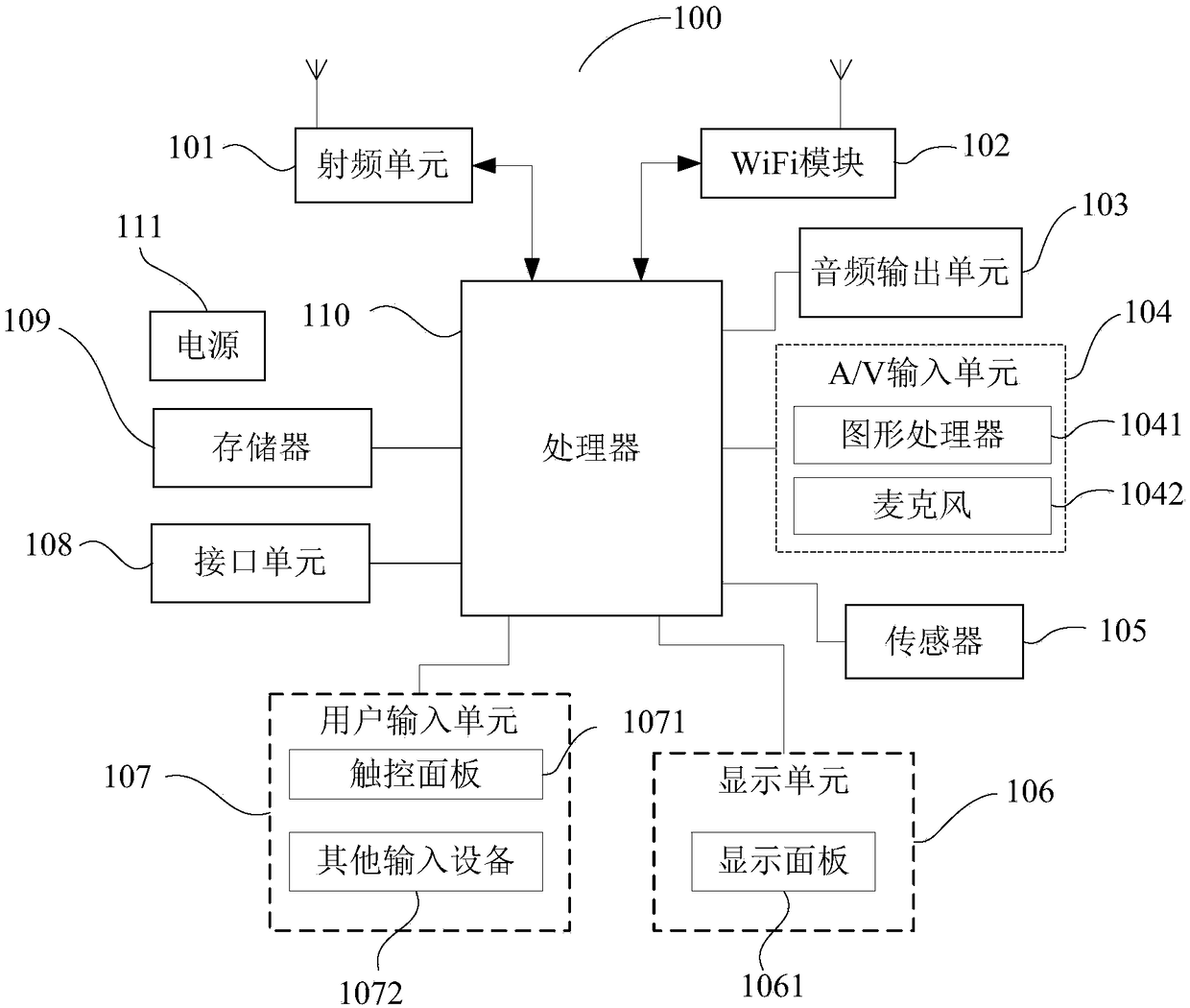

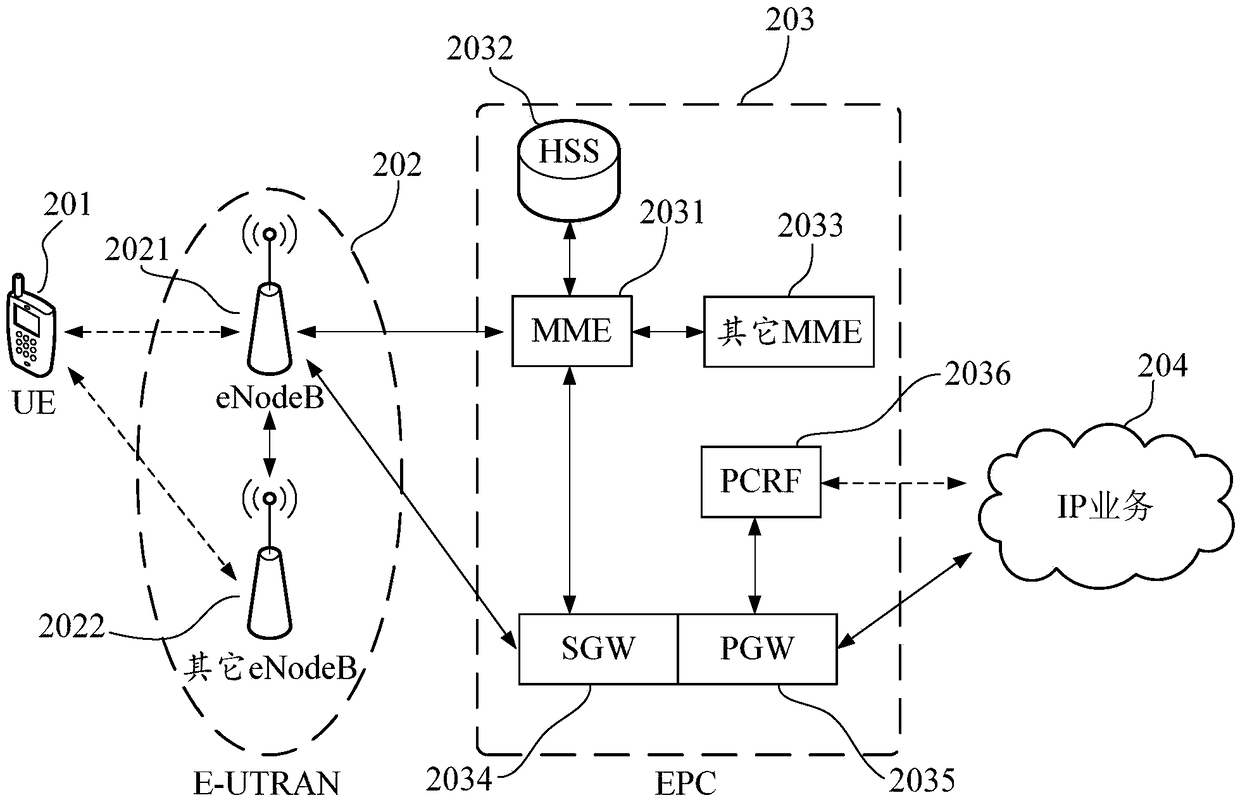

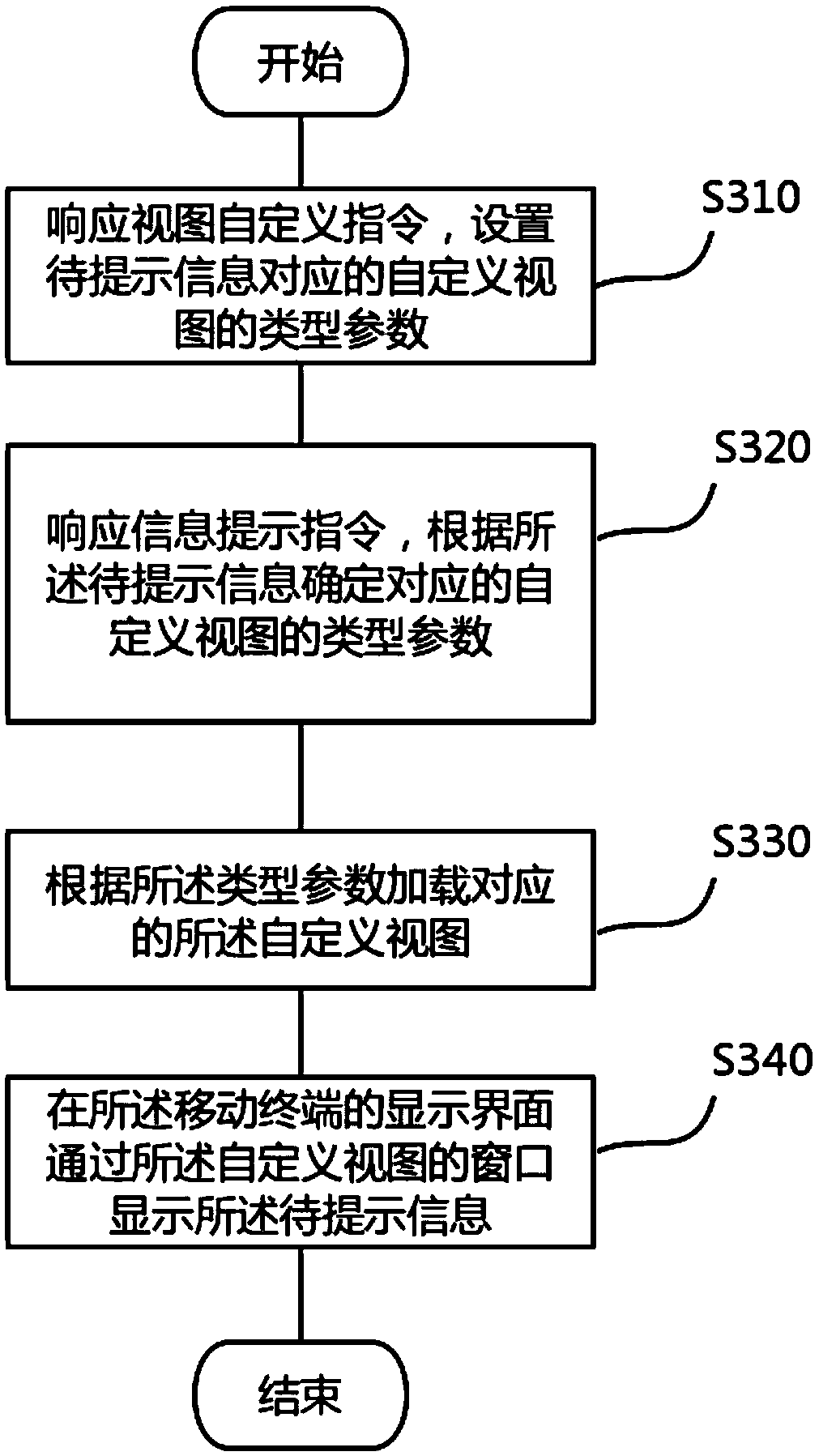

Information prompting method, mobile terminal and computer readable storage medium

ActiveCN109462696AAvoid interruptionSubstation equipmentExecution for user interfacesComputer terminalCustom instruction

The invention provides an information prompting method which is applied to a mobile terminal. The method comprises the following steps of setting type parameters of a custom view corresponding to information to be prompted in response to a view custom instruction; determining the type parameters of the corresponding custom view according to the information to be prompted in response to an information prompting instruction; loading the corresponding custom view according to the type parameters; and displaying the information to be prompted through a window of the custom view on a display interface of the mobile terminal. The invention further provides the mobile terminal and a computer readable storage medium. Through the information prompting method, the mobile terminal and the computer readable storage medium, which provided by the invention, a user can customize an information prompting way through the method, and a display level of the view for prompting the information, a display duration and a relation between a foreground window and a focus window are defined, so that the view used for displaying messages can be effectively prevented from being interrupted by other applications, prompts and other contents.

Owner:NUBIA TECHNOLOGY CO LTD

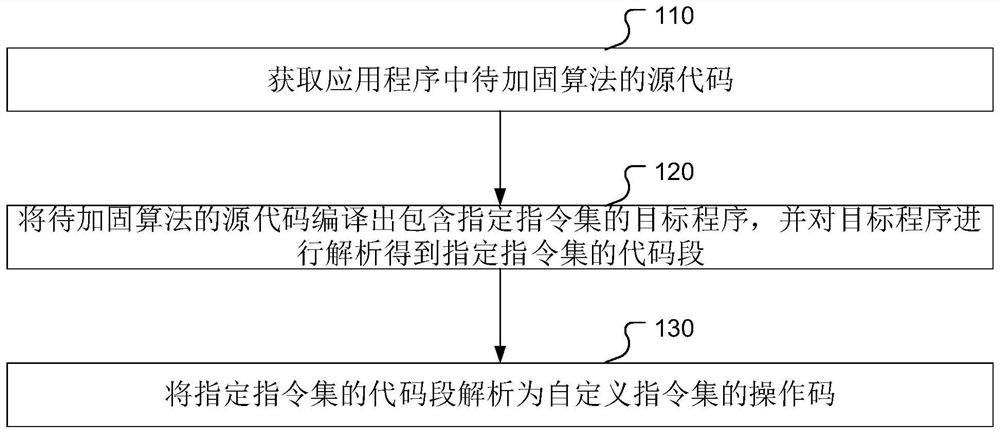

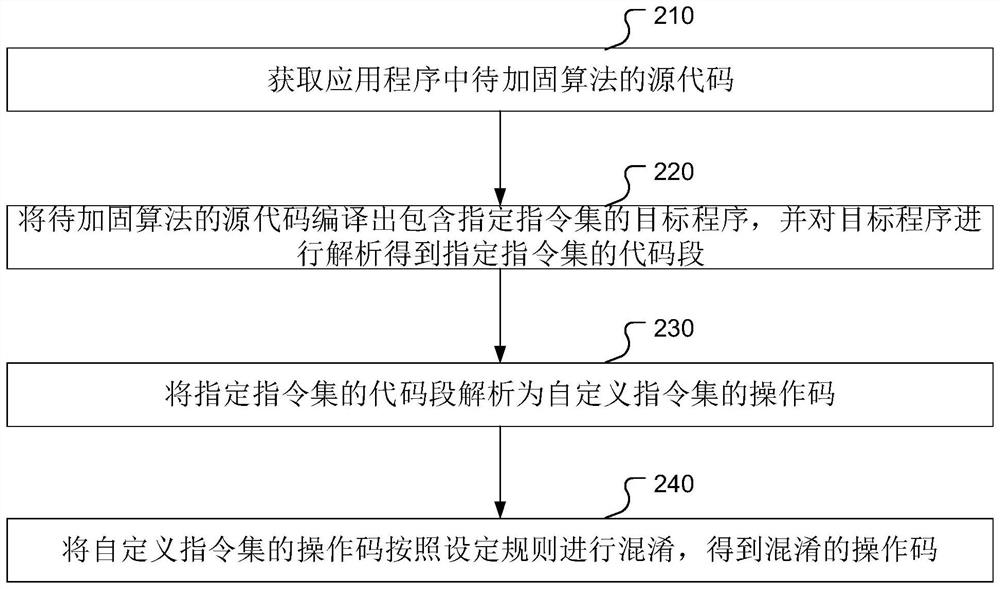

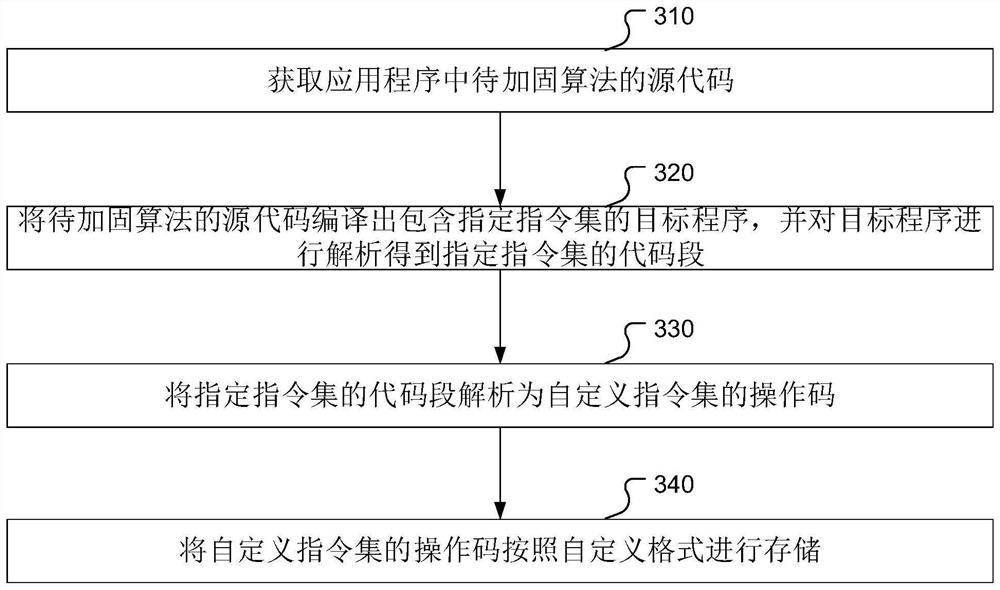

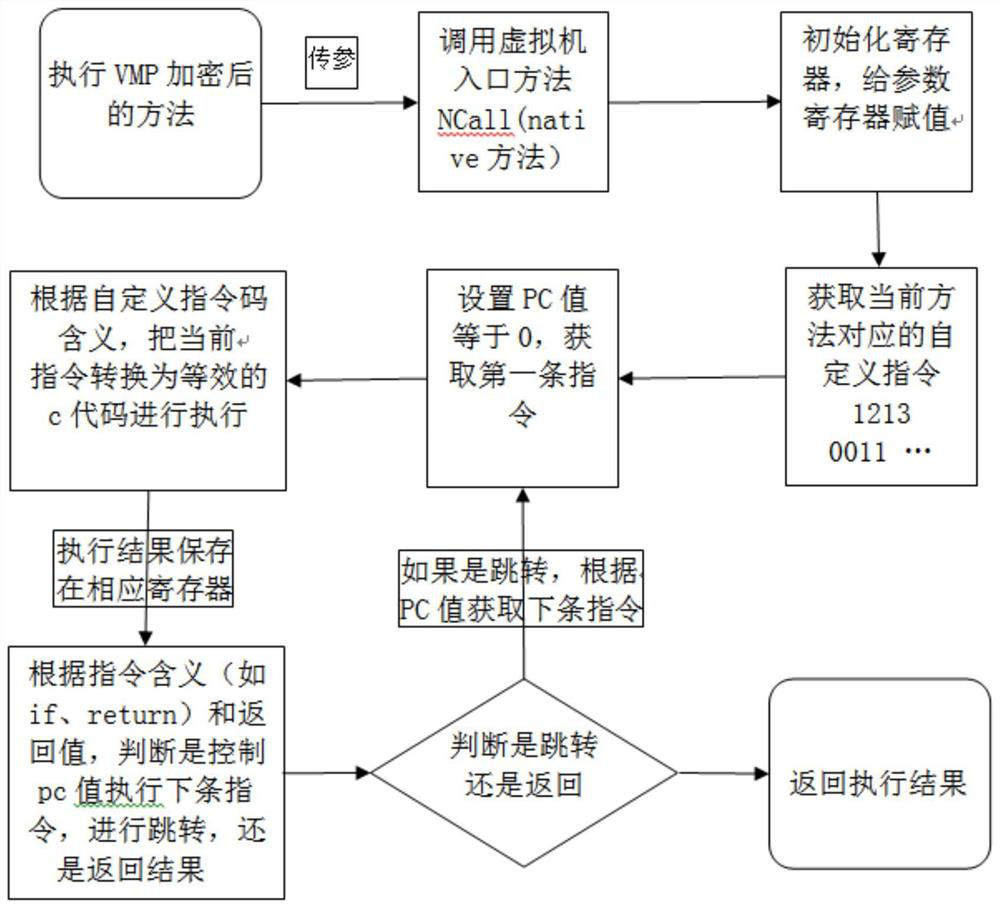

Application program reinforcing method, system and equipment and storage medium

PendingCN114416097AImprove reinforcementAvoid analysisSoftware simulation/interpretation/emulationCode compilationApplication procedureSource code

The invention provides an application program reinforcing method, system and device and a storage medium, and the method comprises the steps: obtaining a source code of a to-be-reinforced algorithm in an application program, compiling the source code of the to-be-reinforced algorithm into a target program containing a specified instruction set, and analyzing the target program to obtain a code segment of the specified instruction set, and analyzing the code segment of the specified instruction set into an operation code of the custom instruction set. According to the method, the machine code of the to-be-reinforced algorithm is analyzed into the operation code of the user-defined instruction set, and the special user-defined virtual machine execution engine is matched for explanatory execution. The instruction set of the operation code is self-defined, and a reverse person is very difficult to know all the mapping rules, so that the scheme can bring a good application program reinforcement effect.

Owner:上海顺途科技有限公司

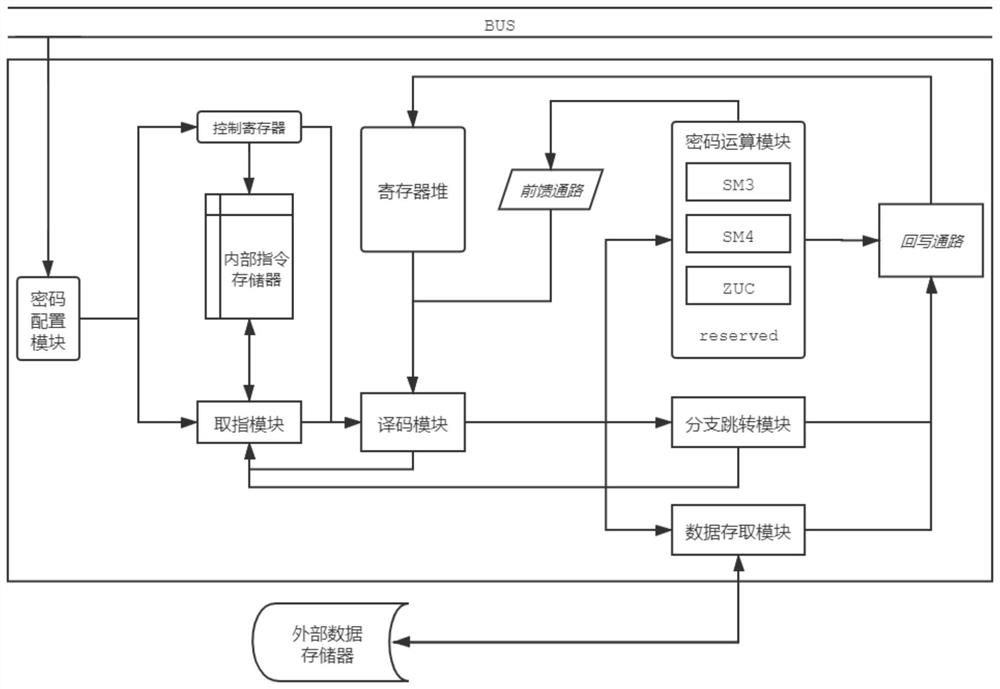

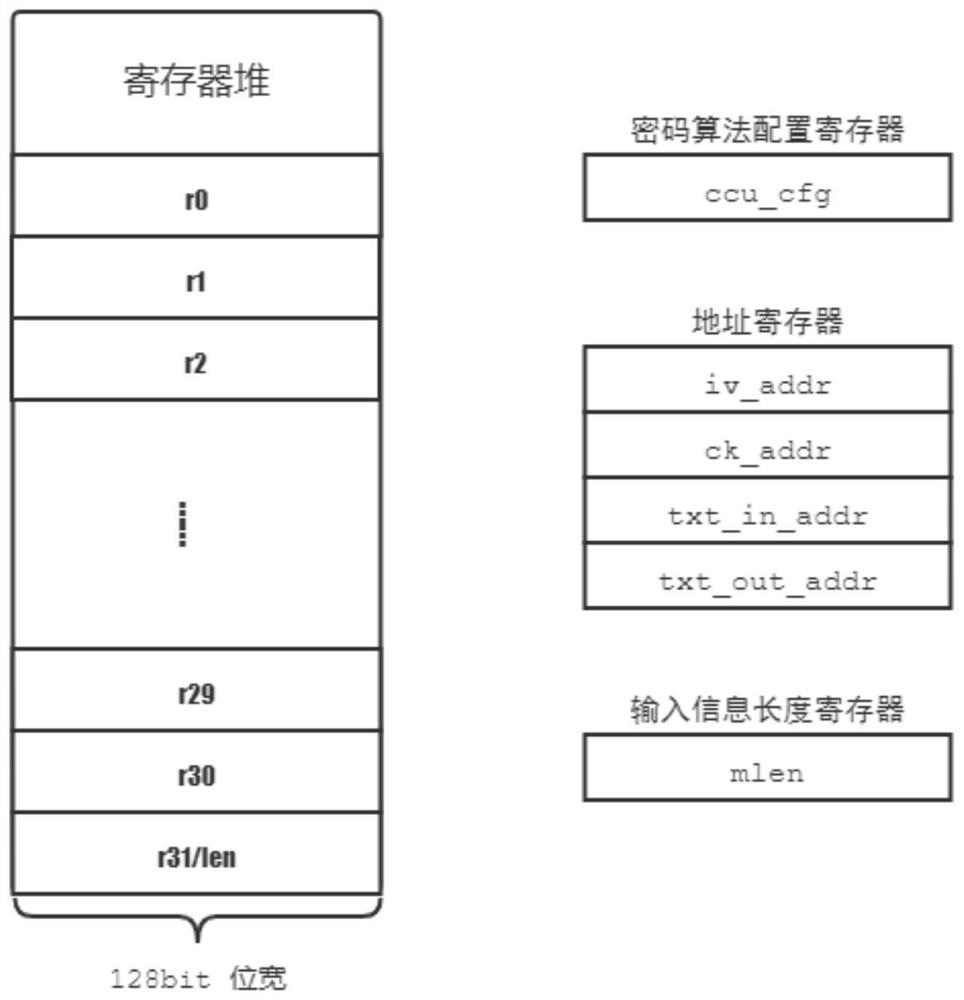

Instruction-driven commercial password special processor system

PendingCN112256633AFlexible supportArchitecture with single central processing unitMachine execution arrangementsInstruction memoryComputer architecture

According to the instruction-driven commercial password special processor system; a processor enters a main assembly line after receiving password configuration information, and an instruction fetching module starts to fetch an instruction from an internal instruction memory and sends the instruction to a decoding module; the decoding module carries out decoding according to a coding format of a customized instruction set, maintains a register file with variable length and bit width and sends a selection signal, an operation code and an operand to each special execution module facing encryption and decryption, and the data access module reads data from off-chip storage according to the grouping length and writes in an output result; the cryptographic operation module processes data in sequence according to the instruction decoding result and feeds forward and writes back an intermediate result, and the branch skip module judges to enter, continue or end iterative loop according to conditions. The invention is oriented to encryption and decryption algorithms, drives a special execution module through an instruction, provides a reasonable intermediate data scheme, can additionally add an execution unit, and flexibly supports more encryption and decryption algorithms.

Owner:ZHEJIANG UNIV

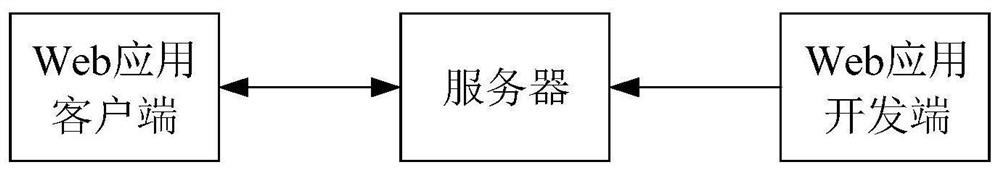

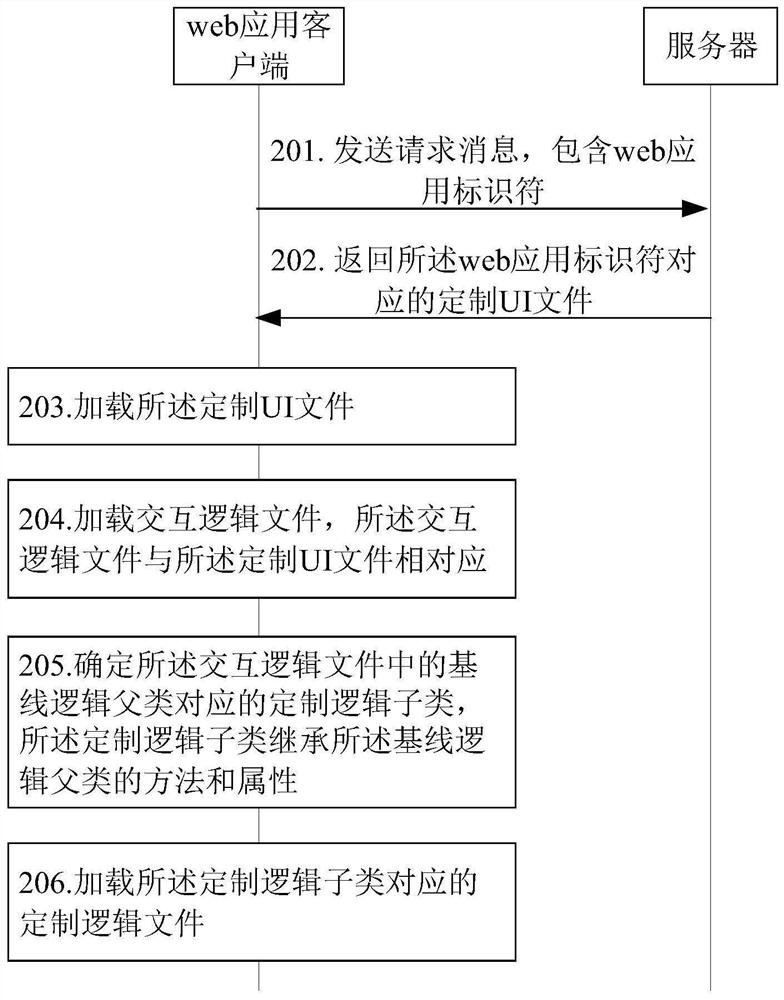

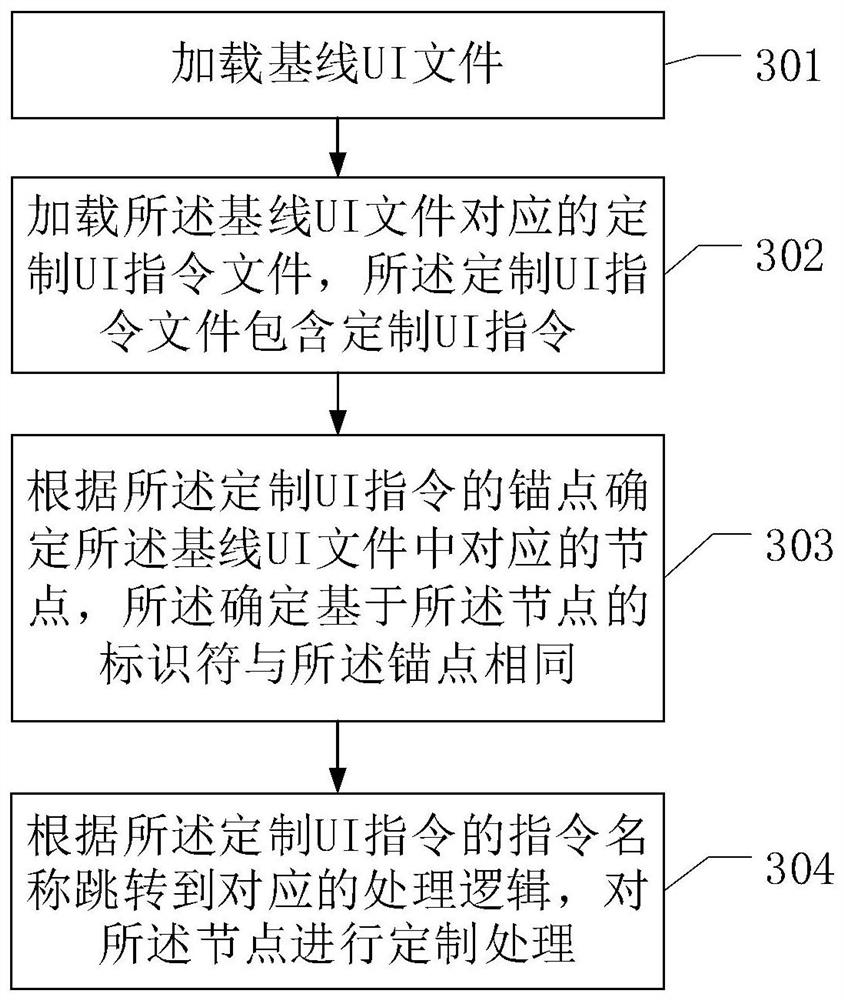

Web application customization method, related device and system

PendingCN111666074AImprove application development efficiencyAvoid duplication of developmentVersion controlSoftware reuseWeb applicationSoftware engineering

The embodiment of the invention discloses a web application customization method, a related device and a system. The method comprises the following steps: describing how to customize a user interfaceof a baseline version by using a customized UI instruction file, and preprocessing the baseline UI file according to the customized UI instruction file to generate a customized UI file so as to customize the display of the user interface; an object-oriented class inheritance method is adopted, and logic processing customization is achieved by dynamically loading an interaction logic file and a customization logic file. According to the method, the web front-end interface can also be put into the baseline version, and the web application development efficiency is improved. In addition, separation of the baseline and customization is achieved, it is guaranteed that smooth upgrading of the customized version can be achieved when the baseline version is upgraded, and the customization cost ofweb application development is reduced.

Owner:HUAWEI TECH CO LTD

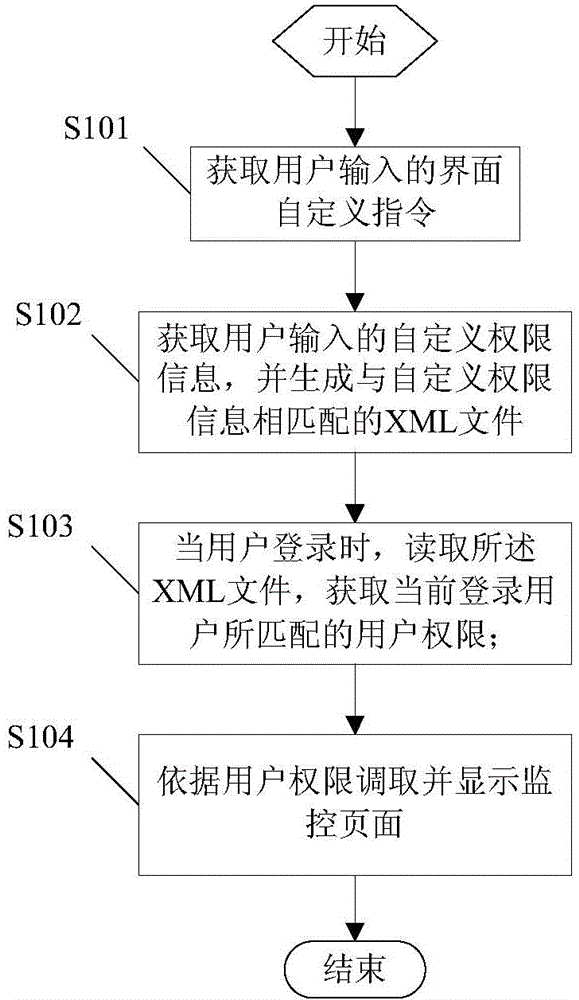

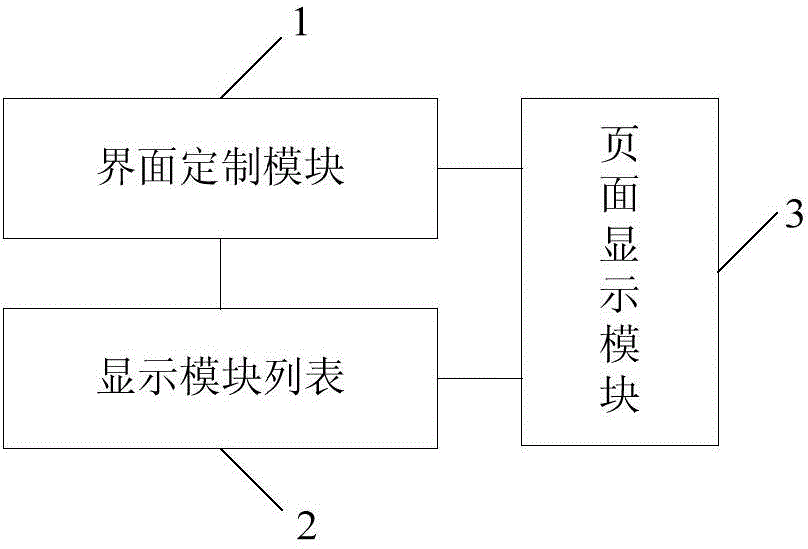

Frequency converter monitoring method and frequency converter monitoring system

InactiveCN104572130AEasy to operateImprove securitySpecific program execution arrangementsFrequency changerUser Privilege

The invention discloses a frequency converter monitoring method. The frequency converter monitoring method disclosed by the invention comprises the steps of obtaining an interface custom instruction input by a user; obtaining custom authority information input by the user, and generating an XML file matched with the custom authority information; reading the XML file when the user logs in so as to obtain user authorization matched with the current login user; and transferring and displaying a monitoring page according to the user authorization. According to the invention, monitoring page information of different users can be customized in a certain range only in need of inputting the custom authority information required by the user; the method can be operated conveniently; furthermore, according to different user levels, different authorities are opened to users in different levels, and thus, the safety of a frequency converter monitoring system is improved.

Owner:沈阳远大科技电工有限公司 +1

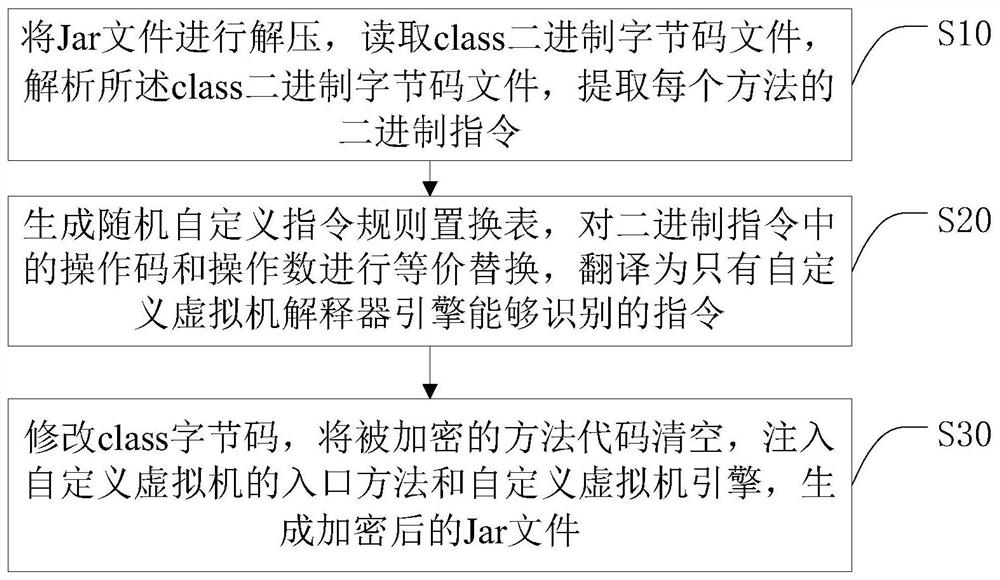

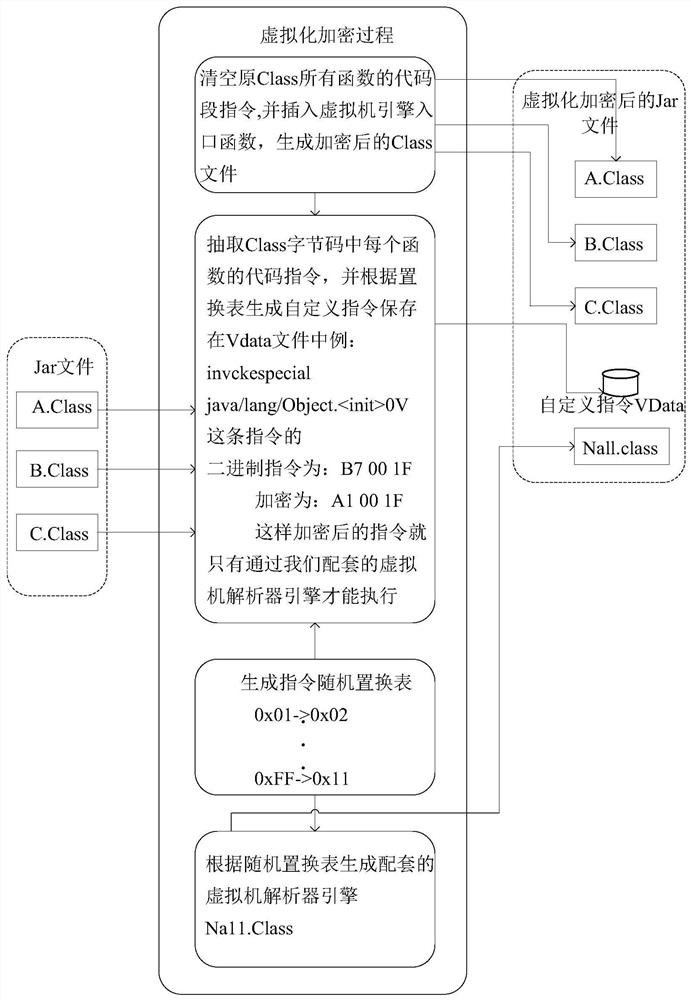

Virtualization protection method of Jar file, terminal and storage medium

PendingCN112052433AHigh strengthPrevent location analysisDigital data protectionProgram/content distribution protectionEngineeringModes

The invention discloses a virtualization protection method of a Jar file, a terminal and a storage medium. The method comprises the following steps: decompressing the Jar file, reading a class binarybyte code file, analyzing the class binary byte code file, and extracting a binary instruction of each method; generating a random custom instruction rule replacement table, performing equivalent replacement on an operand and an operand in the binary instruction, and translating the binary instruction into an instruction which can only be identified by a custom virtual machine interpreter engine;and modifying a class byte code, emptying an encrypted method code, injecting an emptied method code into an entry method of the custom virtual machine and a custom virtual machine engine, and generating an encrypted Jar file. In the encryption process, the Jar package is input for reinforcement protection, the Jar package is still downloaded after reinforcement, and the calling and using modes ofthe Jar package are not changed, so that the encrypted code cannot be decompiled, and the security is higher.

Owner:北京智游网安科技有限公司

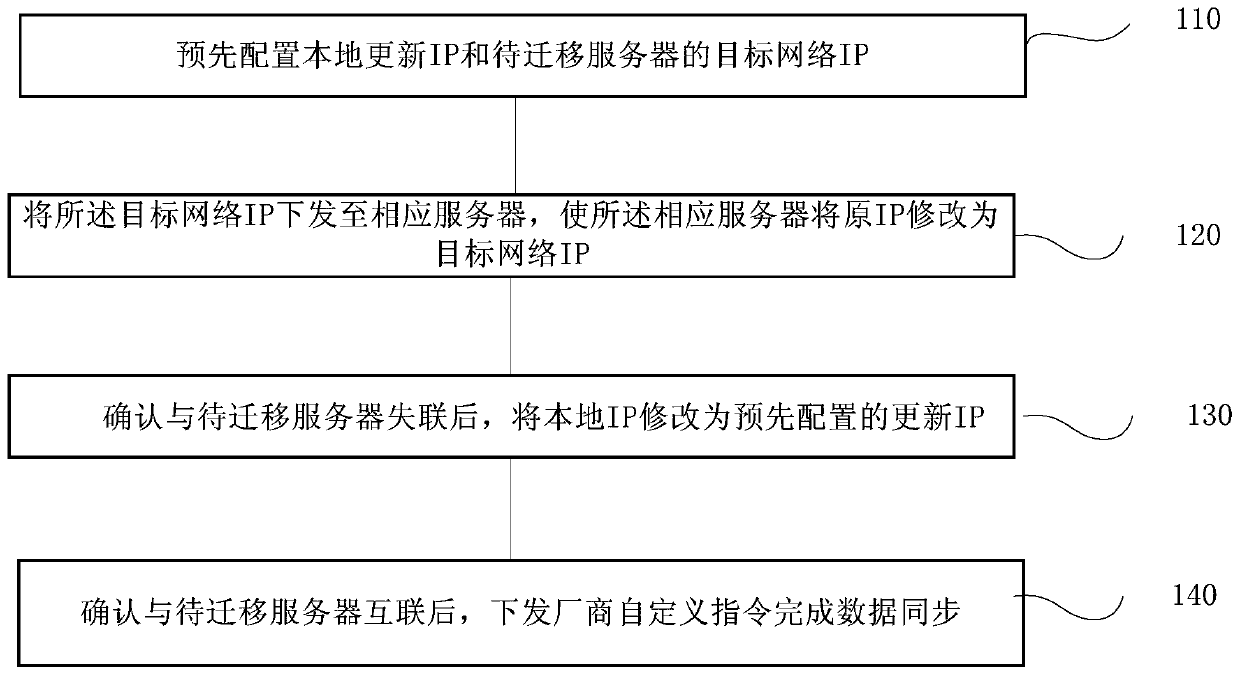

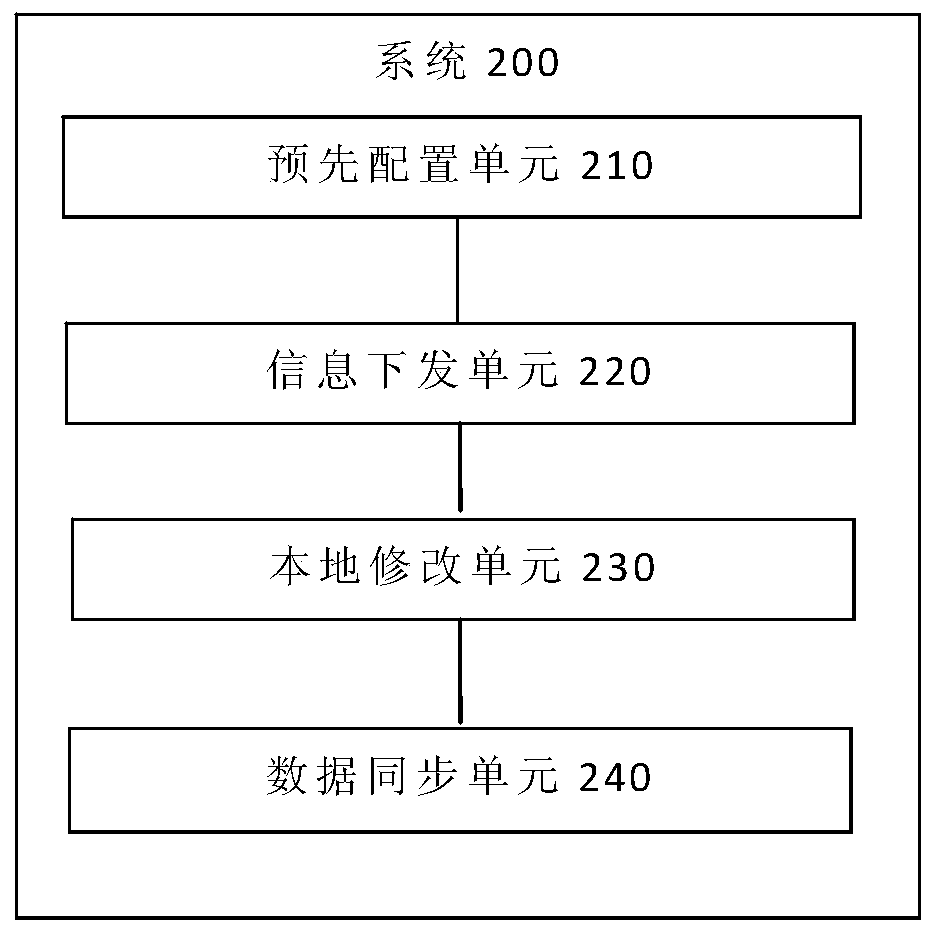

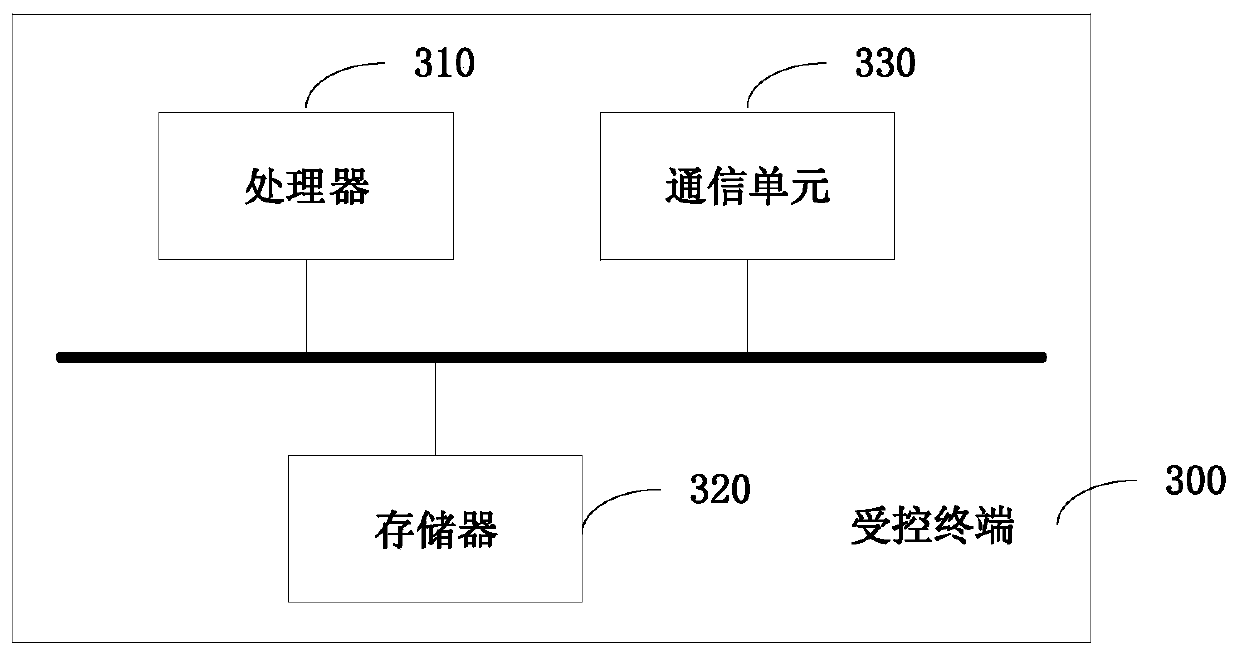

Cloud platform server network migration method and system, terminal and storage medium

ActiveCN110401729AImprove usabilityHigh degree of automationTransmissionComplete dataData synchronization

The invention provides a cloud platform server network migration method and system, a terminal and a storage medium. The method comprises the steps of pre-configuring a local update IP and a target network IP of a to-be-migrated server; issuing the target network IP to a corresponding server, so that the corresponding server modifies the original IP into the target network IP; modifying the localIP into a pre-configured update IP after confirming that the local IP is not in communication with the server to be migrated; and after it is confirmed that the to-be-migrated server is interconnected, issuing a manufacturer custom instruction to complete data synchronization. According to the invention, combining the server life cycle sensing assembly, the network environment migration requirement of the whole set of environment is met, manual background intervention is not needed. After environment physical layer debugging is passed, management software is directly operated, connection fromthe client side to the manager side is automatically completed, data is automatically synchronized, the deployment threshold is reduced, cost is saved, and product competitiveness is improved.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

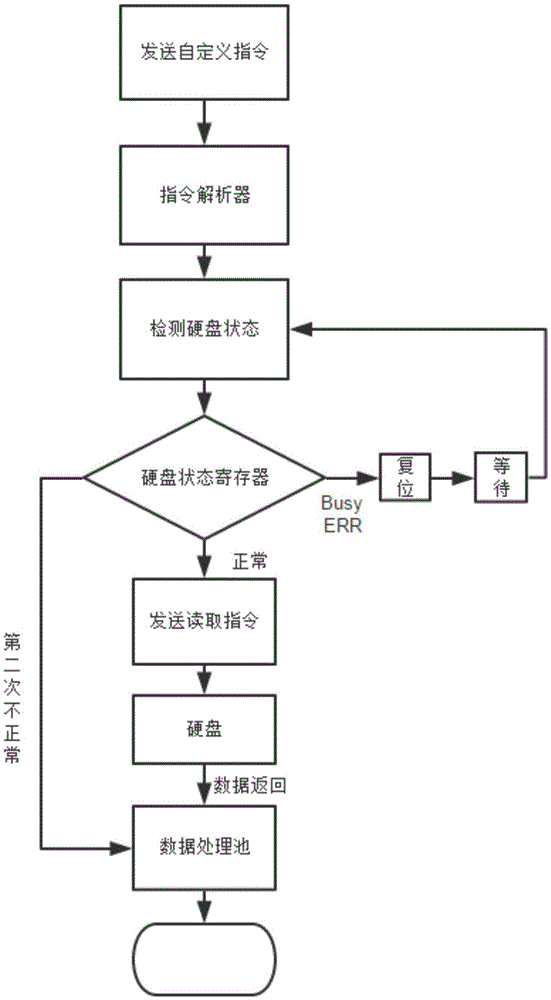

Method for carrying out defect isolation during connection of defect hard disk and PC (Personal Computer) side

ActiveCN105589665AEffective isolationPrevent crashInput/output to record carriersOperational systemData information

The invention discloses a method for carrying out isolation during the connection of a defect hard disk and a PC (Personal Computer) side, and belongs to the field of hard disk data recovery. The method comprises the following steps: 001: the PC side sends a custom instruction which is obtained in a way that an original instruction is changed; and 002: the changed custom instruction is received and analyzed to be reduced to the original instruction. When equipment is connected with a PC system, the equipment can not directly access any data information of storage equipment and must be combined with a corresponding software system to transfer and interact with virtual protection to finish data interaction on the hard disk. The method adopts a defect isolation technology to effectively isolate the hard disk with defects from the PC, and an operating system can be prevented from loading the startup code of the defect hard disk so as to avoid a phenomenon that a PC upper-level system is crashed since the PC system loads the startup code of the hard disk.

Owner:XLY SALVATIONDATA TECHNOLOGY INC