Chip test system and test method

A test system and chip technology, applied in the direction of static memory, instruments, etc., can solve the problems of small number of chip tests, high test costs, and small number of test machines, to achieve efficient parallel test capabilities and solve test costs High, flexible and adjustable effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention is described below based on examples, but the present invention is not limited to these examples. In the following detailed description of the invention, some specific details are set forth in detail. The present invention can be fully understood by those skilled in the art without the description of these detailed parts. In order to avoid obscuring the essence of the present invention, well-known methods, procedures, and flow charts are not described in detail. Additionally, the drawings are not necessarily drawn to scale.

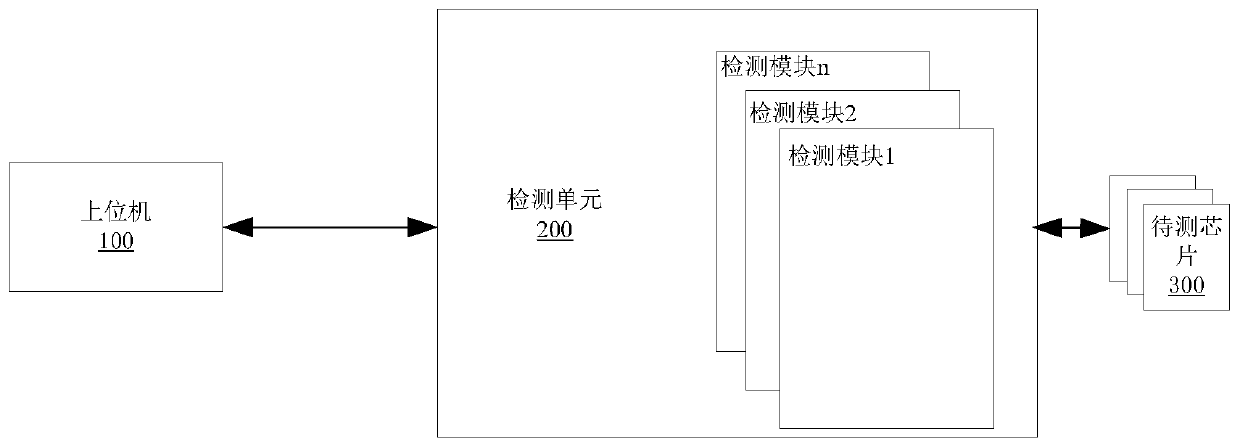

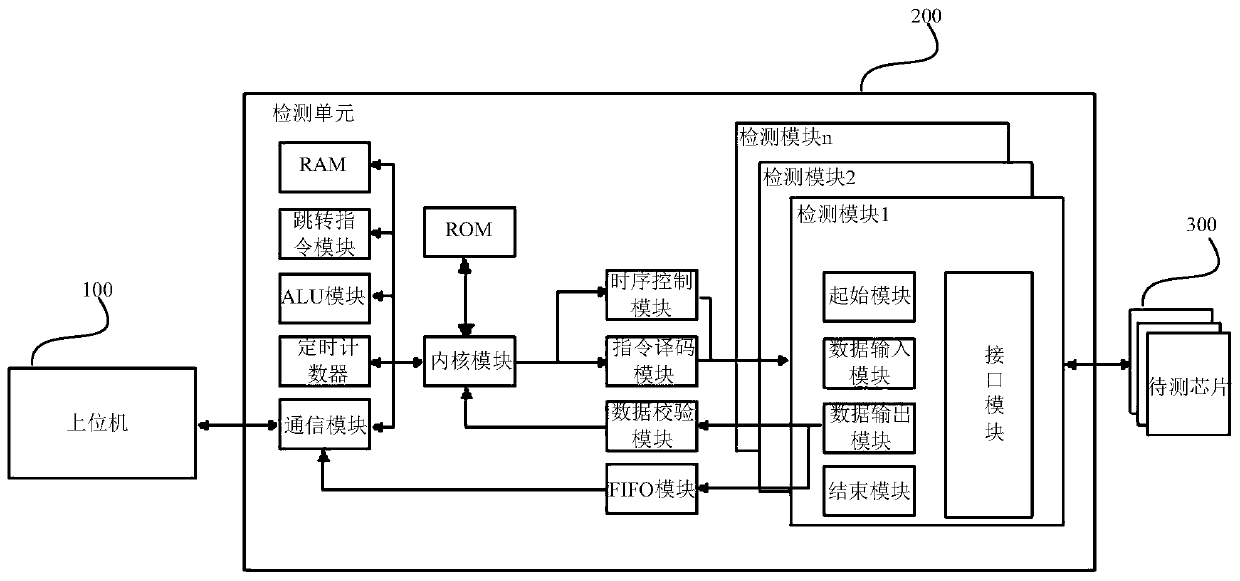

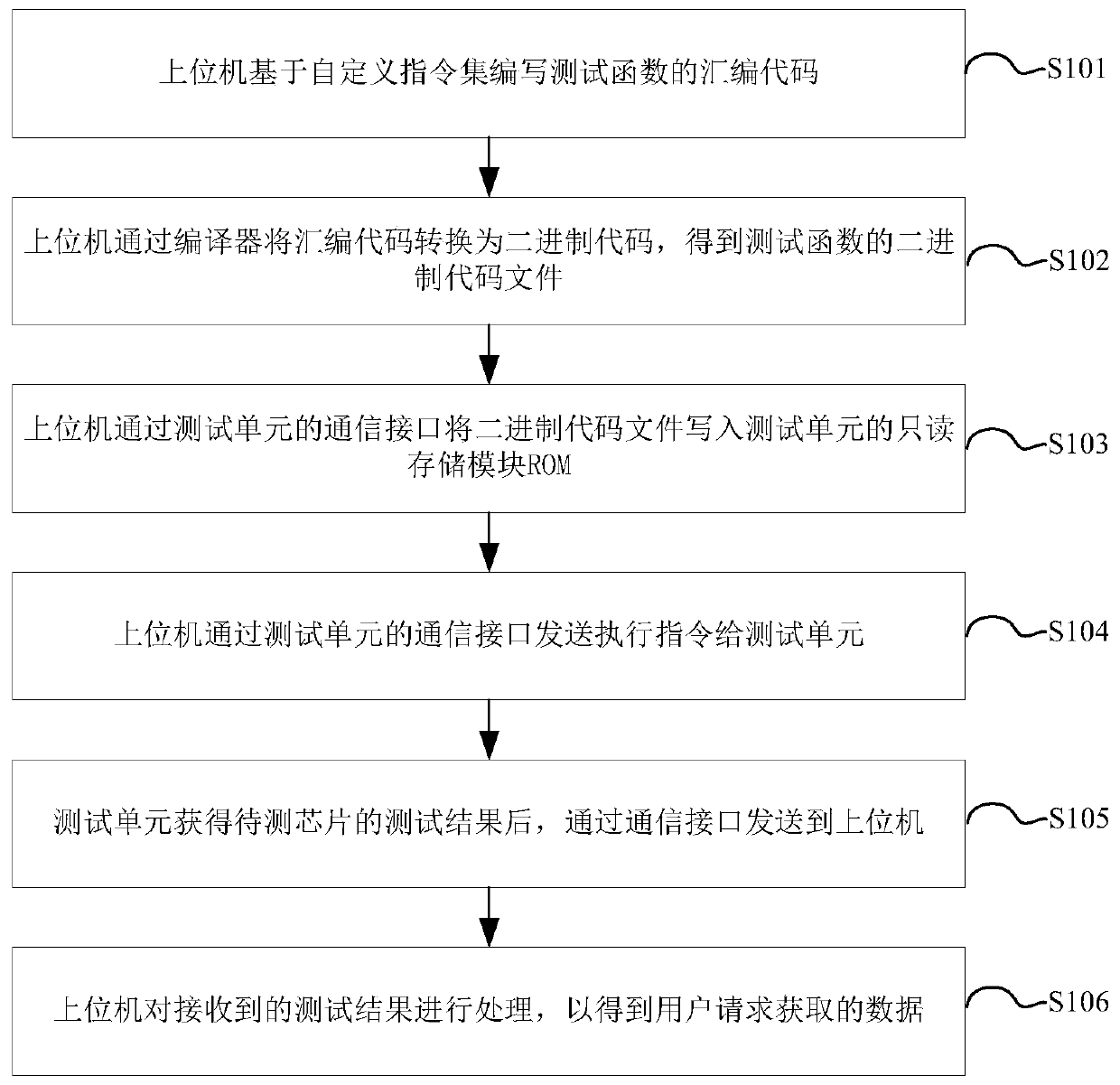

[0039] figure 1 Shown is a chip testing system provided by the embodiment of the present invention. refer to figure 1 , chip test system, including:

[0040] A test unit 200, the test unit 200 is built by an FPGA chip and configured with a plurality of parallel test modules, and the test modules and the chip 300 to be tested are in a one-to-one correspondence;

[0041] The host computer 100 connected with the test unit 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More