Asynchronous data triggering micro-processor architecture

An architecture and microprocessor technology, applied in the direction of concurrent instruction execution, machine execution devices, etc., can solve the problems of clock network power consumption, area occupation, clock distortion, etc., to reduce complexity and delay, reduce power consumption, The effect of improving safety

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be described in further detail below in conjunction with the accompanying drawings.

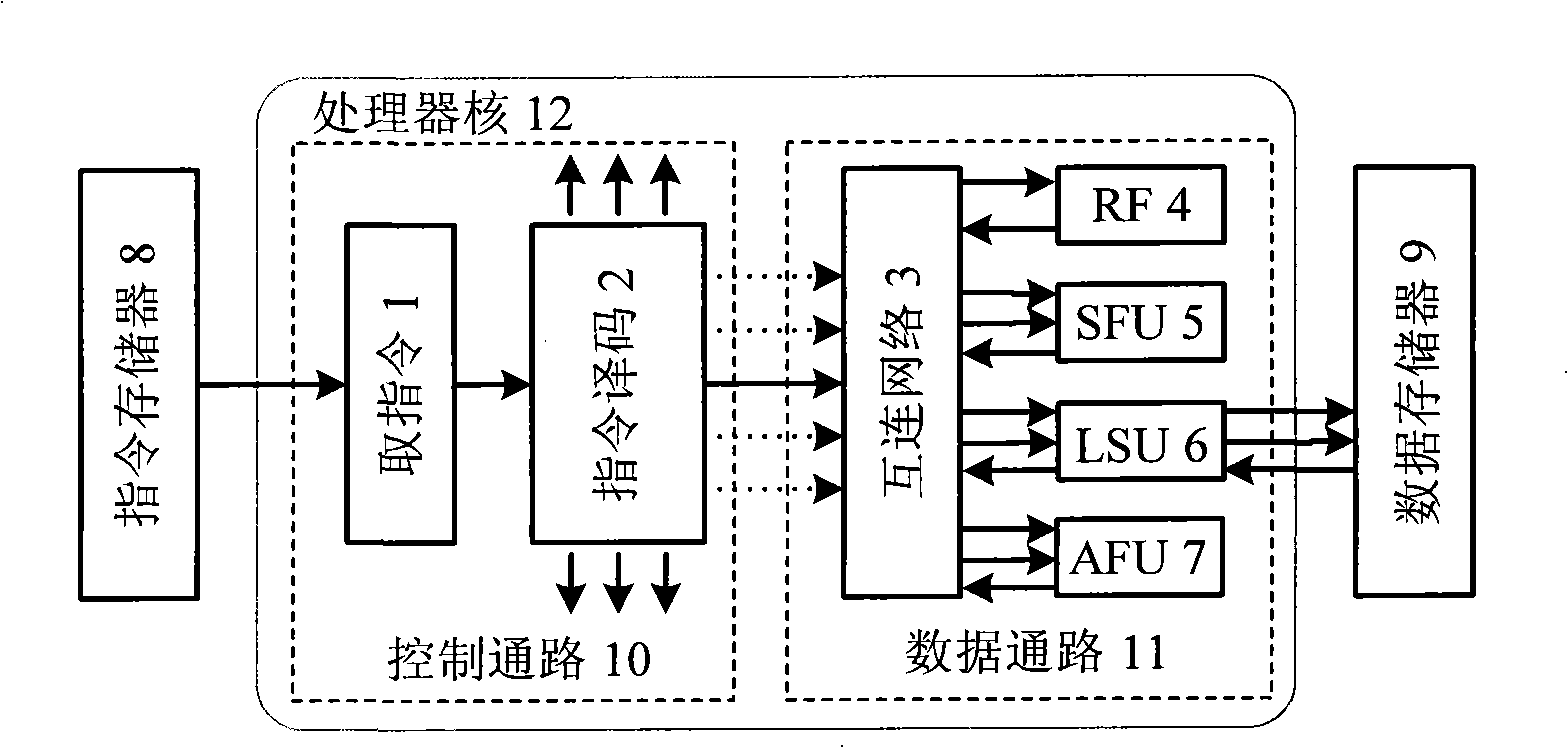

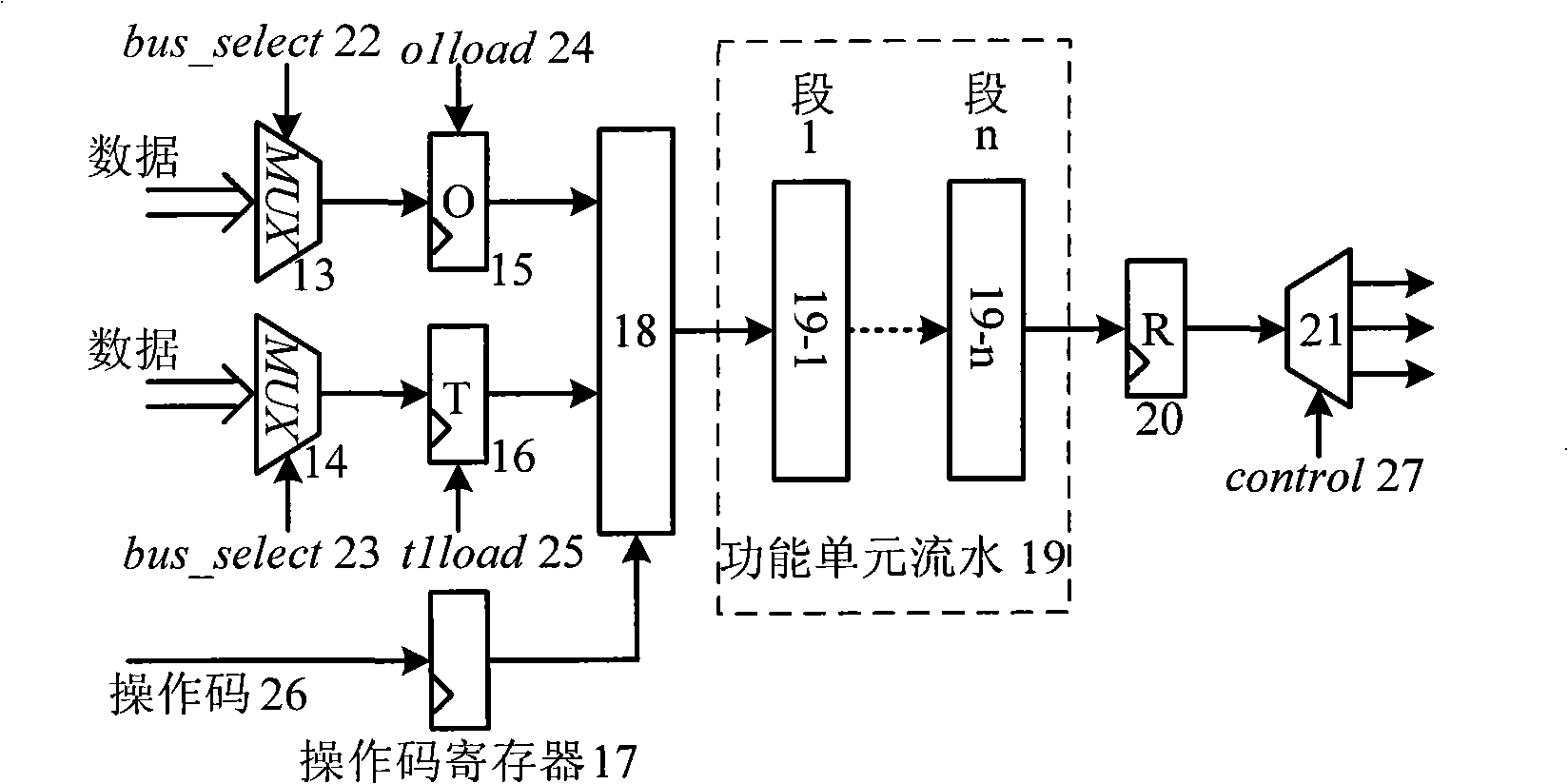

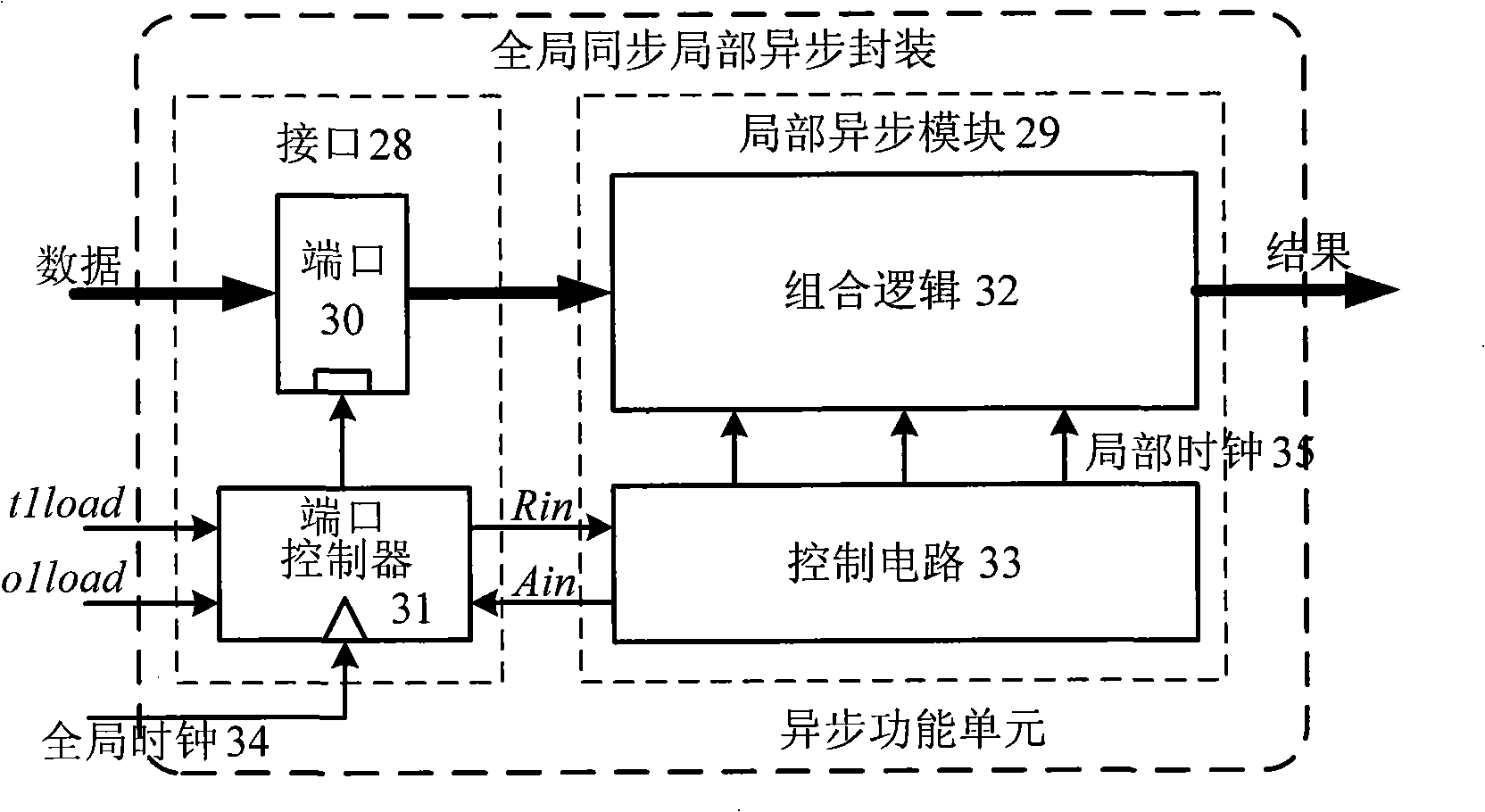

[0033] The present invention is made up of data path 11 and control path 10 ( figure 1 ), the data path is made up of register file RF4 and functional unit FU, wherein functional unit comprises synchronous functional unit SFU, Load / Store unit and asynchronous functional unit AFU, and the Load / Store unit LSU6 in the functional unit is connected with data store 9, to data memory for reading and writing. The control path is composed of an instruction fetch unit 1 and a decoding unit 2, wherein the instruction fetch unit is connected to the instruction memory 8, and reads instructions from the instruction memory, and at the same time, the instruction fetch unit is connected to the decoding unit, and sends the acquired instruction to the decoding unit. unit to decode. The control path and the data path are connected through the interconnection network 3, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More