Integrated circuit computing device and computing processing system

A computing device and integrated circuit technology, applied in the field of system-level chip design, can solve the problems of high cost, poor practicability, low computing power, etc., and achieve the effect of low power consumption and low manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

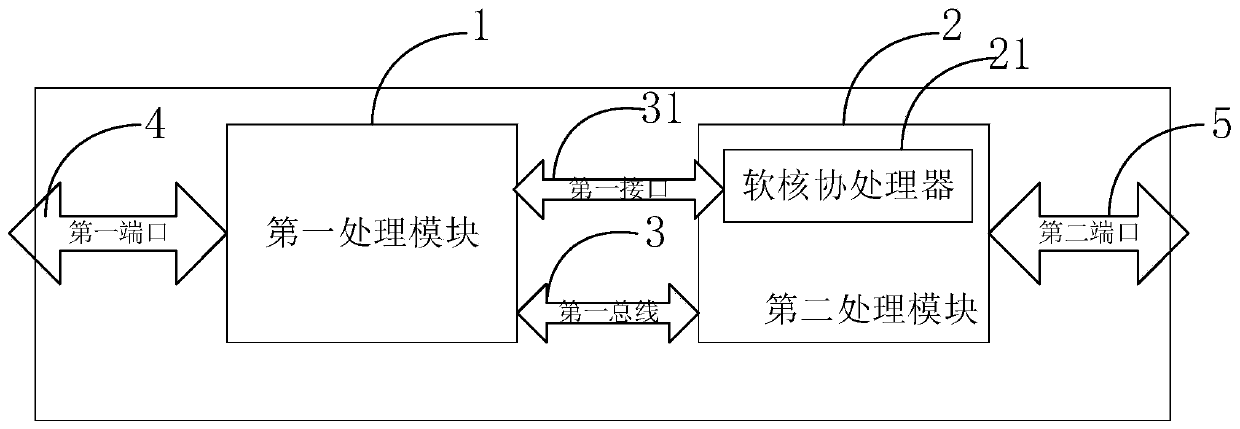

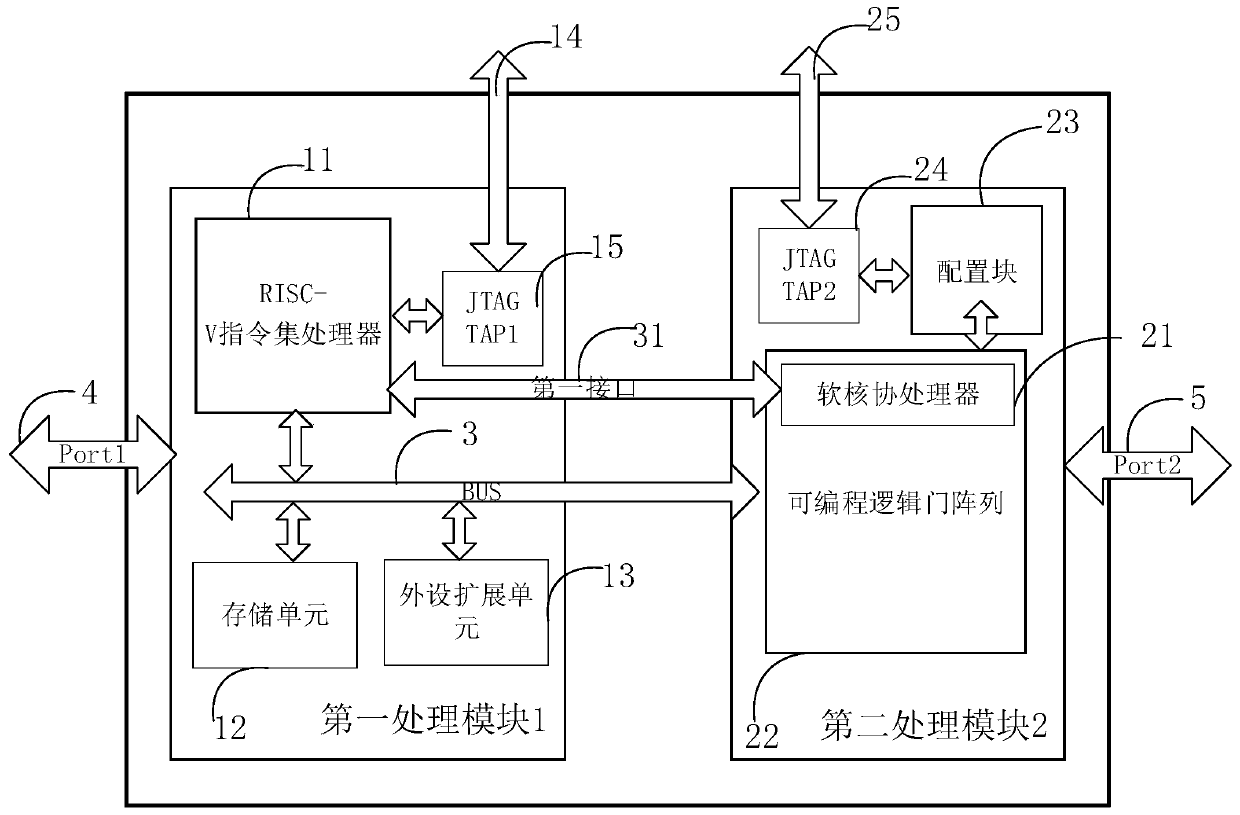

[0035] See figure 1 , figure 1 A module block diagram of an integrated circuit computing device provided for an embodiment of the present invention, including:

[0036] The first processing module 1 is used to receive and process RISC-V instruction set instructions, wherein the RISC-V instruction set instructions include basic instructions, extended instructions and custom instructions;

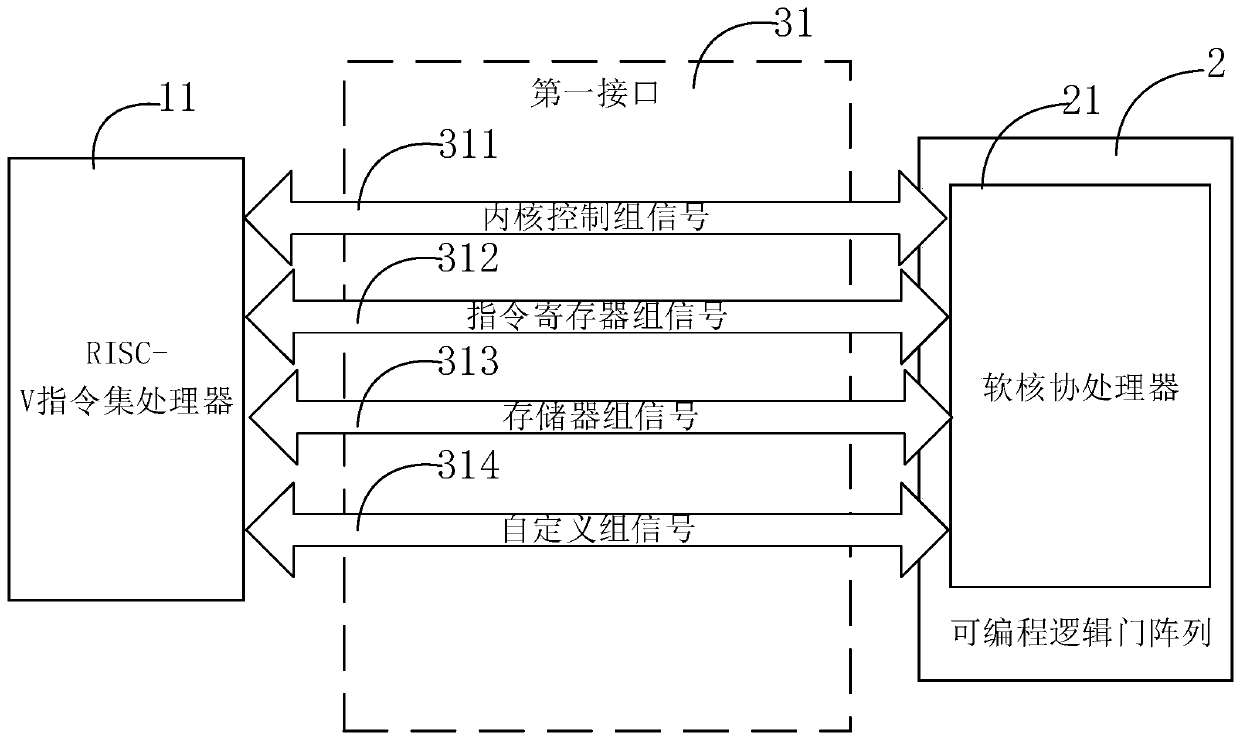

[0037] The second processing module 2, which includes a soft-core coprocessor 21, the soft-core coprocessor 21 is connected to the first processing module 1 through a first interface 31, and is used to process the first processing module 1 sent by the first processing module 1 Describe the custom instruction;

[0038] A first bus 3, connecting the first processing module 1 and the second processing module 2; and

[0039] The first port 4 of the first processing module 1 is connected with the second port 5 of the second processing module 2 .

[0040] RISC-V is an open source instruction se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More