Patents

Literature

67results about How to "Reduce the number of instructions" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Calculation module and method

InactiveCN108388446AFunction increaseEasy to useInstruction analysisEnergy efficient computingControl unitPower consumption

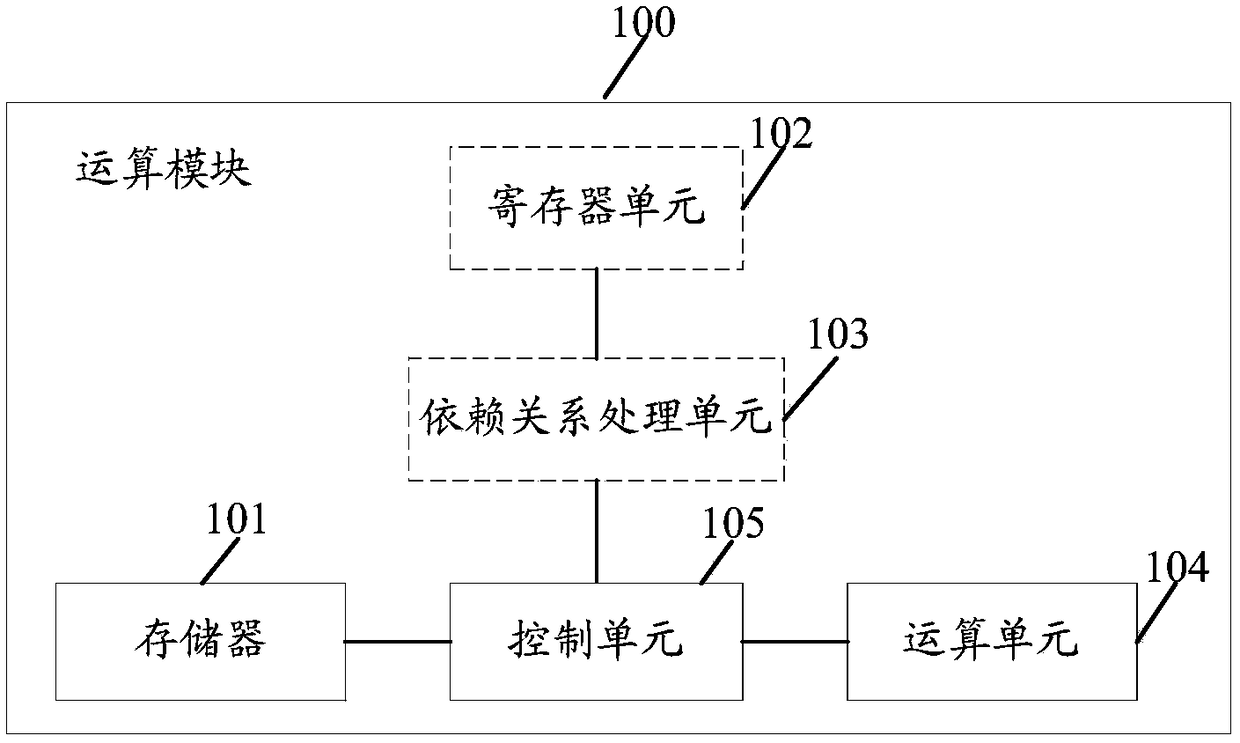

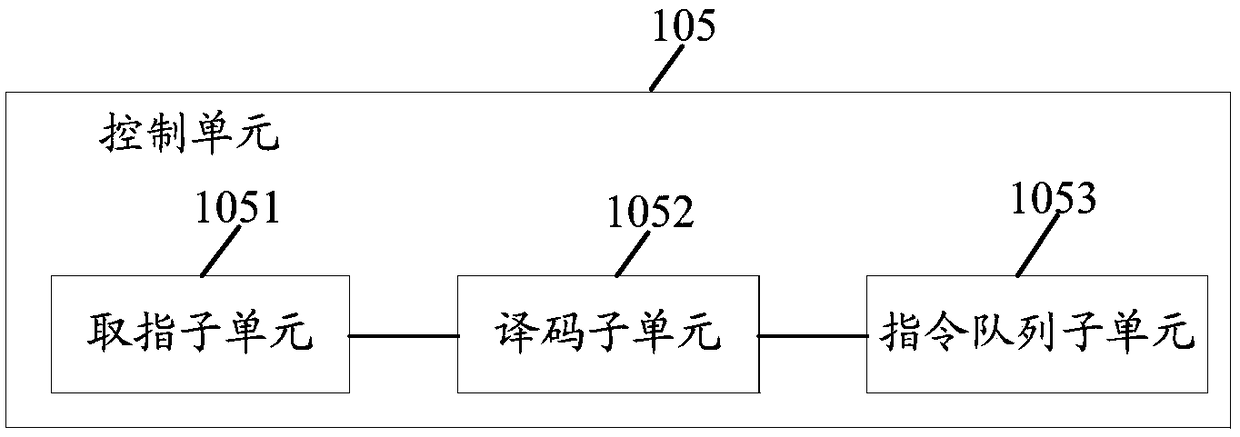

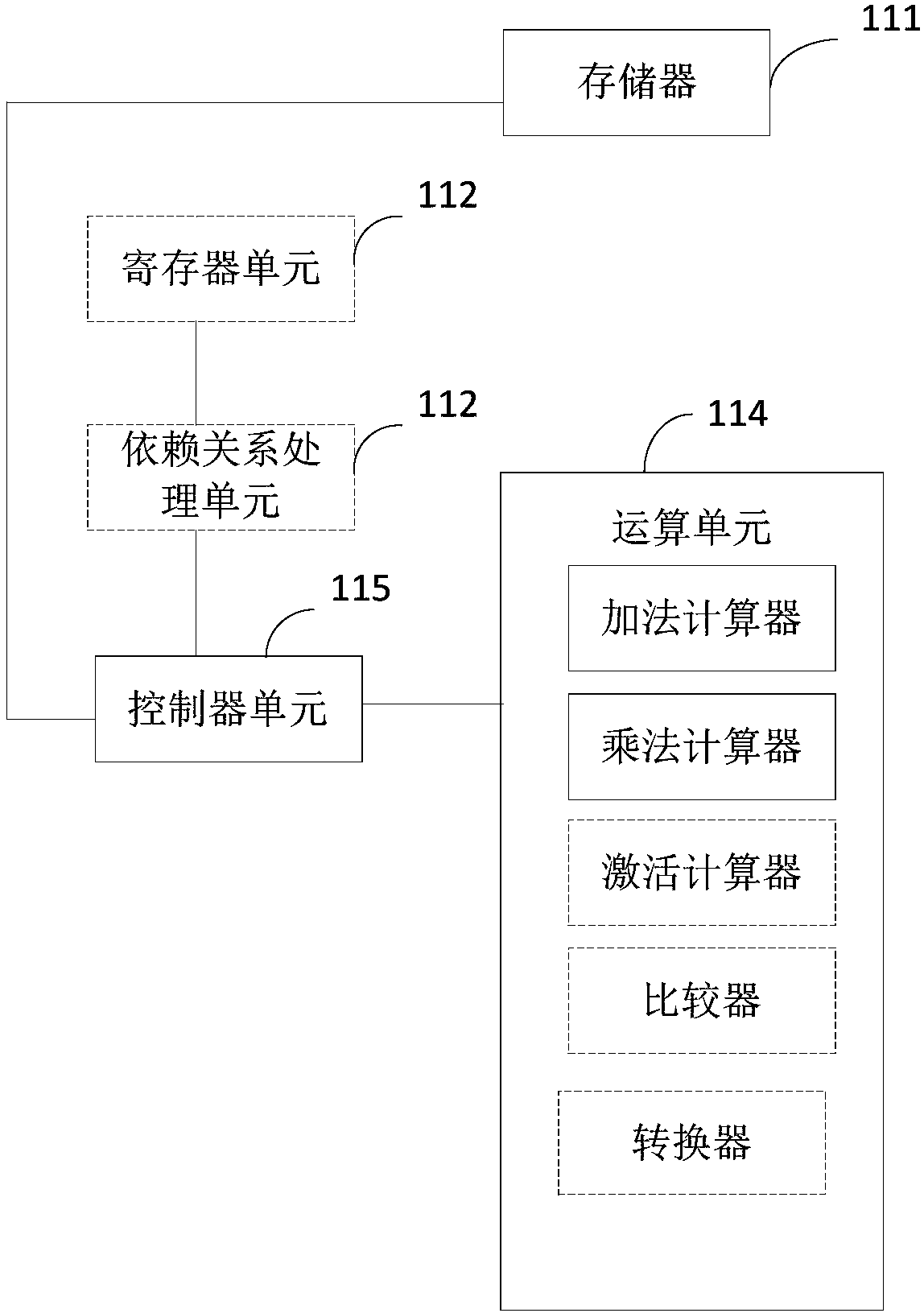

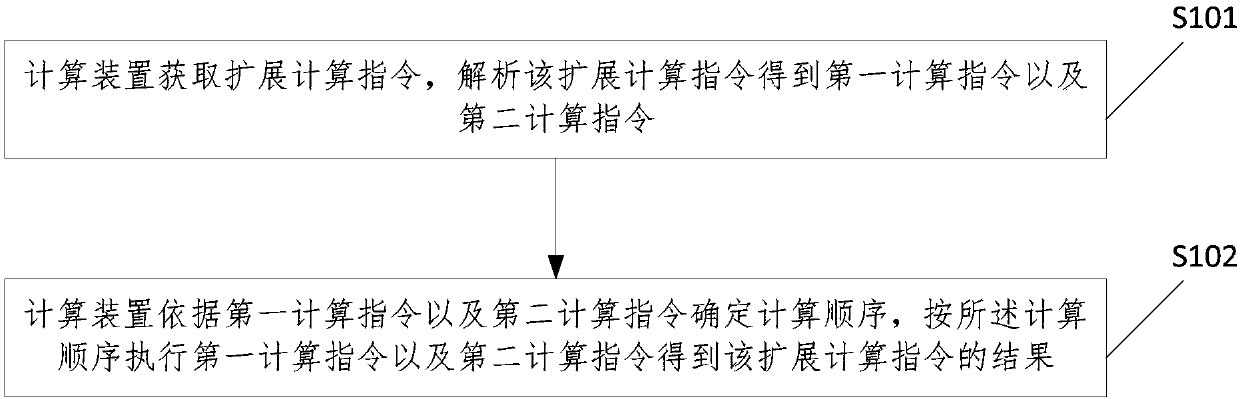

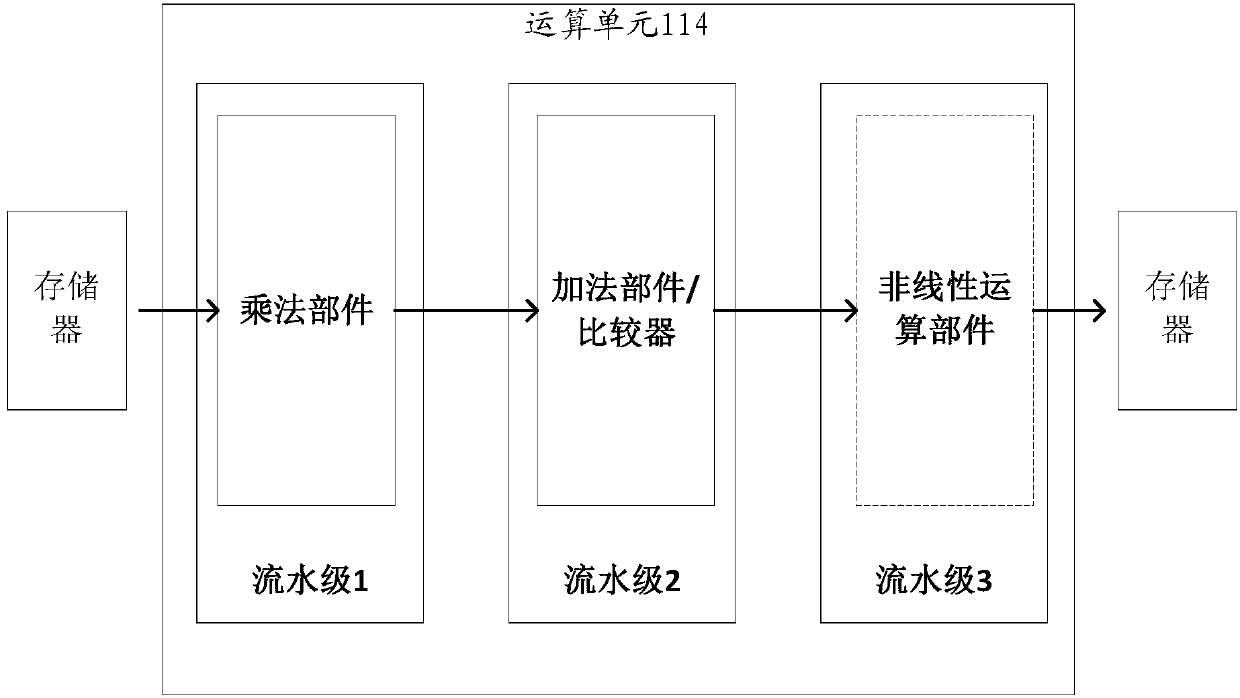

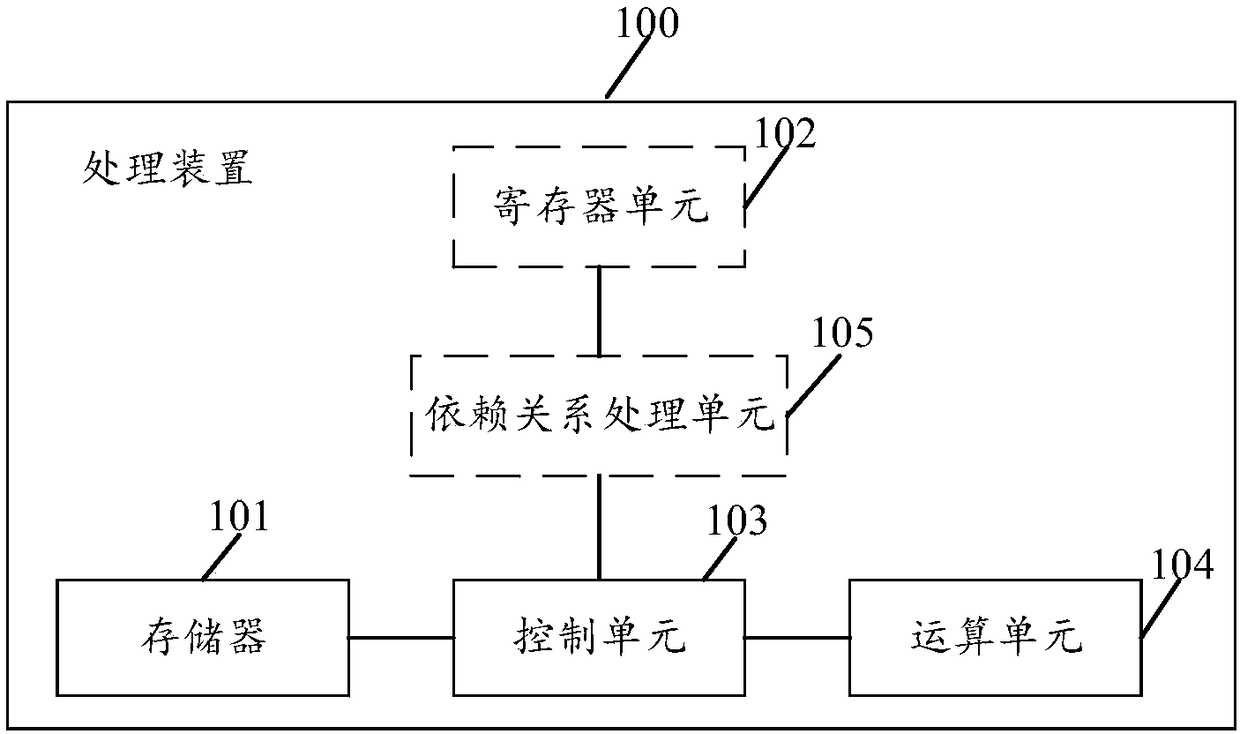

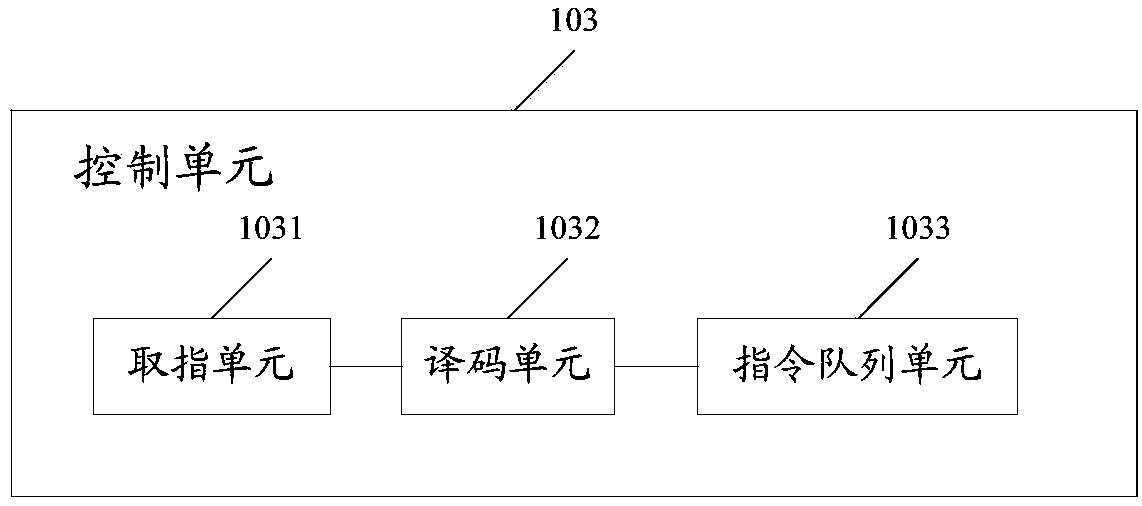

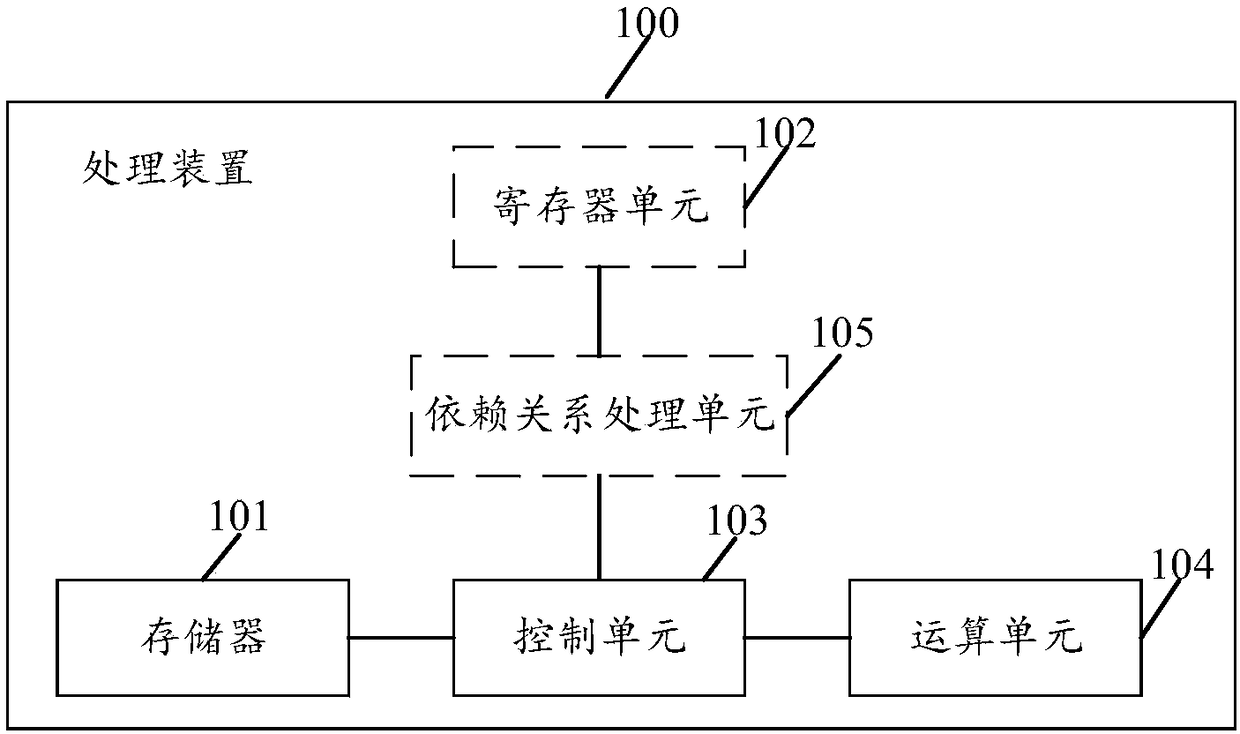

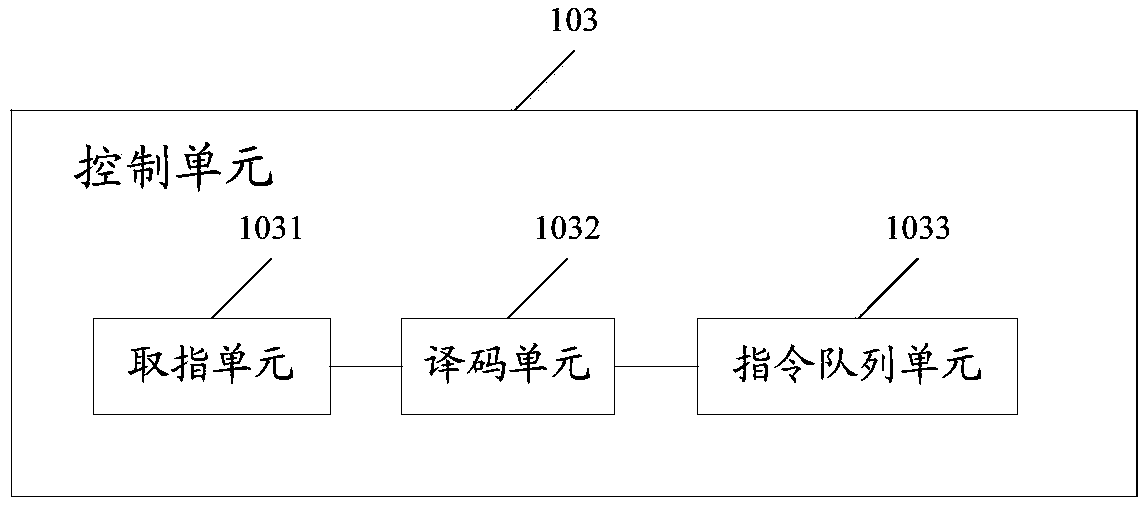

The invention provides a calculation module. The calculation module comprises a memory, a register unit, a dependency relationship processing unit, a calculation unit and a control unit; the memory stores vectors; the register unit stores an expansion instruction; the control unit obtains the expansion instruction, analyzes the expansion instruction to obtain a first calculation instruction and asecond calculation instruction, determines an executive sequence of the first calculation instruction and the second calculation instruction according to the first calculation instruction and the second calculation instruction, and reads an input vector of the first calculation instruction from the memory; an index processing unit finishes operations related to index transformation, index-based data screening and the like; and the calculation unit finishes transformation of an index representation mode of input data of the first calculation instruction, screens the data according to indexes, and executes the first calculation instruction and the second calculation instruction for the input data of the first calculation instruction according to the executive sequence to obtain a result of the expansion instruction. The technical scheme provided by the calculation module has the advantages of low power consumption and low calculation expense.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

Operation device and related product

ActiveCN107861757AFunction increaseEasy to useConcurrent instruction executionControl unitPower consumption

The invention provides an operation device. The operation device is used for executing operation according to an extended instruction and comprises a storage, an operation unit and a control unit; theextended instruction comprises an operation code and an operation domain, and the storage is used for storing a vector; the control unit is used for obtaining the extended instruction, analyzing theextended instruction to obtain a vector operation instruction and a second operation instruction, determining the calculation sequence of the vector operation instruction and the second operation instruction according to the vector operation instruction and the second operation instruction and reading an input vector corresponding to an input vector address from the storage; the operation unit isused for executing the vector operation instruction and the second operation instruction on the input vector according to the calculation sequence to obtain a result of the extended instruction. The operation device has the advantages of being low in power consumption and small in calculation expenditure.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

Rendering method of ambient occlusion image, method for generating effect image and apparatus

ActiveCN107730578AResolve distortionGood effectProcessor architectures/configuration3D-image renderingPerspective transformationScreen space

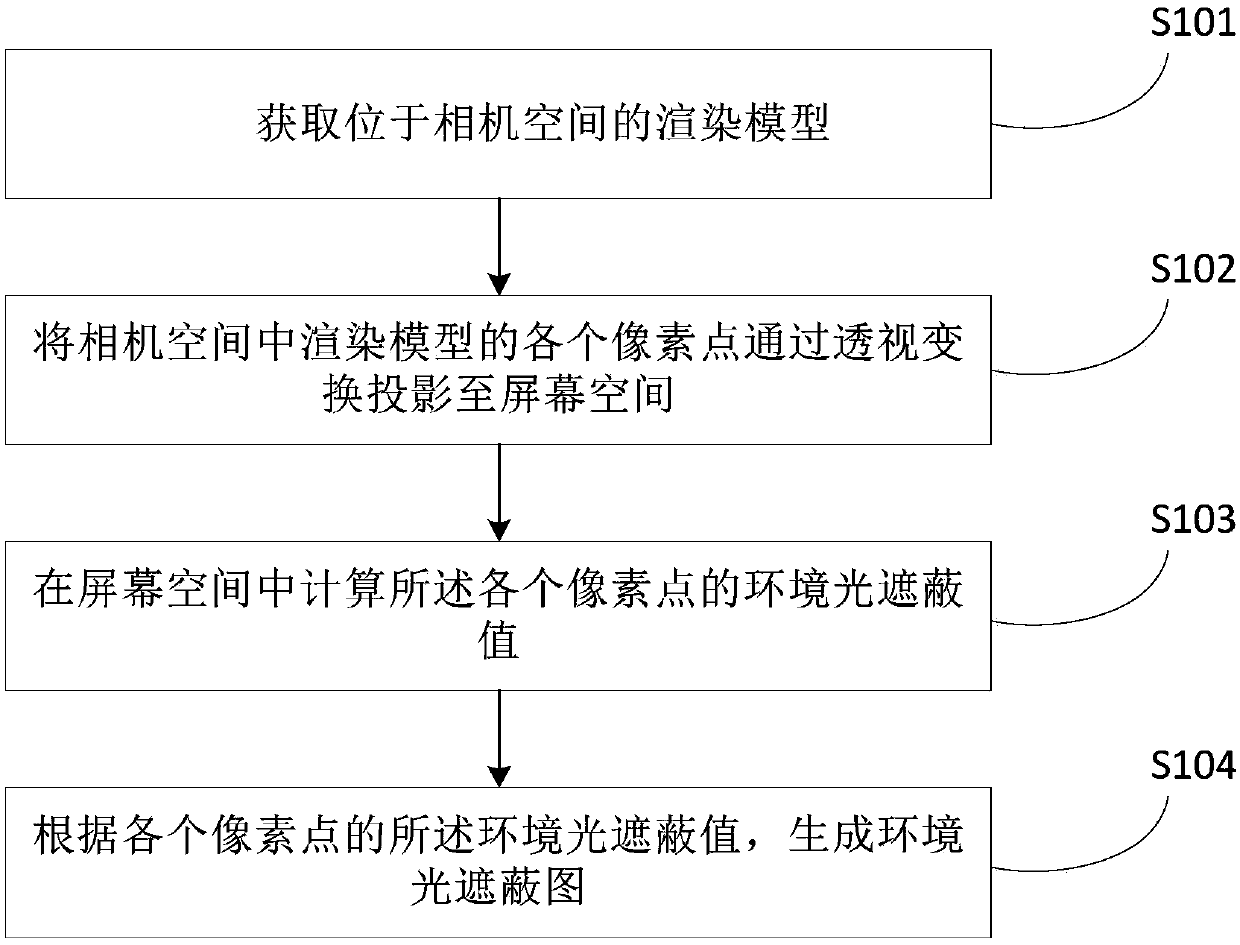

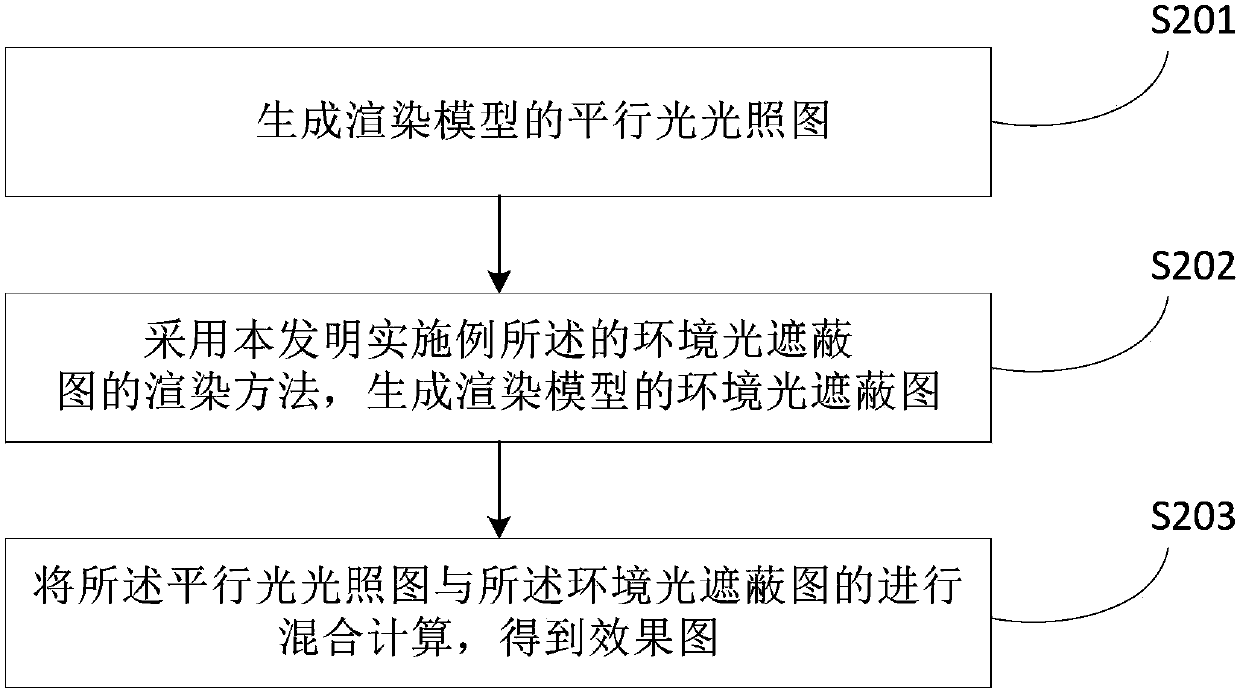

The present invention discloses a rendering method of an ambient occlusion image, a method for generating an effect image and an apparatus. The rendering method includes the following steps that: a rendering model located in a camera space is obtained; each pixel of the rendering model in the camera space is projected to a screen space through perspective transformation; the ambient occlusion value of each pixel in the screen space is calculated; and the ambient occlusion image is generated according to the ambient occlusion value of each pixel. According to the rendering method provided by the technical schemes of the invention, the pixels of the rendering model in a scene are projected to the screen space from the camera space; the ambient occlusion values of the pixels in the screen space are calculated; and therefore, a frequent space transformation process is omitted, the number of the instructions of a GPU during operation can be saved, and the operation efficiency of the GPU canbe improved.

Owner:上海灵犀互动娱乐有限公司

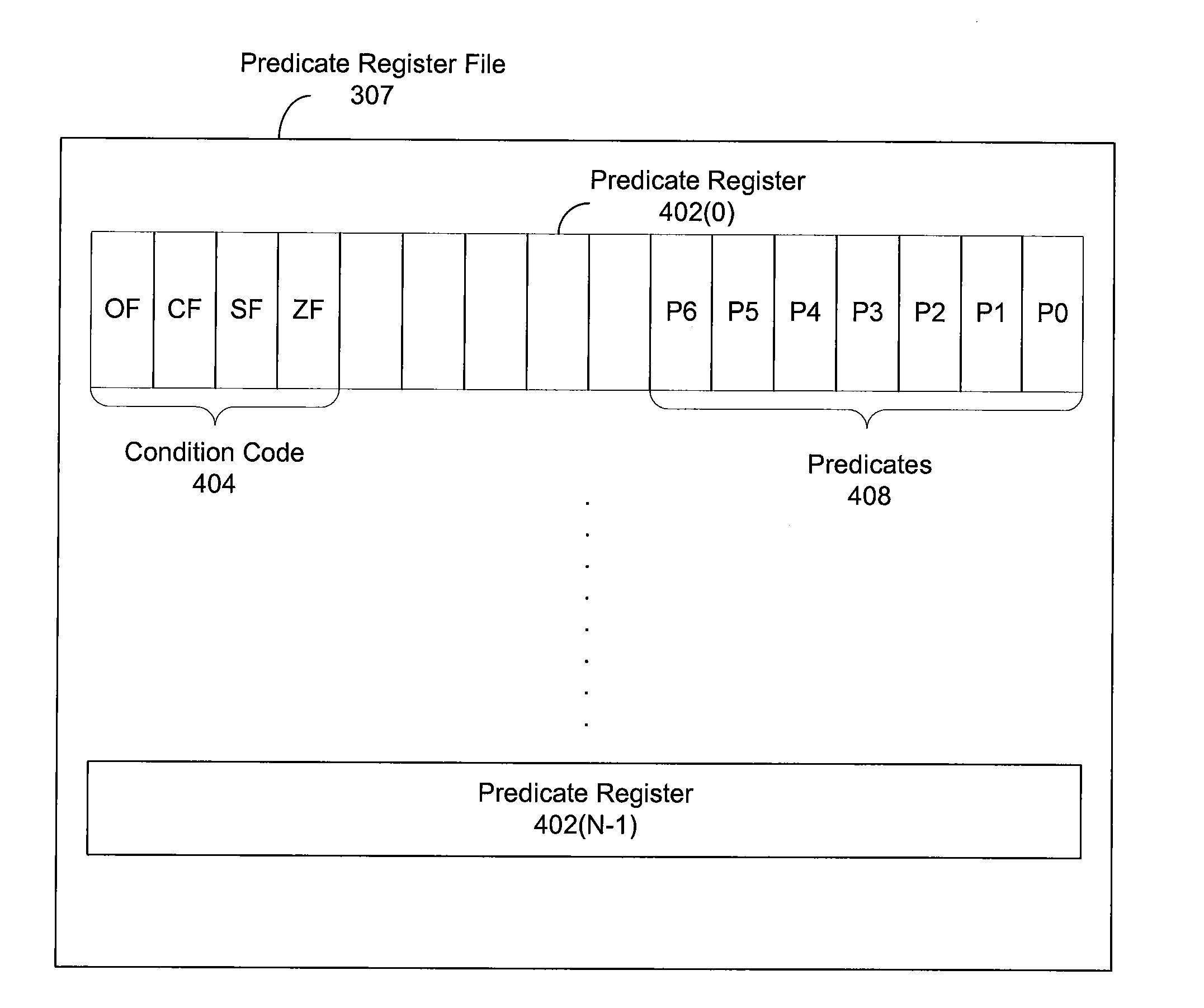

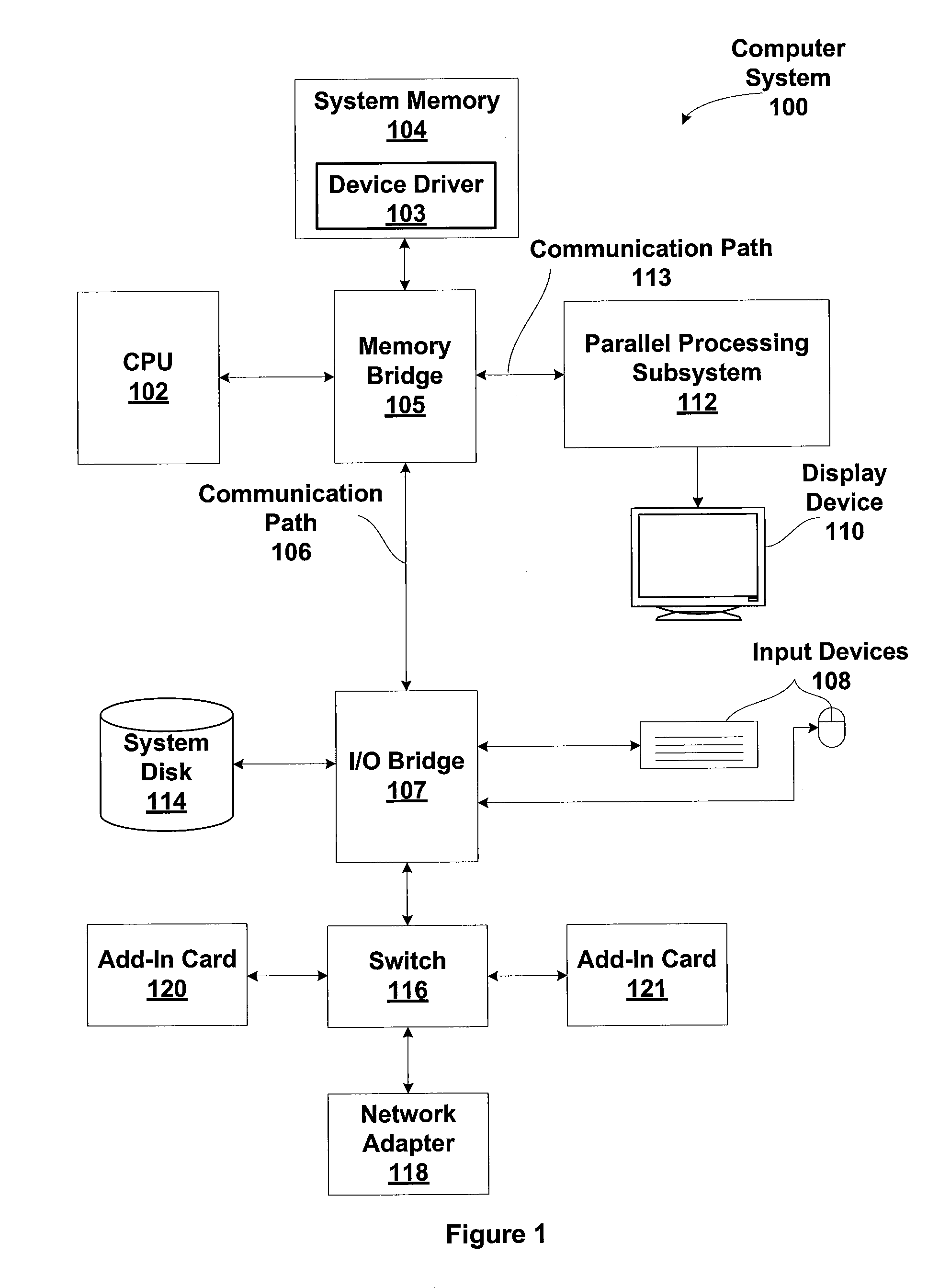

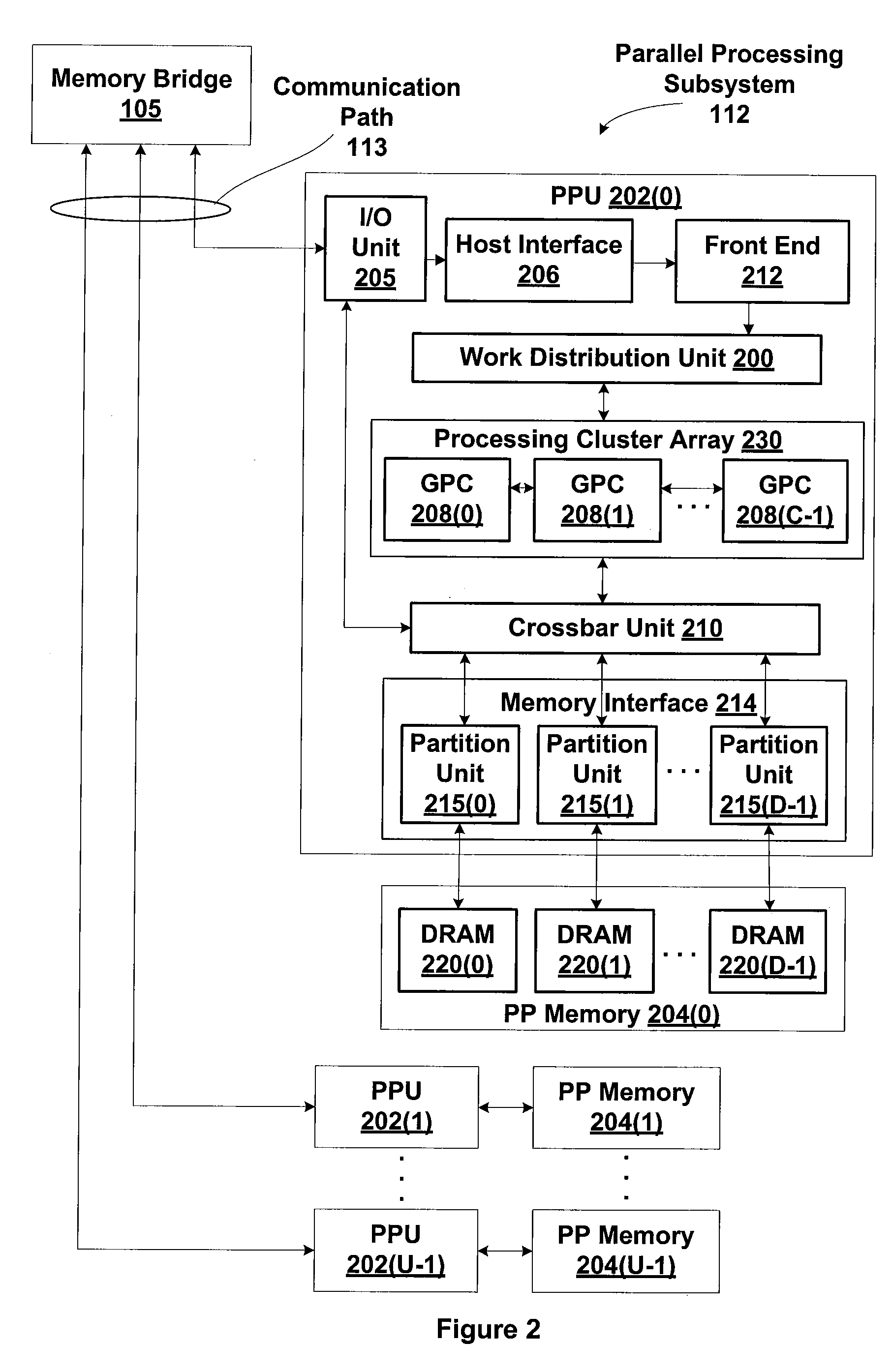

Extended-Precision Integer Arithmetic and Logical Instructions

ActiveUS20110078225A1Reduce the number of instructionsShorten the counting processConditional code generationRegister arrangementsOperandCondition Code

The invention set forth herein describes a mechanism for efficiently performing extended precision operations on multi-word source operands. Corresponding data words of the source operands are processed together via each instruction of a cascading sequence of instructions. State information generated when each instruction is processed is stored in condition code flags. The state information is optionally used in the processing of subsequent instructions in the sequence and / or accumulated with previously set state information.

Owner:NVIDIA CORP

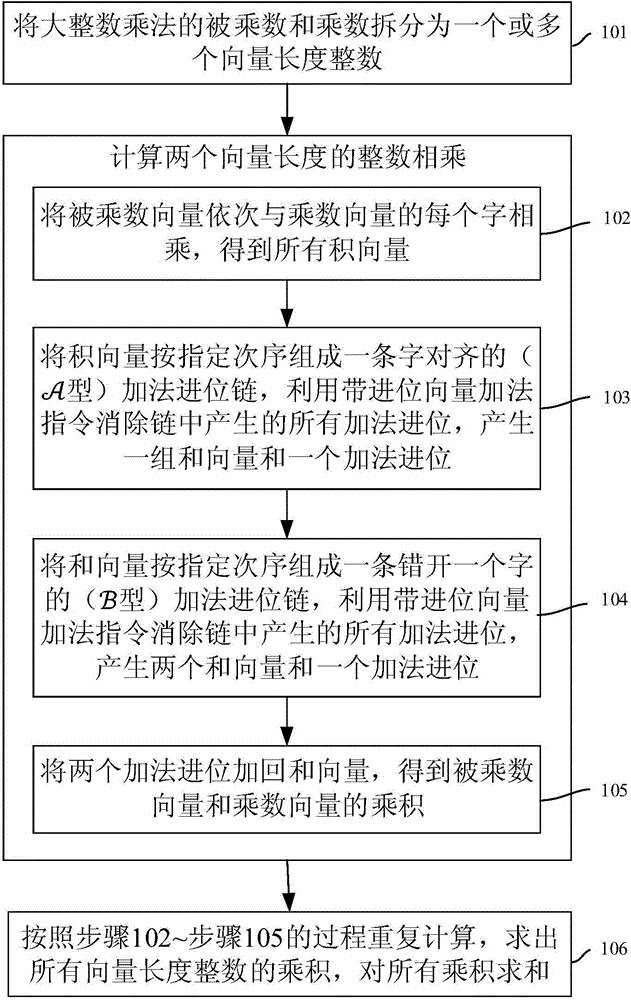

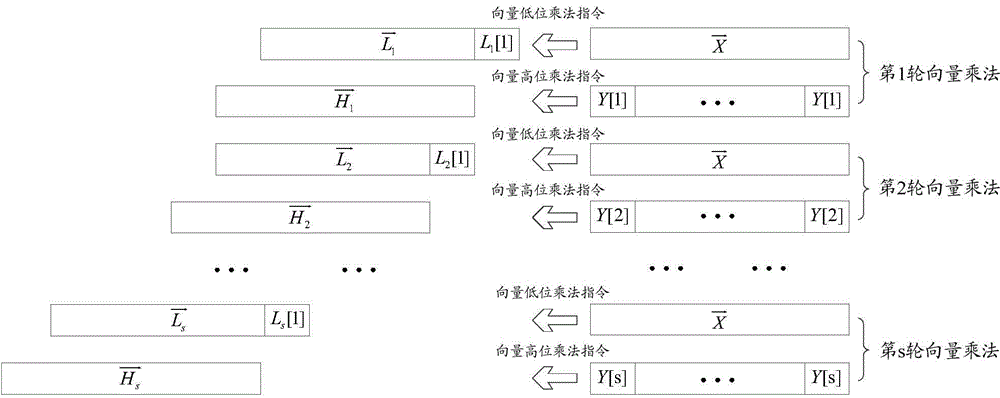

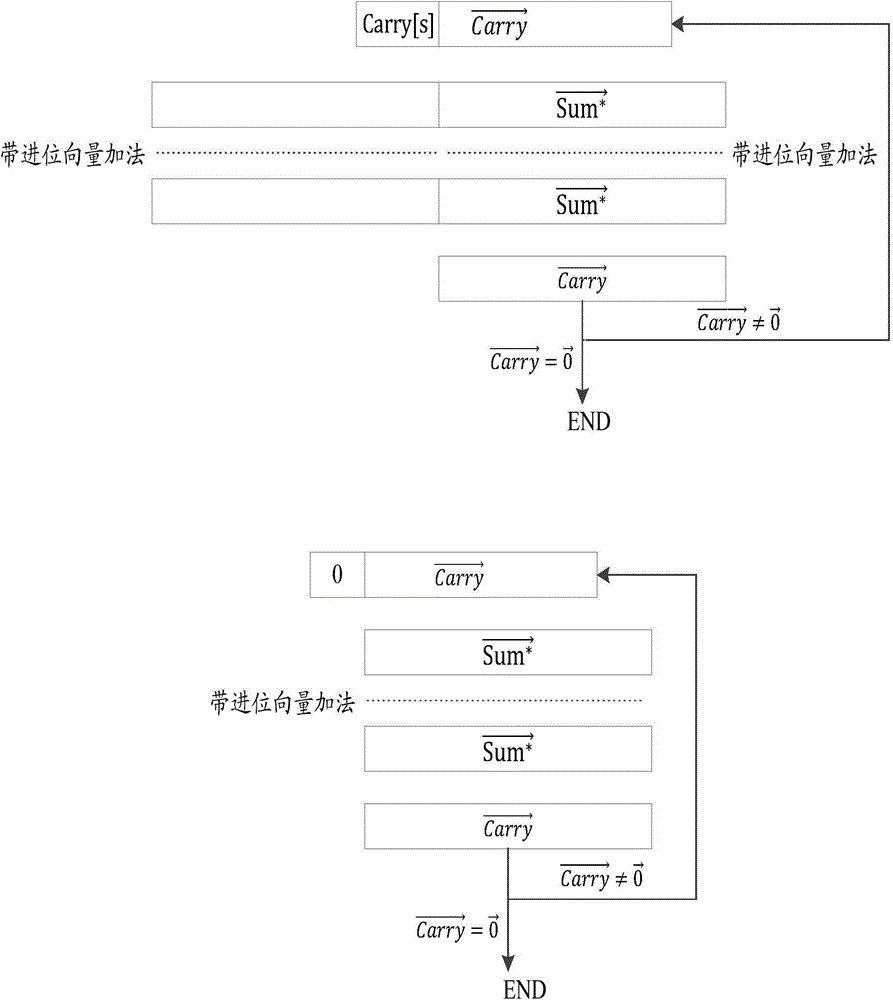

Large integer multiplication realizing method and device based on vector instructions

ActiveCN104461449AReduce the number of instructionsImprove computing throughputDigital data processing detailsXeon PhiTwo-vector

The invention provides a large integer multiplication realizing method and device based on vector instructions. The multiplicand and the multiplier of the large integer multiplication are each split into one or more vector length integers, the integers are multiplied, and all products are summed; when the integers with two vector lengths are multiplied, product vectors generated by all the vector multiplication instructions form two addition carry chains according to the appointed sequence, the vector addition instructions with carries are utilized for making carries generated by vector addition each time serve as input of the next vector addition instruction, all the addition carries in the chains are eliminated, and only two addition carries are generated and added back to obtain the product of the integers with the two vector lengths. Specifically, if the length of the multiplicand and the length of the multiplier are smaller than 1 / n of the vector length, multiplication of n groups of integers is combined into the one-time multiplication of vector length integers, and the calculation handling capacity is promoted by n times. Based on the large integer multiplication method, the invention further discloses a high-speed large integer multiplication device based on an Intel Xeon Phi co-processor. According to the method, instruction numbers needed by the large integer multiplication method are reduced, calculation delay is reduced, and the calculation handling capacity is improved.

Owner:DATA ASSURANCE & COMM SECURITY CENT CHINESE ACADEMY OF SCI

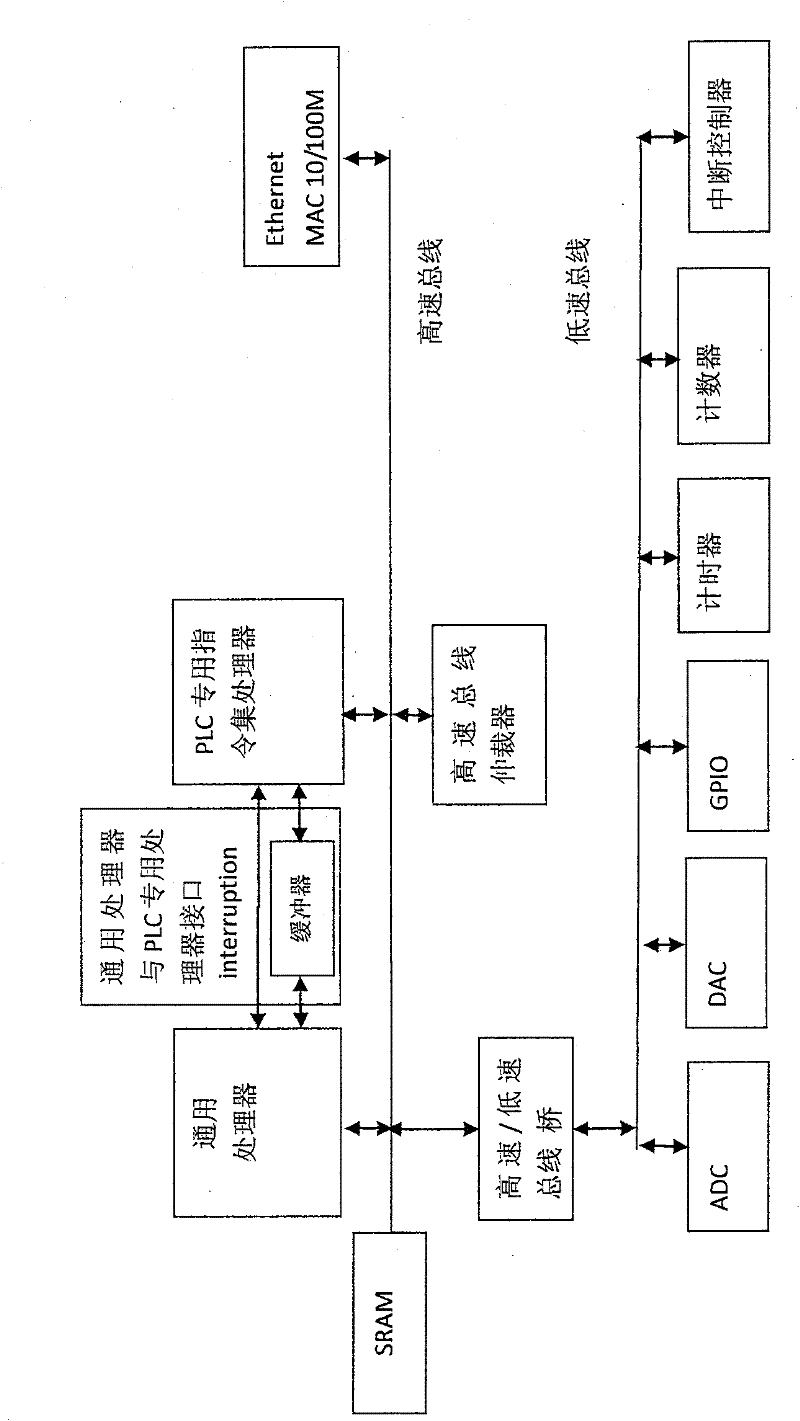

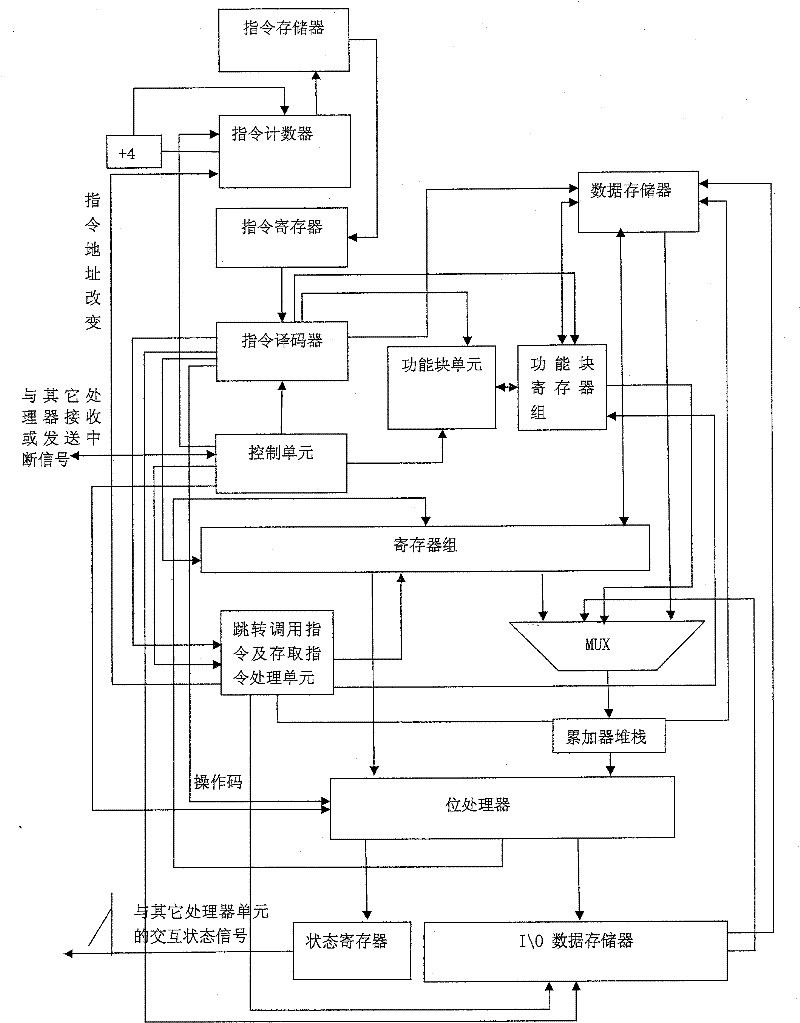

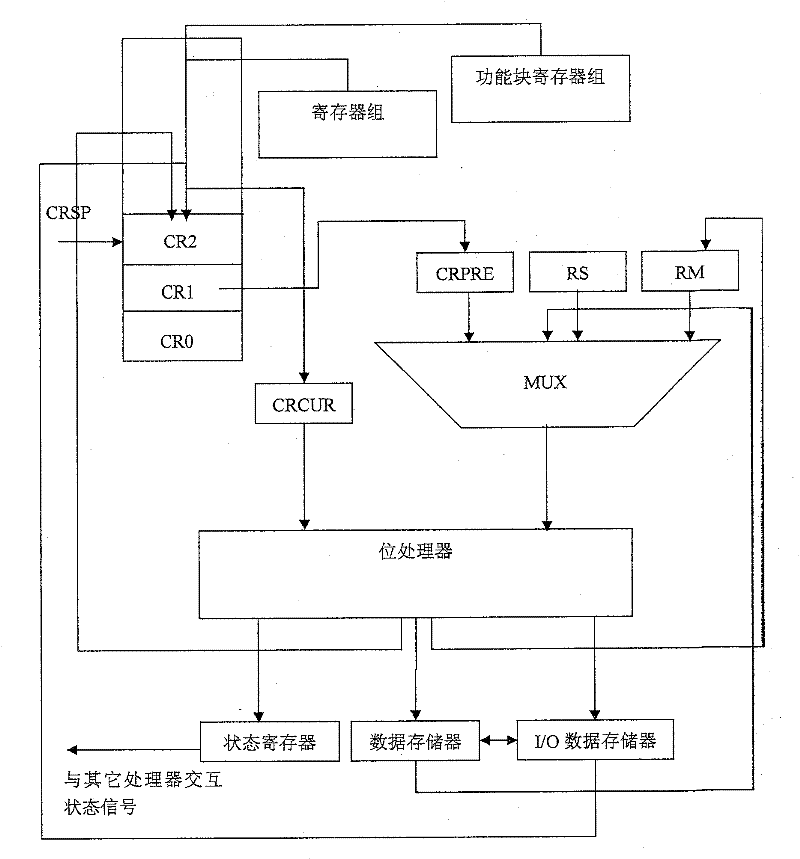

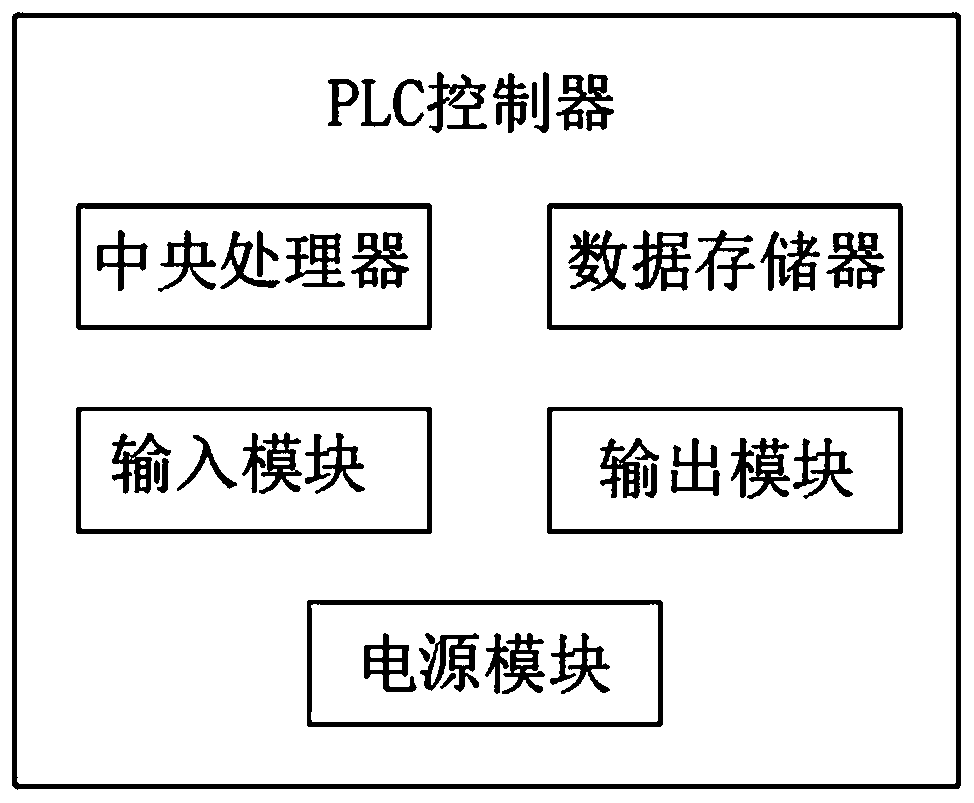

High-performance Programmable Controller Special Processor Architecture and Its Realization Method

ActiveCN102298352AReduce the number of instructionsFast executionProgramme control in sequence/logic controllersComputer architectureProgrammable logic controller

The invention relates to a specific processor system structure for a high-performance programmable controller and an implementation method of the dedicated processor system structure. The specific processor system structure comprises a PLC (Programmable Logic Controller) specific instrument set processor and a general processor, wherein the PLC specific instrument set processor is connected with a general processor through the PLC specific instrument set processor and an interface of the general processor. The implementation method comprises a four-level flow line consisting of a fetch stage,a decoding stage, an executing stage and a writing-back stage, according to the PLC specific instrument set processor. By designing the PLC specific instrument set which accords with the PLC instrument characteristics, the number of instruments for executing a PLC processor is reduced, the execution speed of a PLC program is accelerated, and the processing performance of the PLC processor to a functional block is improved.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

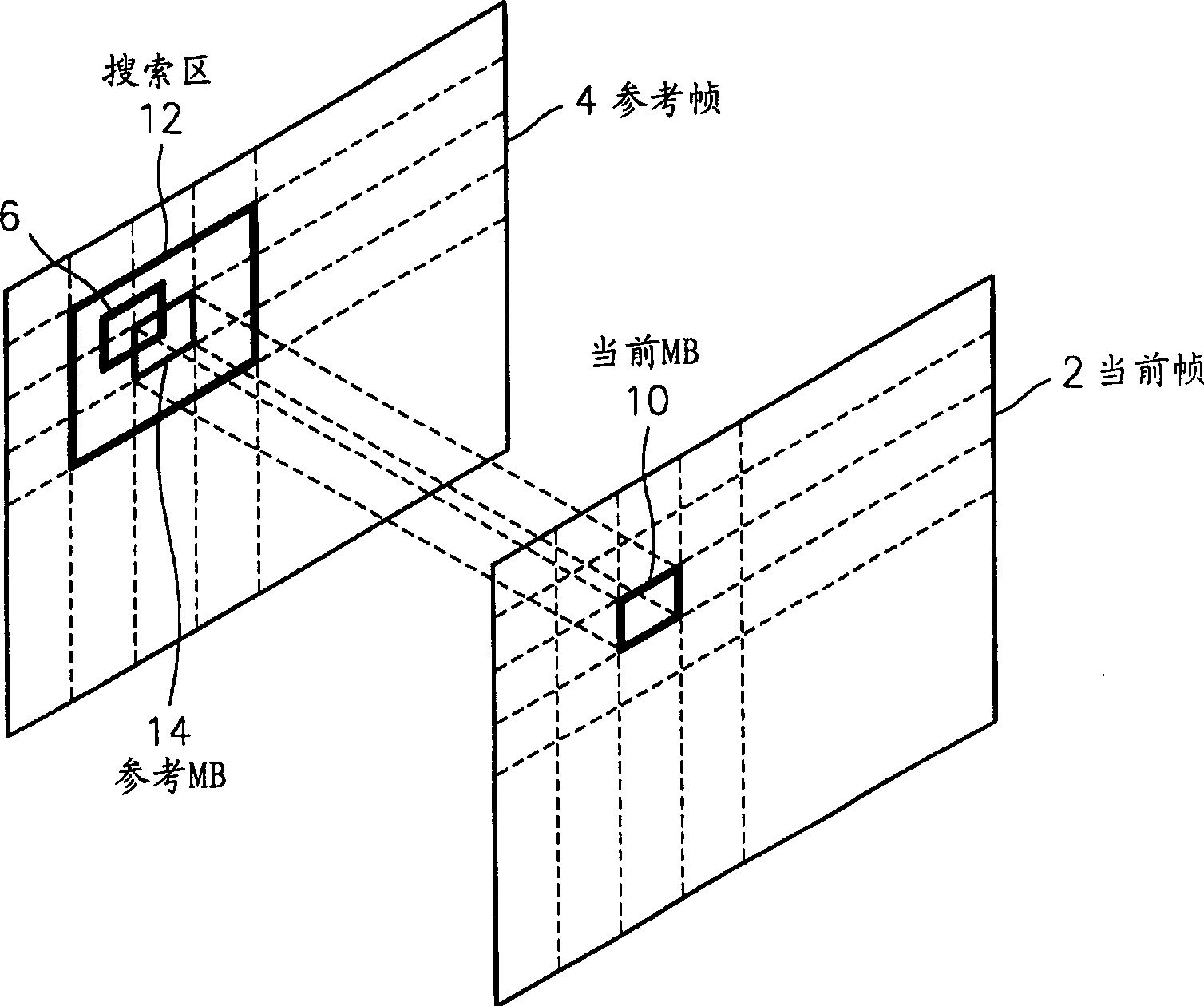

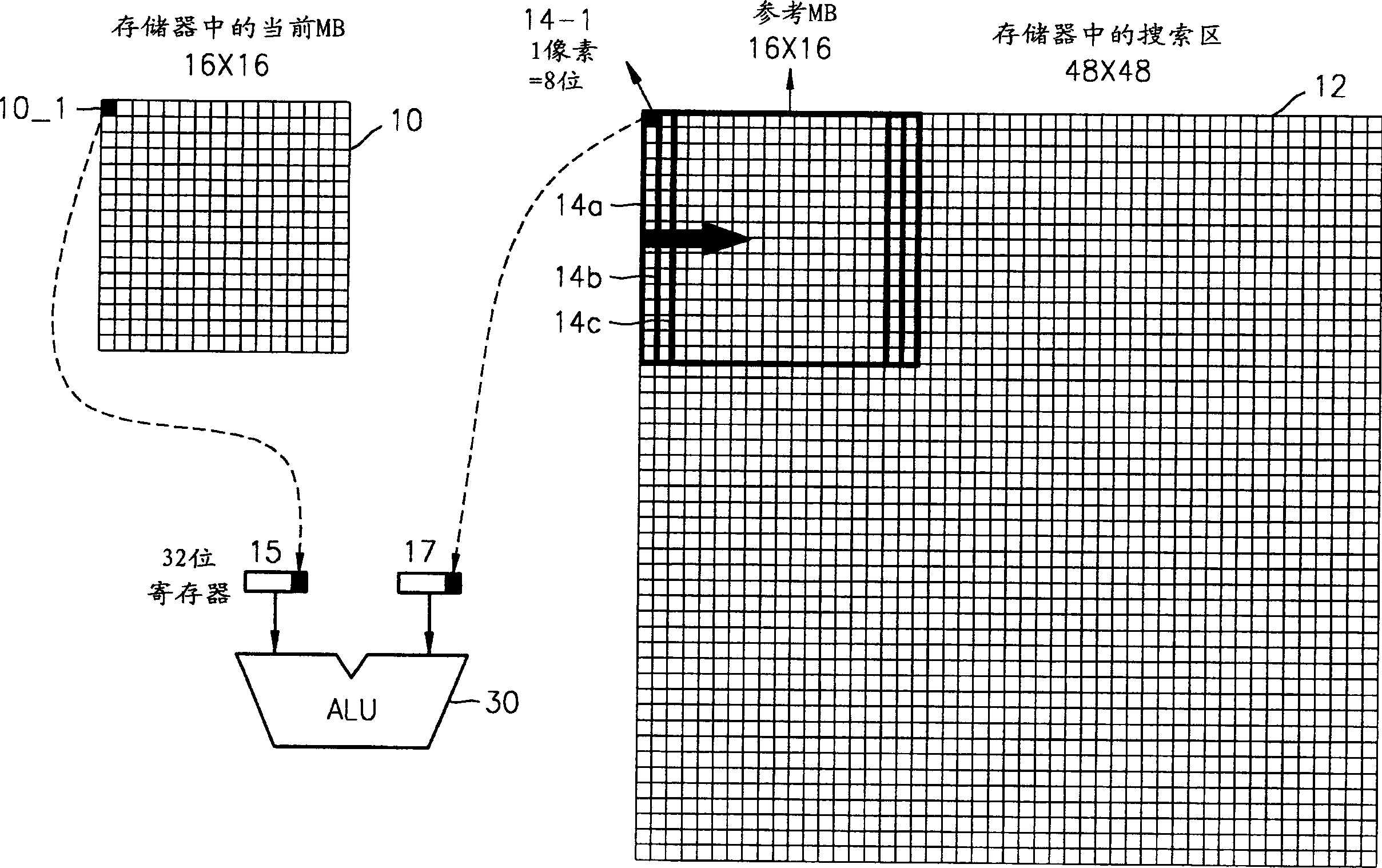

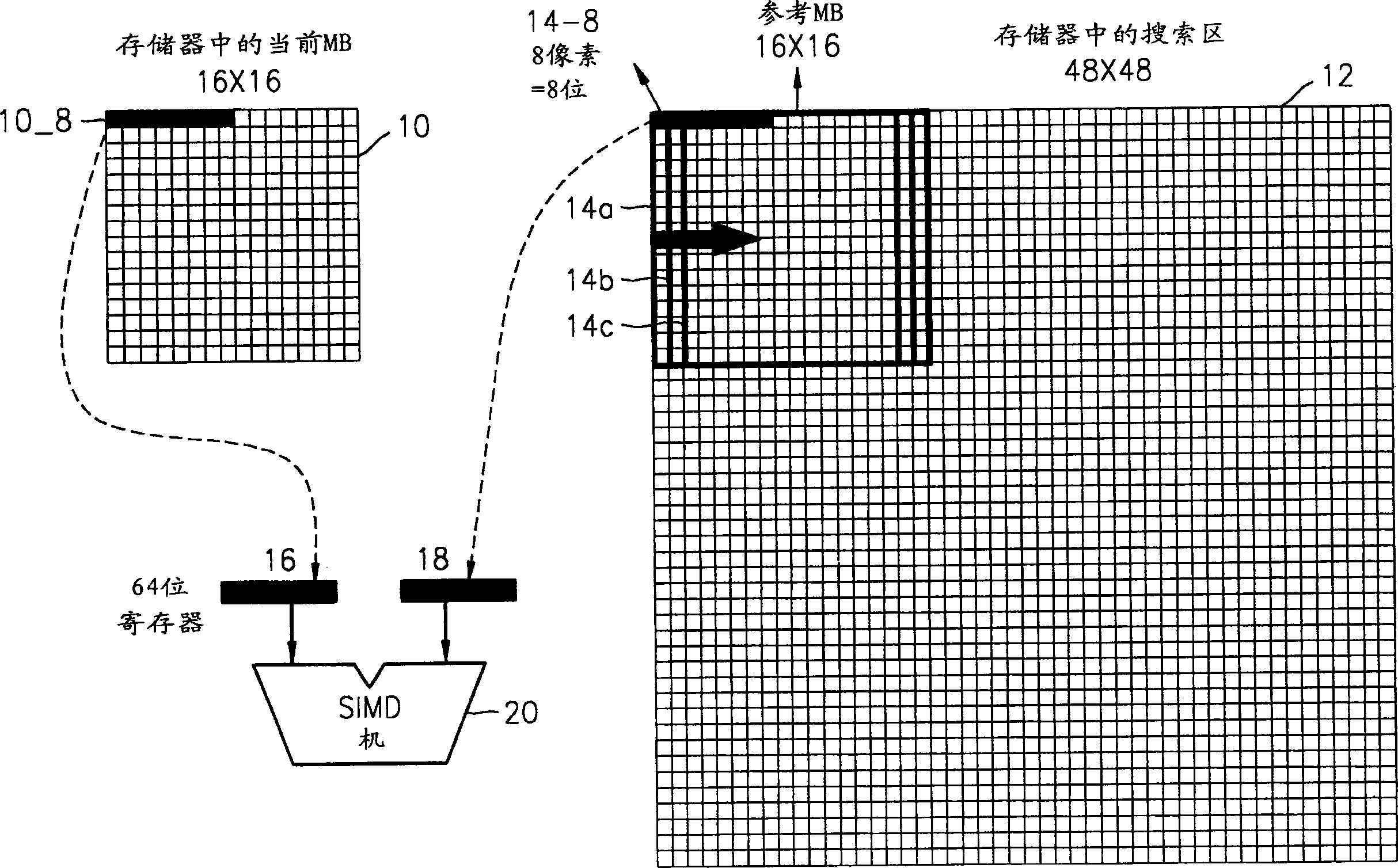

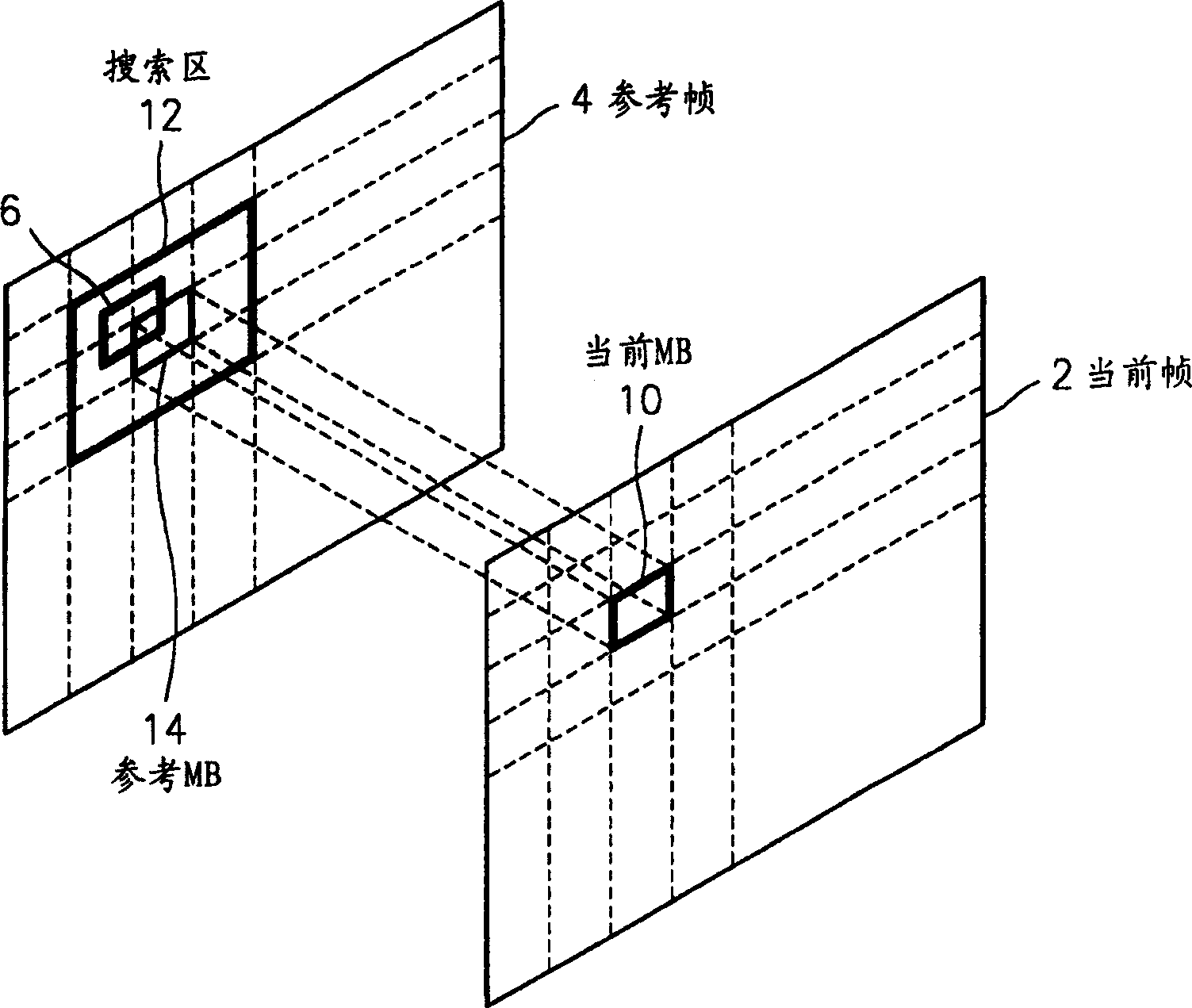

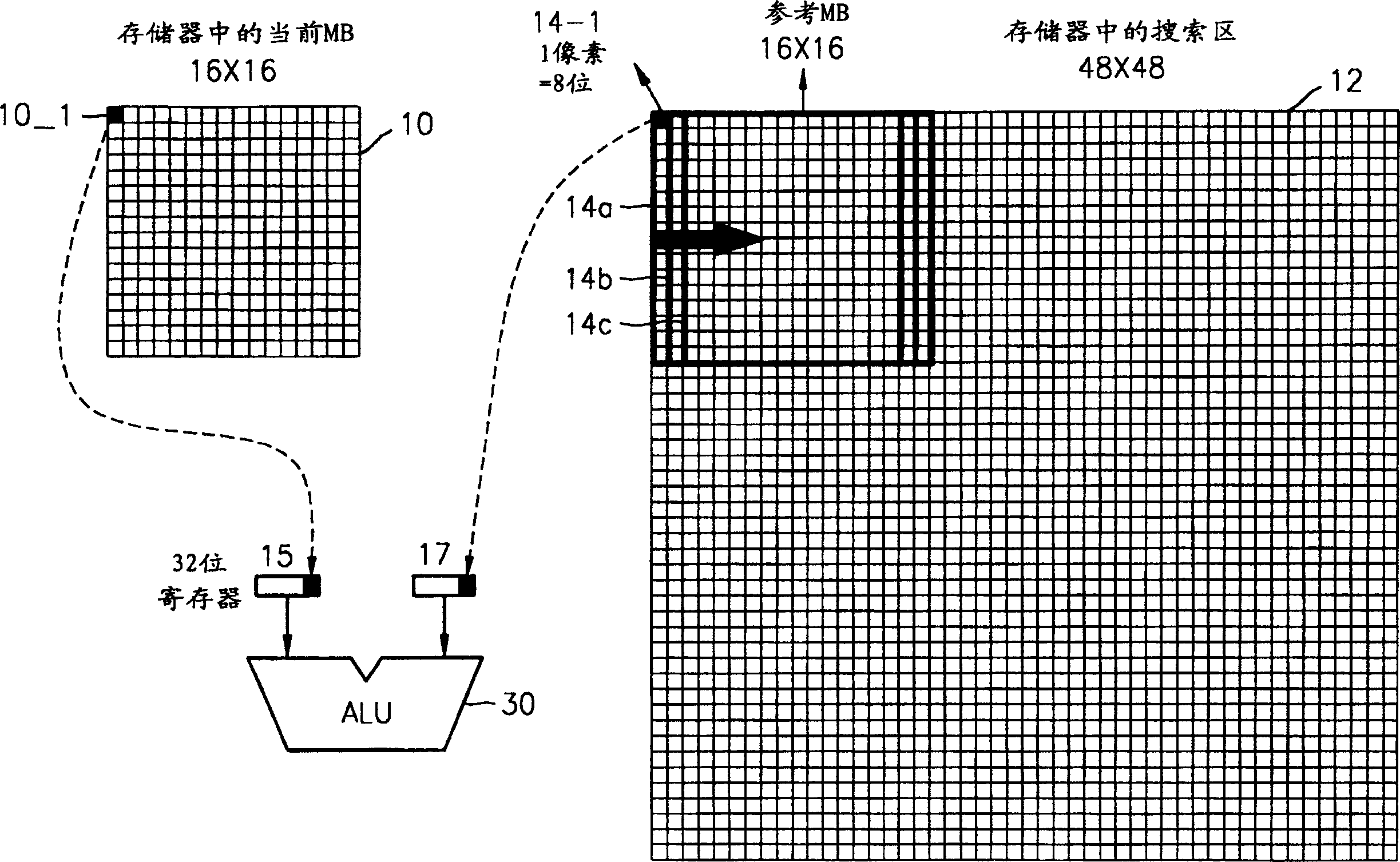

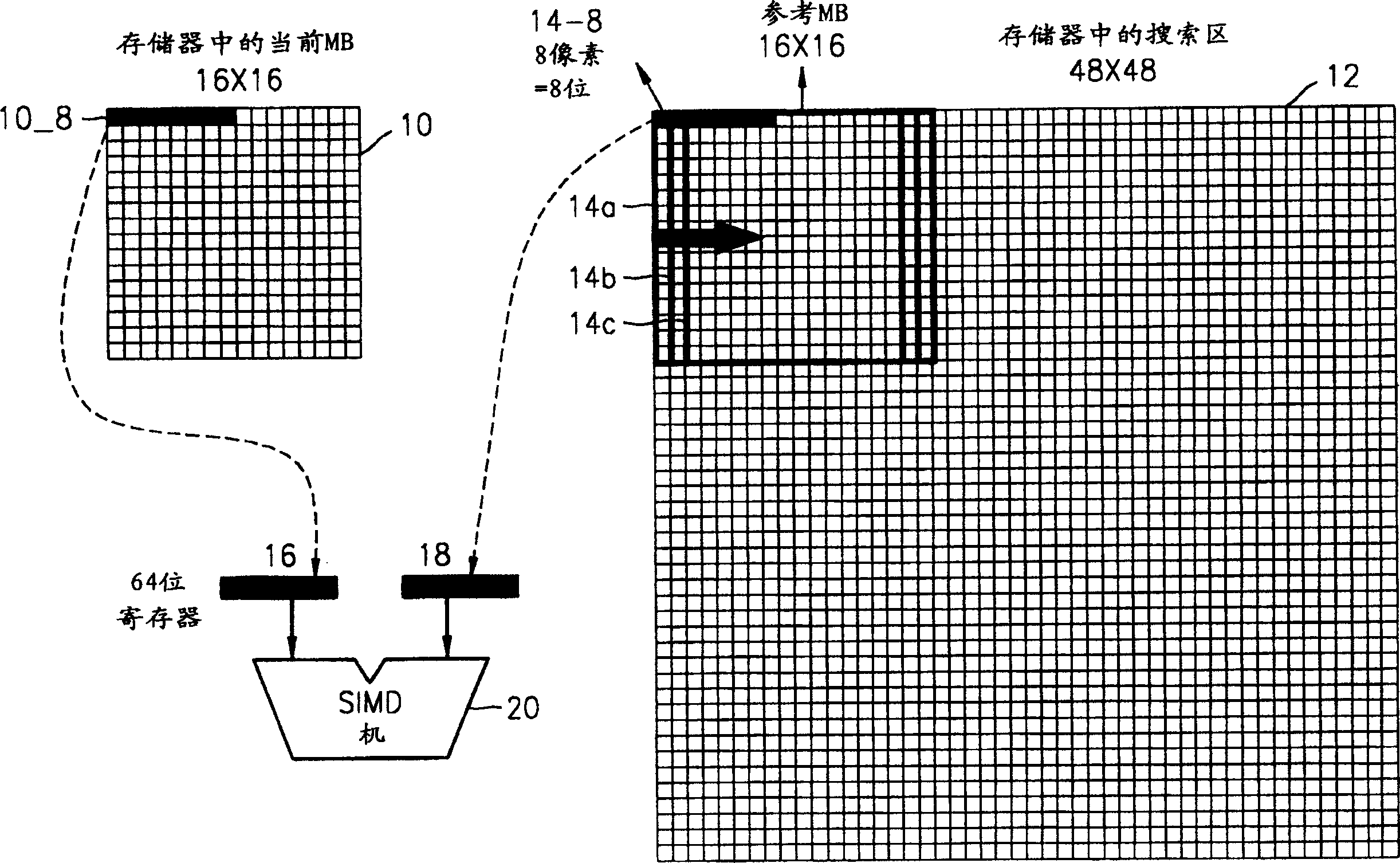

Moving estimating device and method for reference macro block window in scanning search area

InactiveCN1396762AReduce the number of instructionsTelevision system detailsDigital data processing detailsMotion vectorParallel computing

A motion estimation technique compares a current macroblock with different reference macroblocks in a reference frame search area. A motion vector for the current macroblock is derived from the reference macroblock most closely matching the current macroblock. To reduce the number of instructions required to load new reference macroblocks, overlapping portions between reference macroblocks are reused and only nonoverlapping portions are loaded into a memory storage device.

Owner:SAMSUNG ELECTRONICS CO LTD

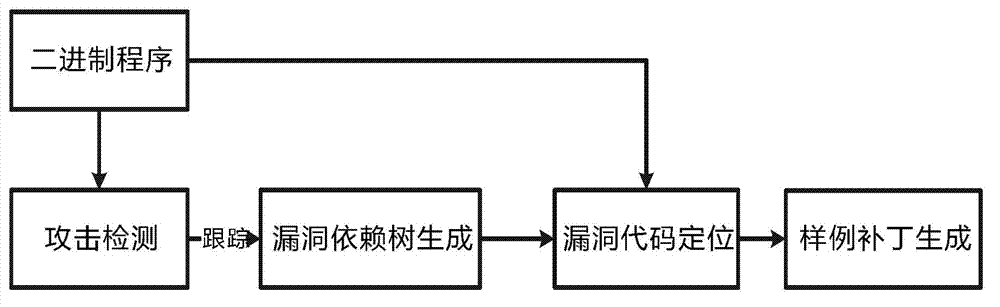

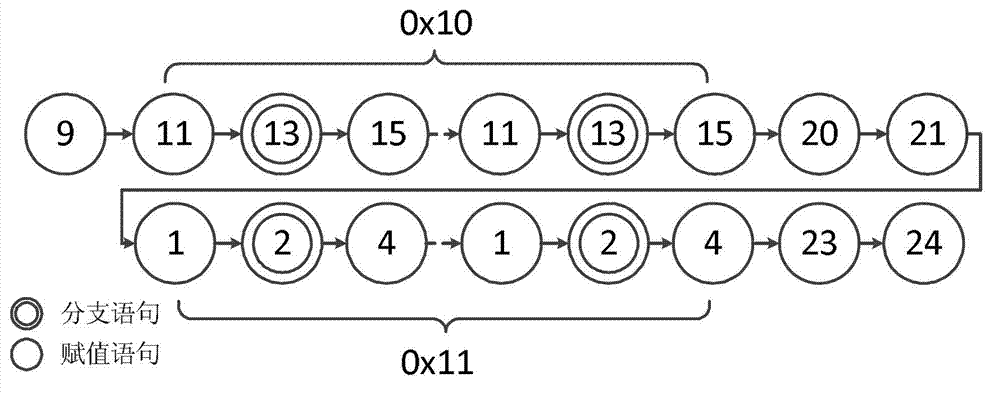

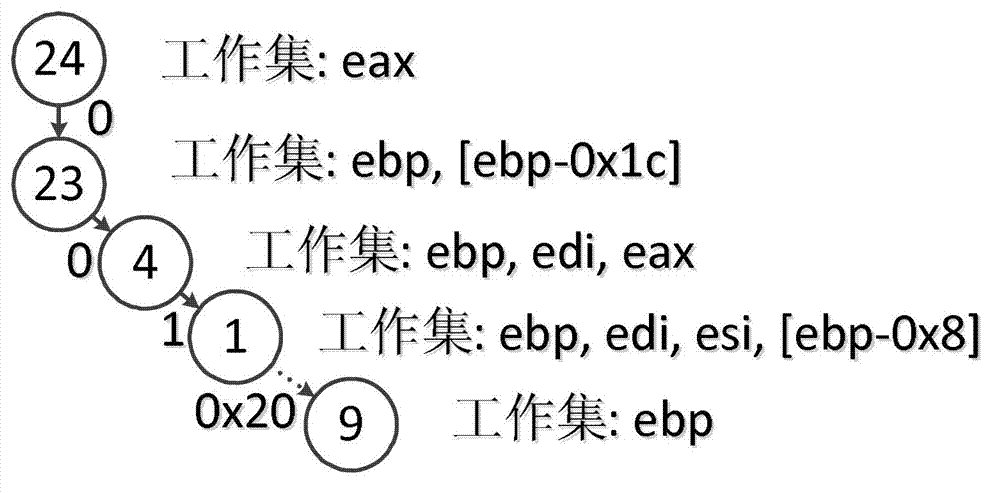

Automation positioning method for binary system program vulnerabilities

ActiveCN103198260AReduce the number of instructionsImprove analysis efficiencyPlatform integrity maintainanceSpecial data processing applicationsDependency treeOperating system

The invention discloses an automation positioning method for binary system program vulnerabilities. The method includes: 1) running a binary system program to be detected, and recording all instructions in the process from the time the program starts to run to the time an error occurs; 2) creating a vulnerability dependency tree according to the recorded instructions, and detecting a vulnerability instruction from the recorded instructions according to the created vulnerability dependency tree; in the process of creating the vulnerability dependency tree, checking whether a vulnerability candidate node appears every time a plurality of nodes are increased, if so, generating an interim fix for the vulnerability candidate node; and 3) observing whether the interim fix is effective, if so, stopping creating the vulnerability dependency tree and regarding the interim fix a basis for positioning a vulnerability position; and if not, continuing creating the vulnerability dependency tree. The automation positioning method for the binary system program vulnerabilities reduces the number of instruction needing to be analyzed and greatly improves the analysis efficiency.

Owner:INST OF INFORMATION ENG CAS

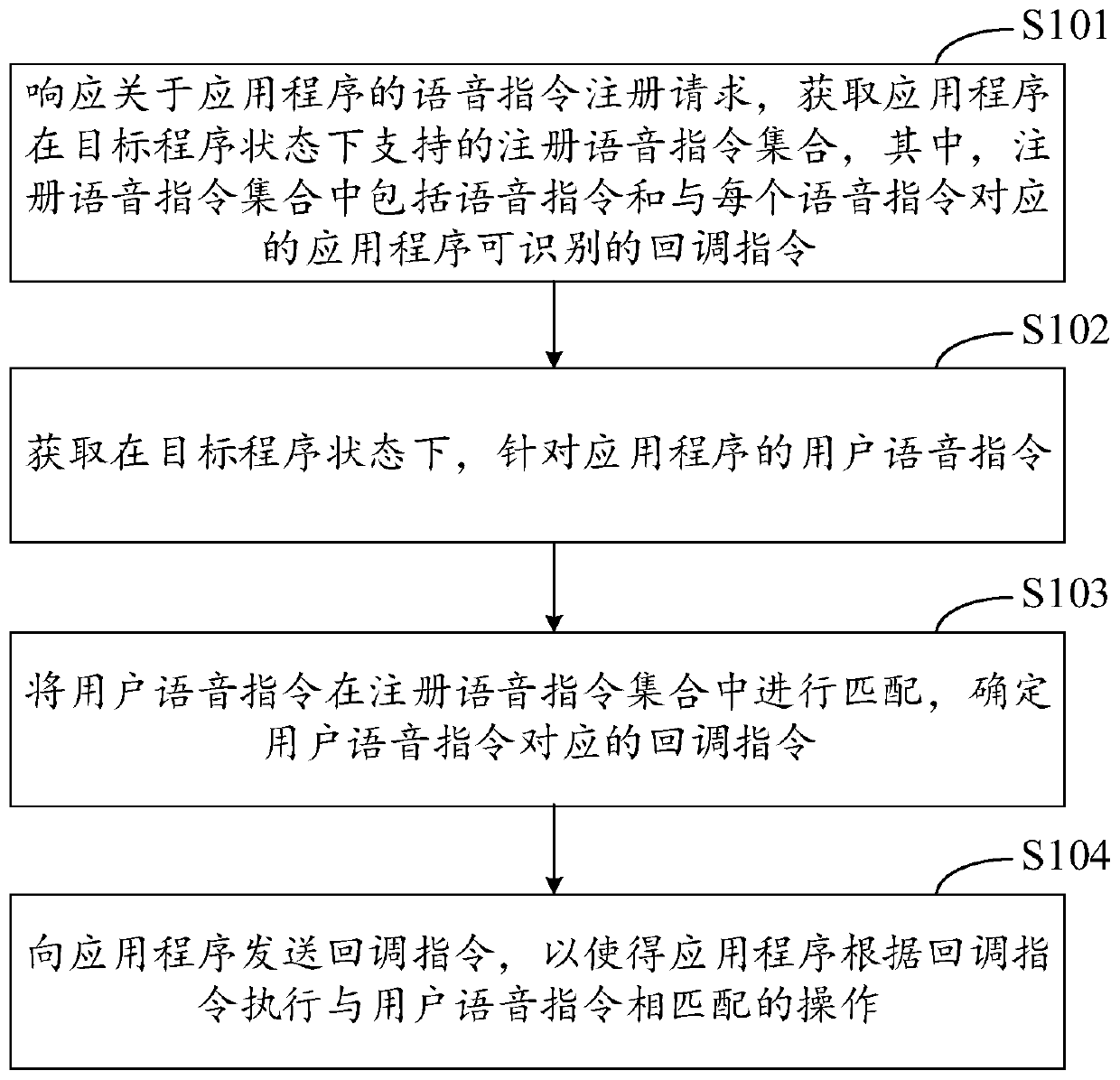

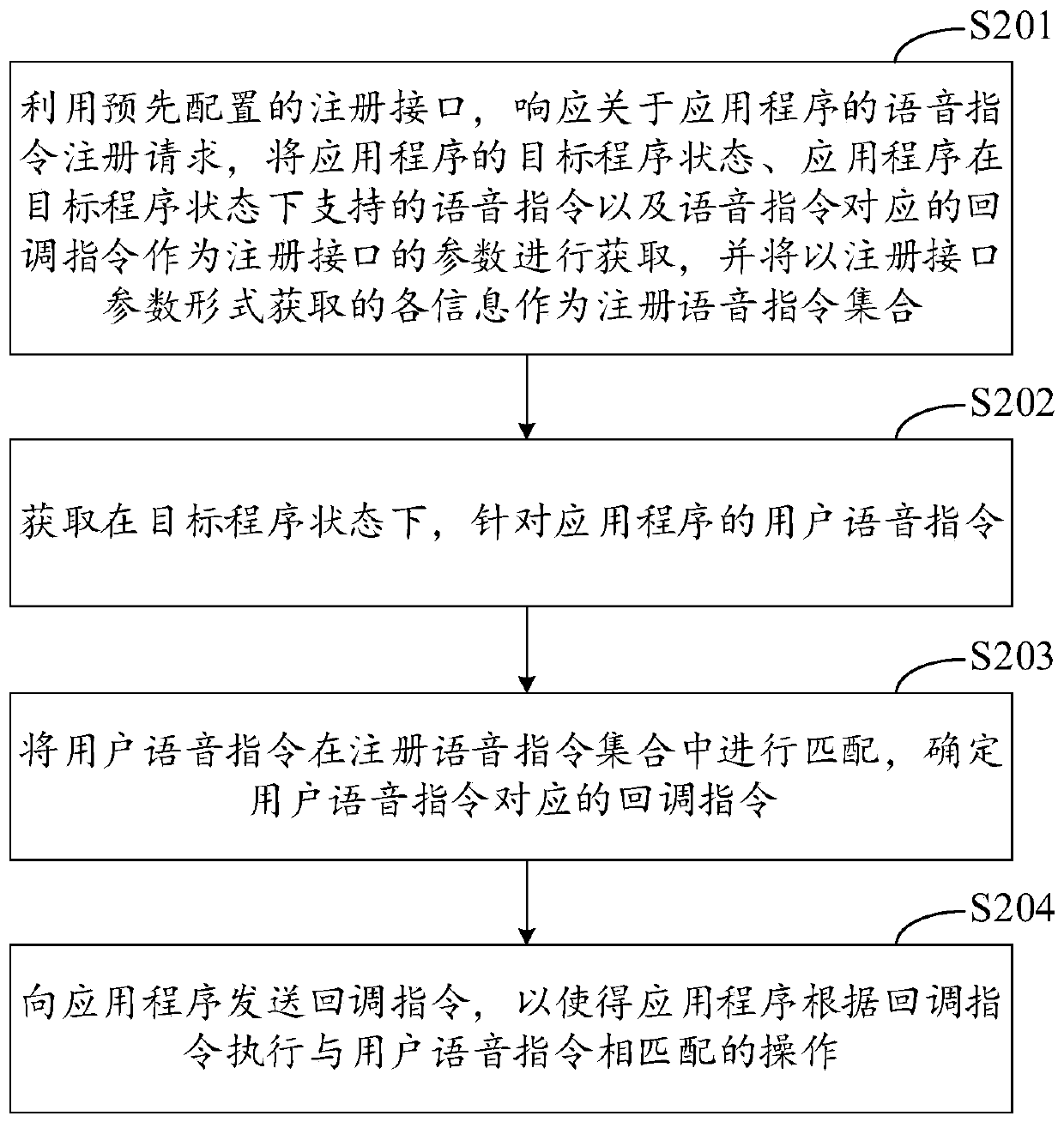

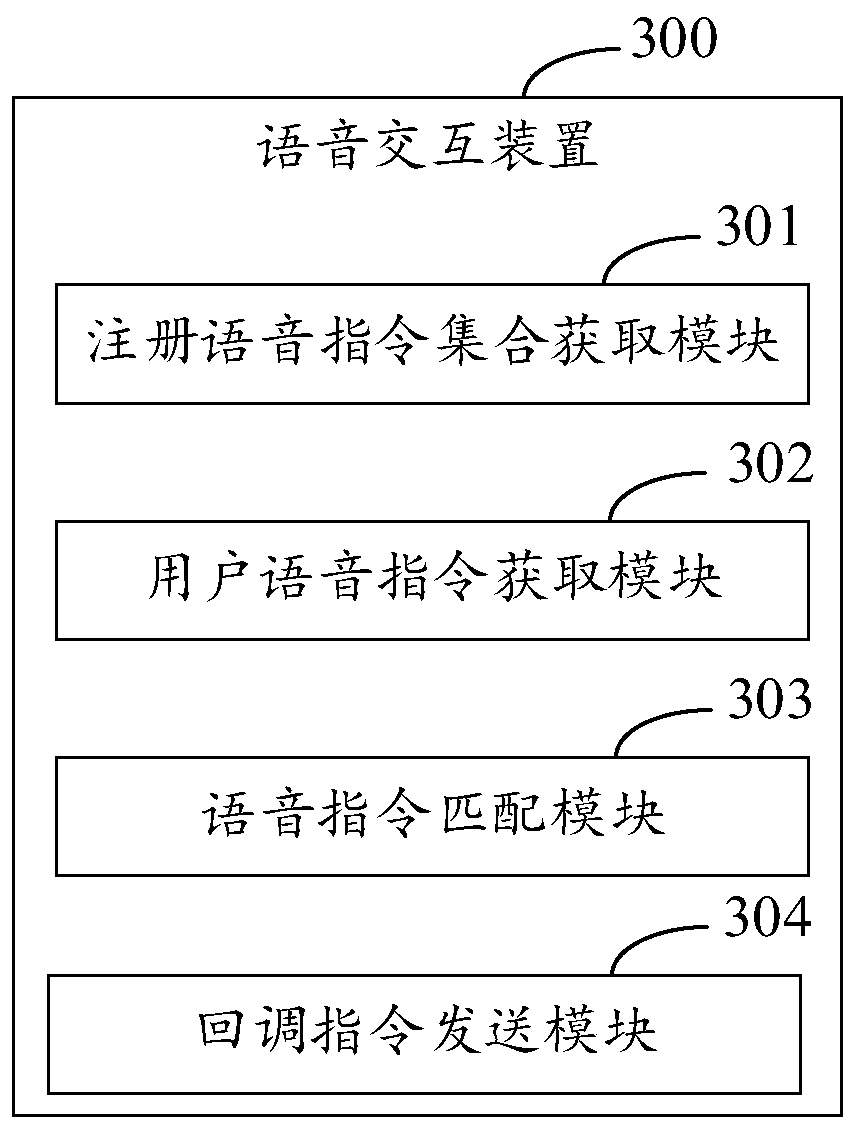

Voice interaction method and device of application program, equipment and medium

PendingCN110647305AImprove response efficiencyImprove recognition accuracySound input/outputCallbackApplication procedure

The embodiment of the invention discloses a voice interaction method and device of an application program, equipment and a medium, and relates to the technical field of voice. According to the specific implementation scheme, a voice instruction registration request about an application program is responded, a registration voice instruction set supported by the application program in a target program state is obtained, and the registration voice instruction set comprises voice instructions and callback instructions which correspond to the voice instructions and can be recognized by the application program; a user voice instruction is acquired for the application program in the target program state; the user voice instruction matches in a registered voice instruction set, and a callback instruction corresponding to the user voice instruction is determined; and a callback instruction is sent to the application to enable the application to execute an operation matched with the user voice instruction according to the callback instruction. According to the embodiment of the invention, the response accuracy of the user voice instruction can be improved, and the implementation process of the voice interaction function of each application program is simplified.

Owner:APOLLO INTELLIGENT CONNECTIVITY (BEIJING) TECH CO LTD

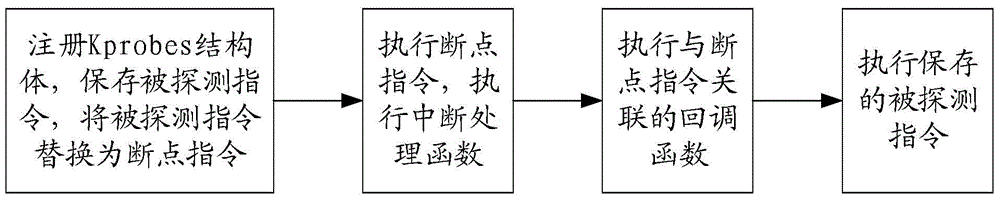

Kernel fault injection method and electronic device

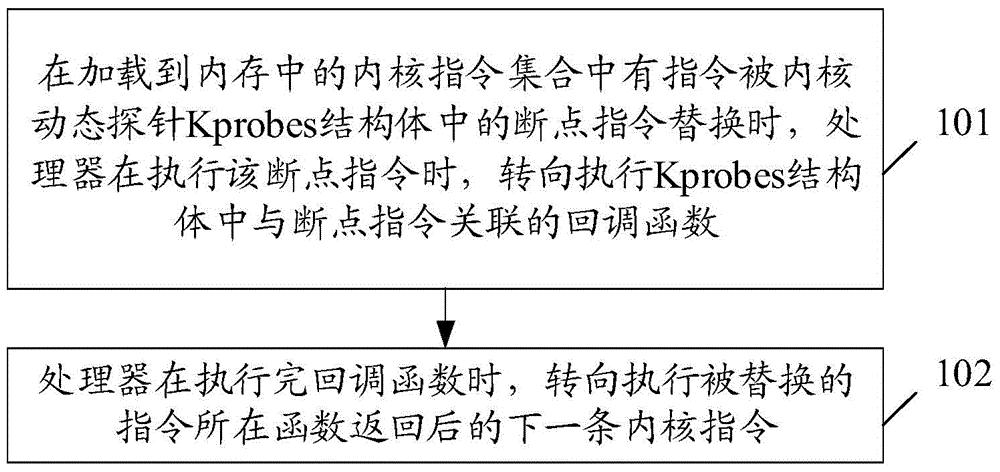

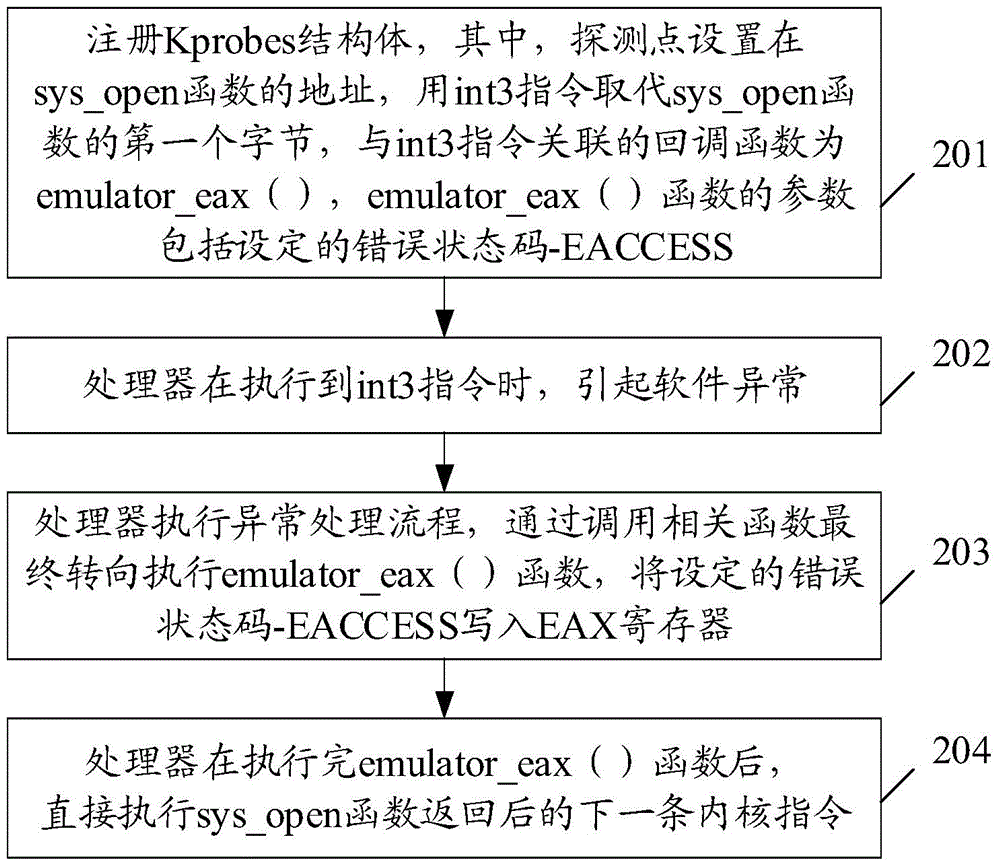

ActiveCN105528284AReduce the number of instructionsReduce waiting timeSoftware testing/debuggingInstruction setFault injection

The invention discloses a kernel fault injection method and an electronic device. The kernel fault injection method is used for solving a technical problem that the latency time for fault injection is long. The kernel fault injection method comprises following steps: when an instruction in a kernel instruction set loaded in a memory is replaced by a breakpoint instruction in a Kprobes (kernel dynamic probes) structure, a processor turns to execute a callback function in the Kprobes structure and related to the breakpoint instruction when the processor executes the breakpoint instruction; and when the processor completes the execution of the callback function, the processor turns to execute a next kernel instruction after a function where the replaced instruction is located returns.

Owner:HUAWEI TECH CO LTD

A neural network processing apparatus and a method thereof for performing a matrix vector multiplication instruction

InactiveCN108960418AFunction increaseEasy to useProgram controlPhysical realisationOperational costsLow power dissipation

The invention provides a processing apparatus comprising a memory, a register unit, an operation unit and a control unit; the memory stores vectors; the register unit stores a matrix vector multiplication instruction; the control unit acquires the matrix vector multiplication instruction; the matrix vector multiplication instruction is analyzed to obtain an operation a code and an operation field;matrix vector multiplication operational data is obtained from the memory according to the operation code; and the operation unit performs matrix vector multiplication on the data participating in the matrix vector multiplication operation. The technical scheme provided by the invention has advantages of low power dissipation and low operational cost.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

Neural network processing apparatus and method for executing vector minimum value instruction thereof

ActiveCN109032669AFunction increaseEasy to useInstruction analysisEnergy efficient computingNetwork processingComputer science

The invention provides a processing device, comprising a memory, a register unit, an arithmetic unit and a control unit, a memory storage vector. The register unit stores vector minimum value instruction, the control unit obtains vector minimum value instruction, and parses the vector minimum value instruction to obtain an operation code and an operation field. The operation data of the minimum value of the participating vector is obtained from the memory according to the operation code; an arithmetic unit performs vector minimum value arithmetic on data participating in vector minimum value arithmetic. The technical proposal provided by the invention has the advantages of low power consumption and low calculation cost.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

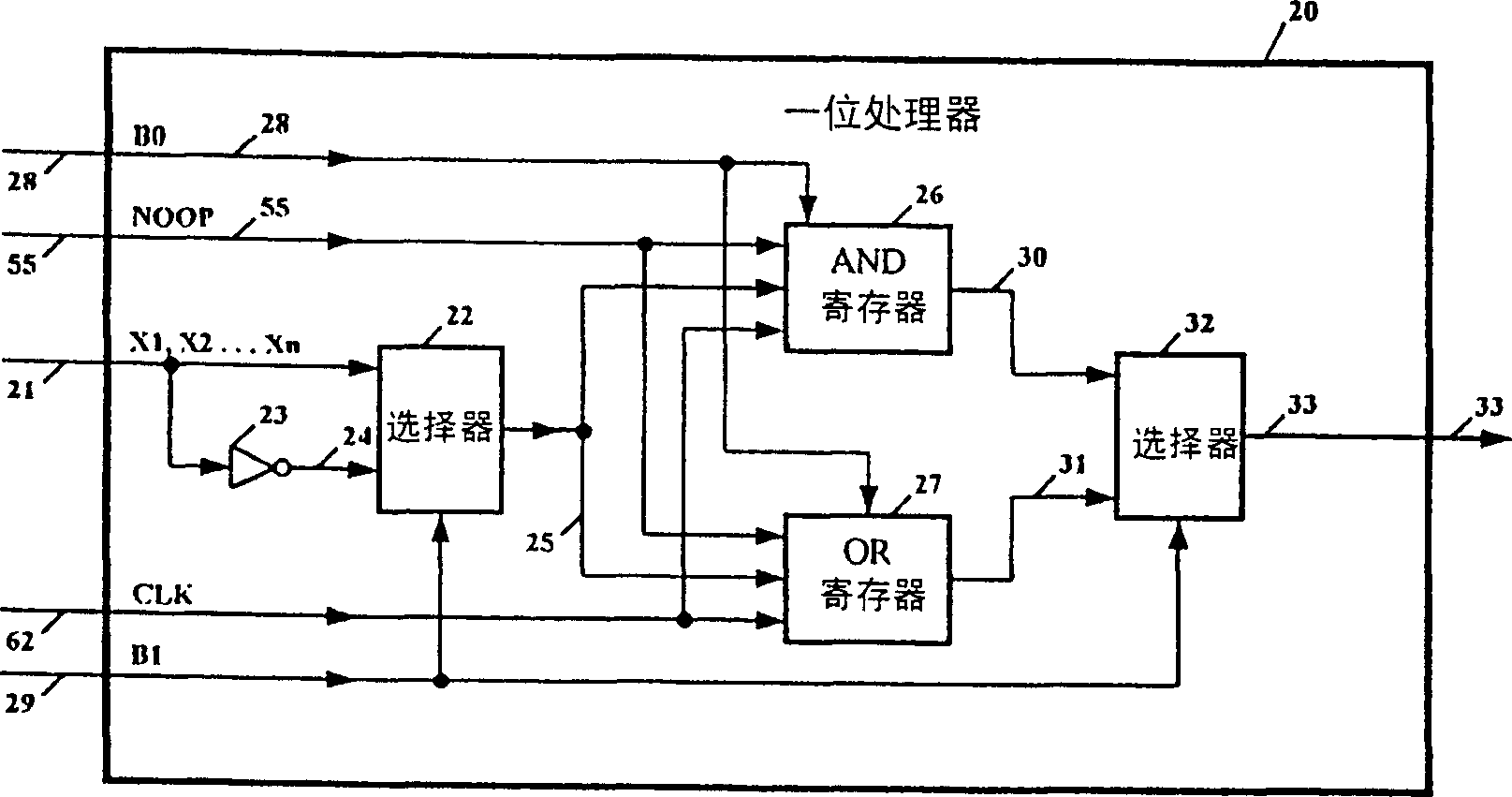

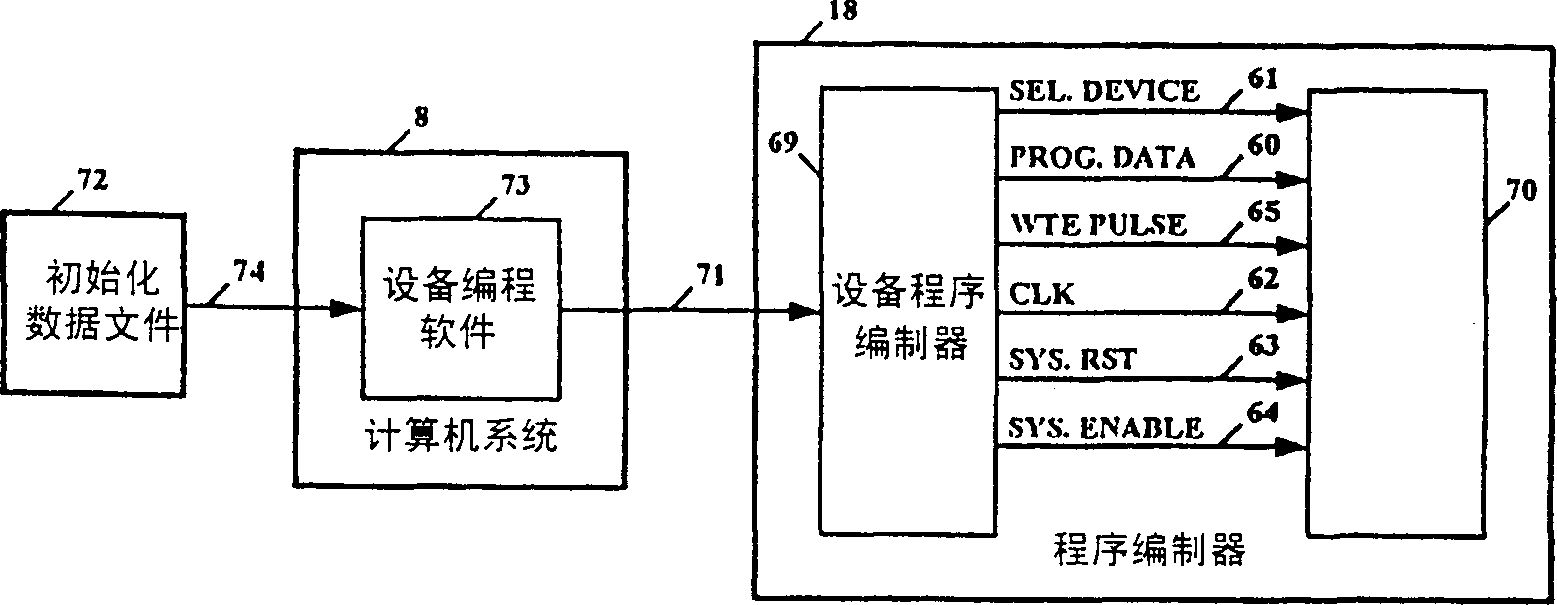

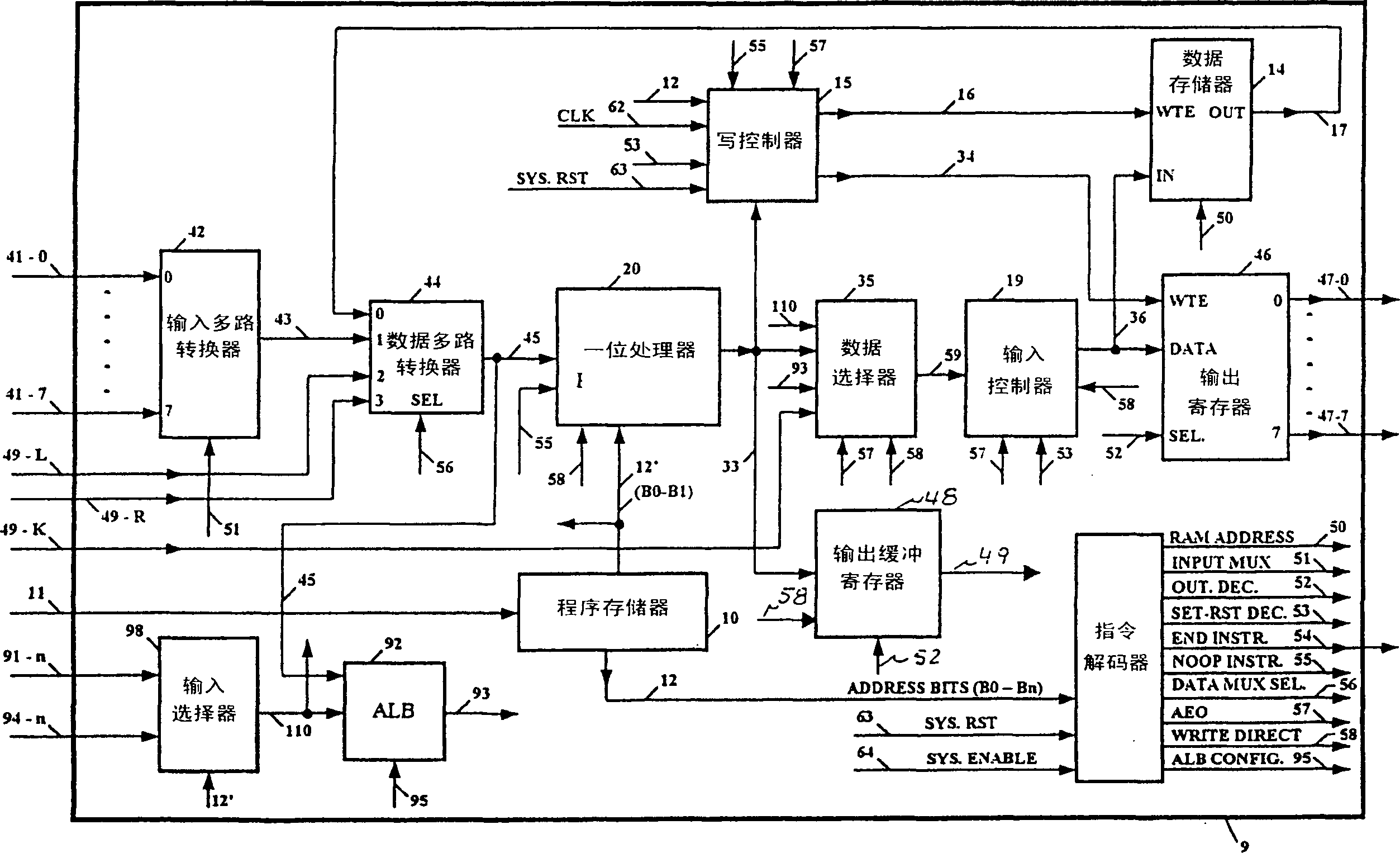

Digital circuit implementation by means of parallel sequencers

InactiveCN1422406AReduce the number of instructionsIncrease clock speedSingle instruction multiple data multiprocessorsMultiple digital computer combinationsControl signalData memory

A system for designing and implementing digital integrated circuits utilizing a set of synchronized sequencers that permit quick and efficient parallel processing of system level designs. The system and method converts digital schematics and hardware description language (HDL) based designs into a set of logic equations and single bit arithmetic-logic operations executed by a set of parallel operating sequencers. The system includes software for converting netlists and DHL designs into Boolean logic equations, and a compiler for distributing these logic equations between multiple sequencers. Each sequencer is comprised of a logic processor and the associated program memory for storing the executable code of the assigned Boolean logic equations and data memory for storing the results of processing of logic equations. To synchronize execution of logic equations by multiple sequencers, all program memories are addressed by one common address register. The processing of logic equations is arranged in such a manner that their outputs can be read by synchronized read instructions in the interconnected sequencers, eliminating any need for control signals.

Owner:斯坦利 M 海杜克

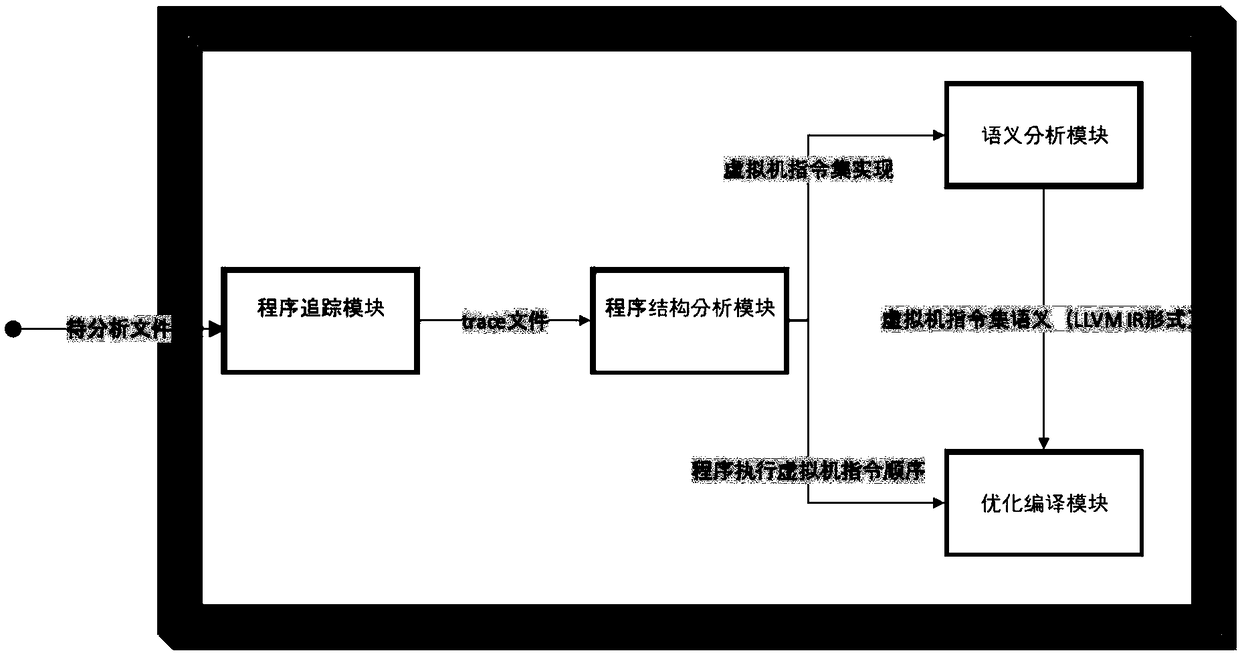

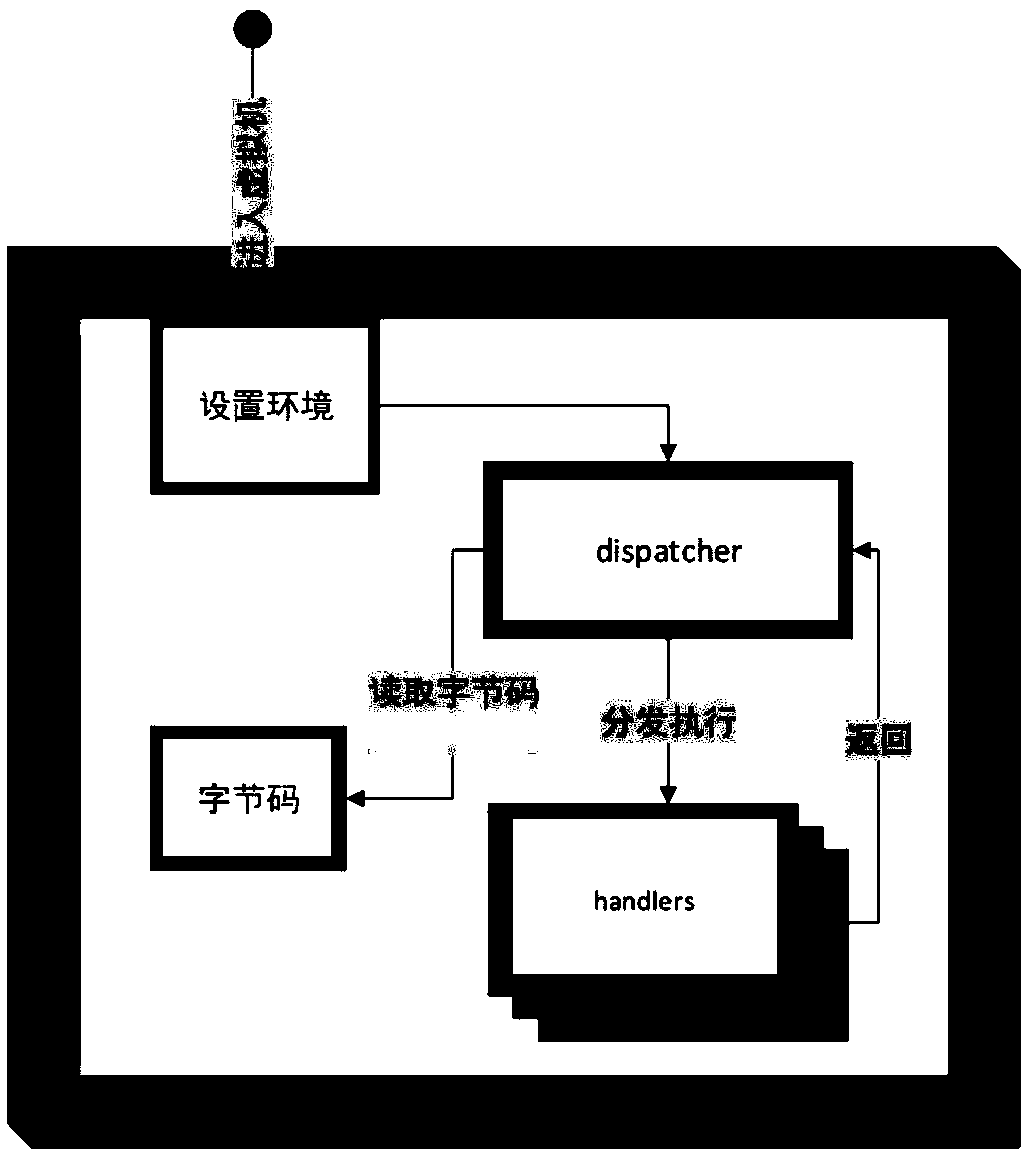

Anti-obfuscation system and method for software virtual machine protection

ActiveCN109145534AReduced number of code instructions to executeReduce the number of instructionsProgram/content distribution protectionSoftware simulation/interpretation/emulationObfuscationReverse analysis

The invention relates to an anti-confusion system and a method for software virtual machine protection. After a program is traced and a tracing file is obtained, a heuristic analysis strategy is adopted to analyze a trace file to obtain a software virtual machine instruction set; then the semantics is extracted from the instruction set of the virtual machine; finally, anti-obfuscation is realizedby rewriting and optimizing compilation. The invention aims at the program protected by the commercial software virtual machine vmprotect, the instructions executed by the optimized program are reduced by 2 / 3 on average, and the program is easy to be modified, thus overcoming the defect of the prior software virtual machine reverse analysis method.

Owner:SHANGHAI JIAO TONG UNIV

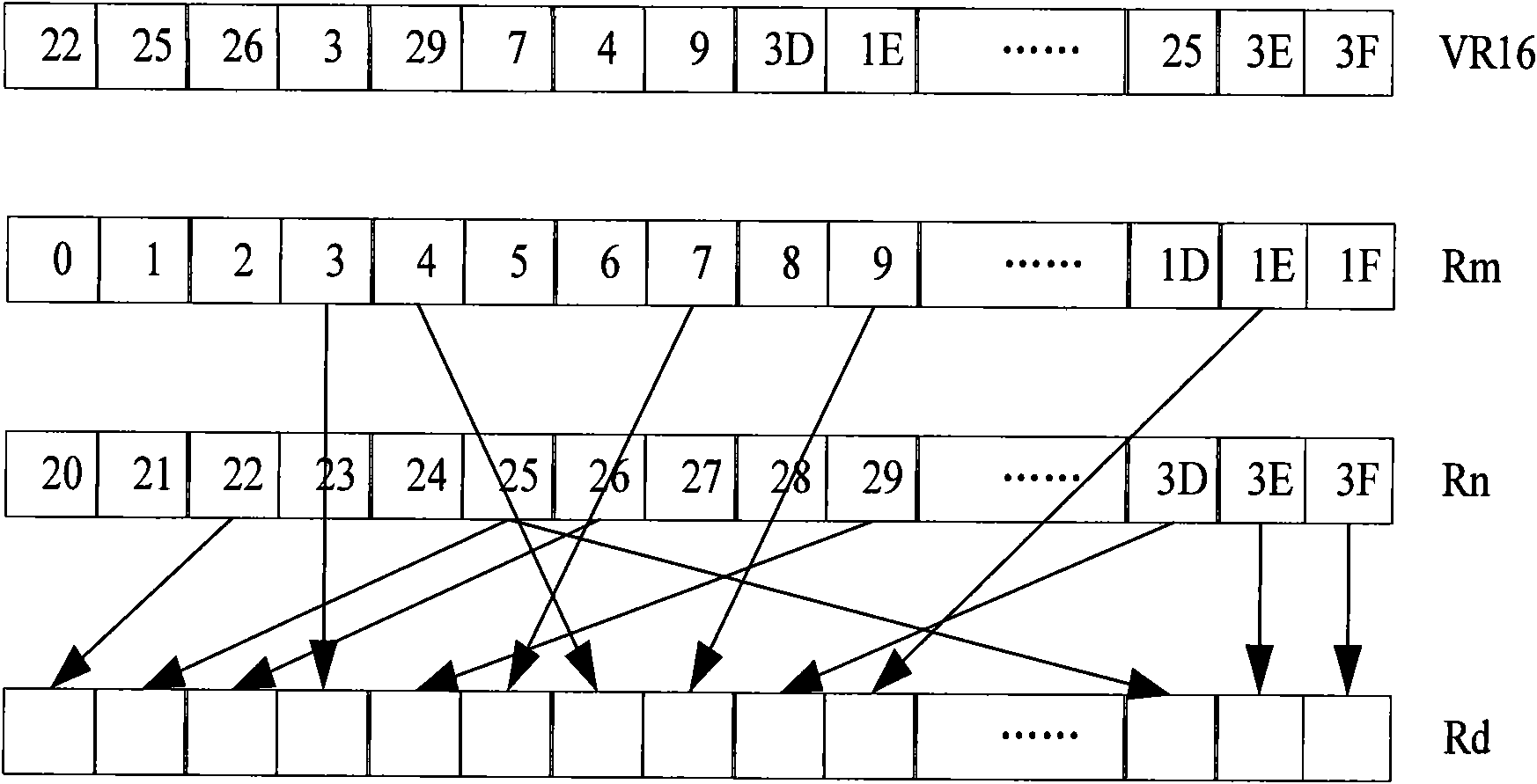

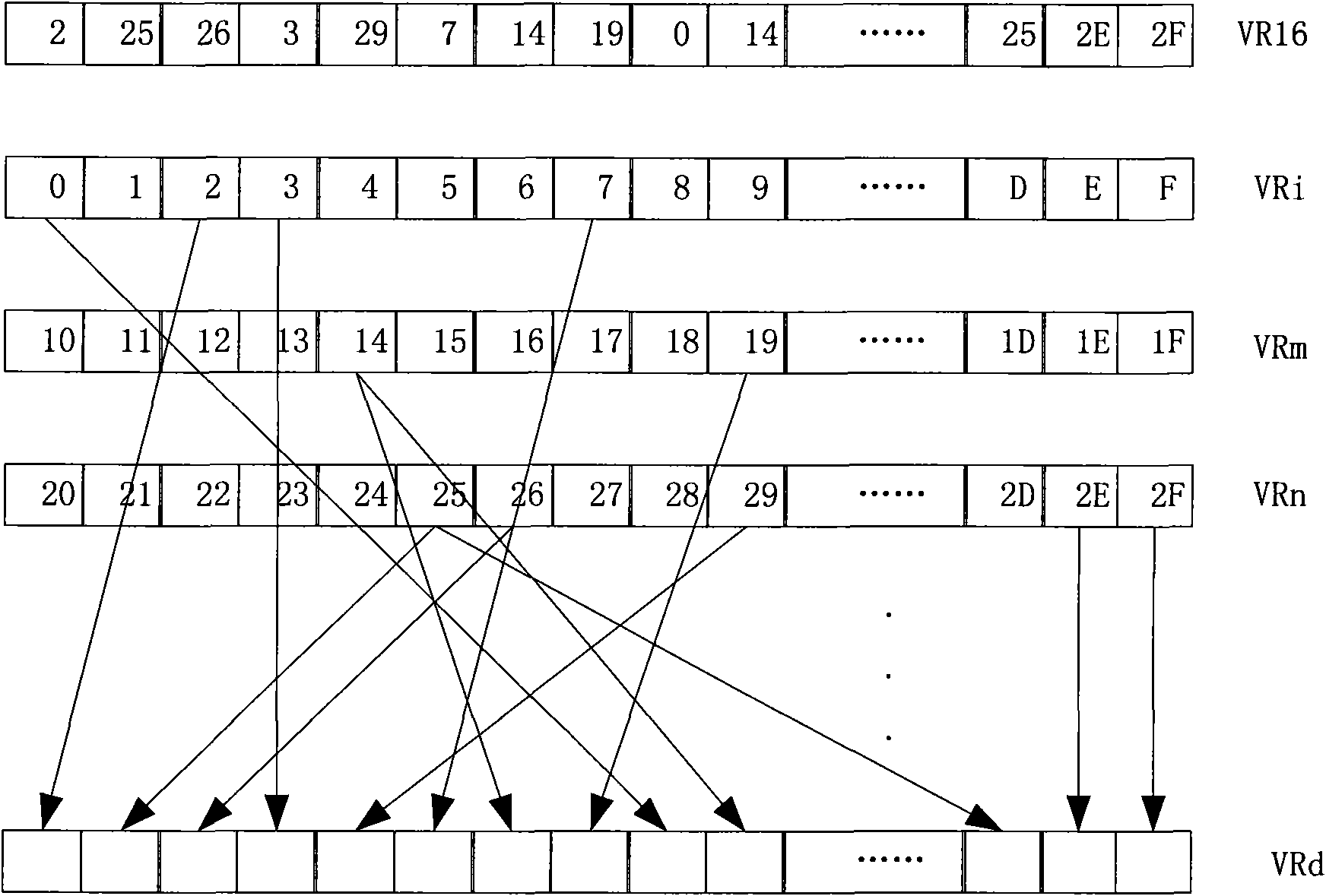

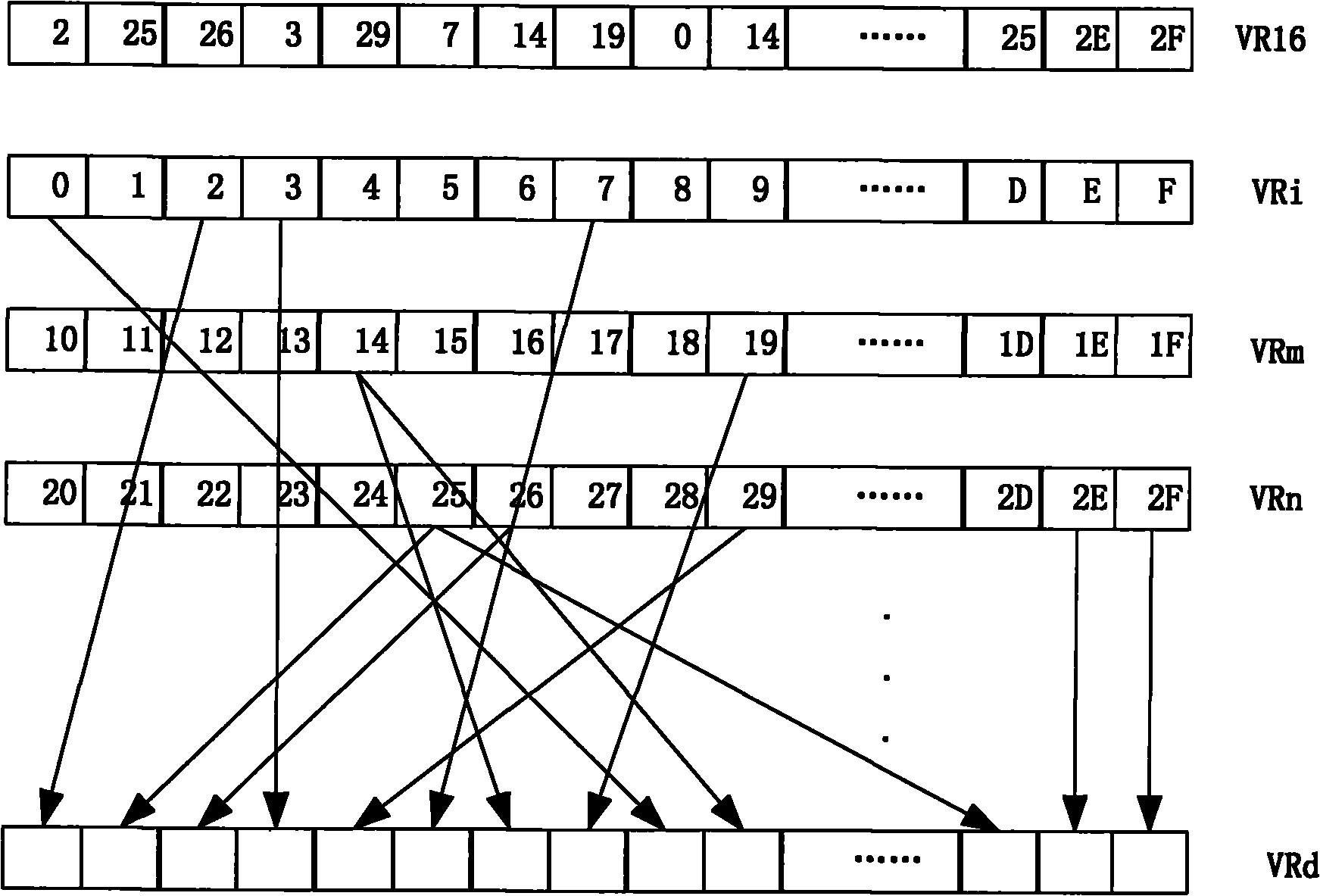

Method for shuffling byte nepit data

InactiveCN102253824AFast executionReduce the number of instructionsConcurrent instruction executionProcessor registerPosition Number

The invention discloses a method for shuffling byte nepit data. The method comprises the steps of: storing byte data to be shuffled in at least two source registers; storing a position number in which the byte data to be shuffled with the quantity same as that of the data stored by a configuration register in the configuration register is located; and shuffling the byte data in the at least two source registers one by one according to the position number in the configuration register. By adopting the technical scheme disclosed by the invention, one source, two sources or three sources can be supported to be shuffled, multi-source shuffling operation is supported, the quantity of commands required in the multi-source data reconfiguration application can be reduced, executing speed of a processor is increased, partial data in a destination register is supported for maintaining and zero clearing, and other parts of normally received and shuffled data and data in the source register are kept unchangeable.

Owner:江苏芯动神州科技有限公司

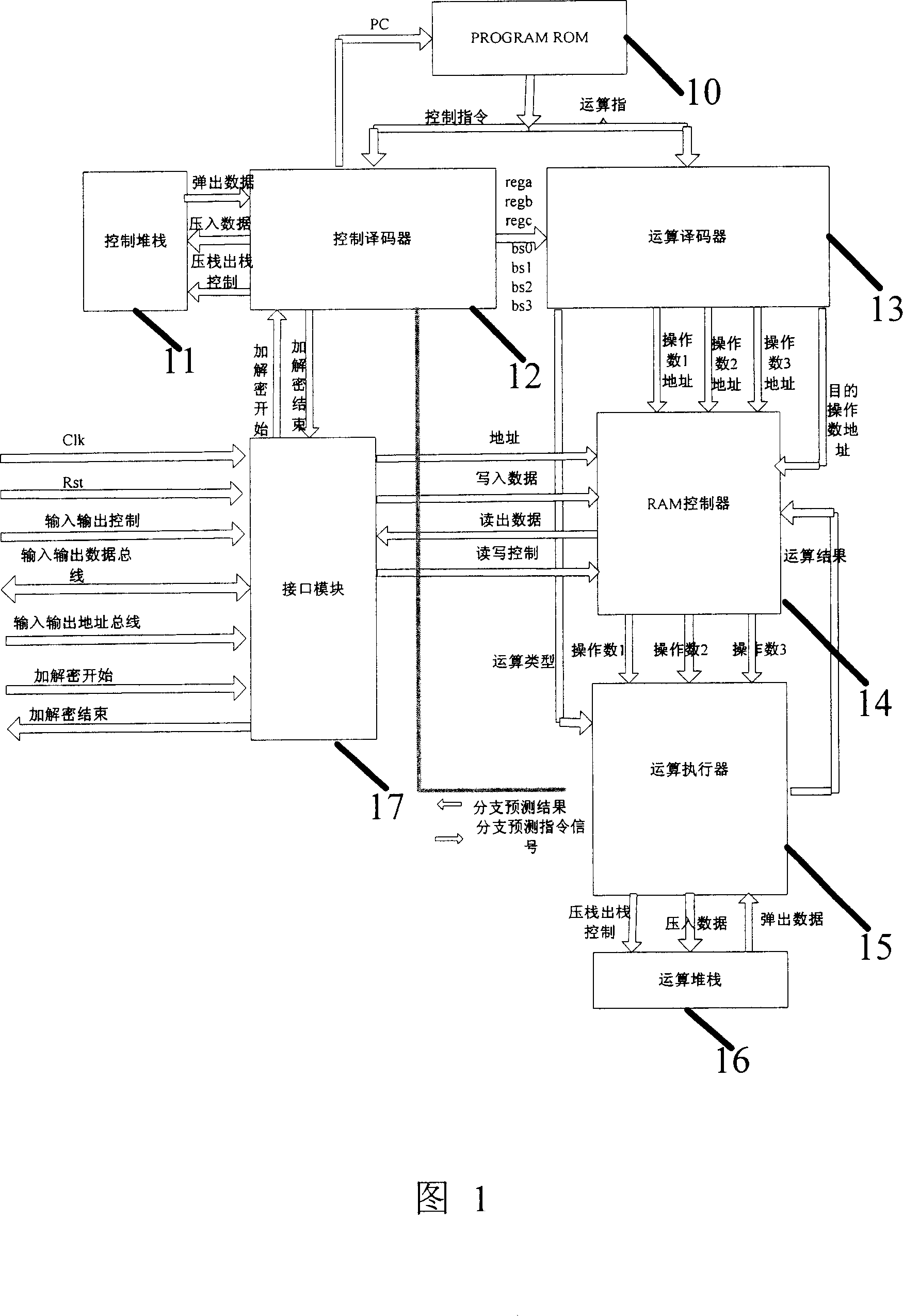

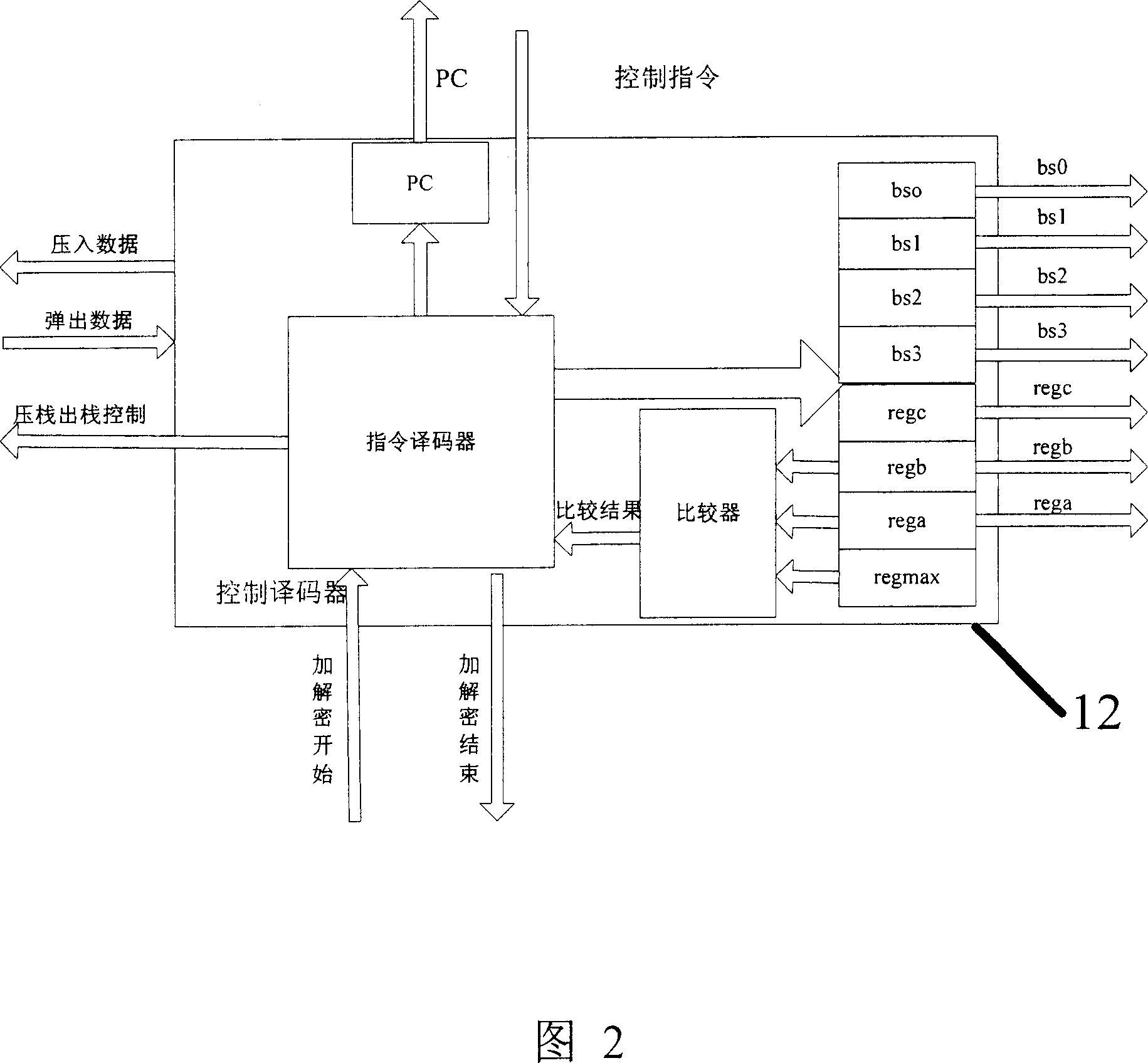

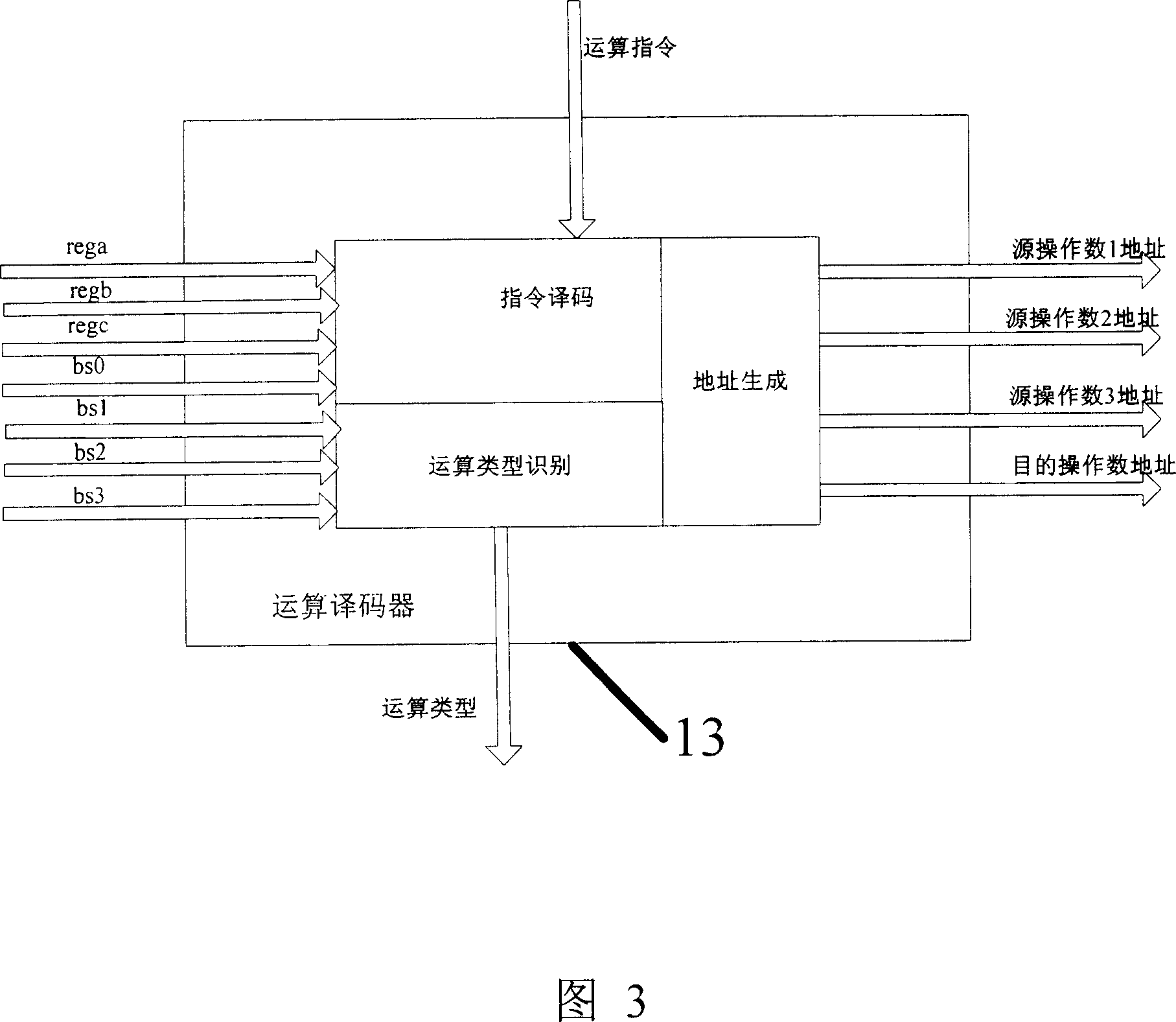

Programmable security processor

InactiveCN1959694AEasy to implementShorten the timeMultiple keys/algorithms usageInternal/peripheral component protectionEmbedded applicationsComputer module

A programmable safety processor consists of program storage, control stack, control decoder, operation decoder, RAM controller, operation executor, operation stack and interface module. It is featured as supporting programmable structure, setting with some basic operation units and utilizing program control and said basic operation unit to realize multiple ciphering deciphering / algorithm.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

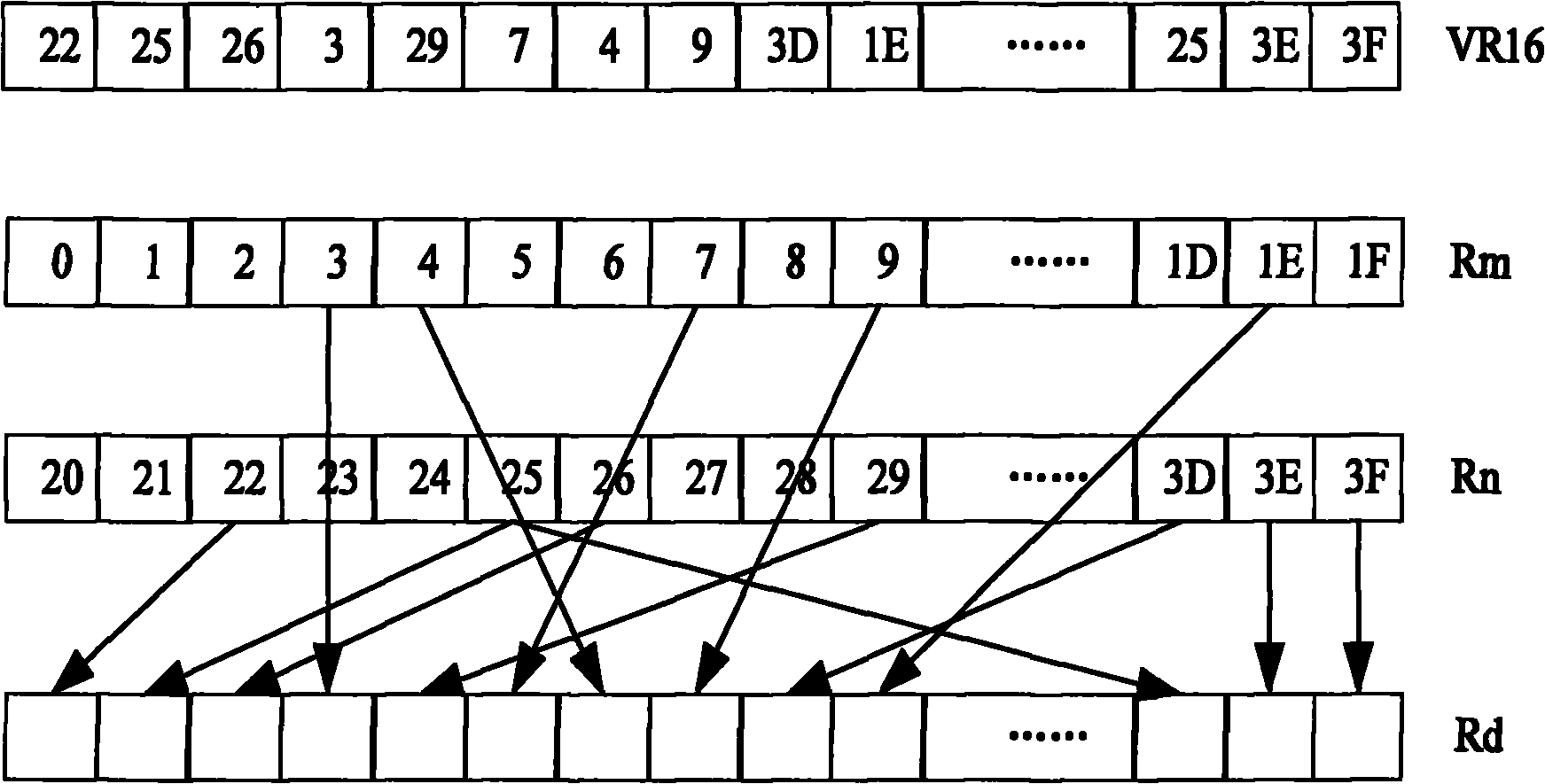

Data shuffling method

InactiveCN102253823AFast executionReduce the number of instructionsMemory systemsMachine execution arrangementsProcessor registerPosition Number

The invention discloses a data shuffling method, which comprises the following steps of: storing data to be shuffled in two or more source registers; storing a position number, equal to the number of data which can be stored by a configuration register, of the data to be shuffled into the configuration register; and shuffling the data in the two or more source registers one by one according to the position number in the configuration register. By adoption of the technical scheme of the invention, the shuffling of one source, two sources or three sources can be supported; the number of instructions required by rearrangement application of multi-source data can be reduced by supporting multi-source shuffling operation; the execution speed of a processor is improved; maintenance of a part of data in a target register is supported; other parts of shuffled data are normally received; and the data in the source registers keeps invariable.

Owner:江苏芯动神州科技有限公司

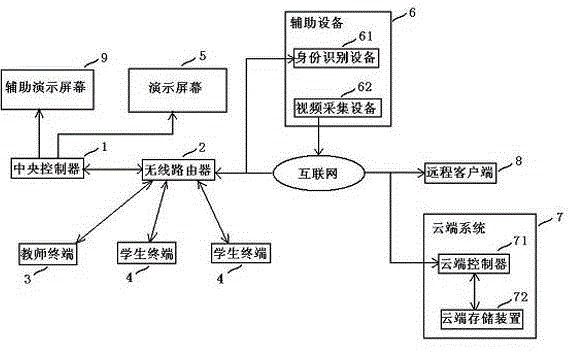

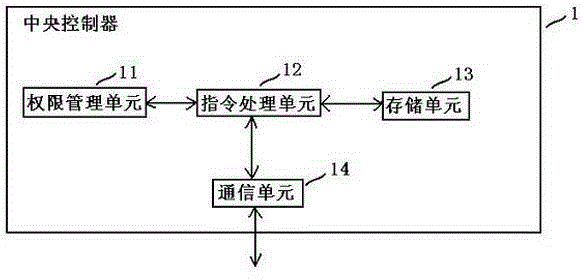

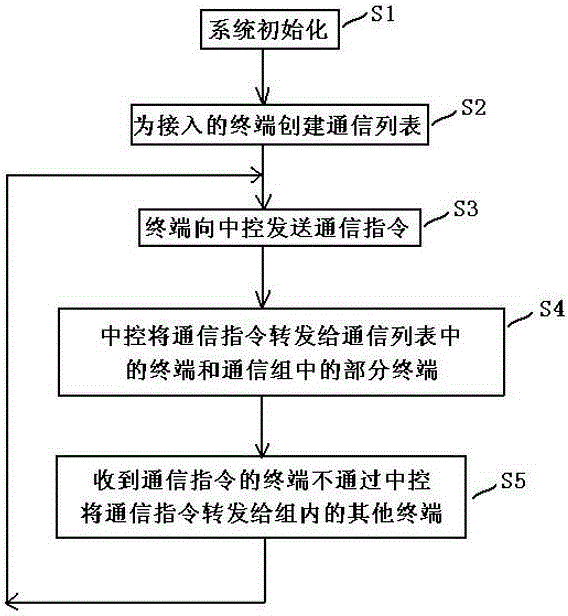

Multimedia information interactive system and interactive method

InactiveCN105376201AImprove experienceImprove convenienceSpecial service provision for substationDigital data authenticationTelecommunicationsTelecommunications link

The present invention provides a multimedia information interactive system which comprises multiple terminals which carry out communication through a central controller, the central controller which forwards the communication requests of the terminals, and a communication link which is connected among the terminals and is connected between the terminals and the central controller. The central controller maintains the communication list comprising the information of target terminals and / or a target communication group for each terminal. When a source terminal carries out communication, a communication signaling is sent to the central controller, and the central controller sends the communication signaling to the target terminals in the communication list of the source terminal and a part of target terminals in the target communication group. A part of the target terminals forward the communication content in the communication signaling to other target terminal in the communication group without the central controller. The invention also provides a multimedia information interactive method.

Owner:TVM BEIJING EDUCATION SCI & TECH CO LTD

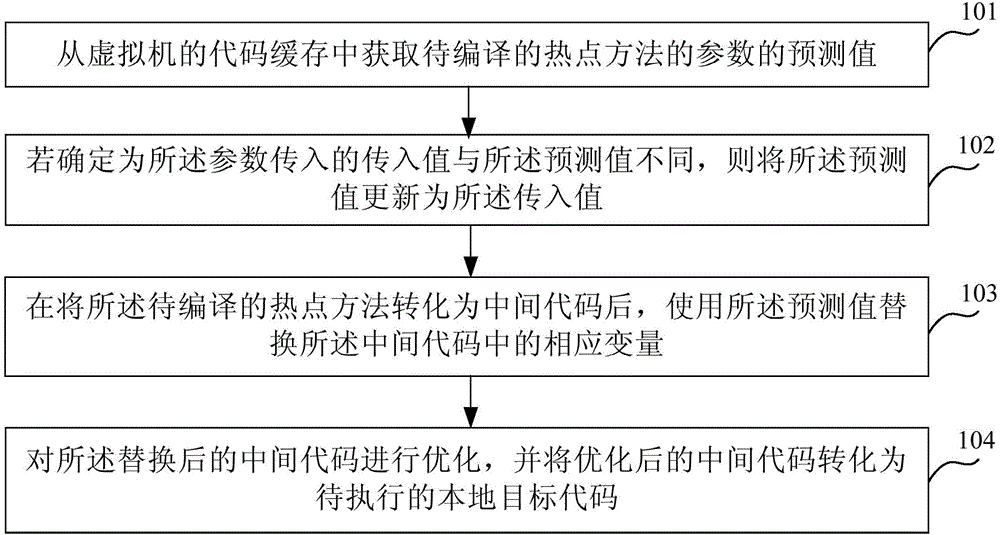

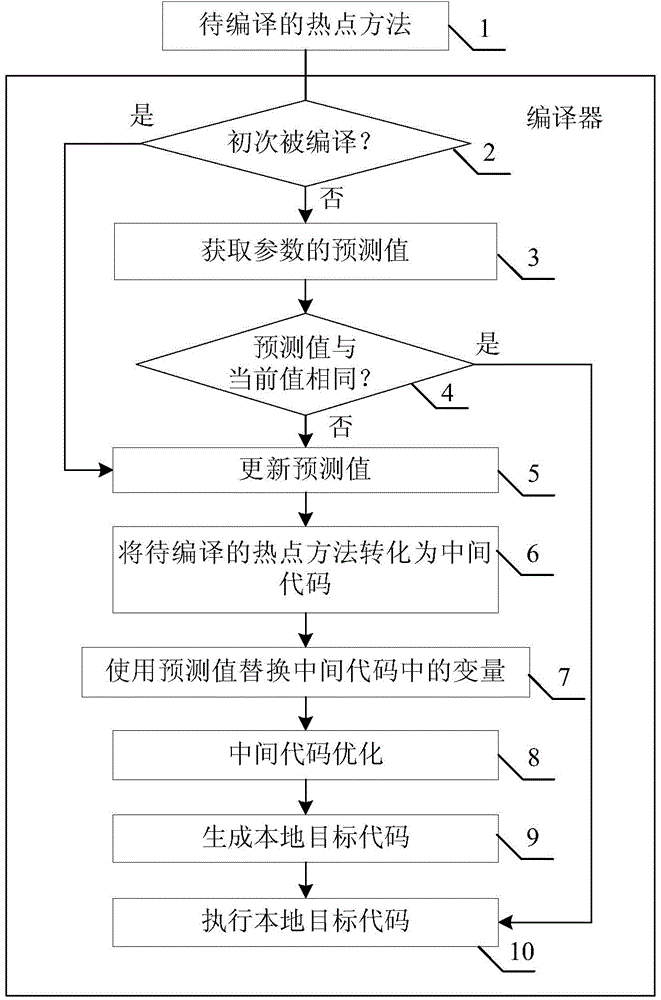

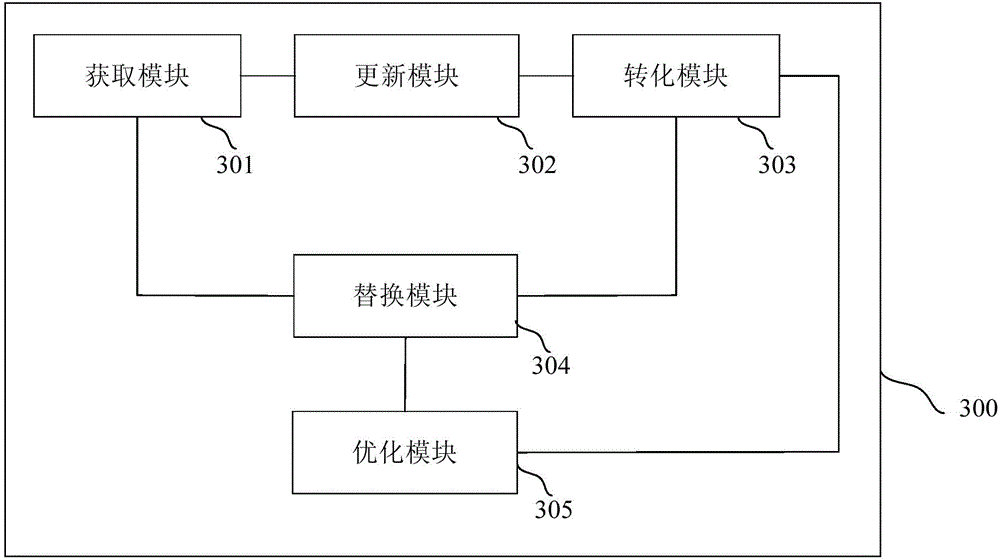

Dynamic compilation method and apparatus

ActiveCN105988854AReduce the number of instructionsSmall scaleProgram controlMemory systemsDynamic compilationParallel computing

Embodiments of the invention provide a dynamic compilation method and apparatus. The method comprises the steps of obtaining a predicted value of a parameter of a to-be-compiled hotspot method from a code cache of a virtual machine; if it is determined that an input value of parameter input is different from the predicted value, updating the predicted value to the input value; replacing a corresponding variable in an intermediate code with the predicted value after converting the to-be-compiled hotspot method into the intermediate code; and optimizing the replaced intermediate code and converting the optimized intermediate code into a to-be-executed local target code. According to the dynamic compilation method and apparatus provided by the embodiments of the invention, the scale of codes generated by compilation can be reduced and the system performance of the virtual machine can be improved.

Owner:LOONGSON TECH CORP

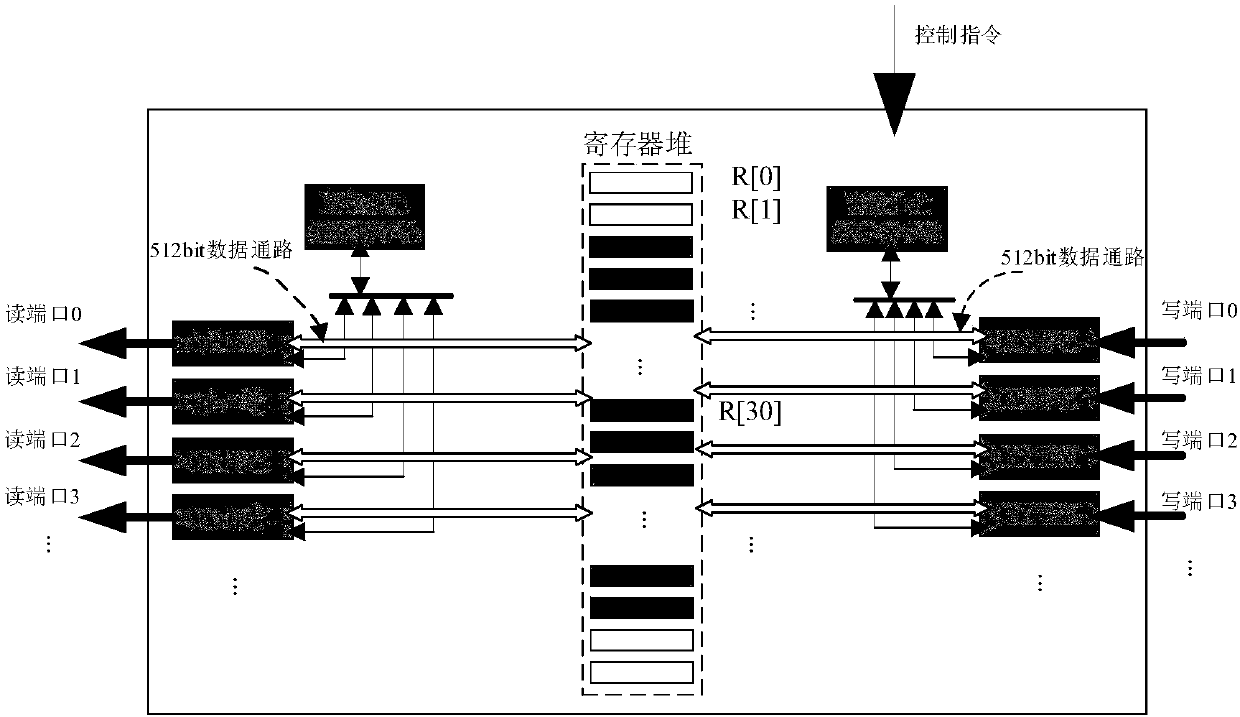

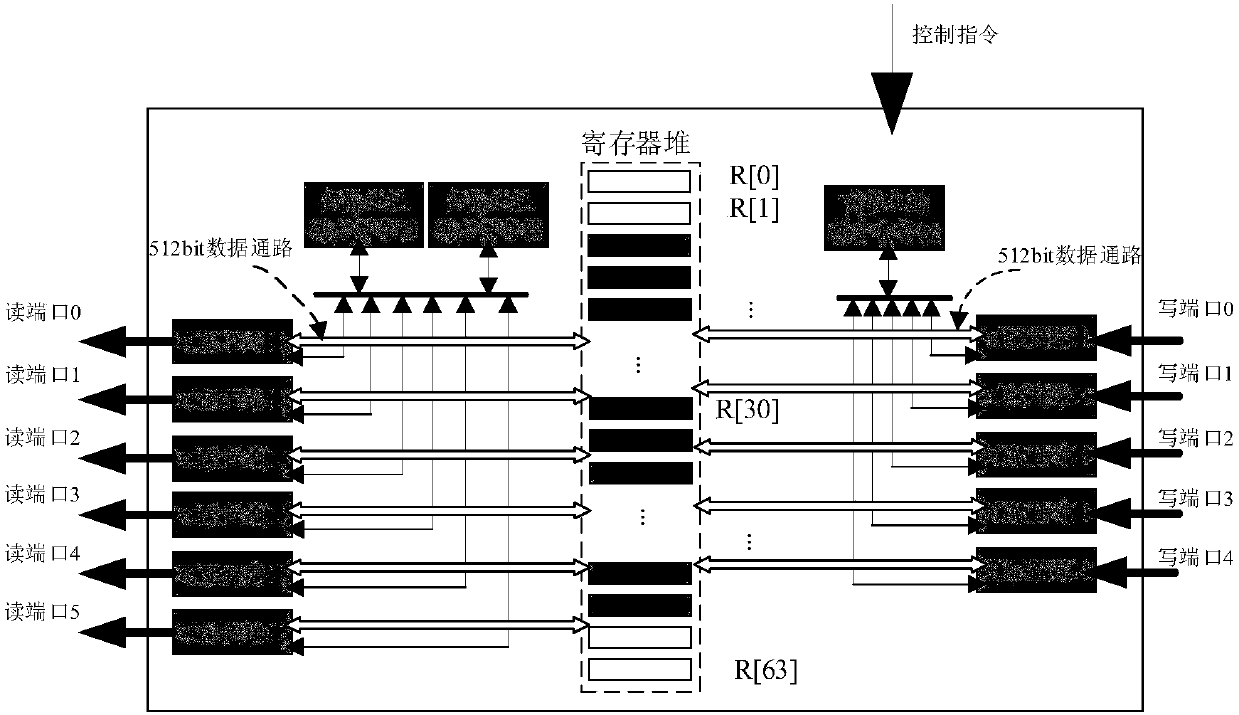

Configurable register and data access method based on same

ActiveCN110018847AImprove reading and writing efficiencyShorten the lengthRegister arrangementsAccess methodProcessor register

The invention provides a configurable register and a data access method based on the configurable register. The configurable register comprises a register file, a plurality of configurable ports and adiscrete address cache register, wherein the register file comprises a plurality of vector data registers for storing the vector data to be accessed and a decoder for decoding an externally inputtedcontrol instruction to execute the control instruction, the configurable port comprises a plurality of read ports and a plurality of write ports and is used for configuring the preset parameters according to the first address configuration information in the control instruction, generating a first data access address and caching the first data access address, obtaining the second address configuration information from the discrete address cache register, calculating a second data access address, and reading / writing the corresponding discrete data into the register file according to the seconddata access address, and the discrete address cache register comprises at least one read address register and at least one write address register and is used for caching the second address configuration information in the control instruction.

Owner:BEIJING SMART LOGIC TECH CO LTD

Neural network processing apparatus and method for executing vector copy instructions thereof

ActiveCN109032670AFunction increaseEasy to useProgram controlPhysical realisationNetwork processingControl unit

The invention provides a processing device, comprising a memory, a register unit, an arithmetic unit and a control unit, a memory storage vector. The register unit stores vector copy instructions, thecontrol unit obtains vector copy instructions, and analyzes the vector copy instructions to obtain an operation code and an operation field. Vector copy operation data from a memory is obtained according to the operation code; an arithmetic unit performs a vector copy operation on the data participating in the vector copy operation. The technical proposal provided by the invention has the advantages of low power consumption and low calculation cost.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

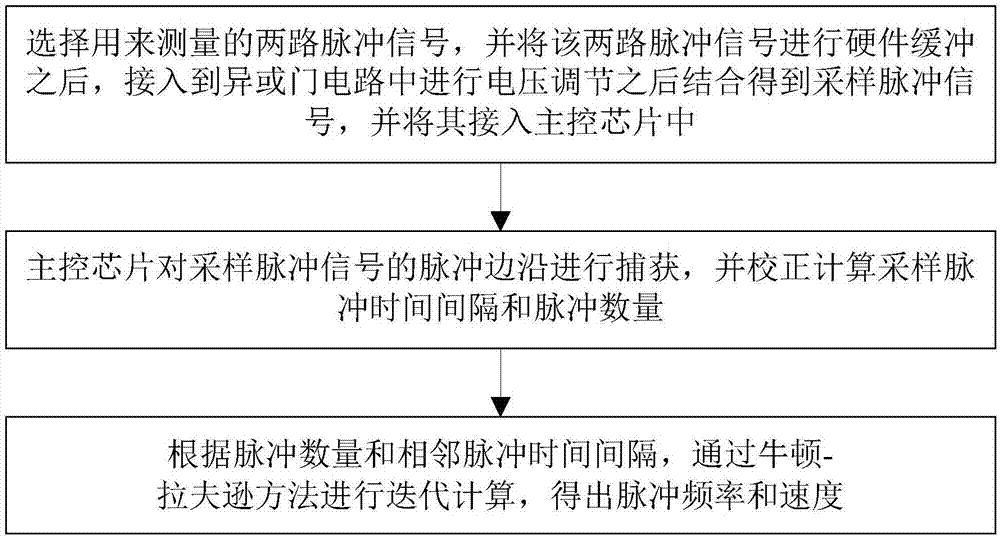

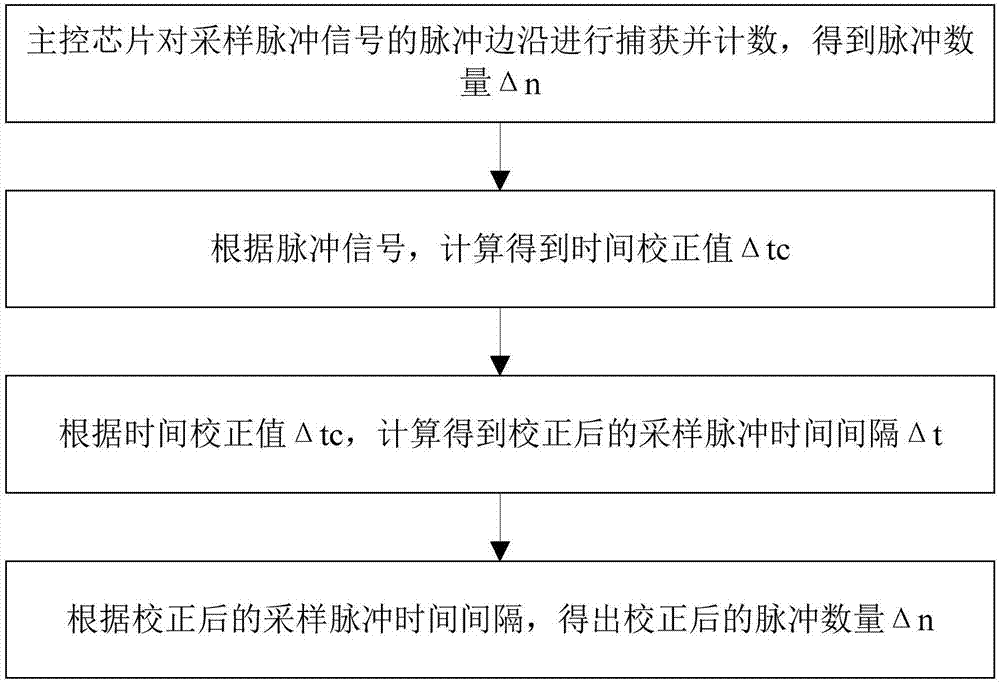

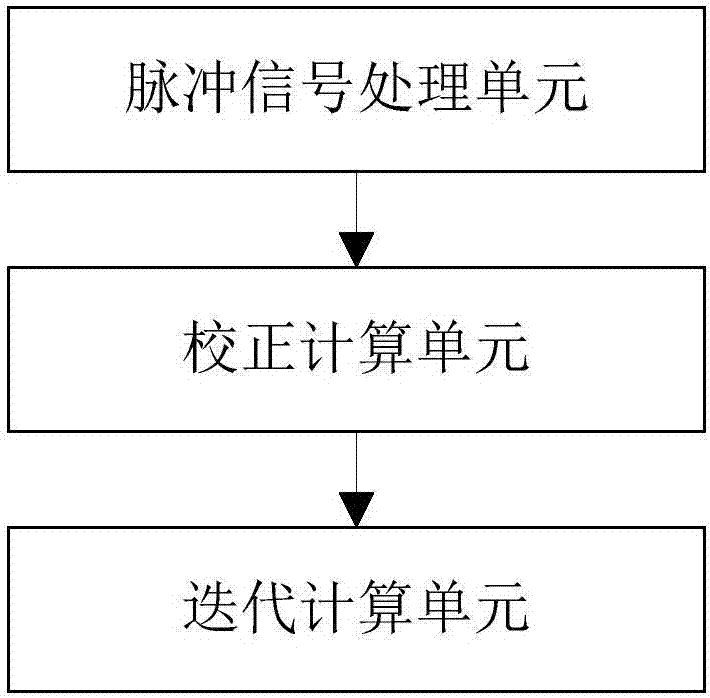

Position signal fast decoding method and system

InactiveCN106950429AReduce processing complexityReduce the number of instructionsFrequency to pulse train conversionPulse techniqueDecoding methodsSignal correction

The invention provides a position signal fast decoding method and system. The method comprises the steps that two pulse signals for measuring are selected and combined to acquire a sampling pulse signal, and the signal accesses a main control chip; the main control chip corrects the sampling pulse signal to calculate the sampling pulse time interval and the number of pulses; and according to the number of pulses and adjacent pulse time interval, a Newton-Raphson method is used for iterative calculation to acquire the pulse frequency and speed. The system comprises a pulse signal processing unit, a correction calculation unit and an iterative calculation unit. According to the invention, the pulse signals are combined; the number of pulse edges can be doubled, which reduces the complexity of chip processing and improves the timing accuracy; in particular, the number of chip instructions can be greatly reduced when parallel processing events are required; compensation and correction methods can be combined to simultaneously improve the counting accuracy of the pulse frequency; the calculation accuracy is greatly improved; and the method and system can be widely applied in the field of integrated circuits.

Owner:GUANGZHOU HKUST FOK YING TUNG RES INST

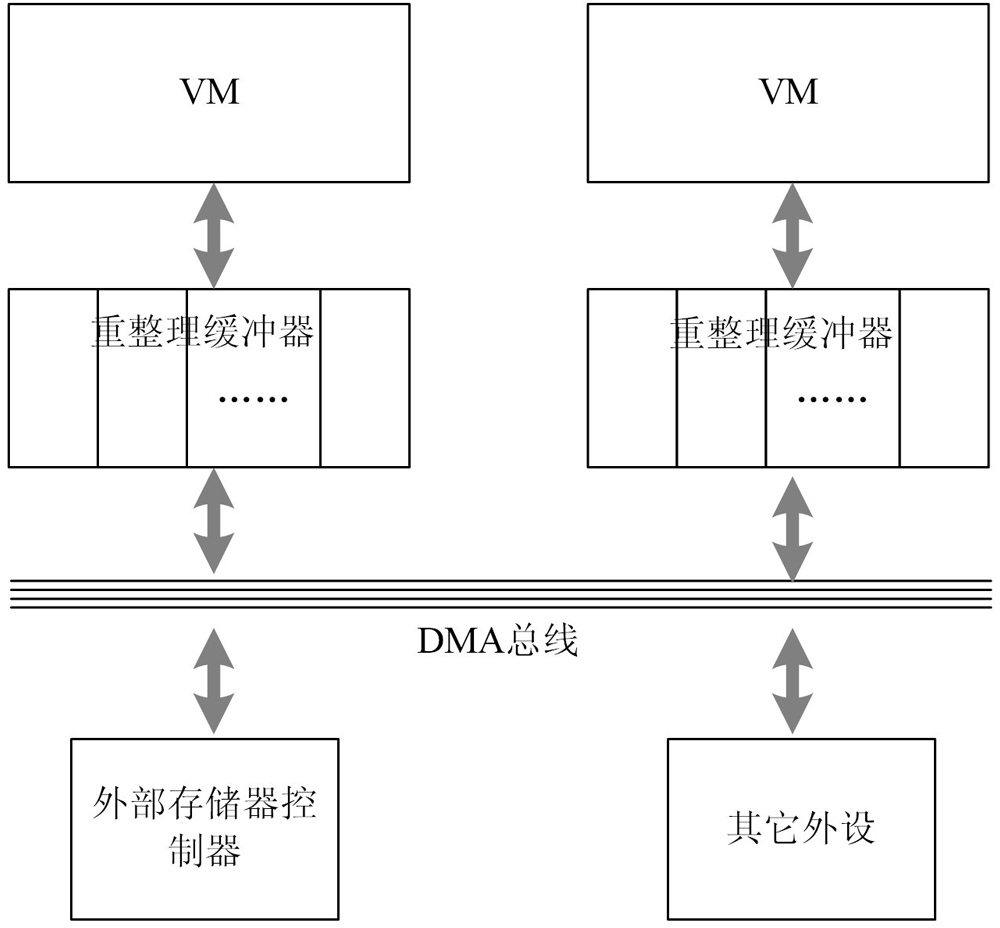

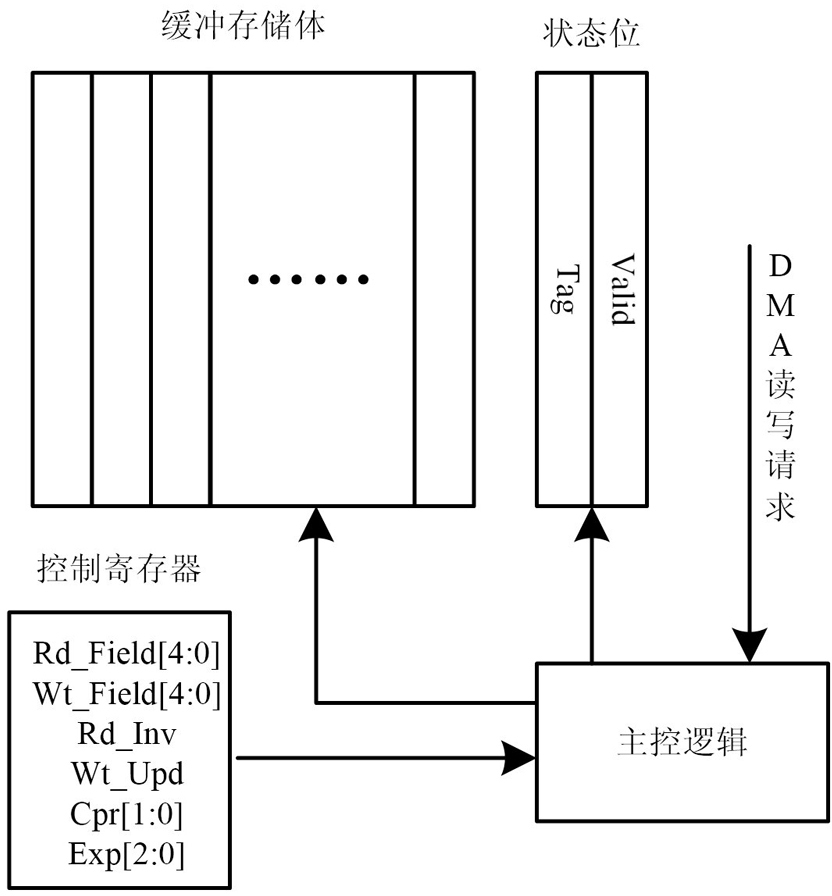

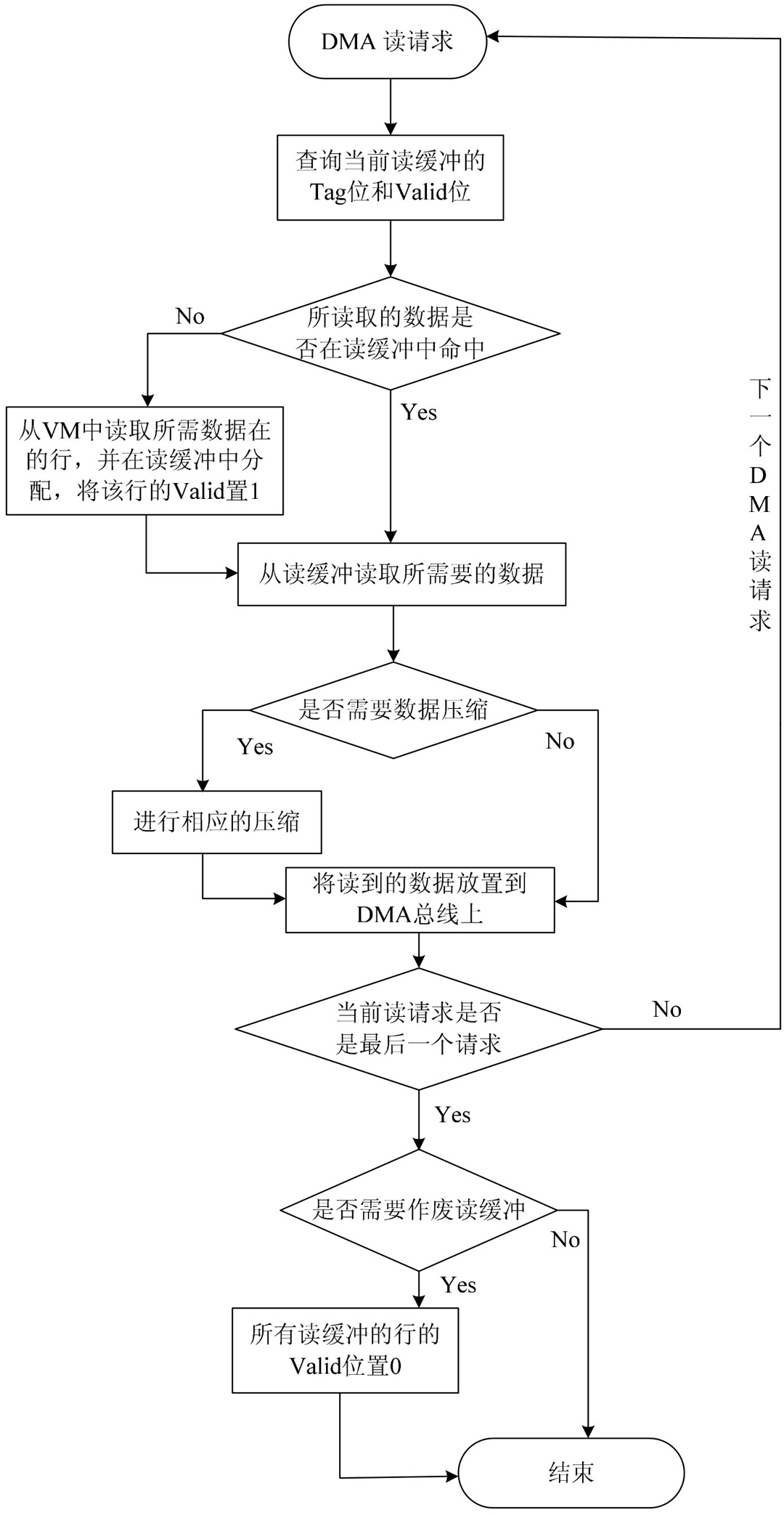

Reform buffer for vector data streams

ActiveCN101986287AReduce interruptionsBalancing Bandwidth DifferencesElectric digital data processingData streamProcessor register

The invention discloses a reform buffer for vector data streams, which comprises a buffer memory stack, a control register, a status bit and a main control logic unit, wherein the buffer memory stack is used for temporarily storing data which comes from a DMA bus and is written into a vector memory VM or temporarily storing data which is read from the vector memory VM and required to be written into other spaces by the DMA bus; the control register is used for carrying out data configuration when the DMA bus starts to carry out data transmission; the status bit is used for recording that which row in the vector memory VM is mapped by each row in the buffer memory stack, and recording whether the row is effective; and the main control logic unit is used for overall control, when the DMA bus carries out the data transmission, the main control logic unit selects different buffer positions according to the control register, carries out corresponding data conversion, and selects whether to cancel or re-process the reading of the buffer when the data transmission is completed. The reform buffer has the advantages of simple and compact structure, low cost, wide application range, and good reliability, etc.

Owner:NAT UNIV OF DEFENSE TECH

Moving estimating device and method for reference macro block window in scanning search area

InactiveCN1297134CReduce the number of instructionsTelevision system detailsPulse modulation television signal transmissionMotion vectorParallel computing

A motion estimation technique compares a current macroblock with different reference macroblocks in a reference frame search area. A motion vector for the current macroblock is derived from the reference macroblock most closely matching the current macroblock. To reduce the number of instructions required to load new reference macroblocks, overlapping portions between reference macroblocks are reused and only nonoverlapping portions are loaded into a memory storage device.

Owner:SAMSUNG ELECTRONICS CO LTD

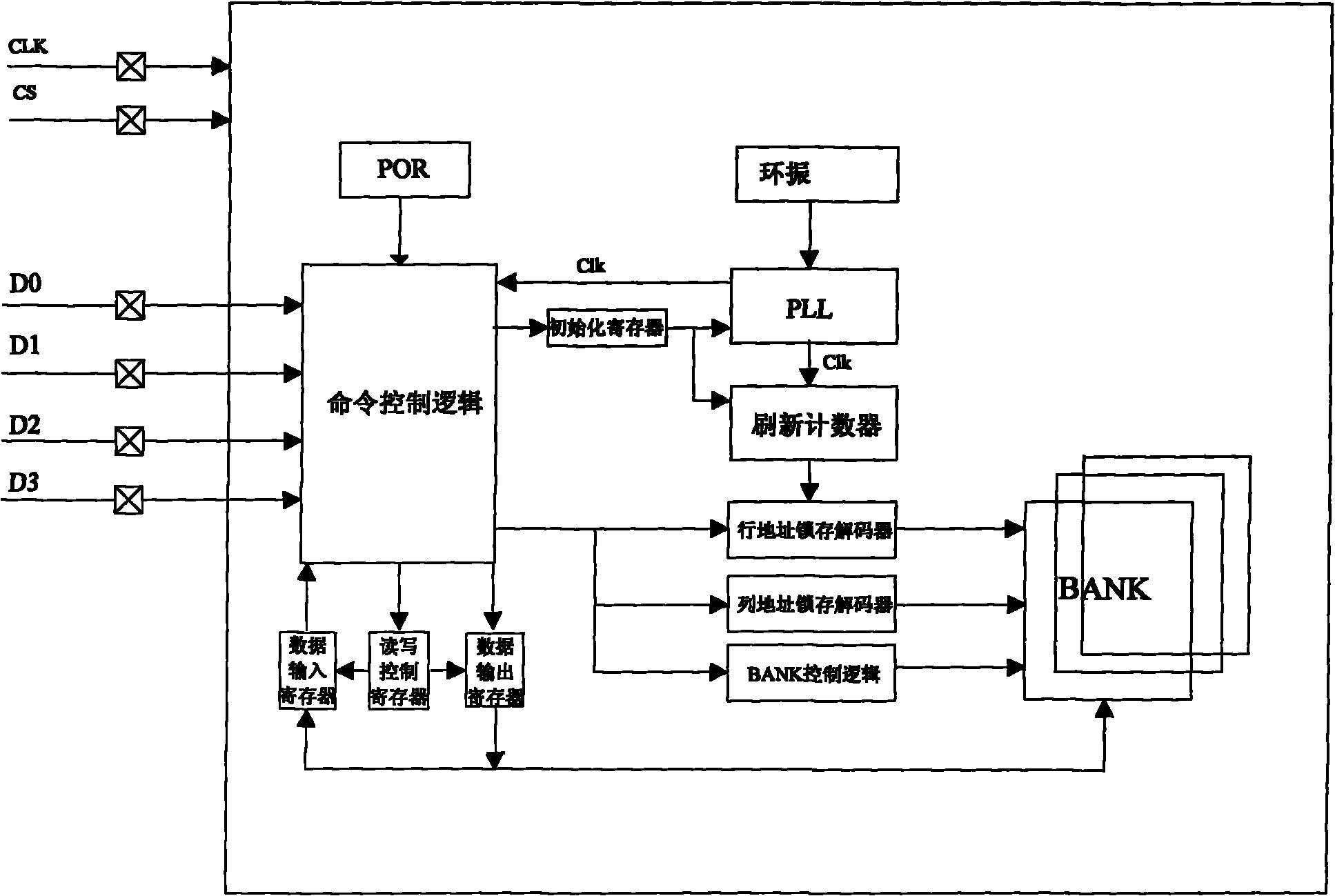

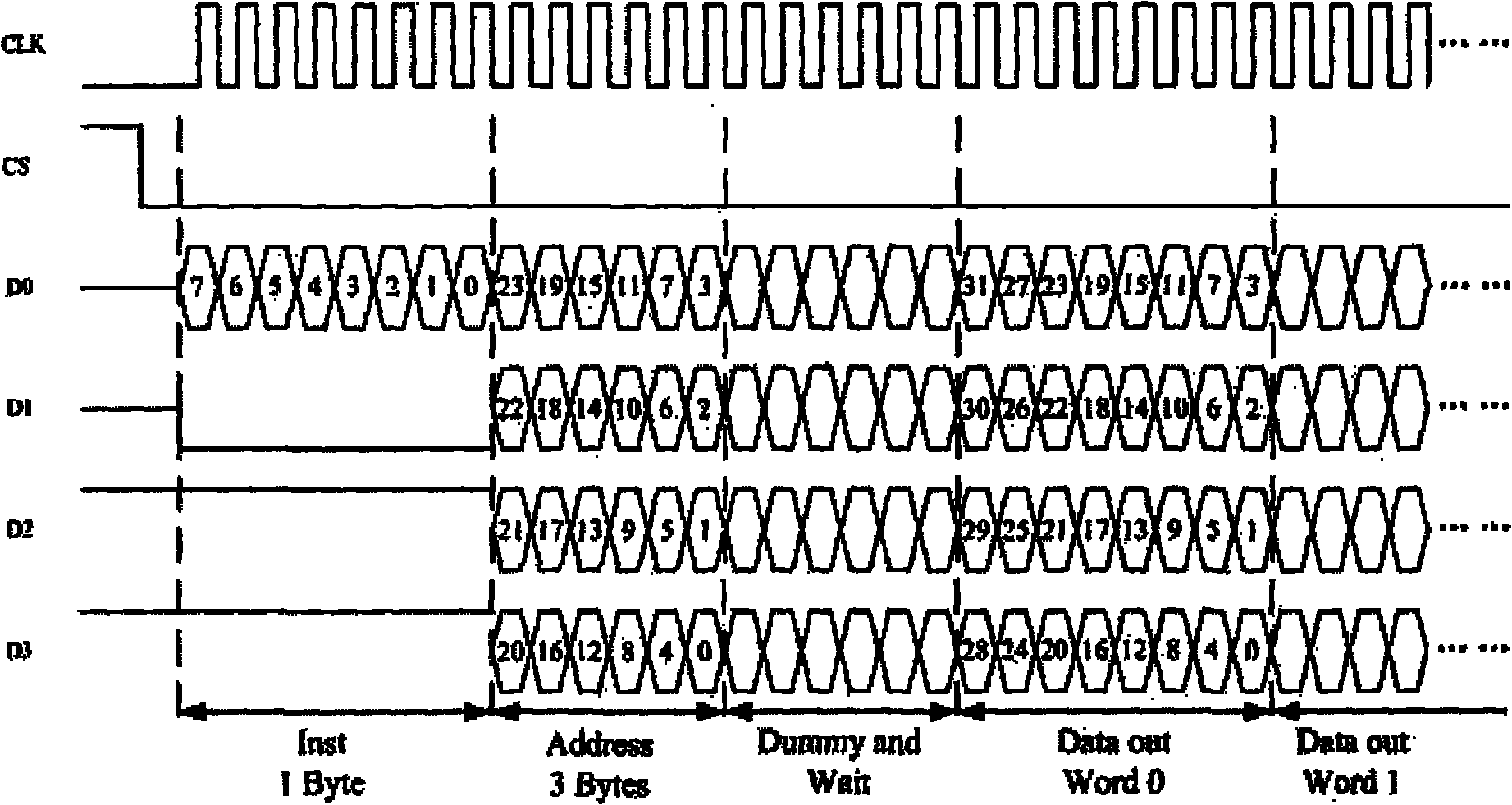

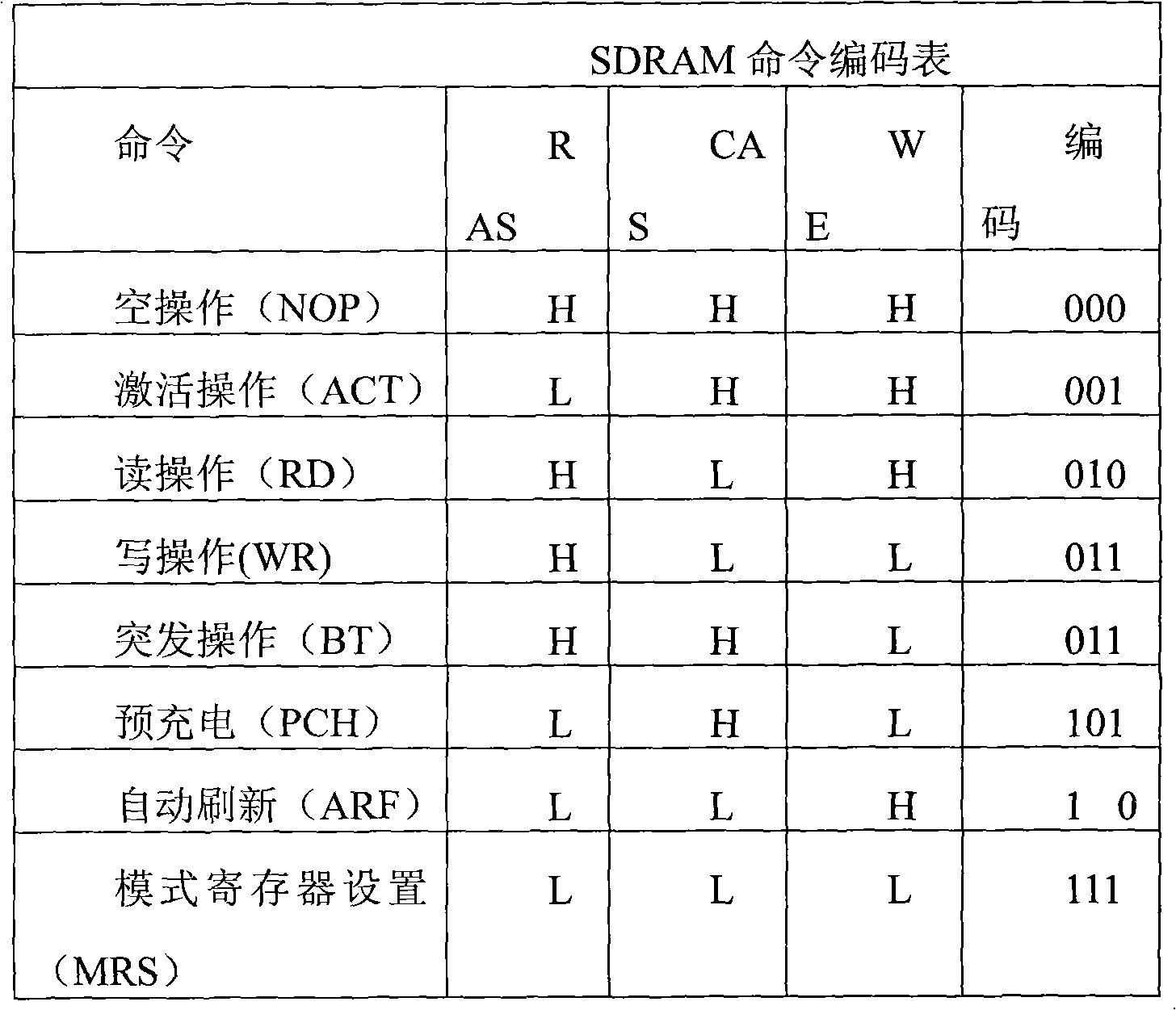

Method for realizing four-channel serial communication of SDRAM (Synchronous Dynamic Random Access Memory)

ActiveCN102063392AReduce the number of instructionsReduce the number of portsElectric digital data processingProcessor registerSynchronous dynamic random-access memory

The invention relates to a method for realizing four-channel serial communication of an SDRAM (Synchronous Dynamic Random Access Memory). The method comprises the steps of: transmitting command signals through one channel, and decoding command signals received from a serial channel D0 through a command control logic unit and recognizing the commands, wherein commands for serial four-channel SDRAM include a read operation command, a write operation command and an initialized configuration command; after the command control logic unit recognizes the initialized command, outputting a signal for configuring a PLL (Phase Locked Loop) and refreshing a counter, executing the configuring operations of configuring the PLL and refreshing the counter; after the command control logic unit recognizes the read and write commands, analyzing a received address signal to generate a column address, a row address and a BANK signal and sending the column address, the row address and the BANK signal to a column address latch decoder, a row address latch decoder and a BANK control logic; and then transmitting data signals, wherein the transmission of the data signals is controlled by a read-write register. The method changes the parallel communication mode of the SDRAM to the serial communication and realizes the four-channel serial communication function of the SDRAM.

Owner:HANGZHOU SYNOCHIP DATA SECURITY TECH CO LTD

Surface myoelectricity man-machine interface system based on visual stimulation interface and control method thereof

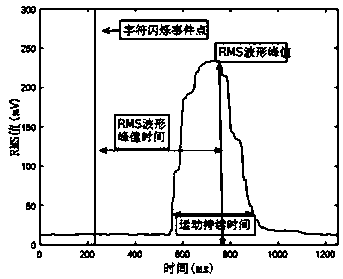

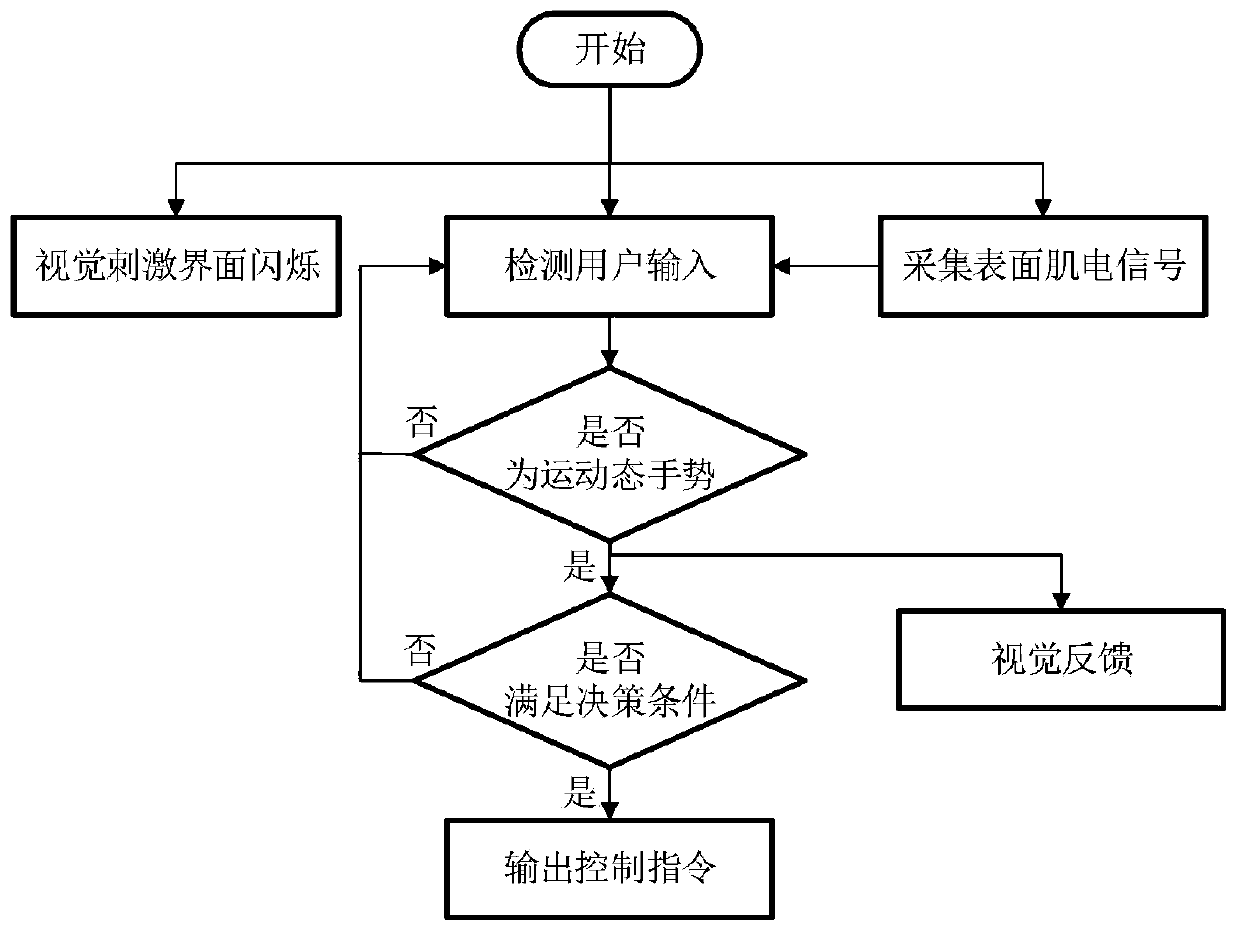

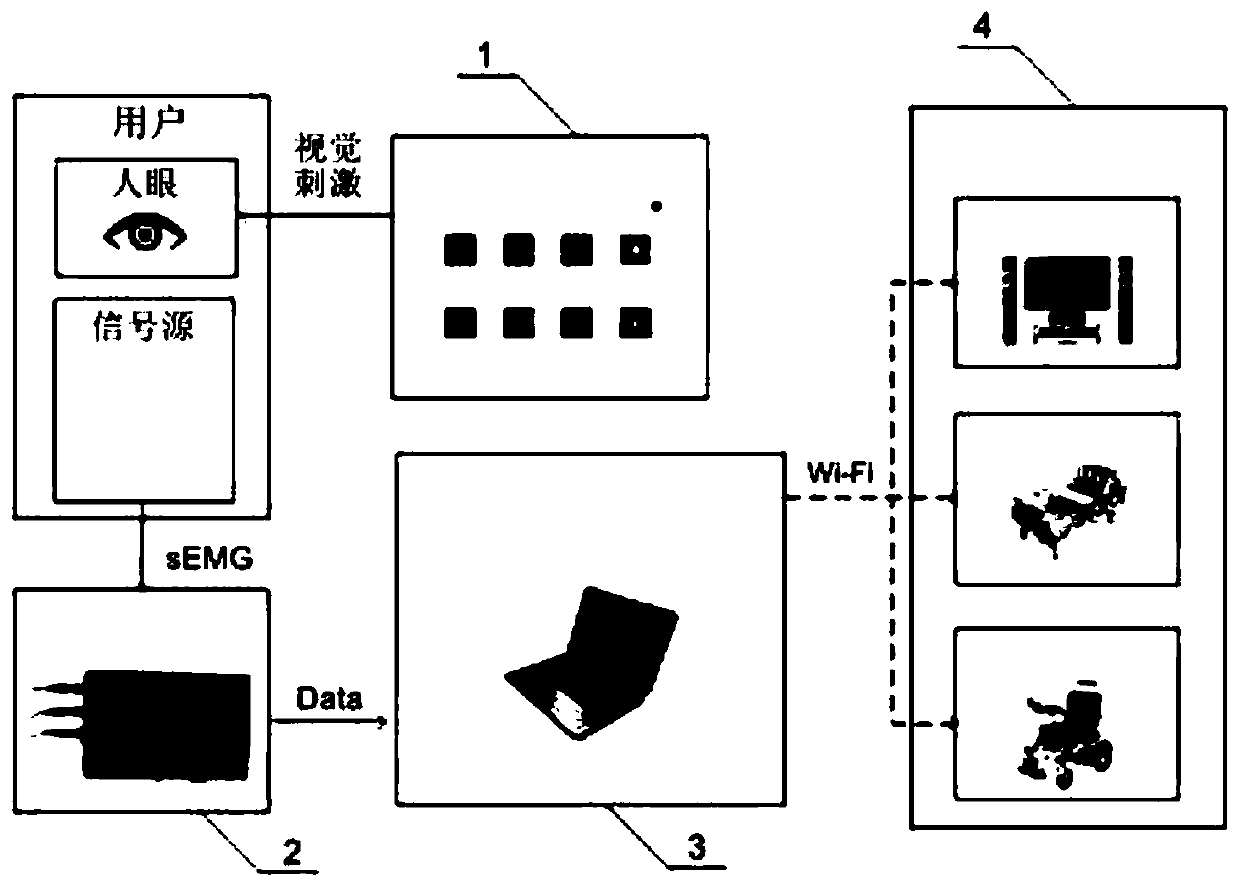

PendingCN110018744AProvide quicklySecure provisionInput/output for user-computer interactionGraph readingHuman–machine interfaceMan machine

The invention discloses a surface myoelectricity man-machine interface system based on a visual stimulation interface, which comprises a visual stimulation unit, a surface myoelectricity signal acquisition unit, a central processing unit and an environment control unit. The visual stimulation unit is based on a man-machine interface single-character stimulation mode and is composed of several characters, each character corresponds to a control instruction executed by the environment control unit; the characters flicker in sequence according to a random sequence, only one character flickers atthe same time, and when all the characters flicker once to form a round, each character in each round can flicker only once, the user synchronously performs hand motion along with flickering of the characters to select the characters, and when the user selects the characters, the visual stimulation unit can give visual feedback to the user to prompt the user that the character is selected; the man-machine interface single-character stimulation mode is adopted, the number of system control instructions is the number of characters of the visual stimulation unit, so that the number of channels for collecting myoelectricity is reduced, and the hardware equipment cost is reduced; operation is simple, and practicability and real-time performance are high.

Owner:SOUTH CHINA UNIV OF TECH

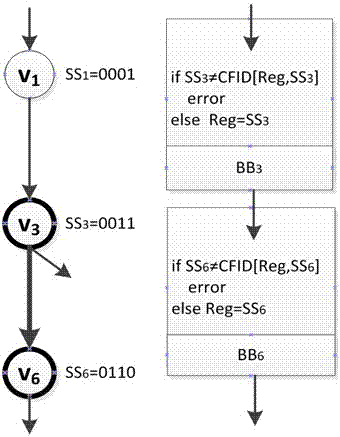

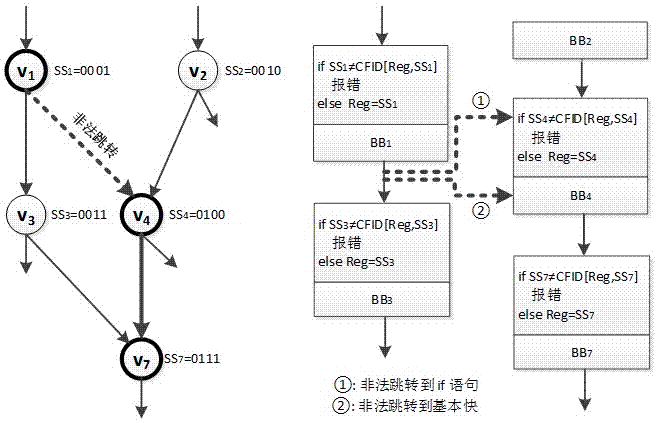

Table-driven signature error detection algorithm

InactiveCN107301123ASimplify usage requirementsImplement error detectionSoftware testing/debuggingComputer hardwareNODAL

The invention discloses a table-driven signature error detection algorithm. According to the algorithm, information of a control flow graph is stored in a two-dimensional table (CFID table) based on a finite state machine (FSM) theory; and by comparing signatures in basic blocks with signatures stored in the CFID table, illegal instruction skip is detected out. Illegal instruction skip errors, incapable of being detected by a CFCSS algorithm, of shared branch fan-in nodes can be successfully detected. An experimental result shows that the average error detection coverage rate reaches 98.1%, and the number of error detection instructions inserted in each basic block is smaller than that of the error detection instructions inserted in CFCSS.

Owner:STATE GRID ZHEJIANG ELECTRIC POWER +1

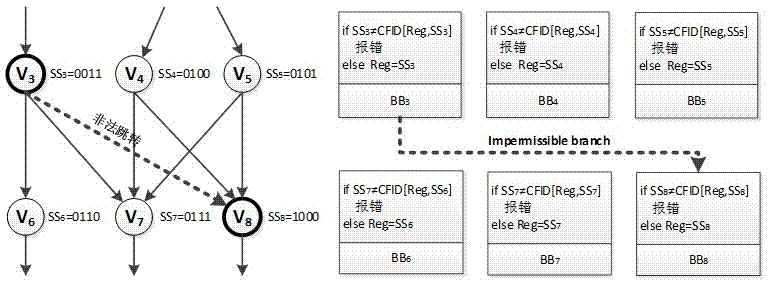

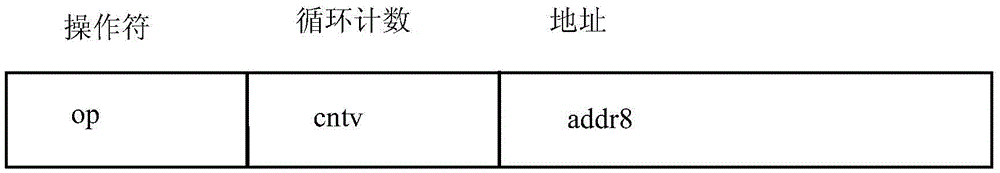

Method and processor for encryption and decryption

ActiveCN106888082ASimple structureDecryption implementationEncryption apparatus with shift registers/memoriesIndex registerCounting Number

The invention discloses a method and processor for encryption and decryption, relates to the encryption and decryption technology and effectively reduces the logic unit number occupied by ARS during FPGA realization. According to the method, input data is stored in an input data register, and a data storage address addr=addr1+addr8 is updated; if a reading of a cycle counter is smaller than a cycle counting number in an instruction, an index register and the cycle counter are respectively plus one, transfer to an instruction address designed by addr8 is then carried out, zero setting of the cycle counter is carried out, and cycle operation in a 0-15 scope is realized; original data of the register is stored to another register when register writing operation is simultaneously carried out, reading operation from a storage device to the register and writing operation from the register to another register is combined to one same instruction, a 16-times cycle program block is realized through six instructions, and the method is for encryption and decryption.

Owner:北京京航计算通讯研究所

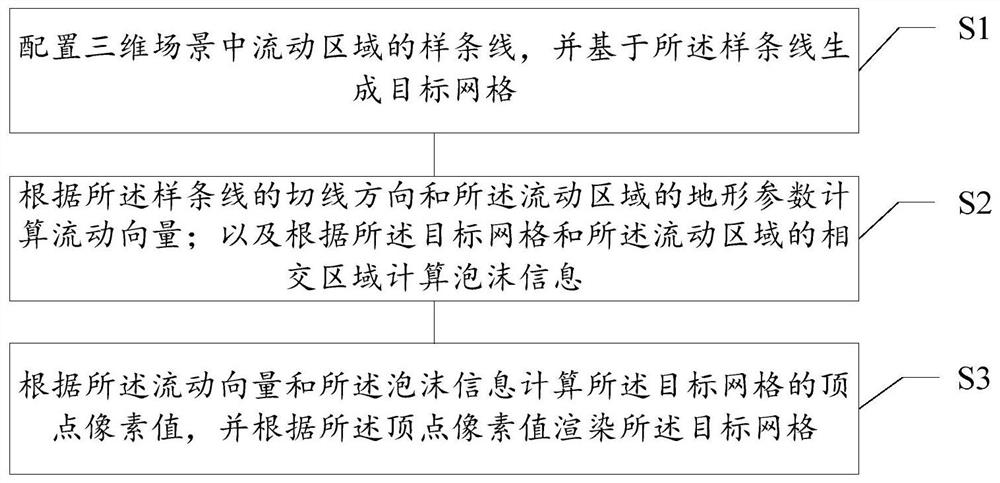

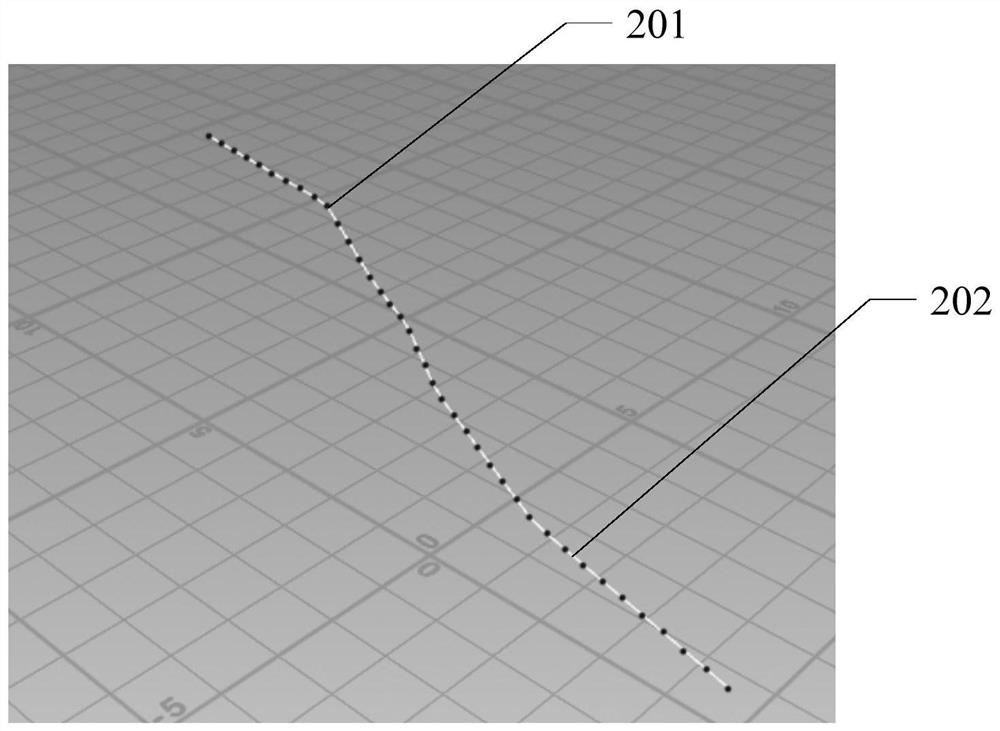

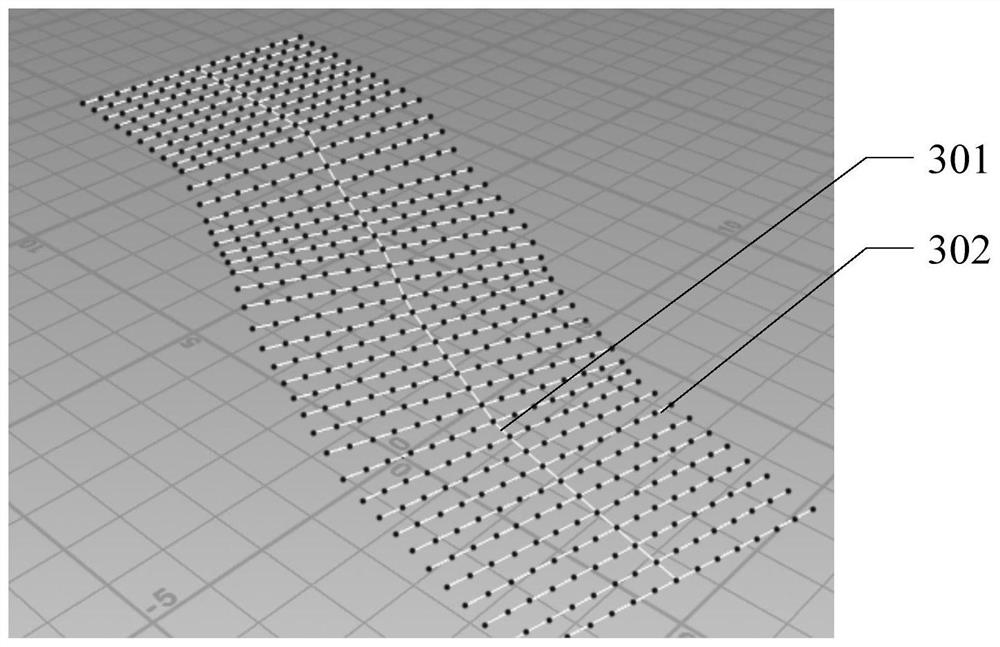

Virtual scene rendering method and device, storage medium and electronic equipment

ActiveCN113034662AReduce the number of instructionsSimplify the export and import stepsAnimation3D-image renderingMesh gridEngineering

The invention relates to the technical field of computers, in particular to a virtual scene rendering method and device, a storage medium and electronic equipment. The virtual scene rendering method comprises the following steps: configuring a spline line of a flowing area in a three-dimensional scene, and generating a target grid based on the spline line; calculating a flow vector according to the tangential direction of the spline line and the topographic parameters of the flow area; calculating foam information according to an intersection area of the target grid and the flow area; and calculating a vertex pixel value of the target grid according to the flow vector and the foam information, and rendering the target grid according to the vertex pixel value. According to the virtual scene rendering method provided by the invention, the steps of virtual scene rendering can be simplified, and the rendering efficiency is improved.

Owner:NETEASE (HANGZHOU) NETWORK CO LTD

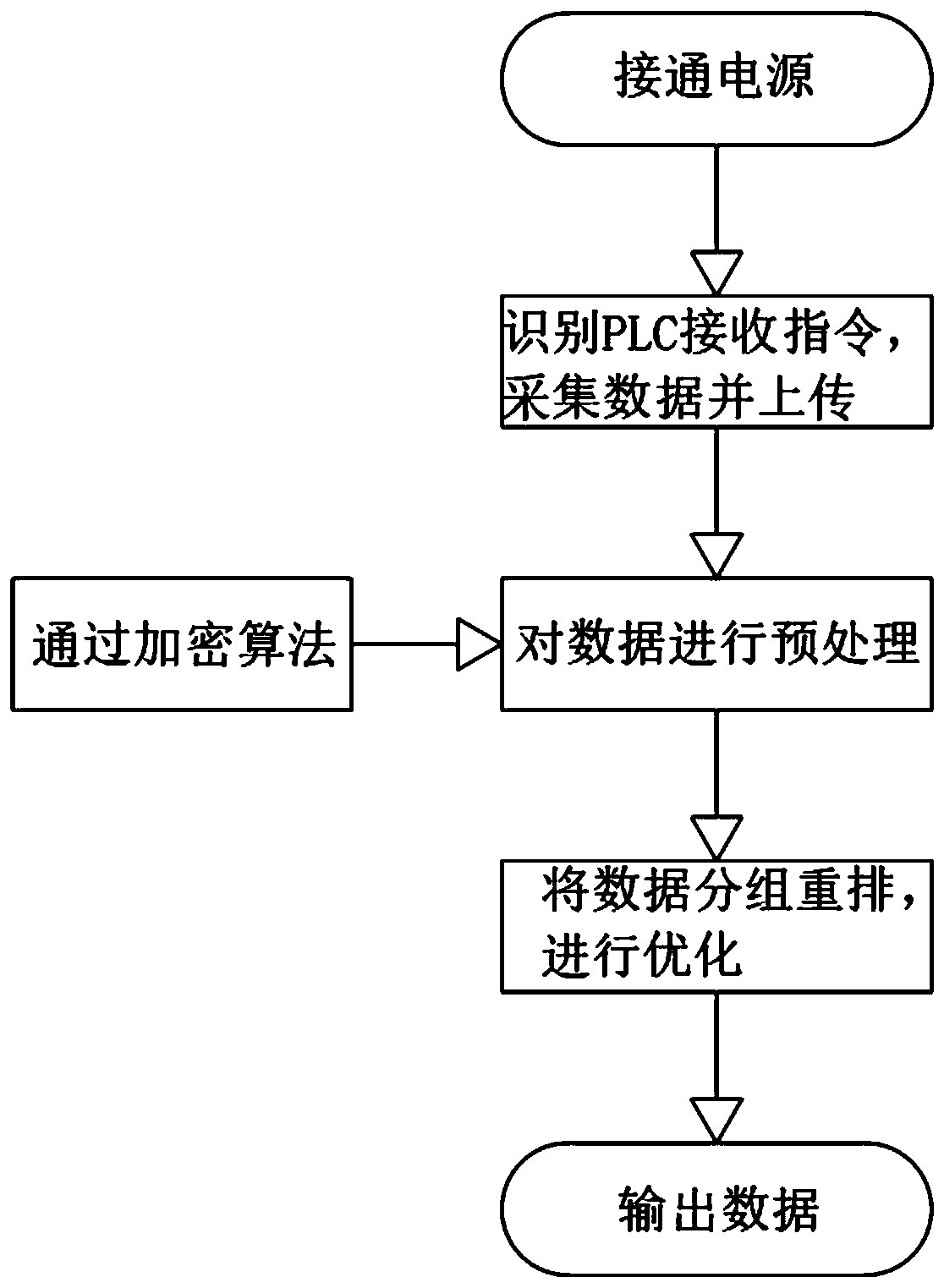

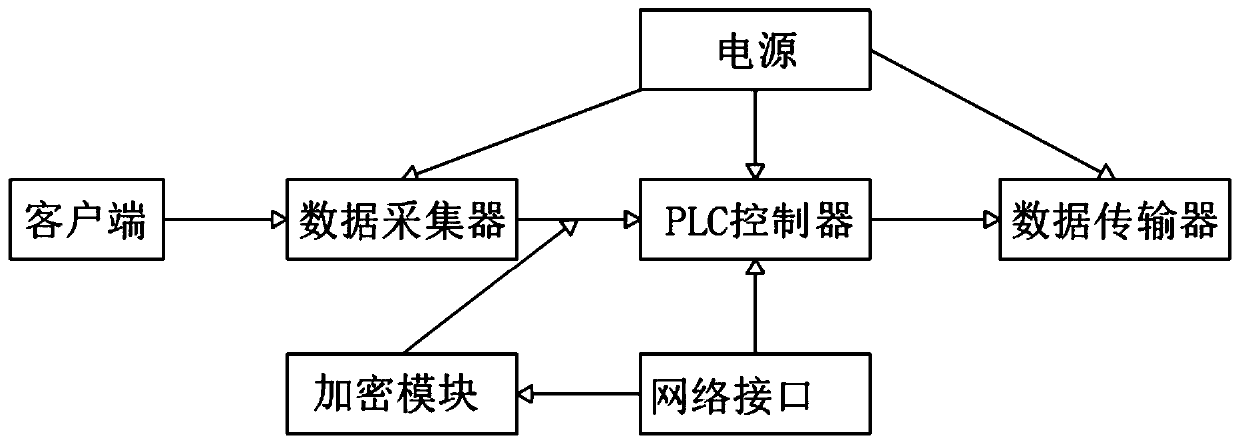

Plc protocol based data collection optimized method

InactiveCN110096023AHighly integratedImprove reliabilityProgramme control in sequence/logic controllersInternet serversData file

The invention discloses a plc protocol based data collection optimized method, and belongs to the technical field of data collection optimization. The method comprises the following steps that S1) a power supply is switched on, and different parts are connected to the network; S2) communication protocols of a PLC are used, an instruction is sent, a data collector identifies the instruction and then collects data, and obtained data is encrypted; S3) the obtained data is preprocessed and divided into multiple parts; S4) the different parts are found, and analyzed and processed, and the parts after processing and optimization are recovered to a main body; and S5) the processed data is reported to an Internet server via PLC communication protocols, stored in a data memory and then output. Thedata collection optimized method can be used to improve the reliability and operation speed of the system, can be conveniently mastered and operated by a user, and can be used to enhance the safety ofdata file storage.

Owner:JIANGSU NANGAO INTELLIGENT EQUIP INNOVATION CENT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com