Digital circuit implementation by means of parallel sequencers

A sequencer and parallel processing technology, applied in CAD circuit design, electrical digital data processing, combination of multiple digital computers, etc., can solve problems such as difficult to use, bulky, and slow design tools

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

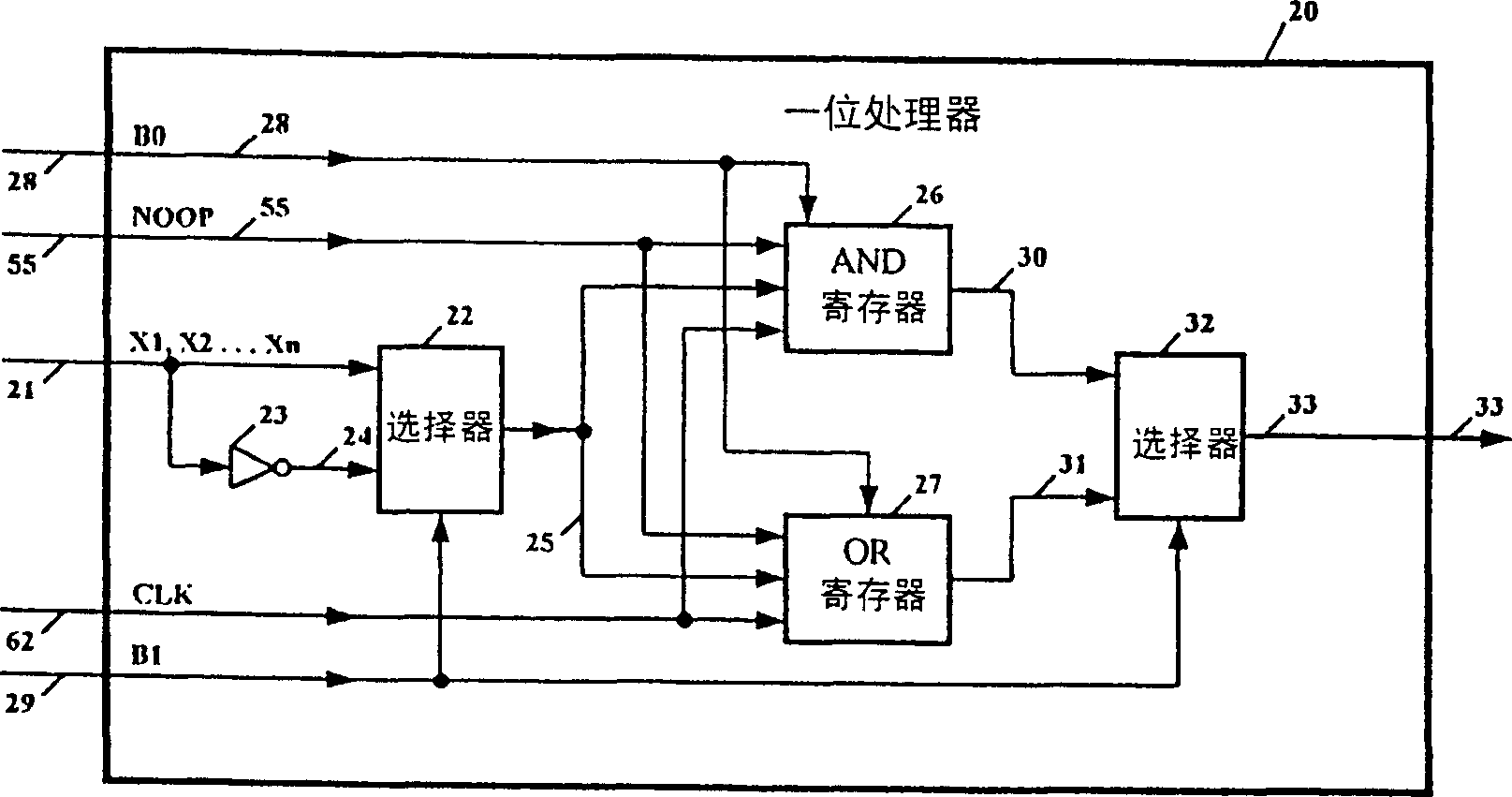

[0032] figure 1 represents an embodiment of a one-bit processor. This embodiment facilitates the execution of Reverse Polish Notation (RPN) machine instructions. Processor 20 is based on two (2) parallel operations performed on all input variables in parallel. figure 1 By way of example, they are shown as AND register 26 and OR register 27 in . Since processor 20 allows an inversion operation by means of inverter 23, the simultaneous presence of registers 26 and 27 does not enforce the logic equation, since the inversion theorem (de Morgan theorem) allows AND The operation is converted to an OR operation or vice versa. It is also within the scope of the present invention to replace the AND register 26 or replace the OR register 27 with a block that performs an XOR or other logical operation.

[0033] At the beginning of the execution of each logic equation, the AND register 26 is set to logic "1". The first "0" resets register 26 to "0" and keeps it at "0" regardless of s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More