Patents

Literature

105results about How to "Increase clock speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

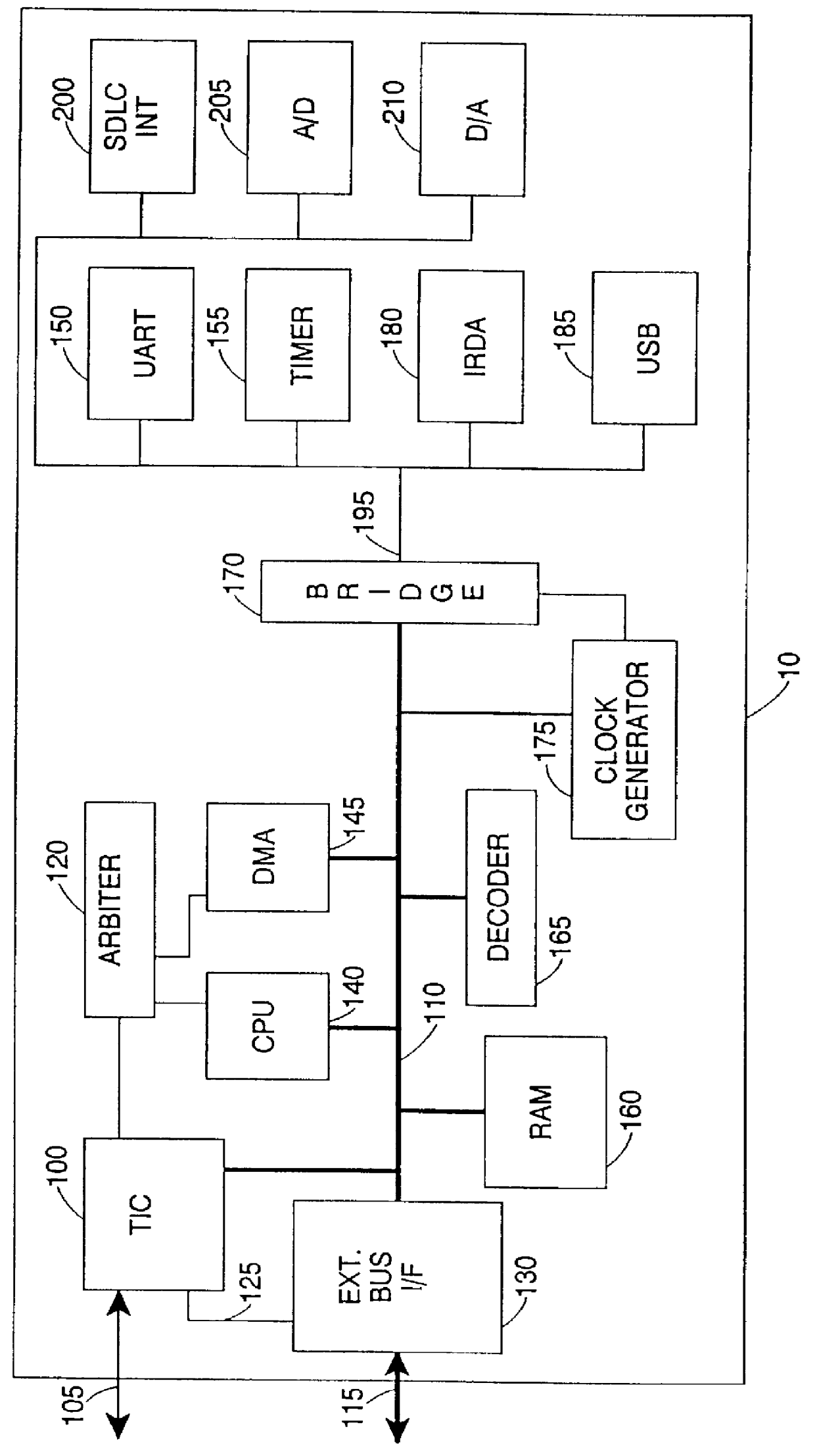

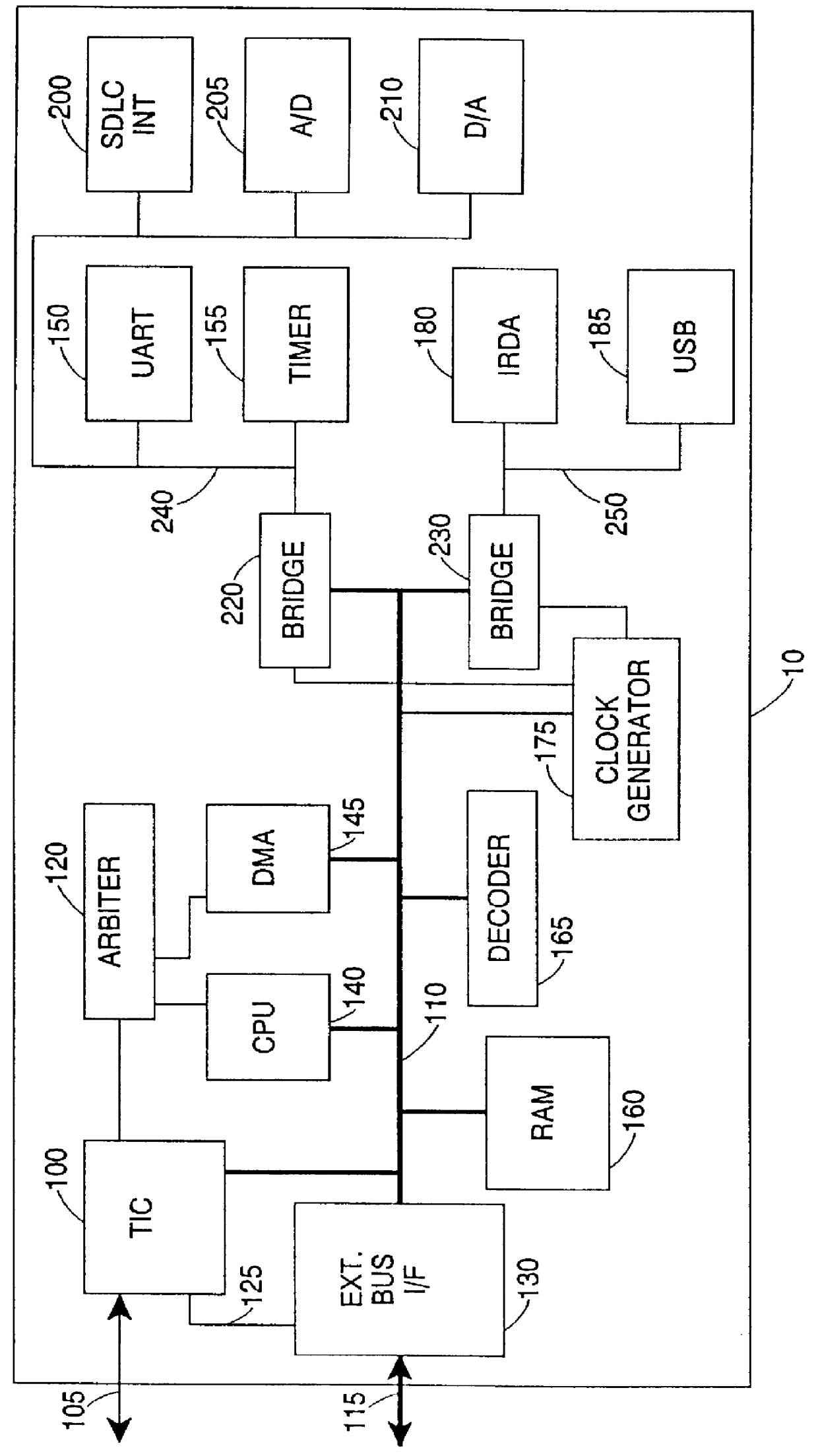

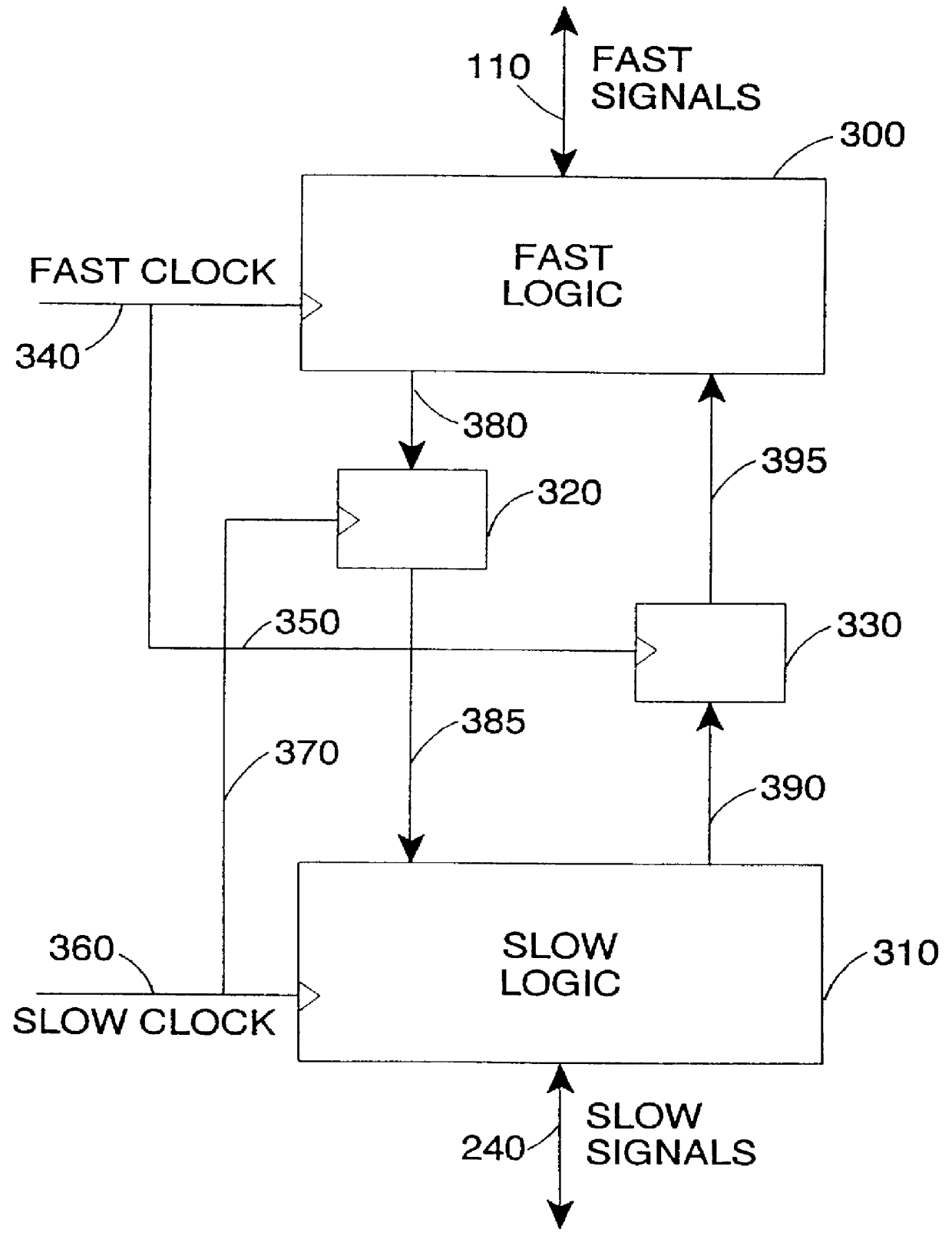

Peripheral buses for integrated circuit

InactiveUS6064626AReduce power consumptionAverage power consumptionEnergy efficient ICTDigital storageCapacitanceClock rate

The present invention provides an integrated circuit comprising a system bus to which a processor is connectable, and first and second peripheral buses to which peripheral units used by said processor are connected, the first peripheral bus operating at a higher clock speed than the second peripheral bus. Further, the integrated circuit comprises bridge logic for providing an interface between the system bus and the peripheral buses to enable signals to be passed between the system bus and the peripheral buses, the bridge logic comprising clock resynchronisation logic for synchronising the system bus and the peripheral buses. Through the provision of first and second peripheral buses operating at different clock speeds, the integrated circuit of the present invention provides a great deal of flexibility for reducing the power consumption of the integrated circuit as compared with a similar integrated circuit having only one peripheral bus. Since the power consumption of each peripheral bus is proportional to the clock frequency and capacitance, significant power consumption savings can be realised by ensuring that each peripheral unit is connected to the slowest peripheral bus appropriate for that peripheral unit.

Owner:ARM LTD

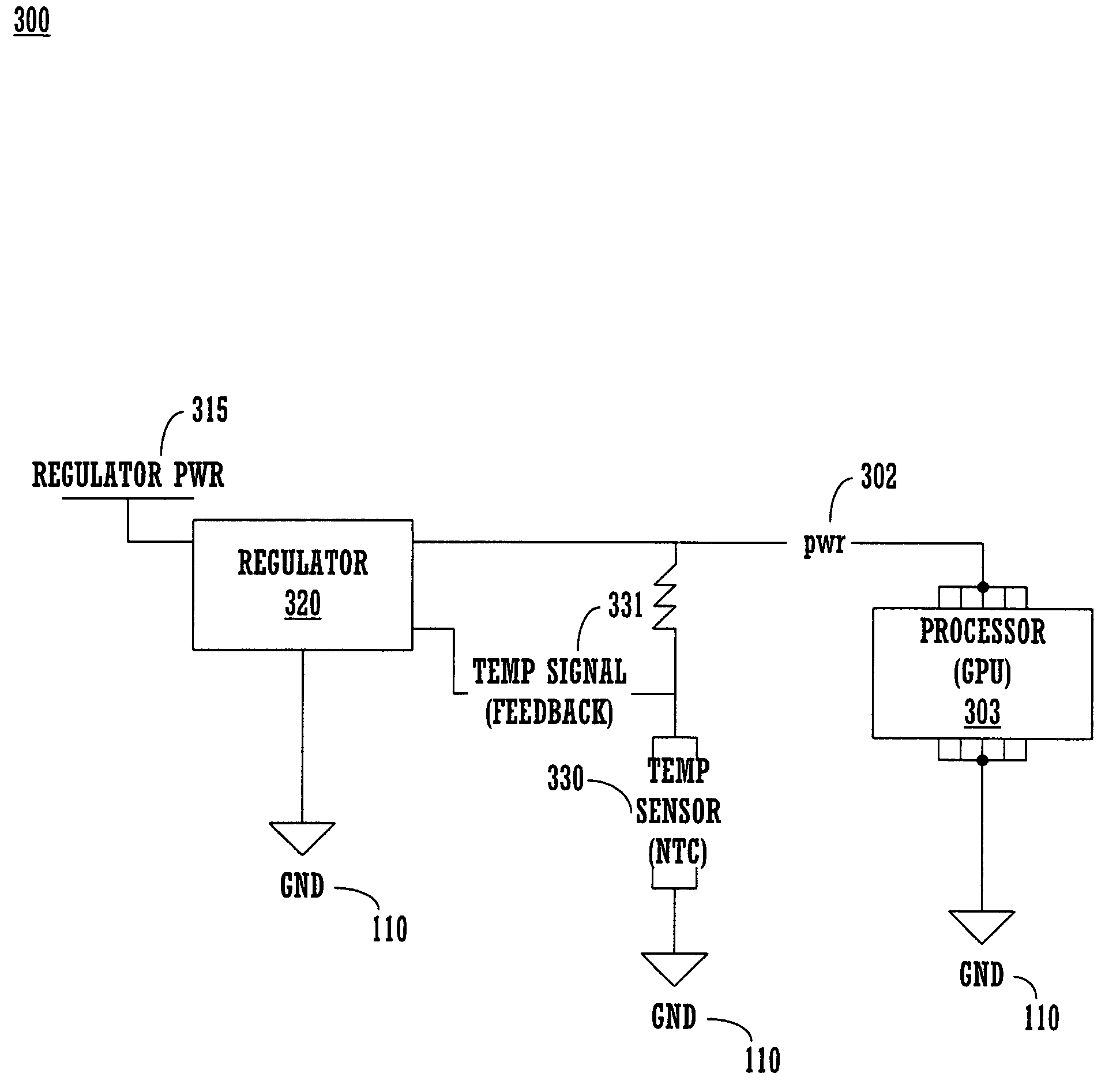

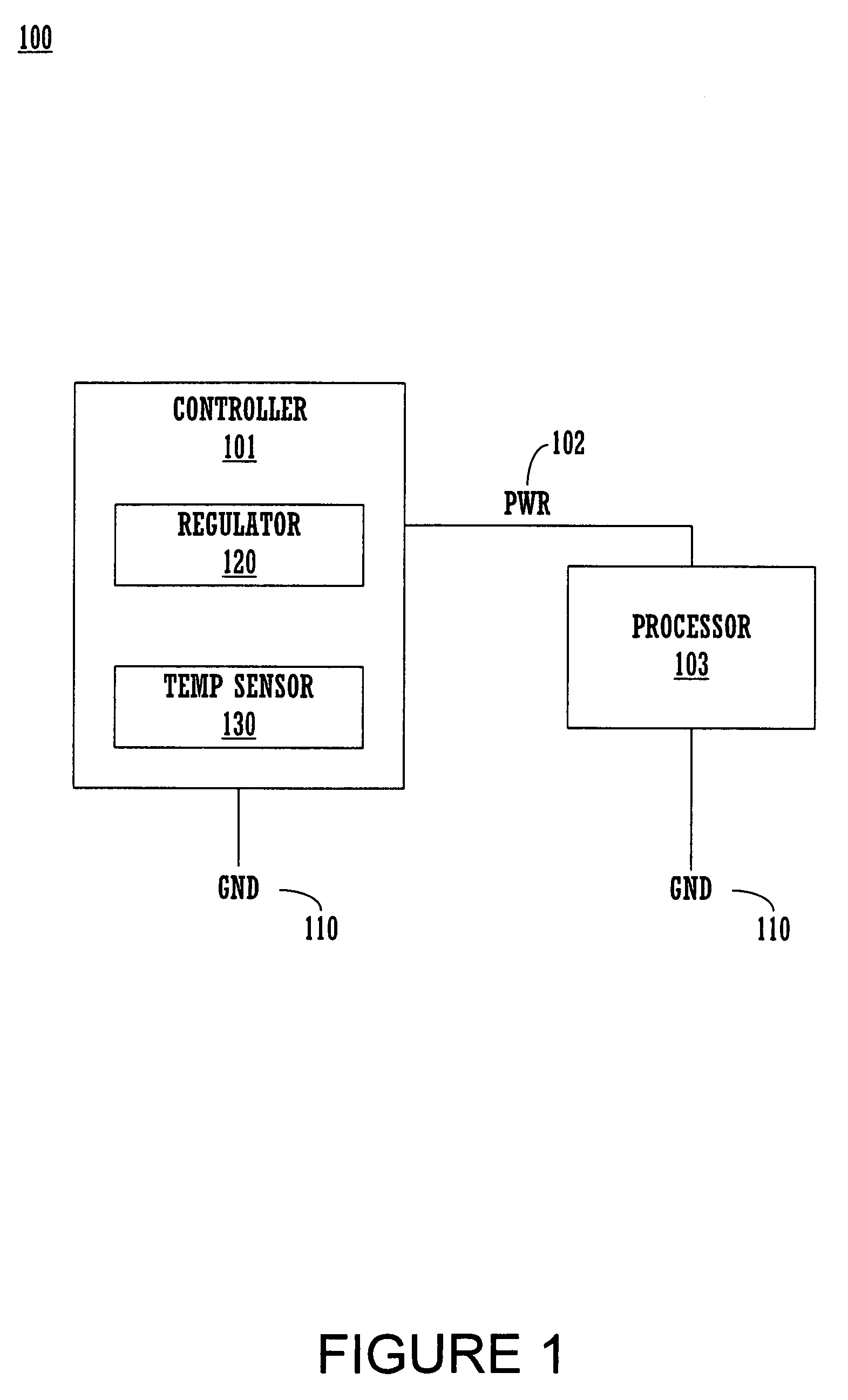

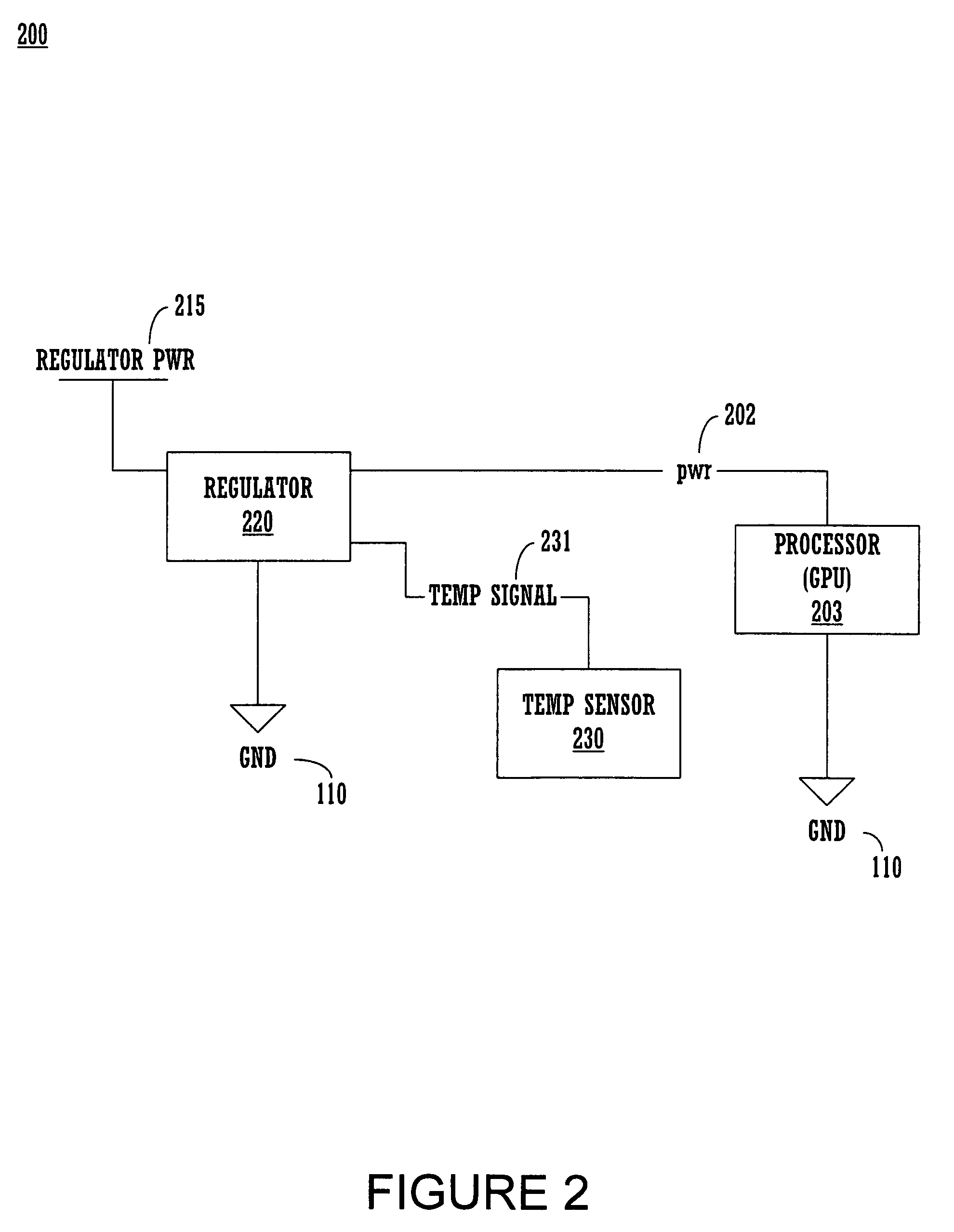

Method and system for dynamic power supply voltage adjustment for a semiconductor integrated circuit device

InactiveUS6947865B1Reduce performance limiting effect of crosstalk and jitter and noiseImprove the level ofThermometer detailsCurrent/voltage measurementSemiconductorCrosstalk

A processor power supply voltage controller. The controller includes a temperature sensor configured to sense a temperature of a processor and generate a temperature signal in accordance therewith. A regulator is coupled to provide a power supply voltage to the processor. The regulator is coupled to receive the temperature signal and control the power supply voltage to maintain a substantially stable crosstalk level within the processor.

Owner:NVIDIA CORP

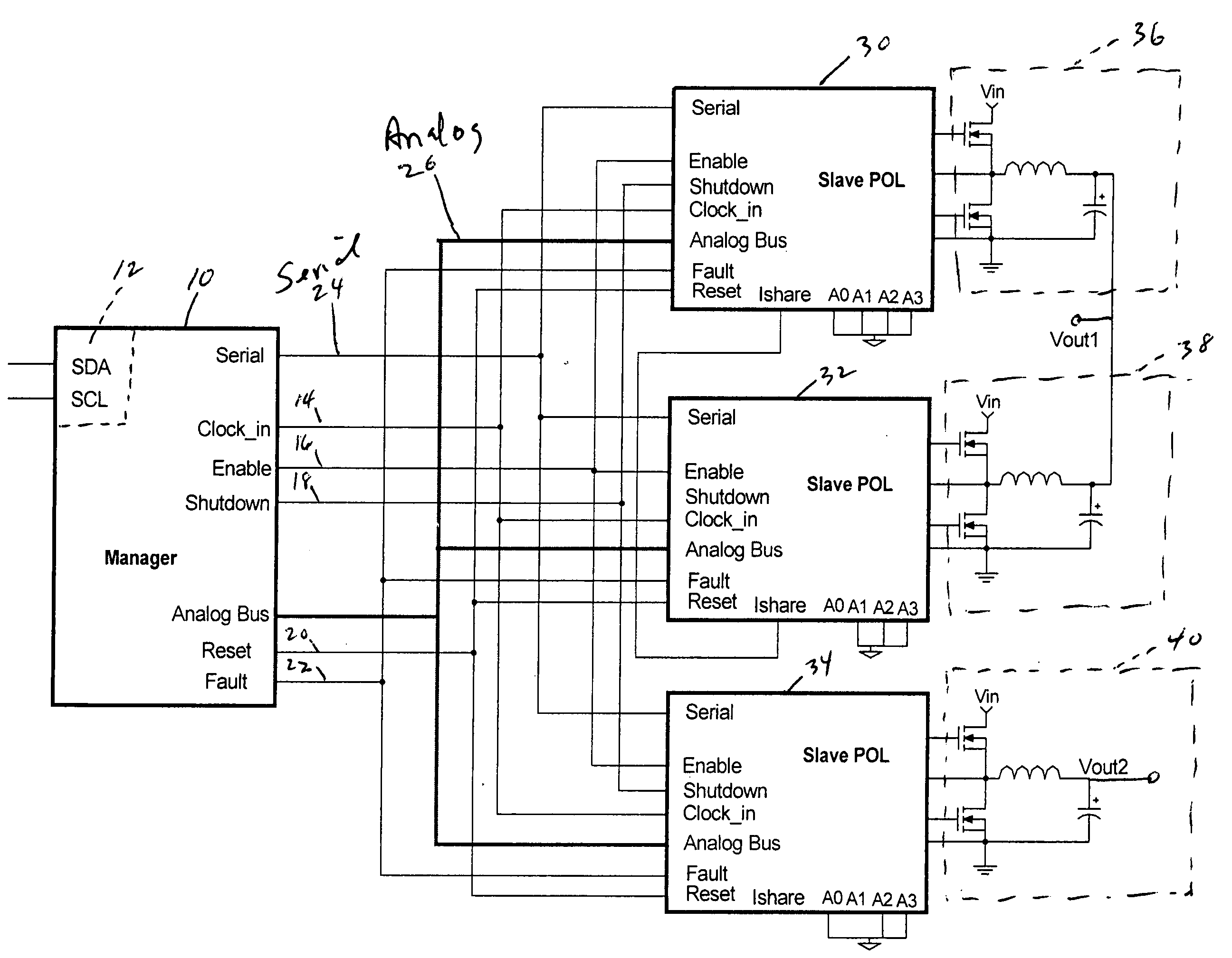

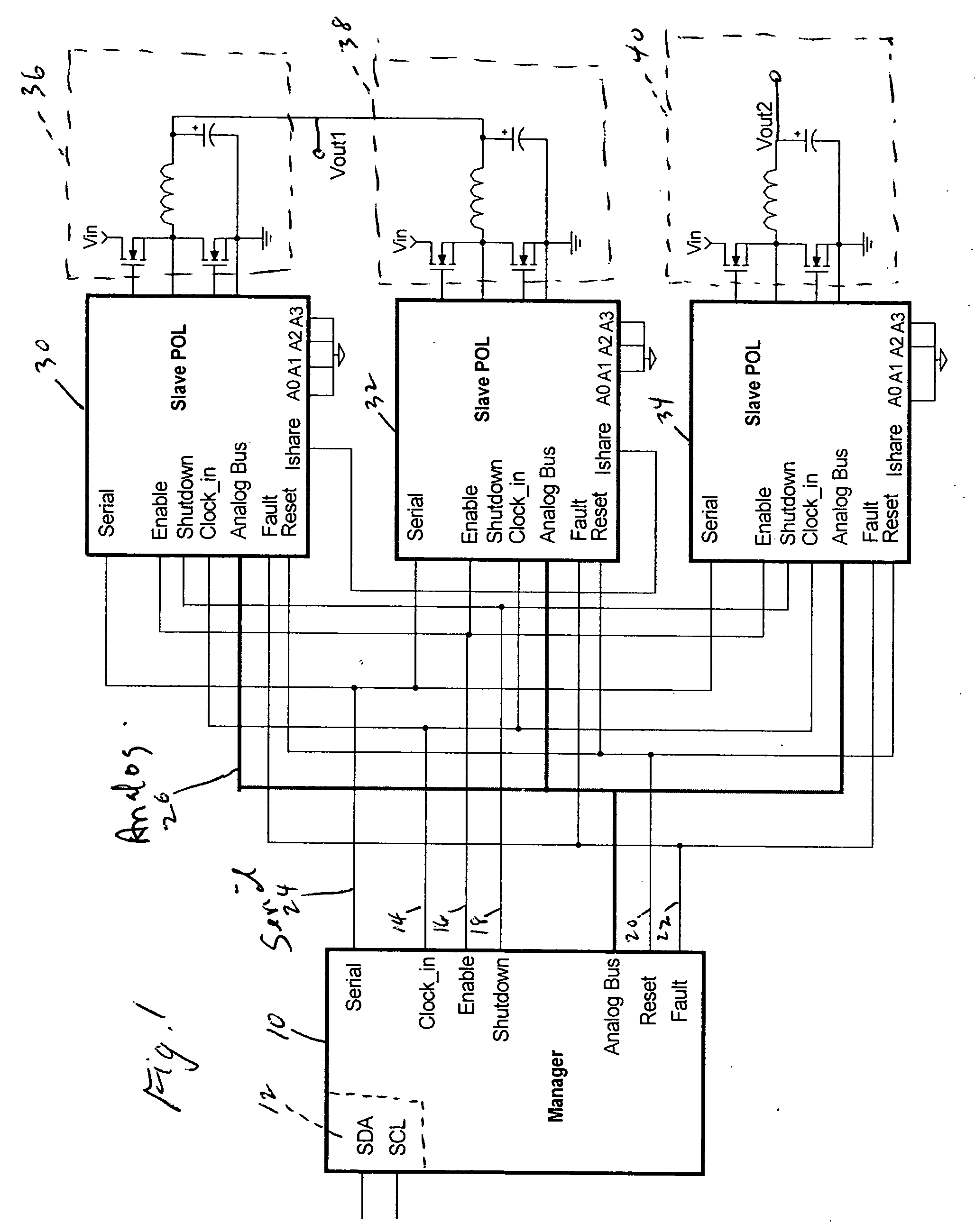

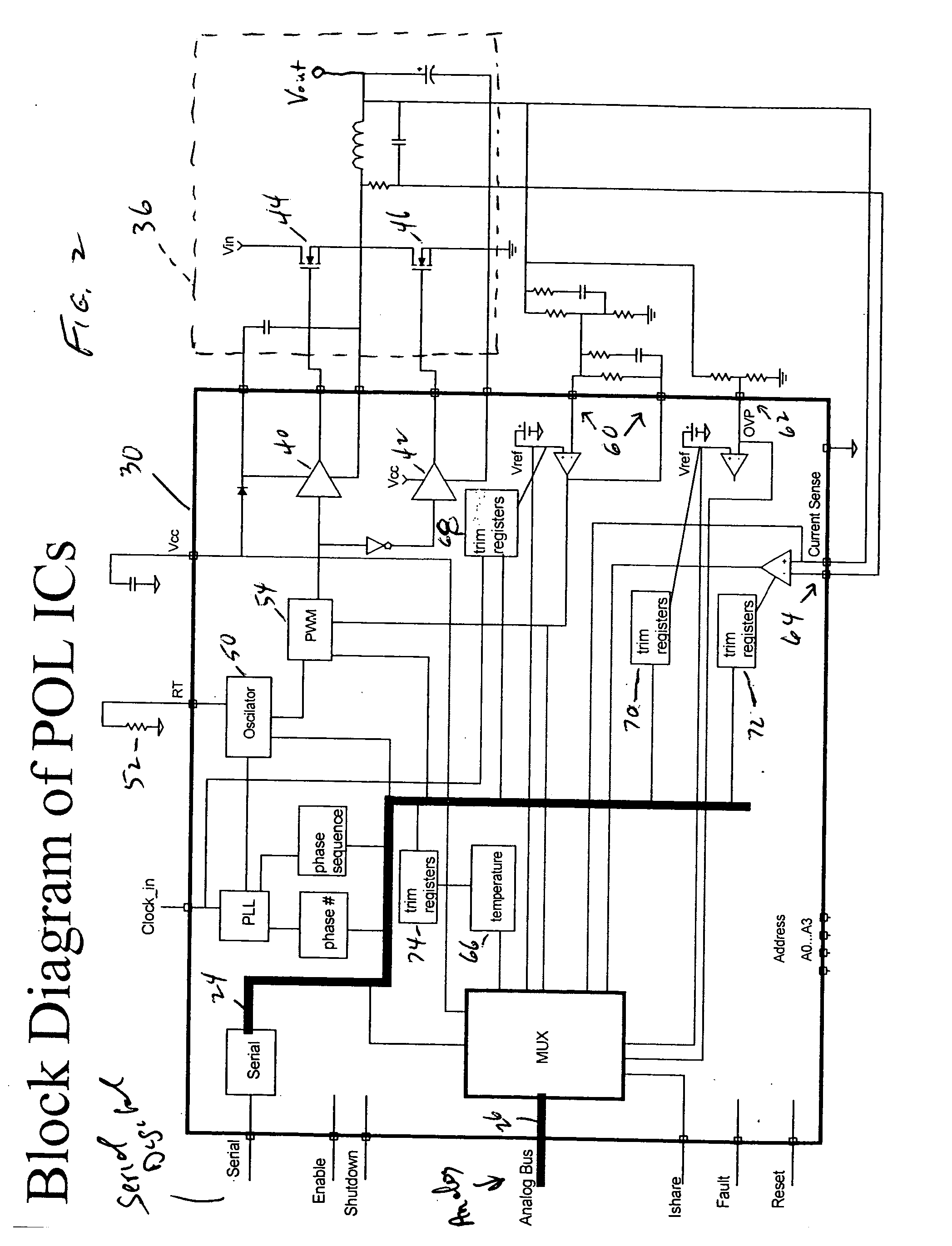

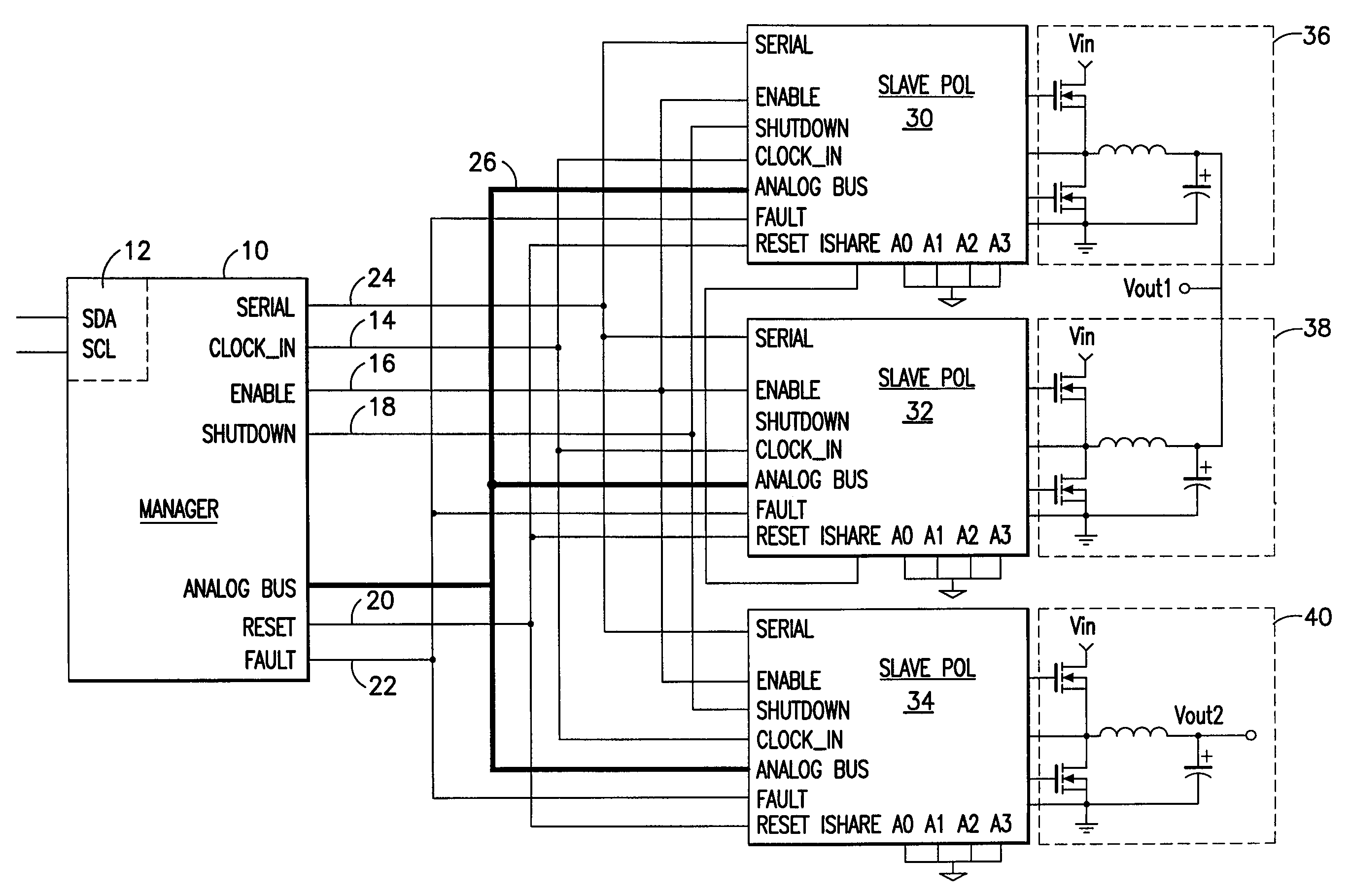

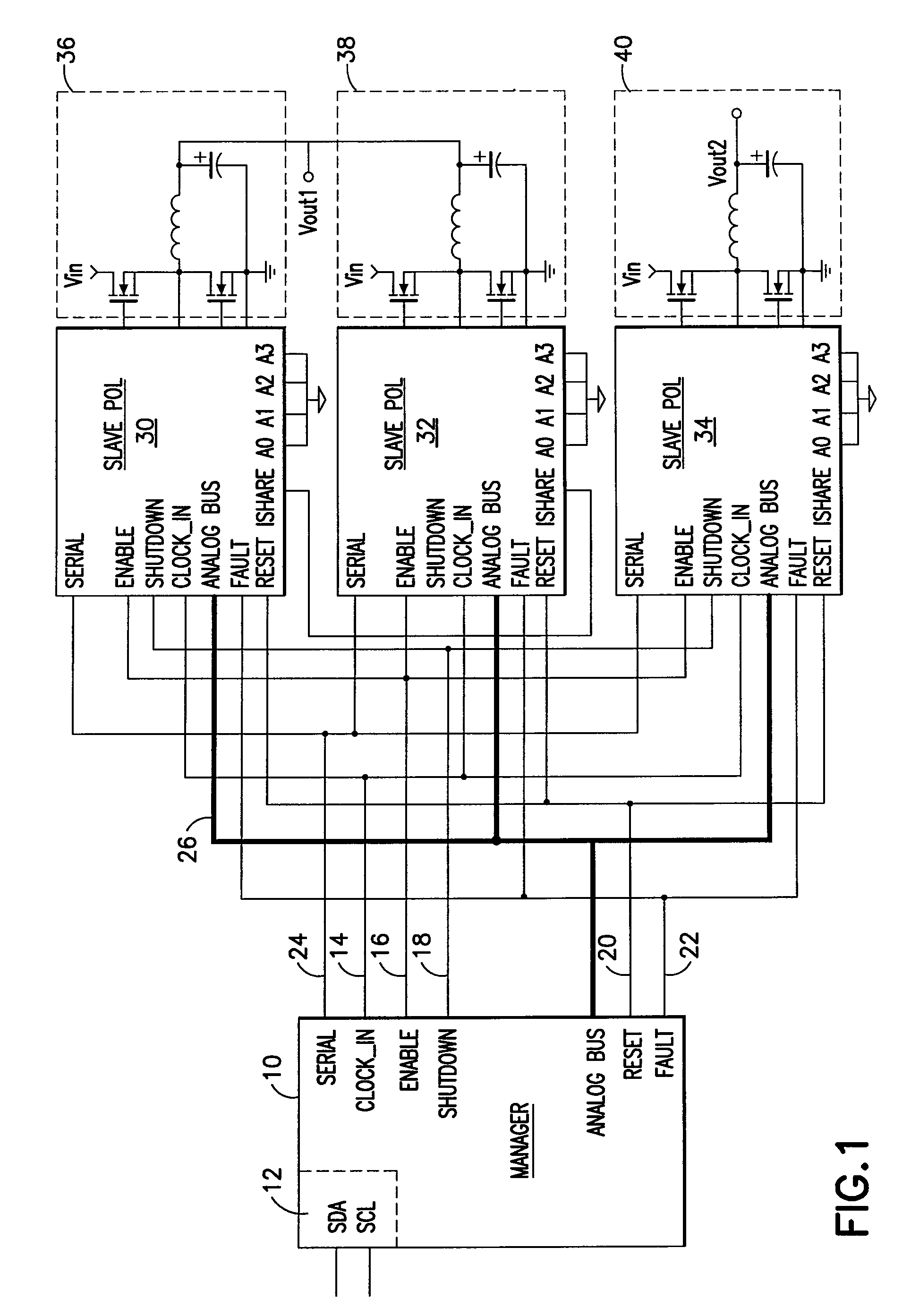

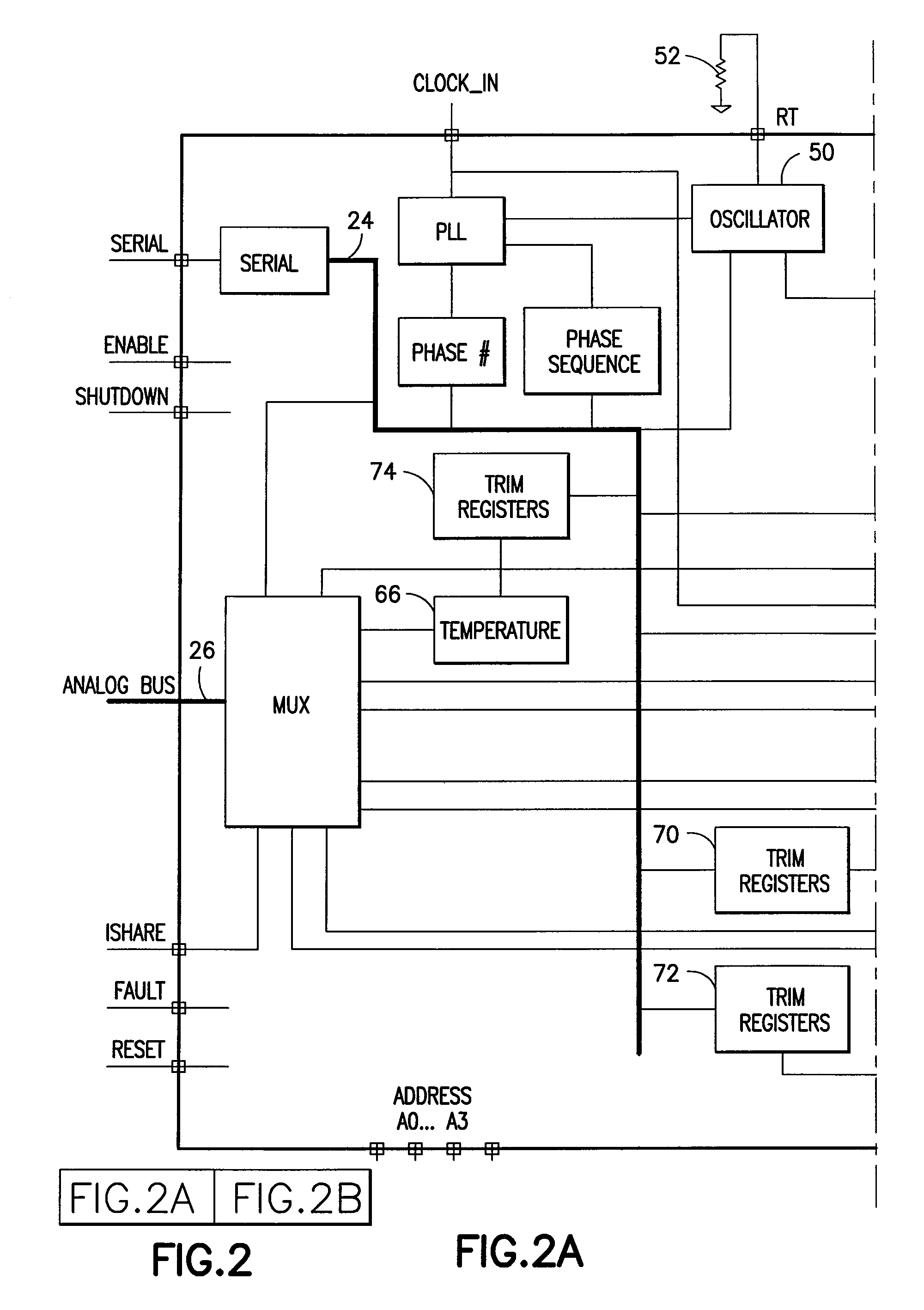

Pol system architecture with analog bus

ActiveUS20060212138A1Increase heightImprove accuracyProgramme controlDc network circuit arrangementsPoint of loadAudio power amplifier

A power control system and method including a plurality of point-of-load regulators (POL) providing corresponding regulated output voltages; a manager for communicating control signals and operational parameters with said point-of load regulators; a digital bus to carry control signals therebetween; and an analog bus to carry operational parameters therebetween. Analog sensing circuits and a mutliplexer on the POL communicate operational parameters to and from the manager via the analog bus and are controlled via the digital bus. The operational parameters include output voltage, output current, over voltage, temperature, amplifier or comparator offset, and amplifier gain. The analog sensing circuits are calibrated by trim registers on the POL under digital control by the manager.

Owner:INFINEON TECH AMERICAS CORP

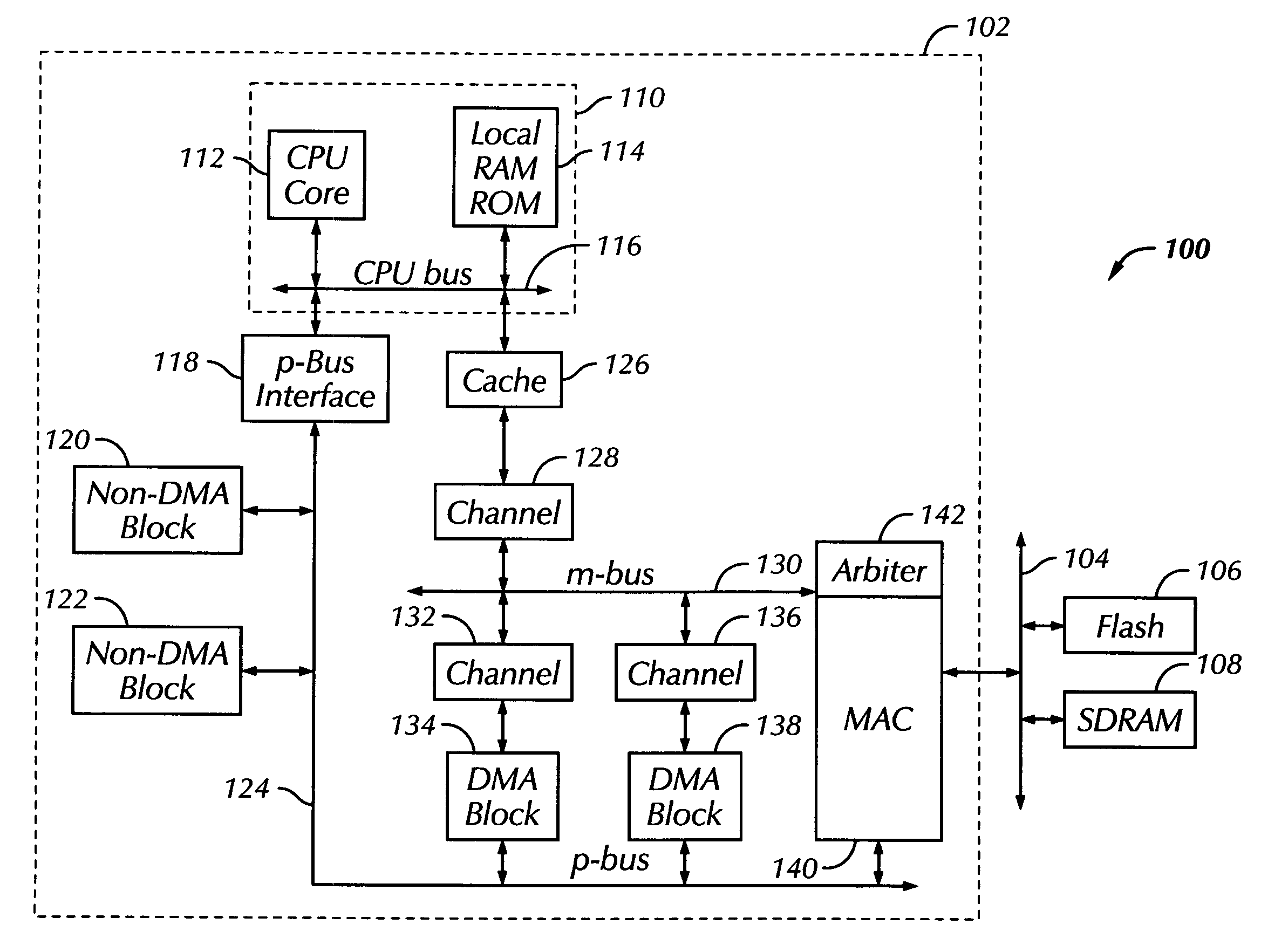

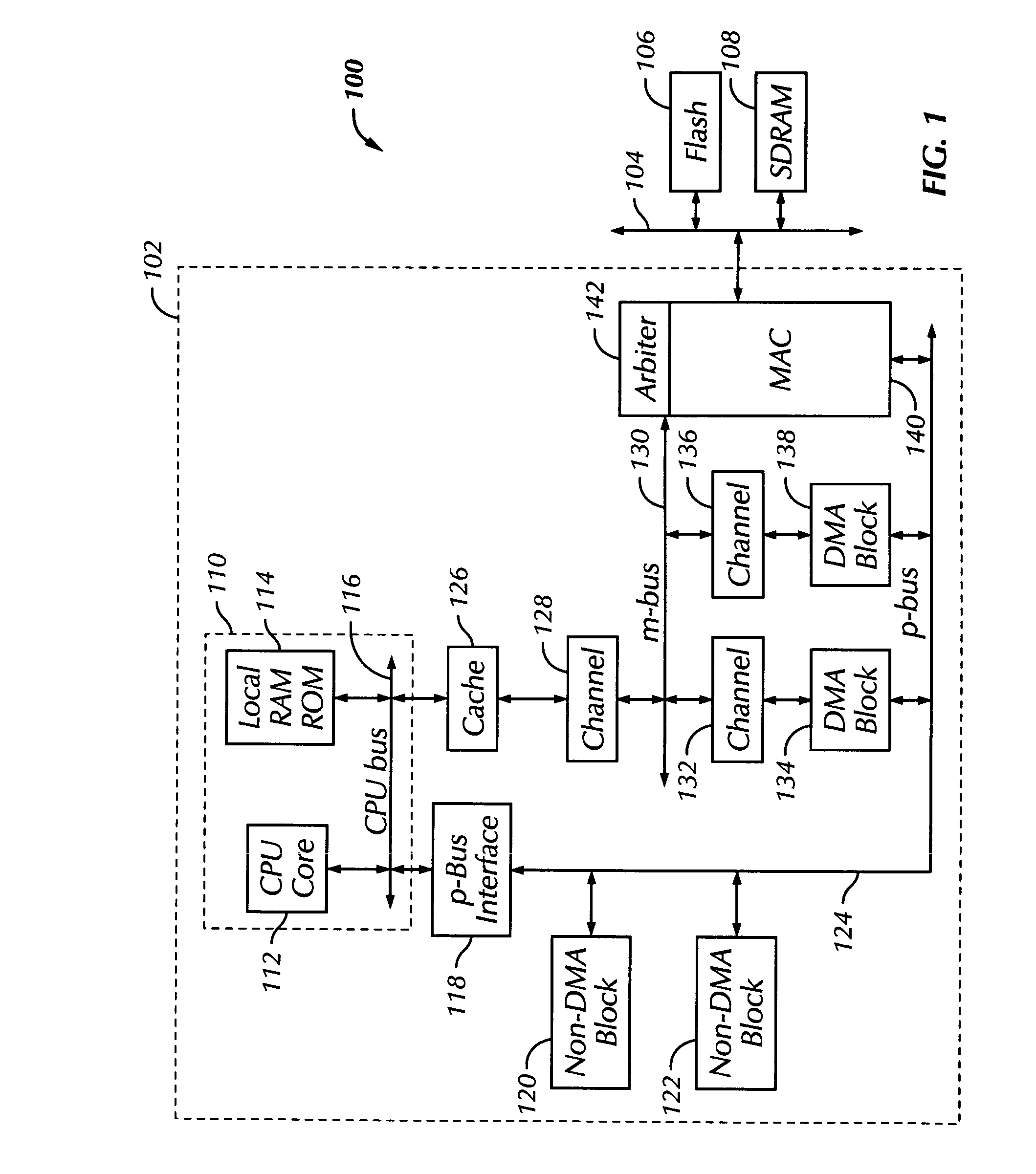

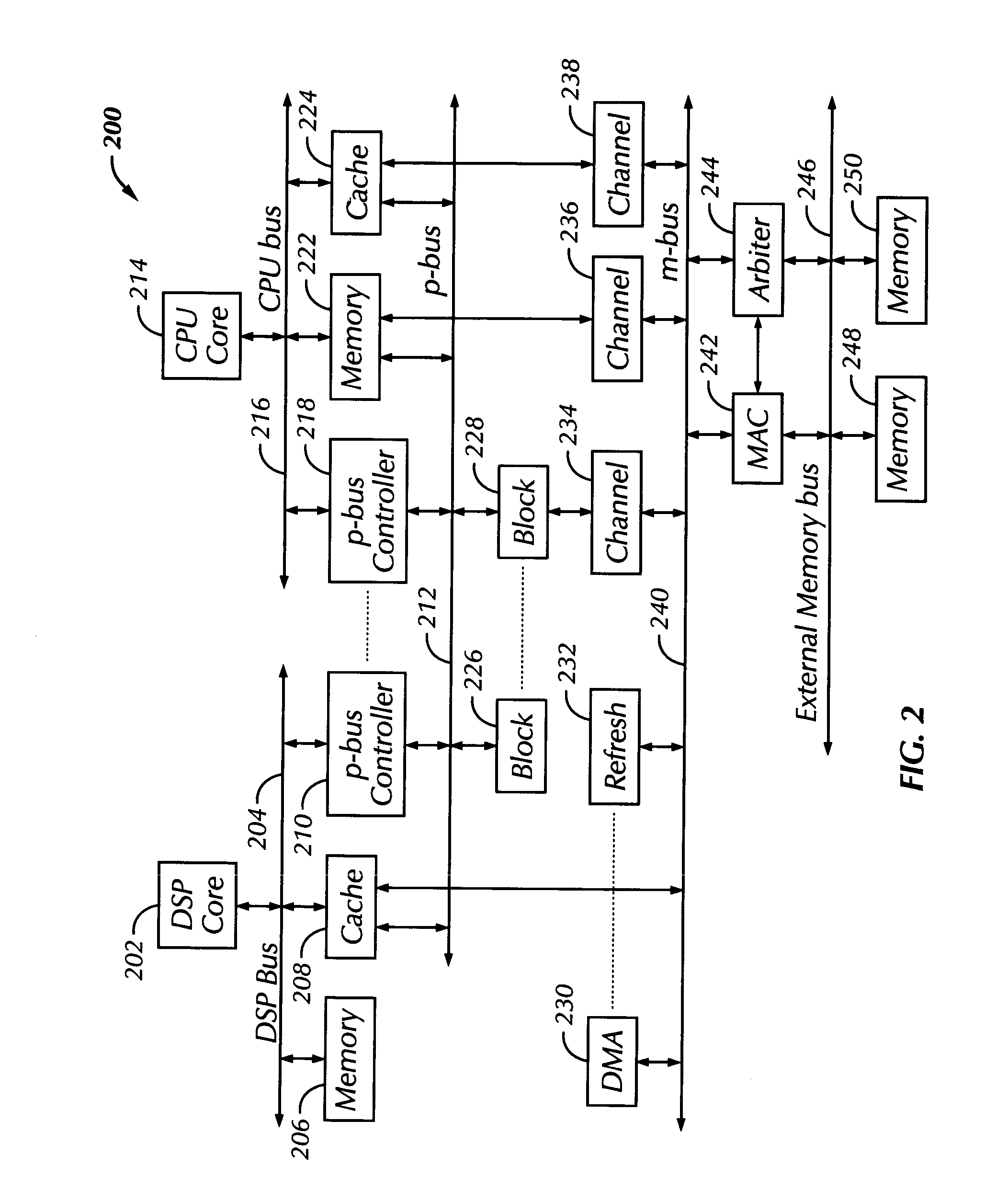

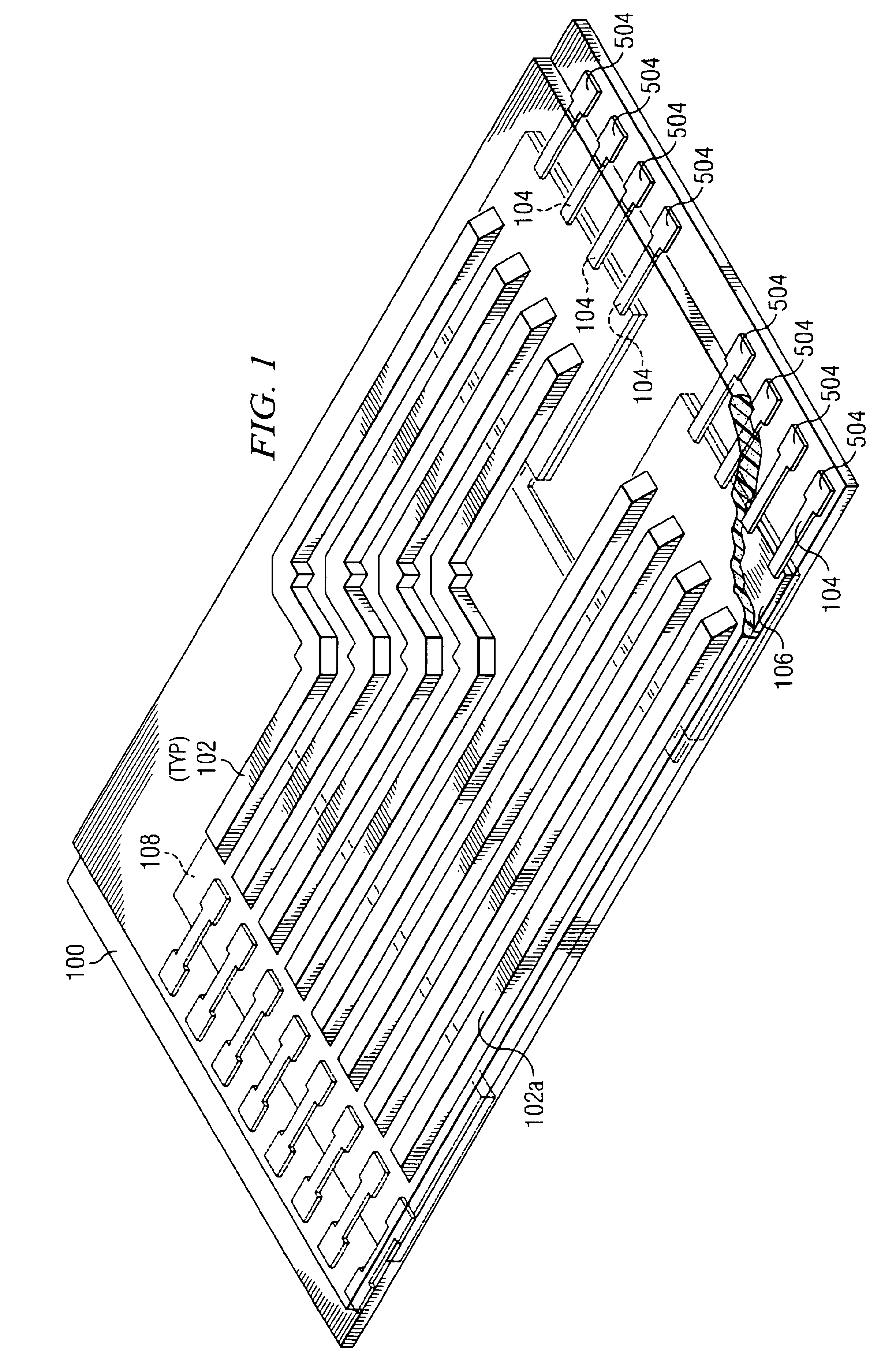

Unidirectional bus architecture for SoC applications

InactiveUS7062587B2Increase clock speedEnergy efficient ICTDigital storageControl signalEmbedded system

The System-on-Chip apparatus and integration methodology disclosed includes a single semiconductor integrated circuit having one or more processor subsystems, one or more DMA-type peripherals, and a Memory Access Controller (MAC) on a first internal unidirectional bus. The first internal unidirectional bus controls transactions between the processor subsystem(s) and the DMA peripheral(s) using a Memory Access Controller (MAC) and unidirectional, positive-edge clocked address and transaction control signals. The first internal unidirectional bus can support burst operation, variable-speed pipelined memory transactions, and hidden arbitration. The SoC may include a second internal unidirectional bus that controls transactions between the processor subsystem(s) and non-DMA peripherals. The second internal unidirectional bus controls transactions between the processor subsystem(s) and the non-DMA peripheral(s) using unidirectional address and transaction control signals. Peripherals may be synchronous or asynchronous to their respective buses.

Owner:NETVINCI

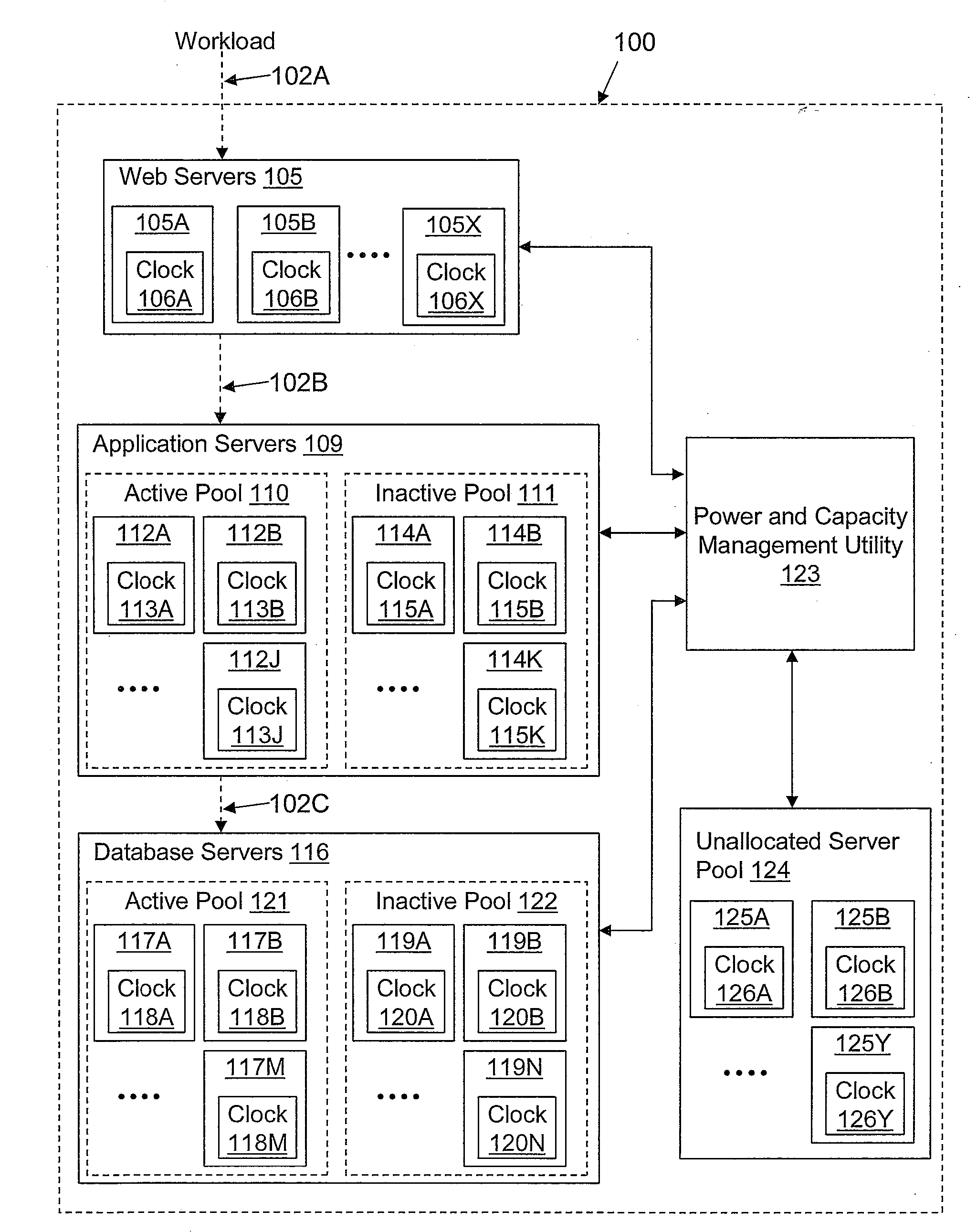

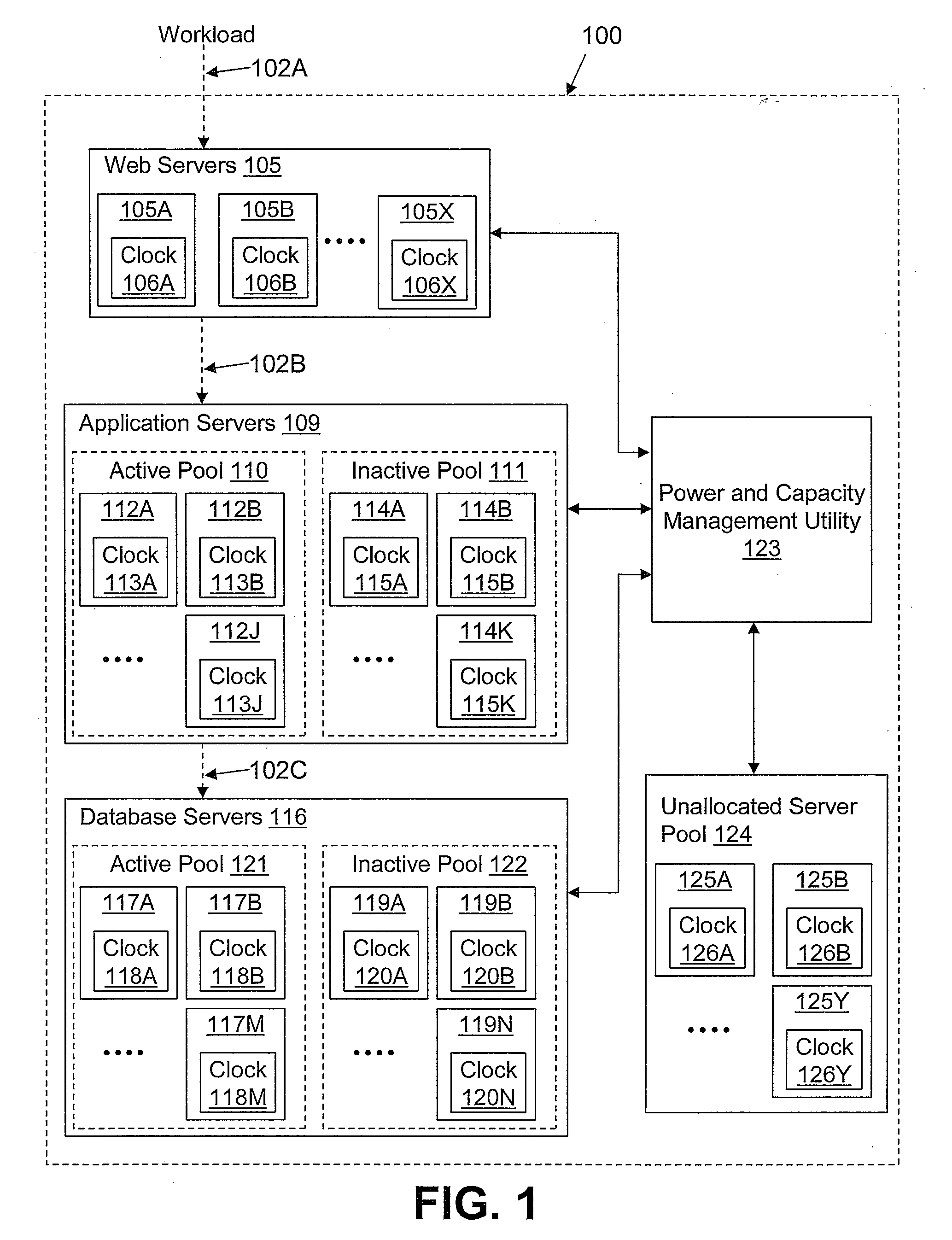

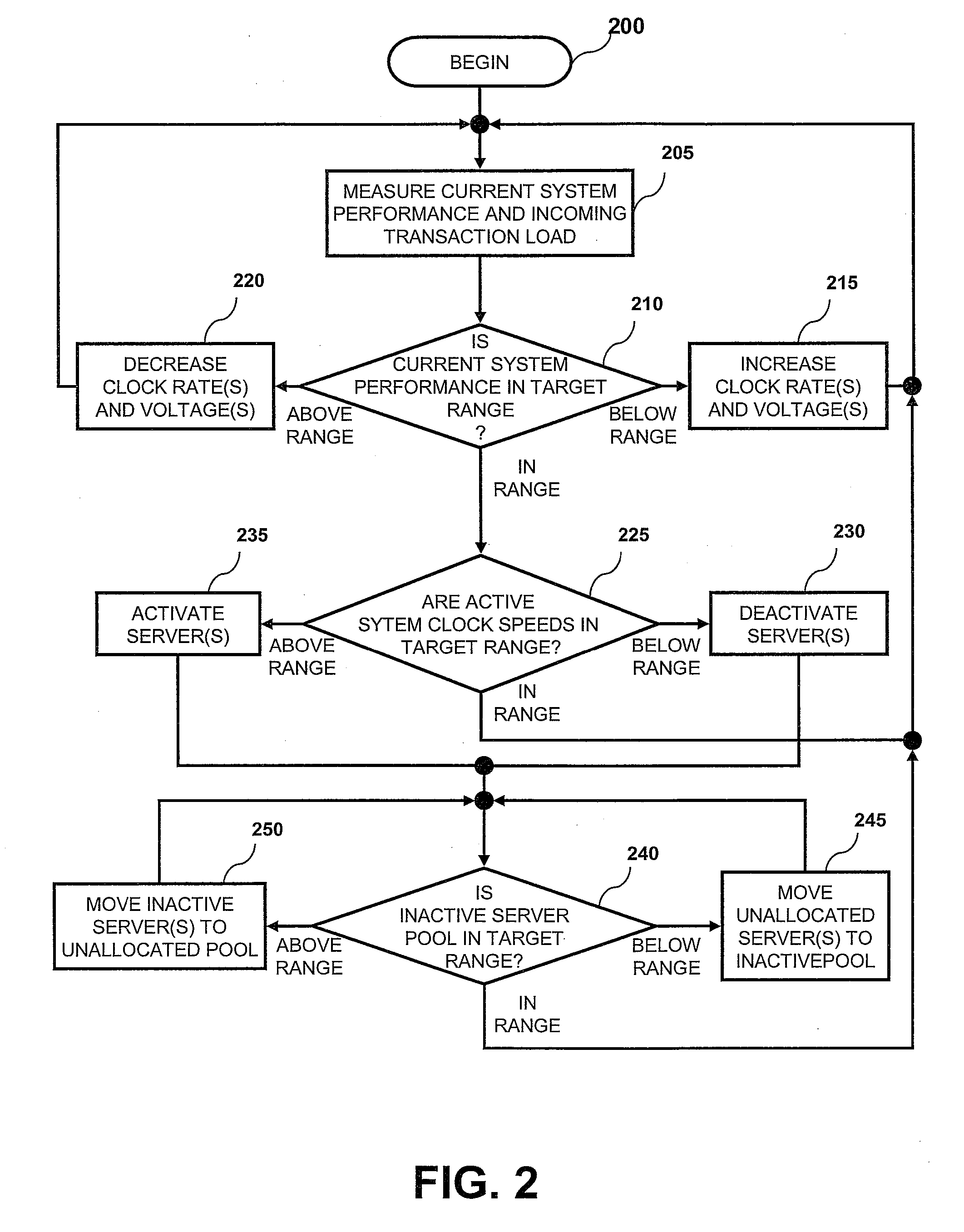

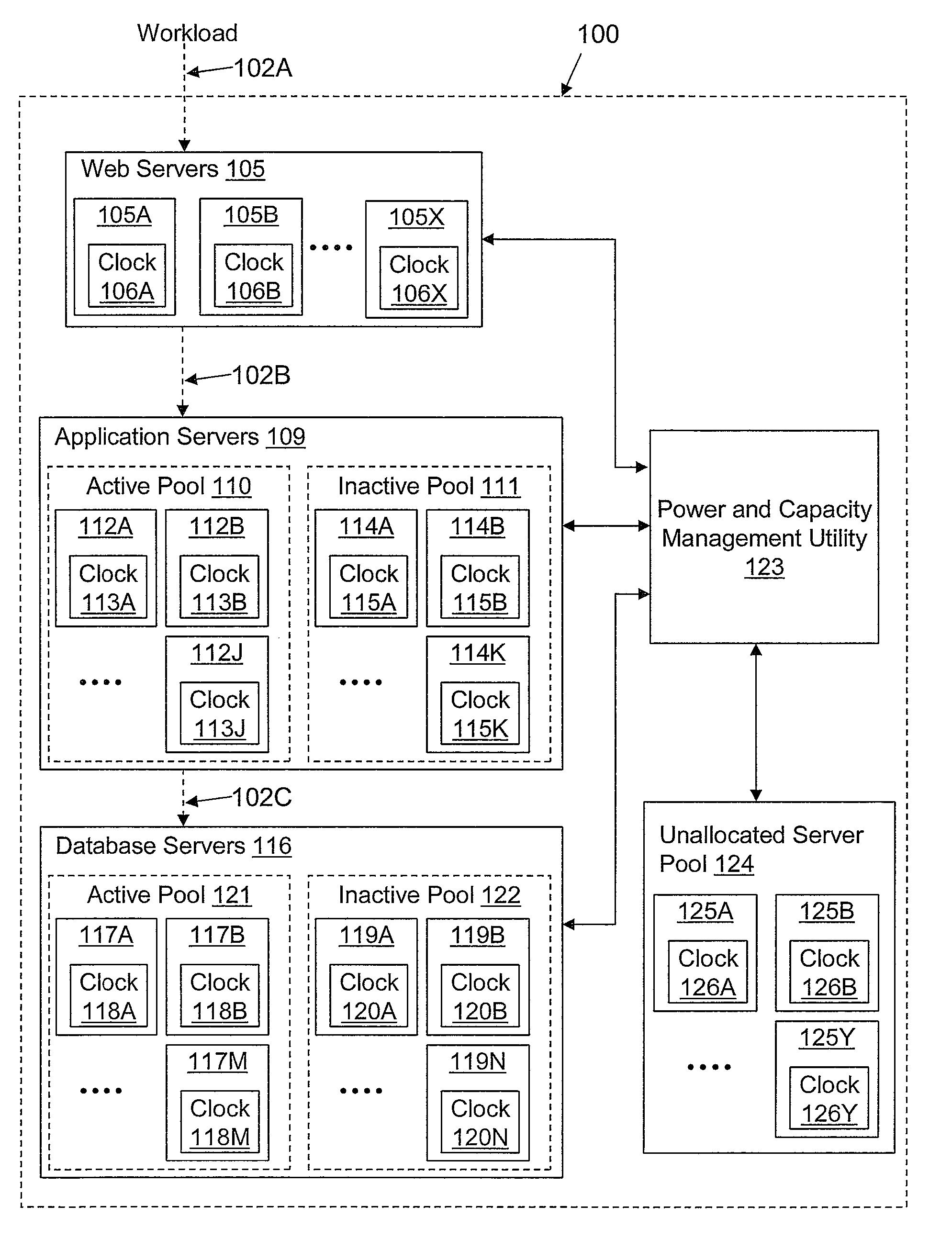

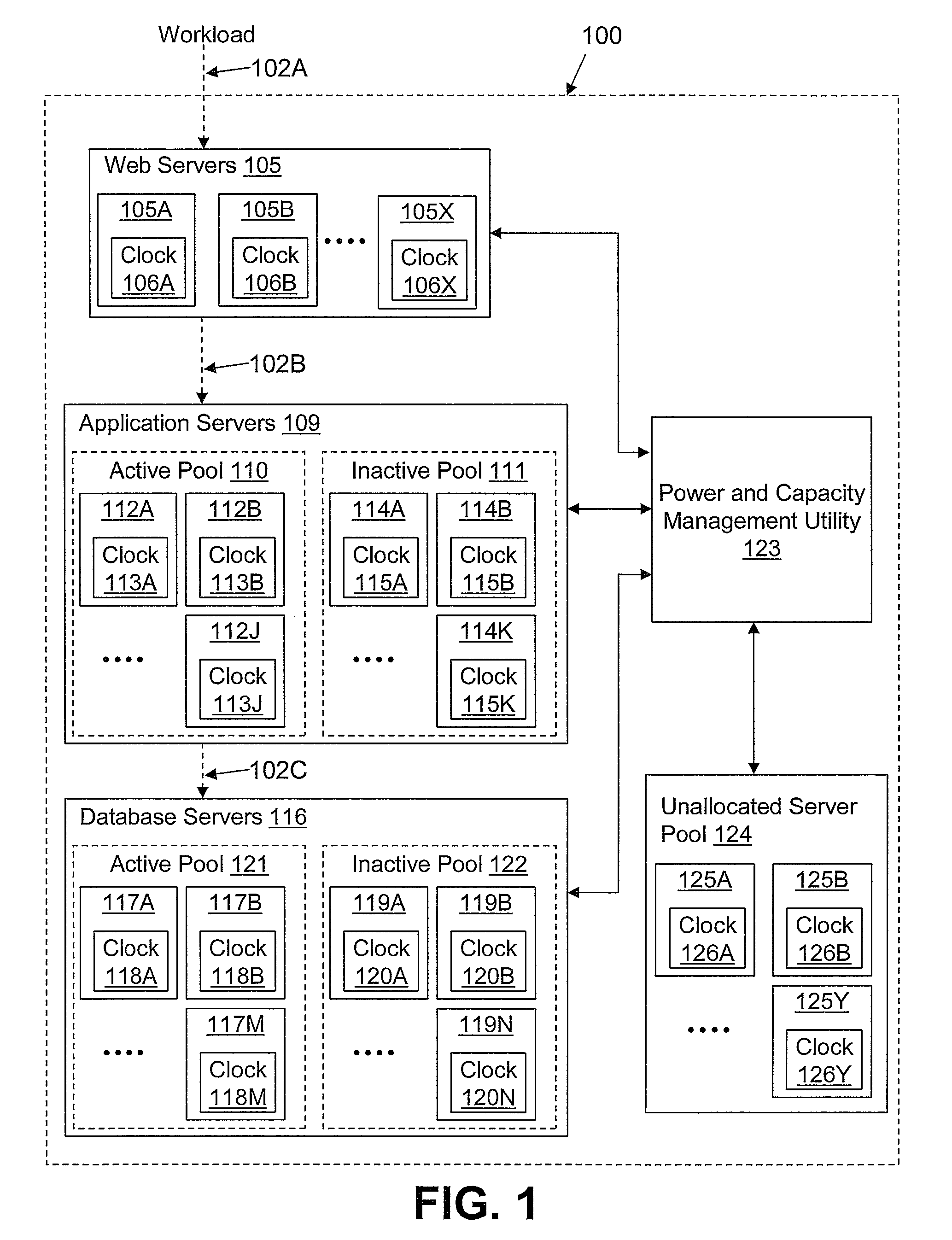

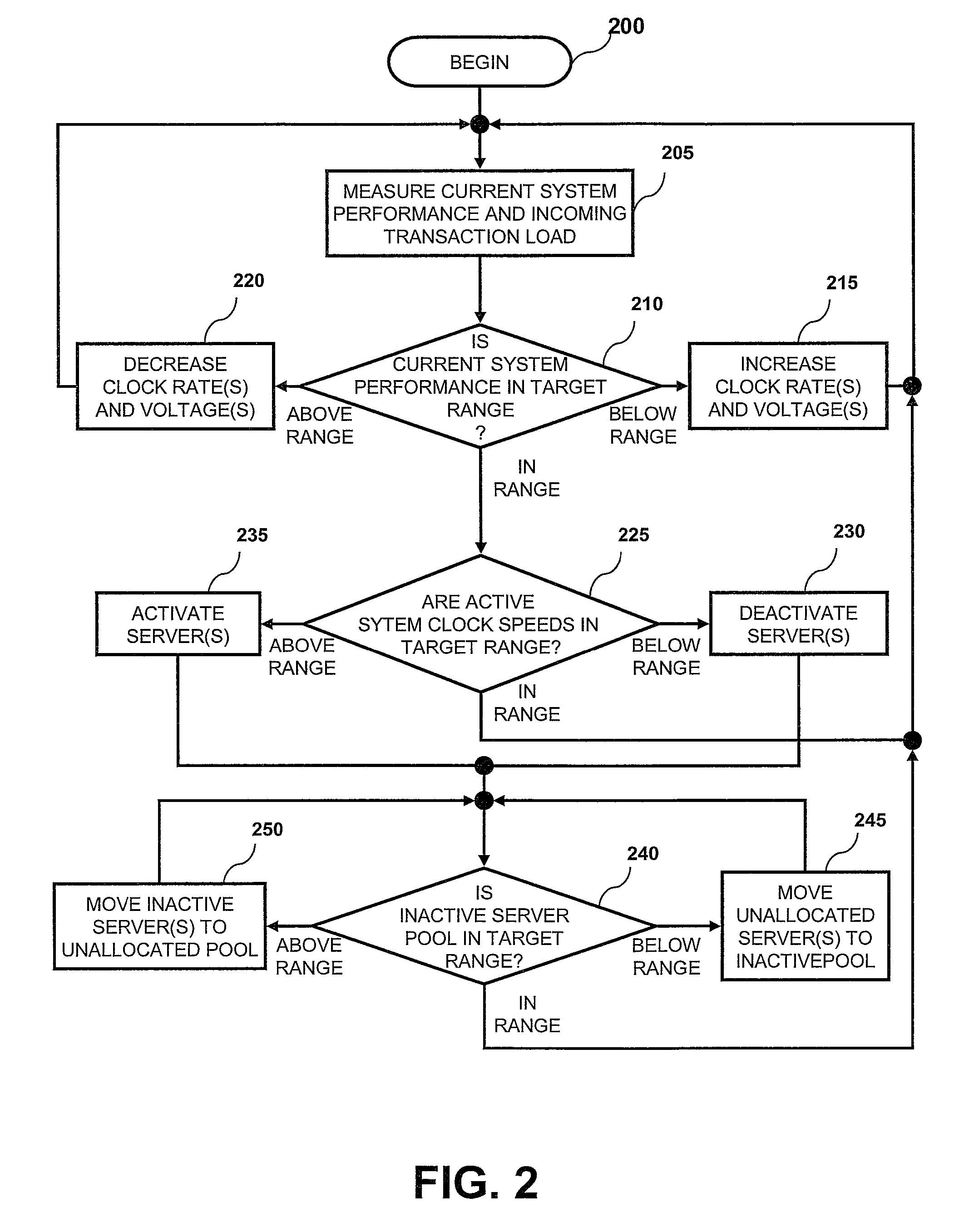

Method and system for managing data center power usage based on service commitments

ActiveUS20080301479A1Reduce power consumptionReduce rateDigital data processing detailsDigital computer detailsClock rateData center

A method of managing data center power usage based on service commitments. A power and capacity management utility measures performance characteristics of applications hosted by a data center that include power consumption and transaction processing time. When the performance characteristics are above (or below) a first pre-defined target range, the utility decreases (or increases, respectively) a clock rate and processor voltage of one or more active servers. When the performance characteristics are within the first target range and the clock speed is above (or below) a second pre-defined target range, the utility activates (or deactivates, respectively) one or more inactive (or active, respectively) servers. When the size of an inactive server pool is above a third pre-defined target range, the utility moves inactive servers to an unallocated server pool. When the size of the inactive server pool is below the third target range, the utility allocates additional servers.

Owner:TWITTER INC

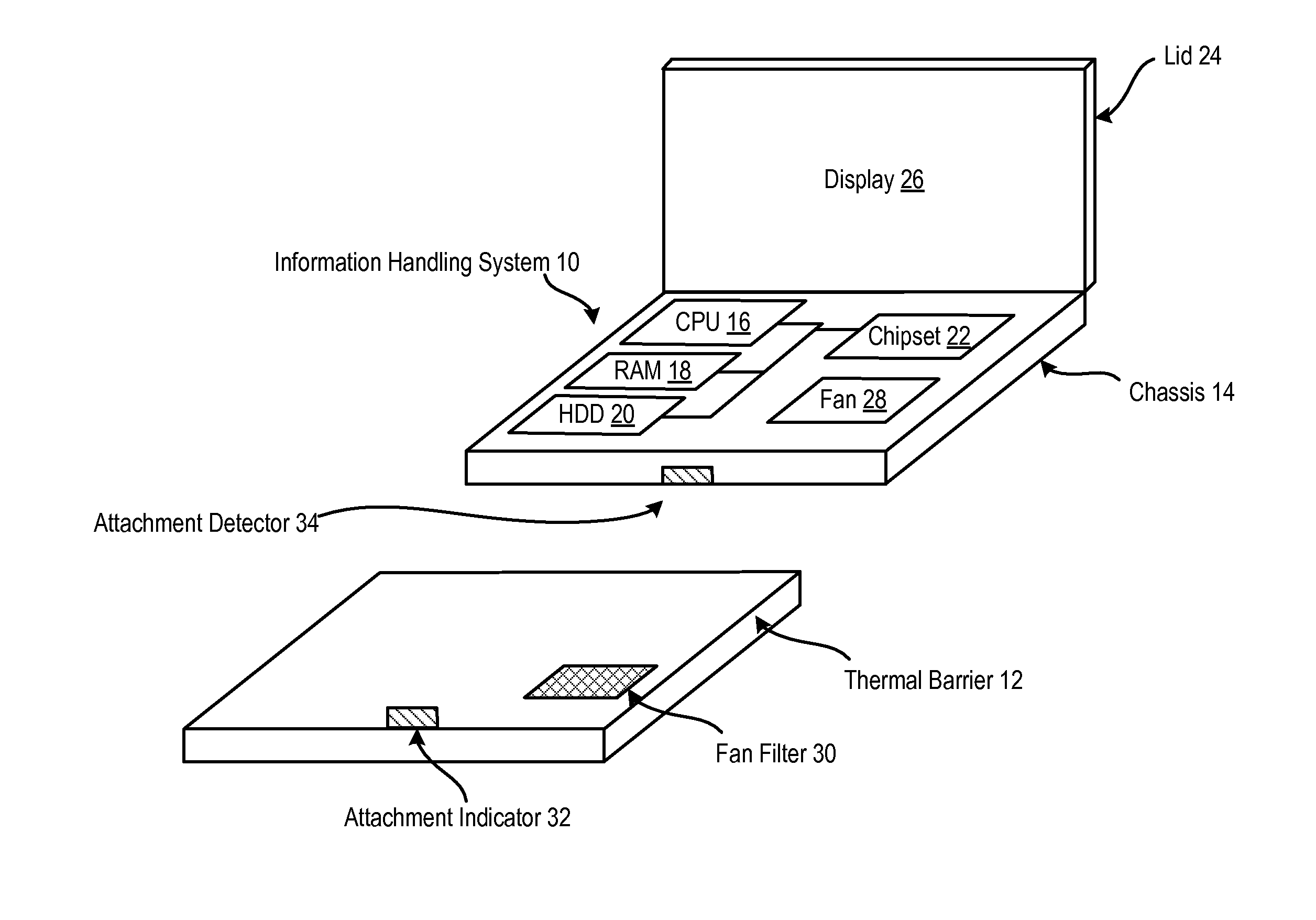

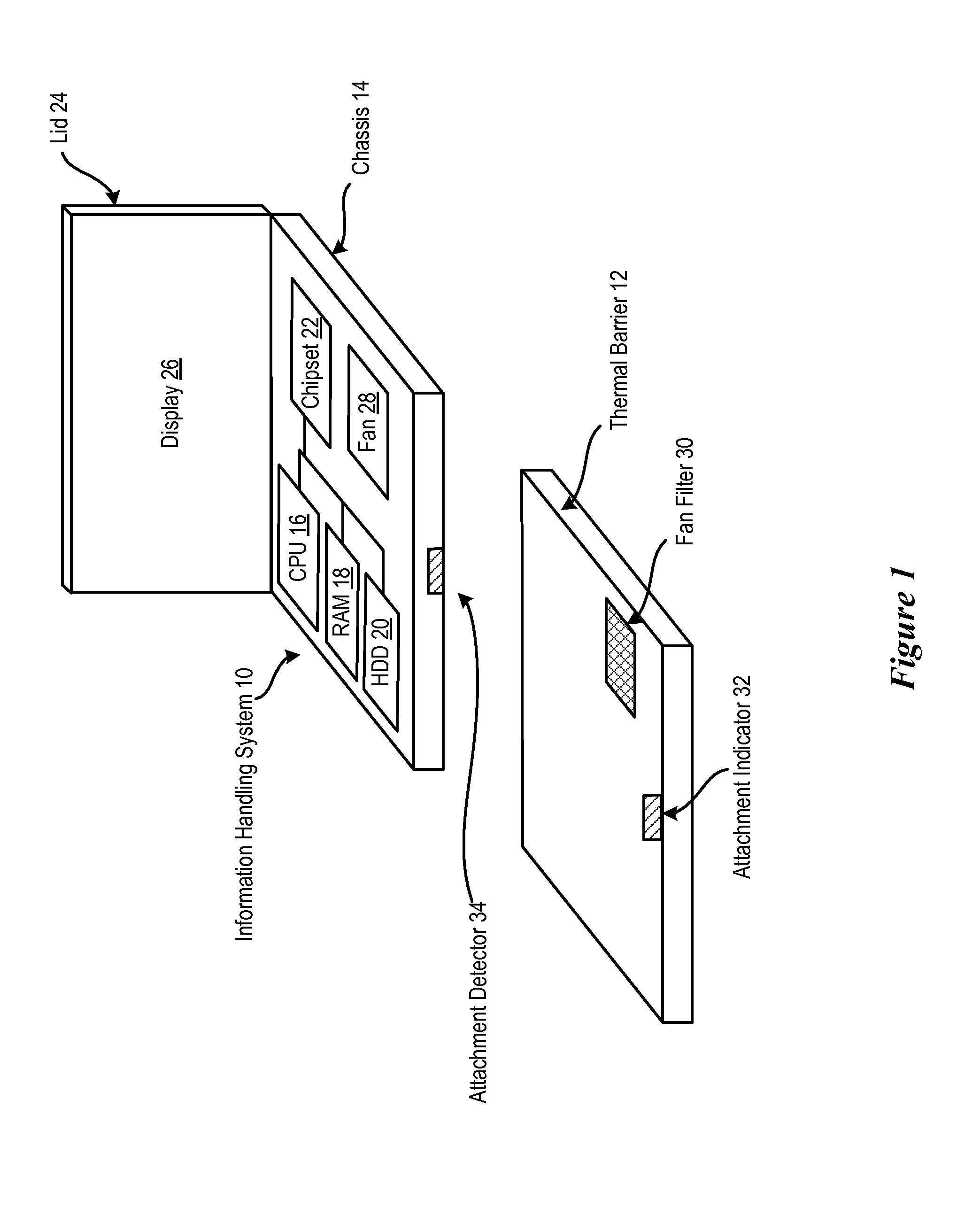

System and Method for Portable Information Handling System Parallel-Wall Thermal Shield

ActiveUS20090323275A1Reduce disadvantagesReduce problemsEnergy efficient ICTDigital data processing detailsThermal energyEngineering

An information handling system's thermal management is selectively altered by coupling a thermal barrier to the bottom surface of the information handling system chassis so that an air channel insulates against the passage of thermal energy from the bottom surface. A vent opening in a side of the thermal barrier allows airflow through the air channel to a vent opening of the information handling system. The airflow through the air channel cools the base of the thermal barrier so that an end user will experience reduced thermal energy if the information handling system rests on the end user, such as in the end user's lap.

Owner:DELL PROD LP

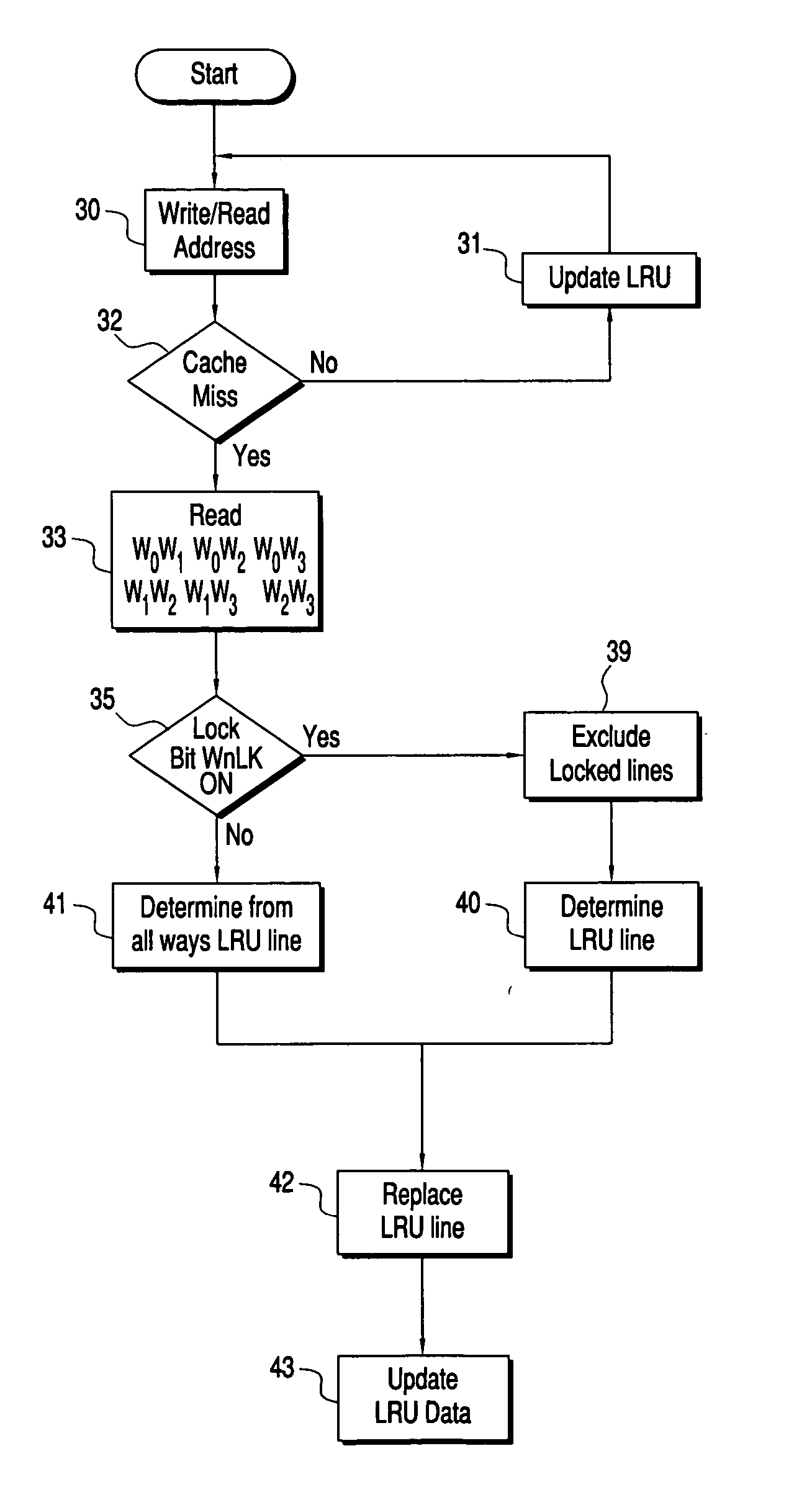

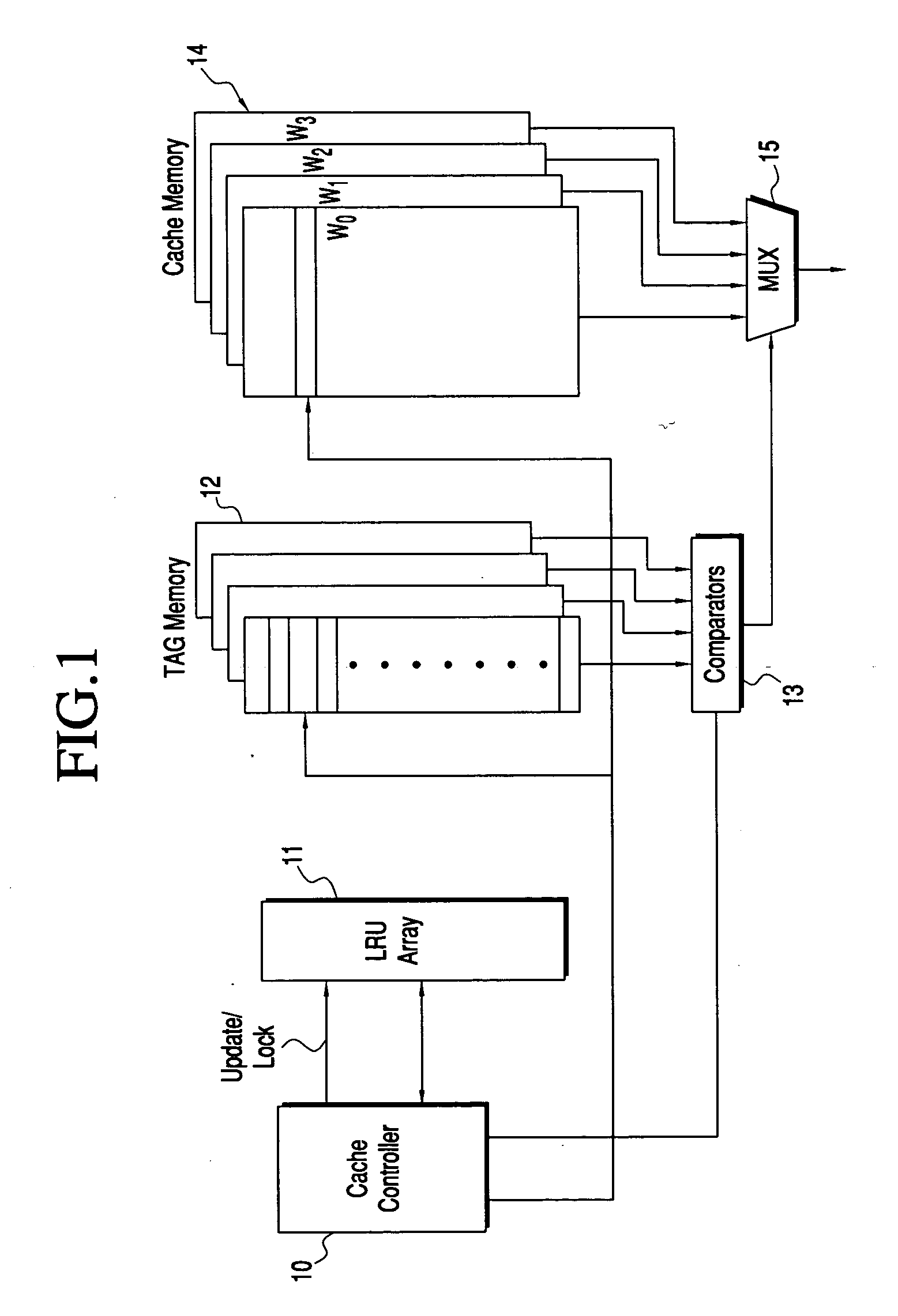

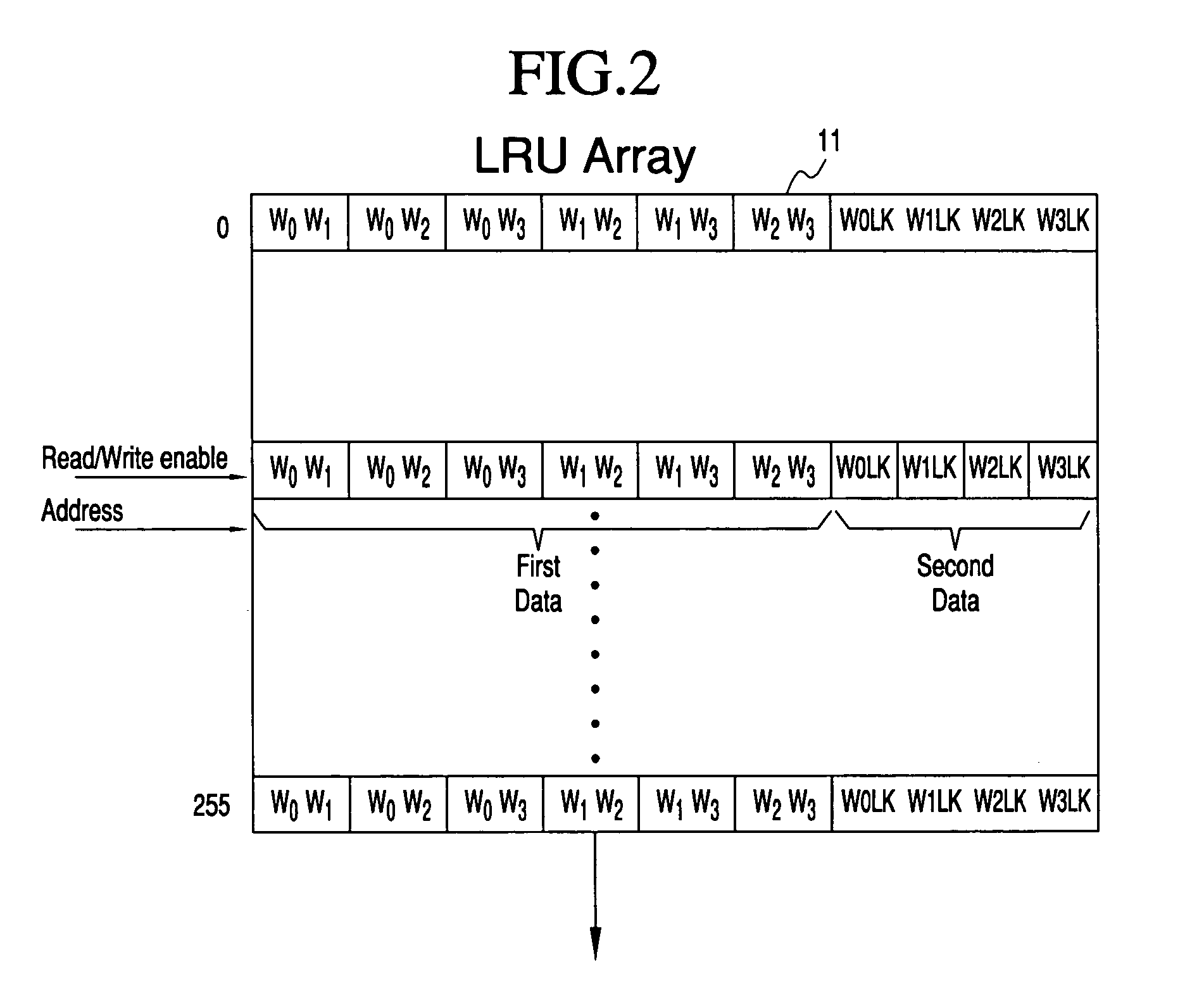

Method for software controllable dynamically lockable cache line replacement system

InactiveUS20060036811A1Shorten access timeSpeed up access timeMemory systemsParallel computingAccess line

An LRU array and method for tracking the accessing of lines of an associative cache. The most recently accessed lines of the cache are identified in the table, and cache lines can be blocked from being replaced. The LRU array contains a data array having a row of data representing each line of the associative cache, having a common address portion. A first set of data for the cache line identifies the relative age of the cache line for each way with respect to every other way. A second set of data identifies whether a line of one of the ways is not to be replaced. For cache line replacement, the cache controller will select the least recently accessed line using contents of the LRU array, considering the value of the first set of data, as well as the value of the second set of data indicating whether or not a way is locked. Updates to the LRU occur after each pre-fetch or fetch of a line or when it replaces another line in the cache memory.

Owner:GOOGLE LLC

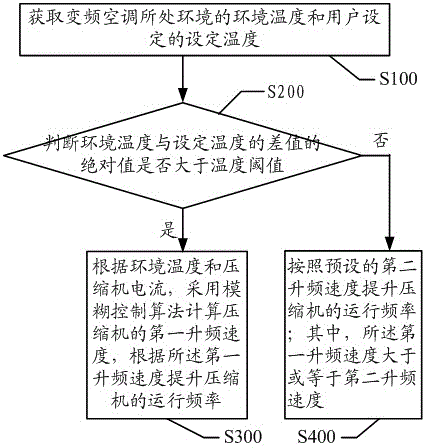

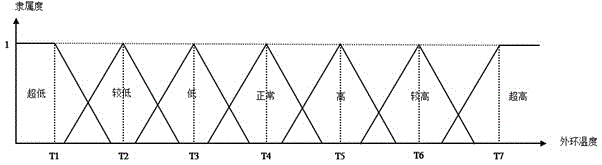

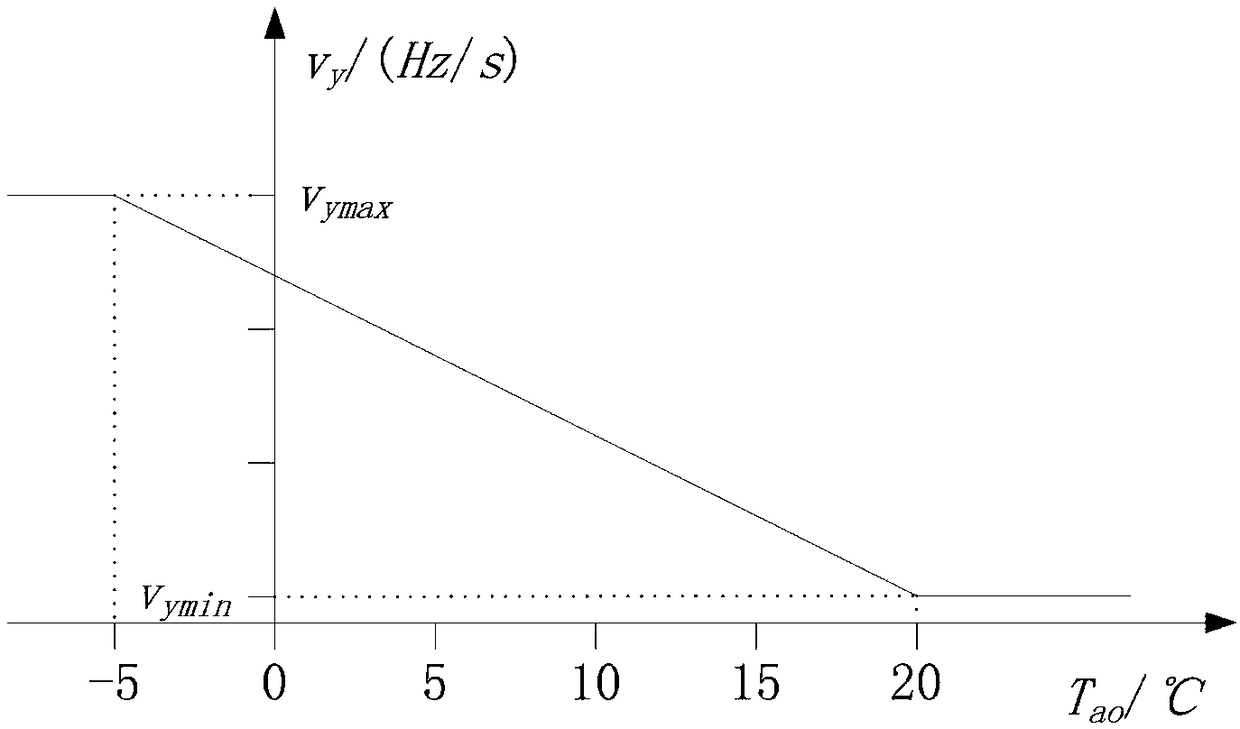

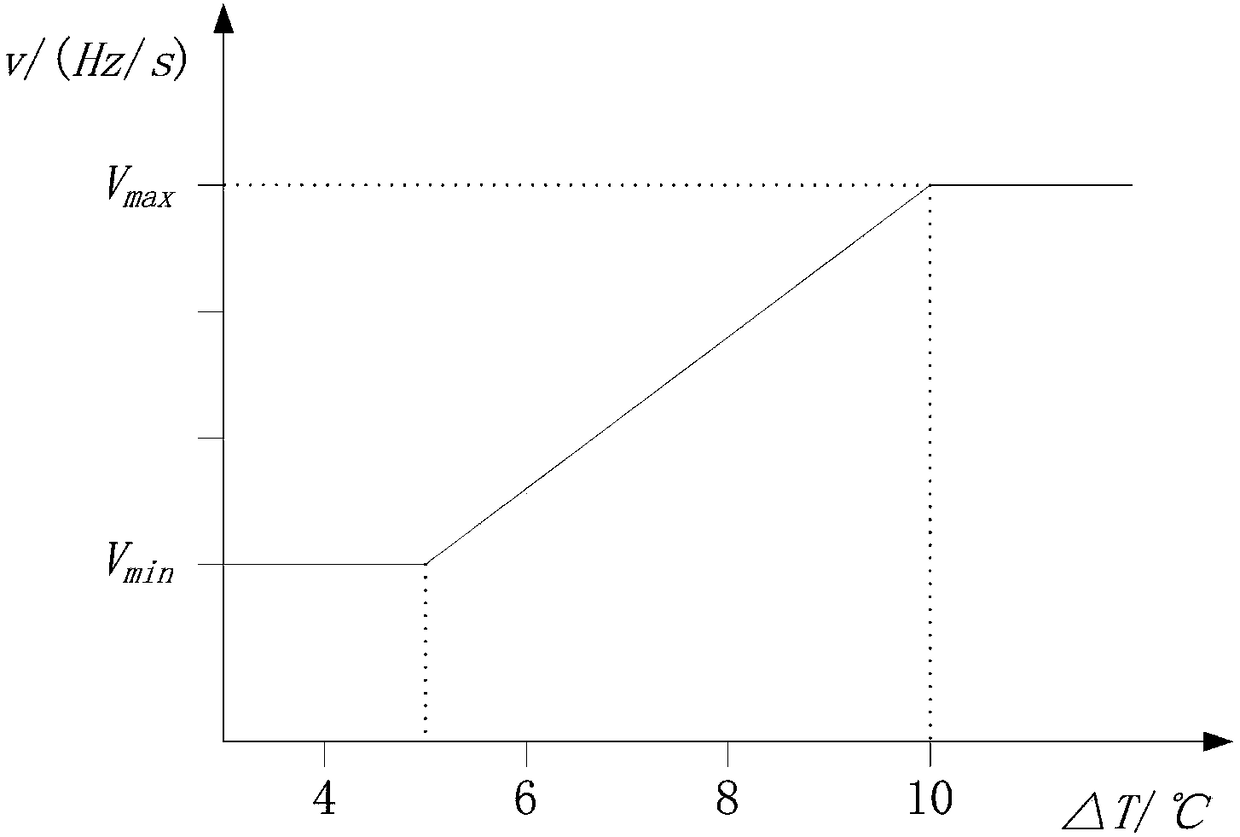

Frequency increasing method and system for variable frequency air conditioner

ActiveCN105135618ASolve the cooling effectImprove heating effectSpace heating and ventilation safety systemsLighting and heating apparatusFuzzy control algorithmElectrical and Electronics engineering

The invention discloses a frequency increasing method and system for a variable frequency air conditioner. The frequency increasing method comprises the steps that the environment temperature of the environment where the variable frequency air conditioner is located and the set temperature set by a user are acquired; whether an absolute value of a difference value between the environment temperature and the set temperature is larger than a temperature threshold value is judged; if yes, the first frequency increasing speed of a compressor is calculated through a fuzzy control algorithm according to the environment temperature and the compressor current, and the operation frequency of the compressor is increased according to the first frequency increasing speed; if not, the operation frequency of the compressor is increased according to the preset second frequency increasing speed; the first frequency increasing speed is higher than or equal to the second frequency increasing speed. According to the frequency increasing method and system, the frequency increasing speed of the compressor can be quickly increased to achieve the purpose of quick refrigerating or heating, and therefore great convenience is brought to a user.

Owner:SHENZHEN SKYWORTH AIR CONDITIONING TECH CO LTD

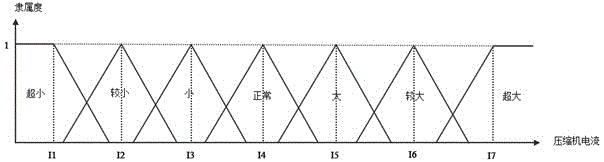

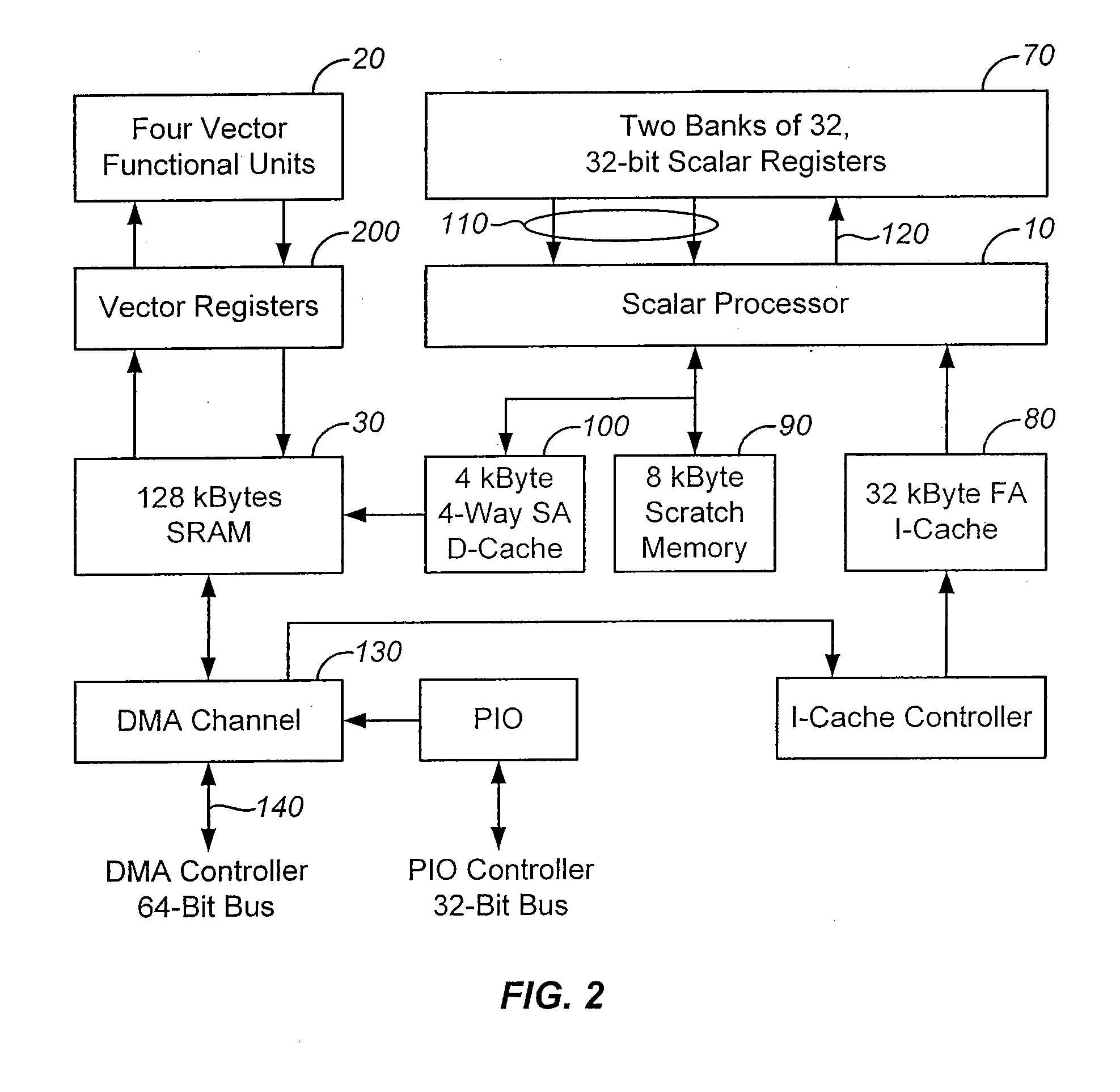

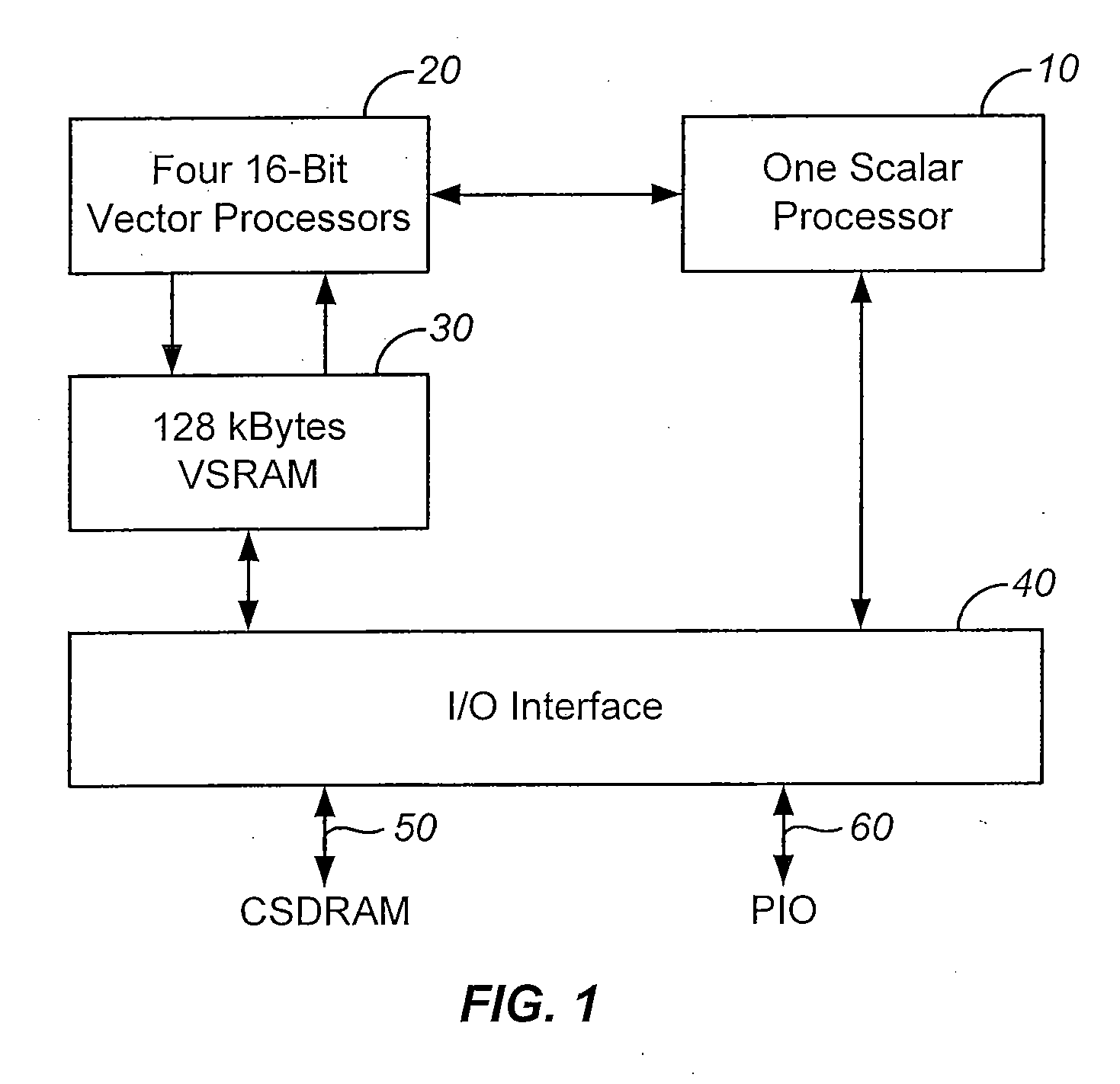

Memory architecture for vector processor

InactiveUS20080059758A1Limited instruction widthGreat instruction widthConditional code generationRegister arrangementsRapid processingTerm memory

A vector processor includes a set of vector registers for storing data to be used in the execution of instructions and a vector functional unit coupled to the vector registers for executing instructions. The functional unit executes instructions using operation codes provided to it which operation codes include a field referencing a special register. The special register contains information about the length and starting point for each vector instruction. A series of new instructions to enable rapid handling of image pixel data are provided.

Owner:MEADLOCK JAMES W MEAD

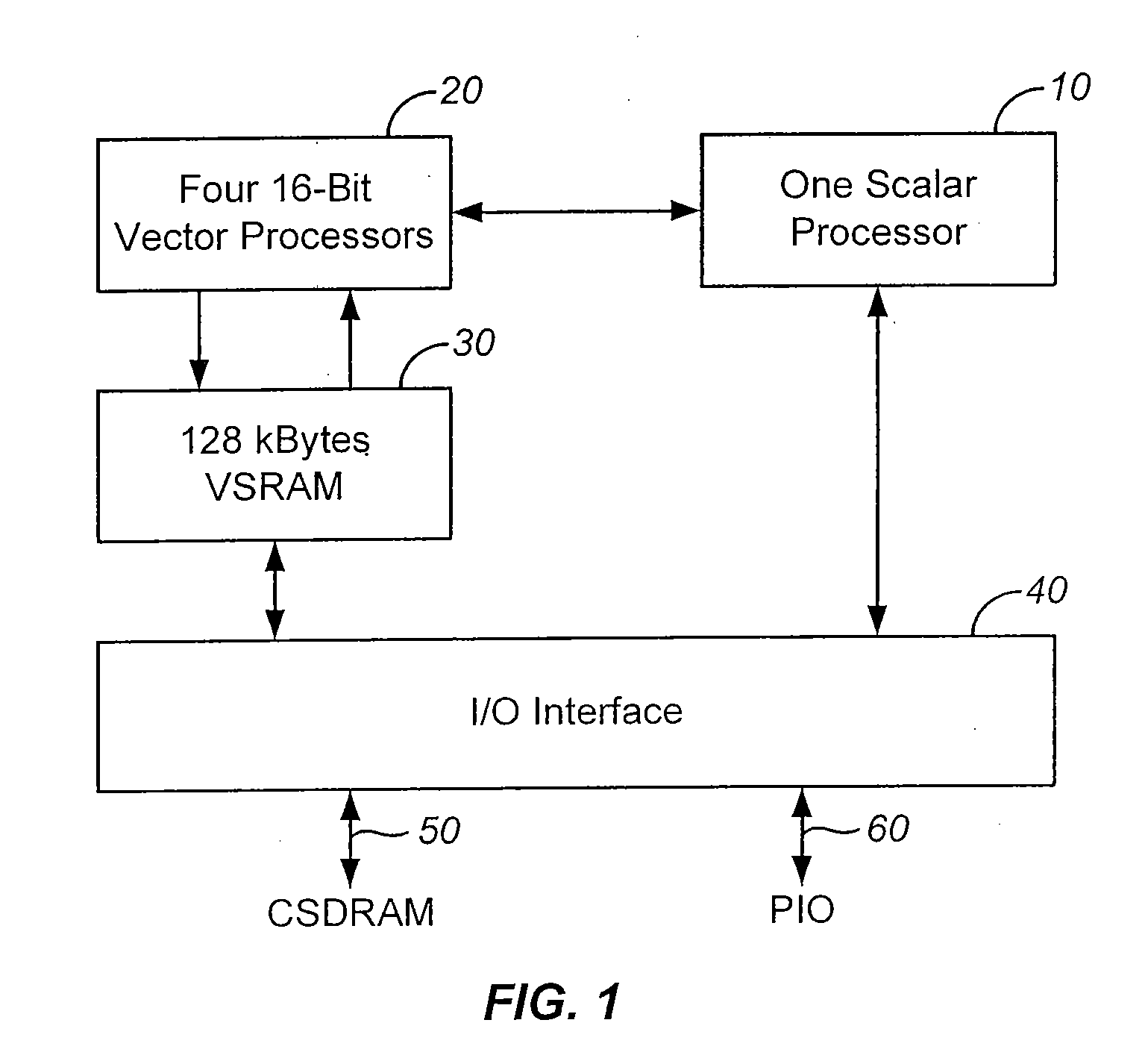

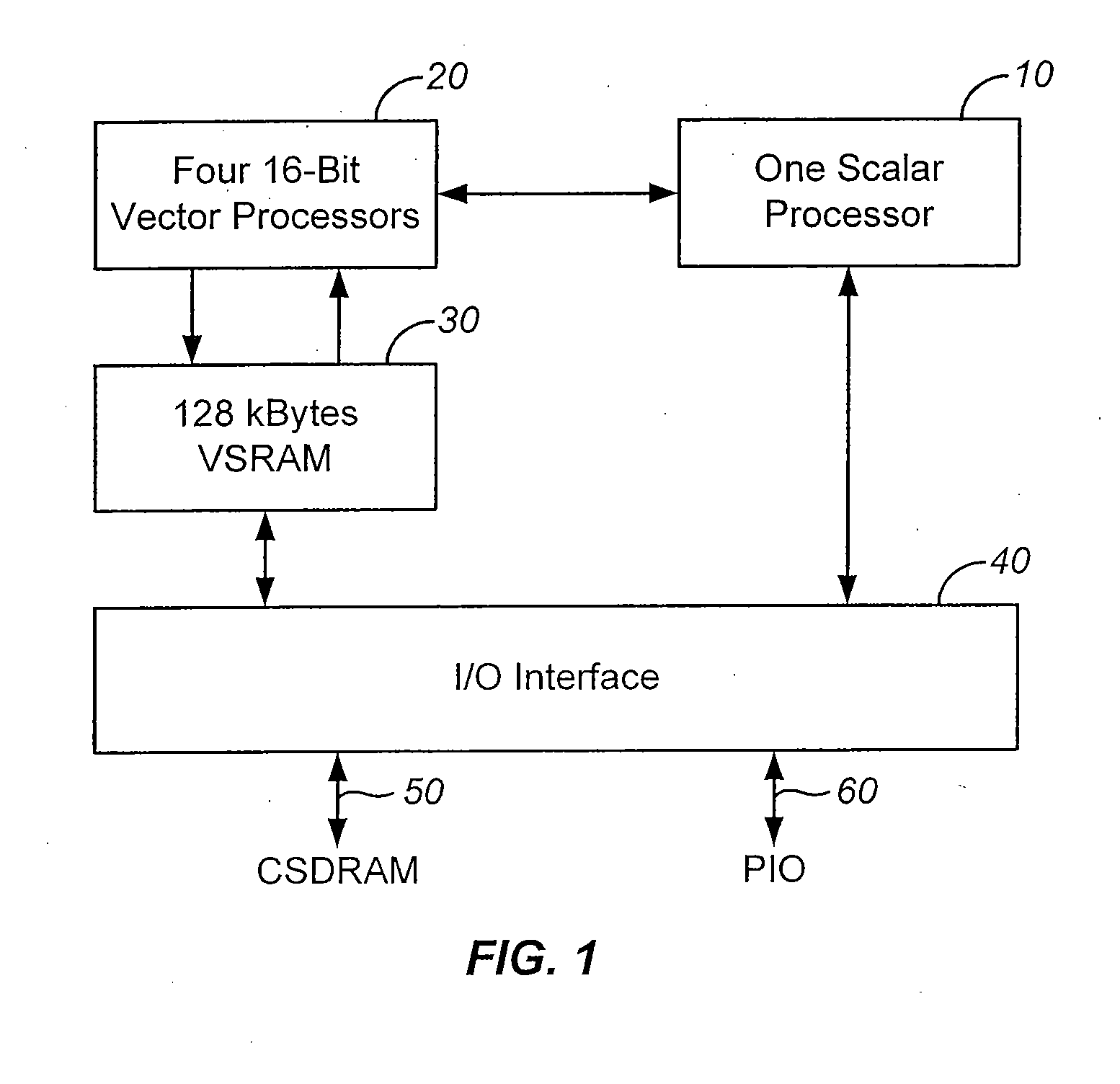

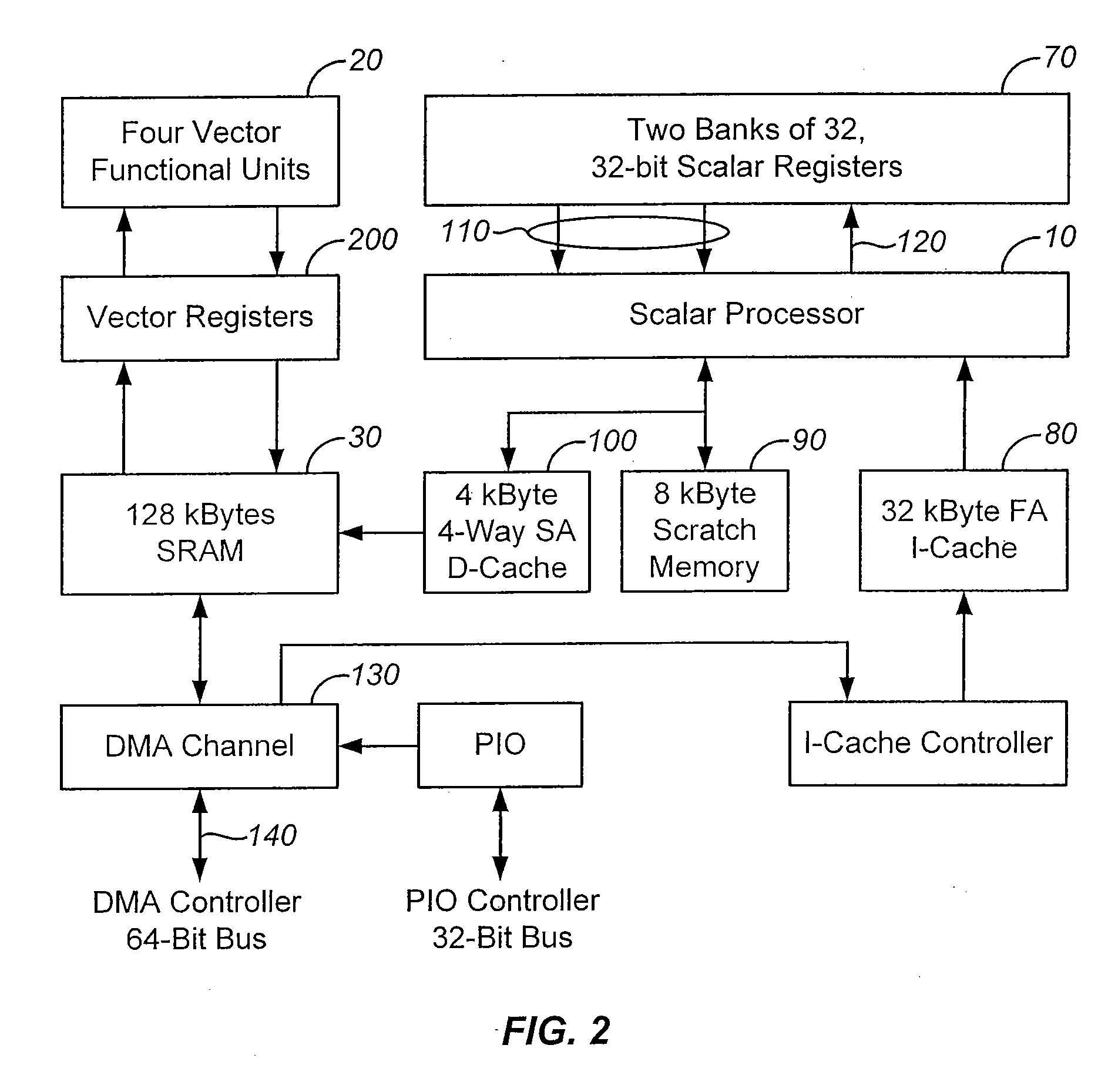

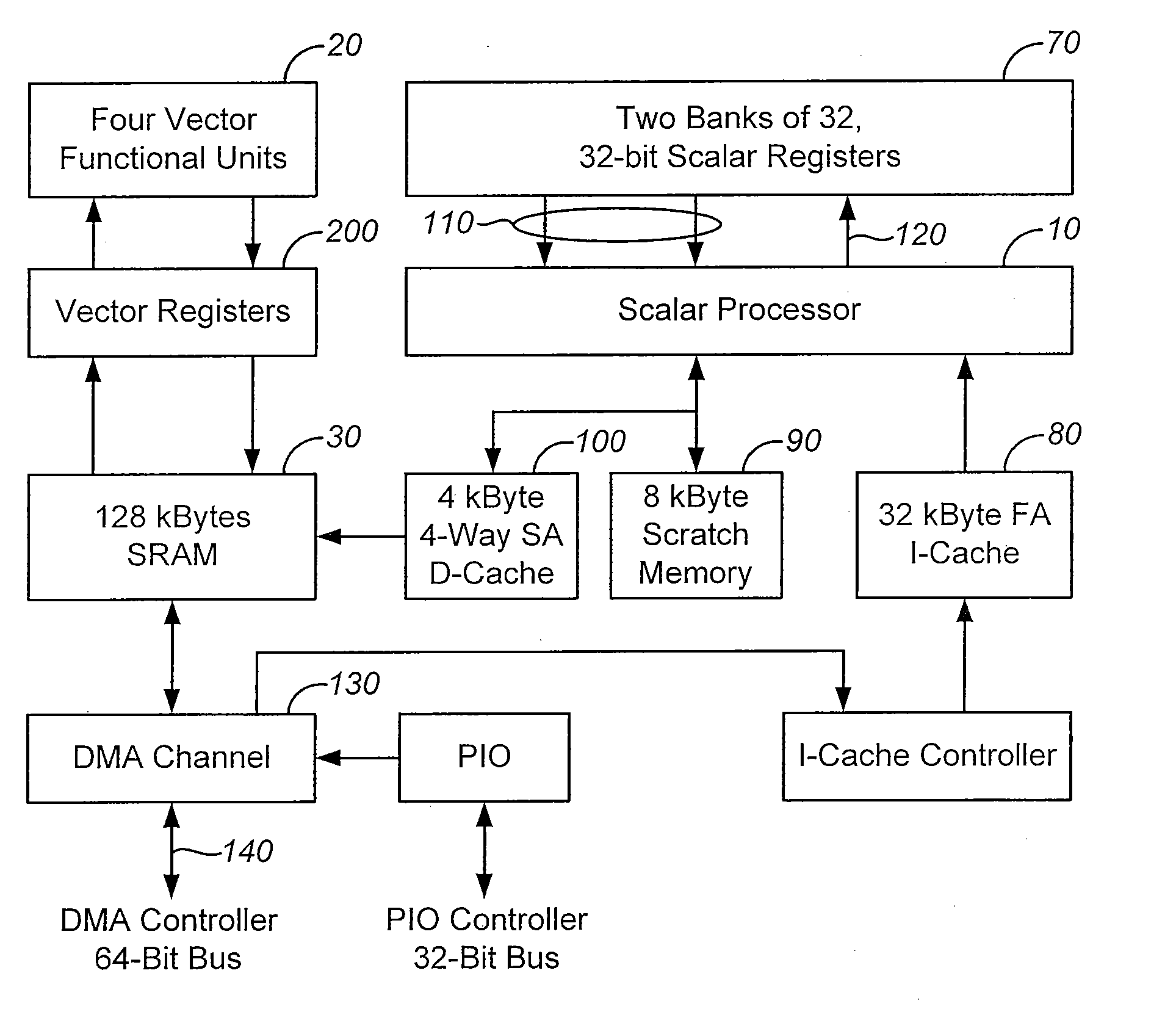

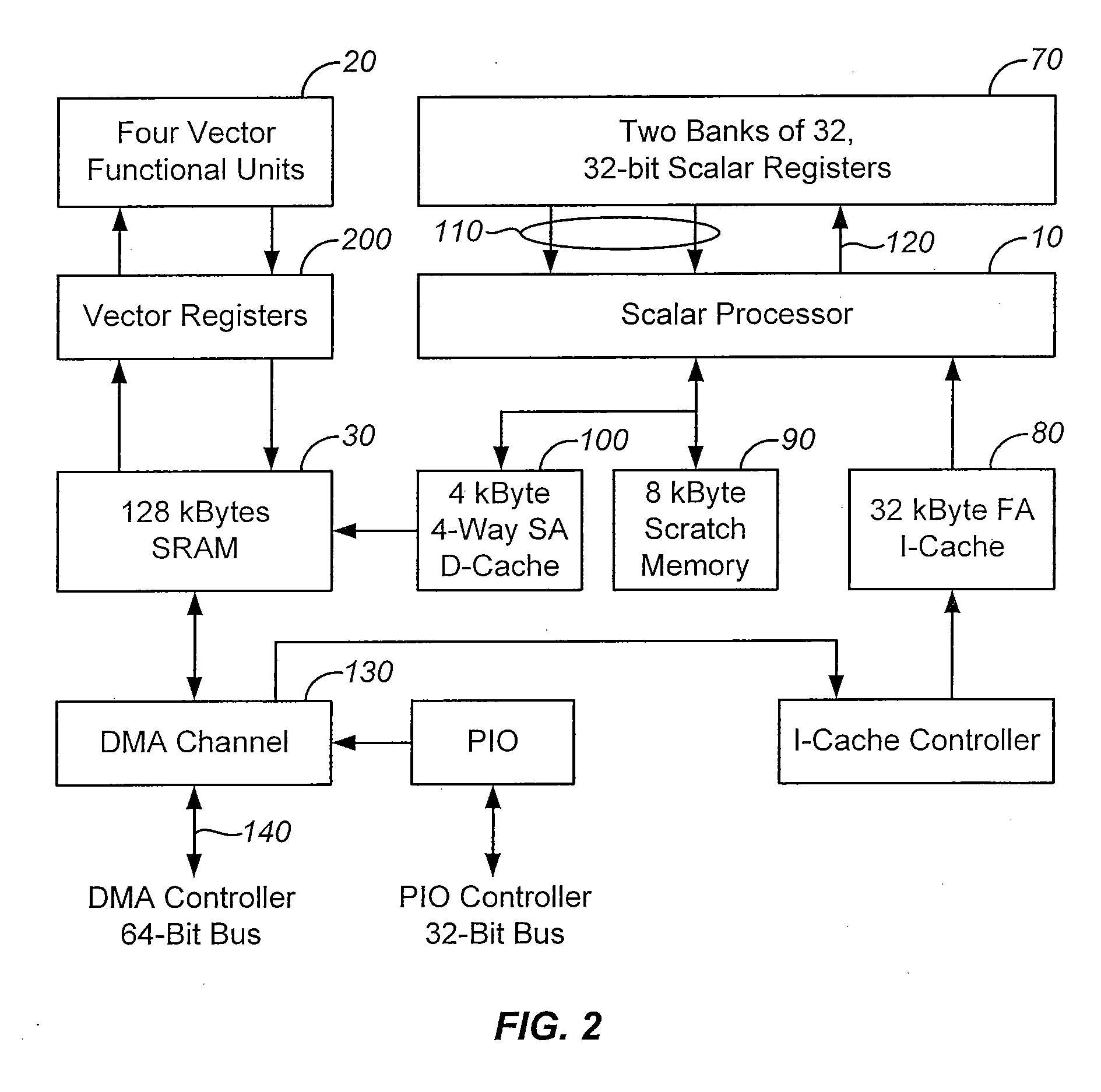

Vector Processor Architecture

InactiveUS20080059759A1Limited instruction widthGreat instruction widthConditional code generationRegister arrangementsRapid processingInformation provision

A vector processor includes a set of vector registers for storing data to be used in the execution of instructions and a vector functional unit coupled to the vector registers for executing instructions. The functional unit executes instructions using operation codes provided to it which operation codes include a field referencing a special register. The special register contains information about the length and starting point for each vector instruction. A series of new instructions to enable rapid handling of image pixel data are provided.

Owner:MEADLOCK JAMES W MEAD

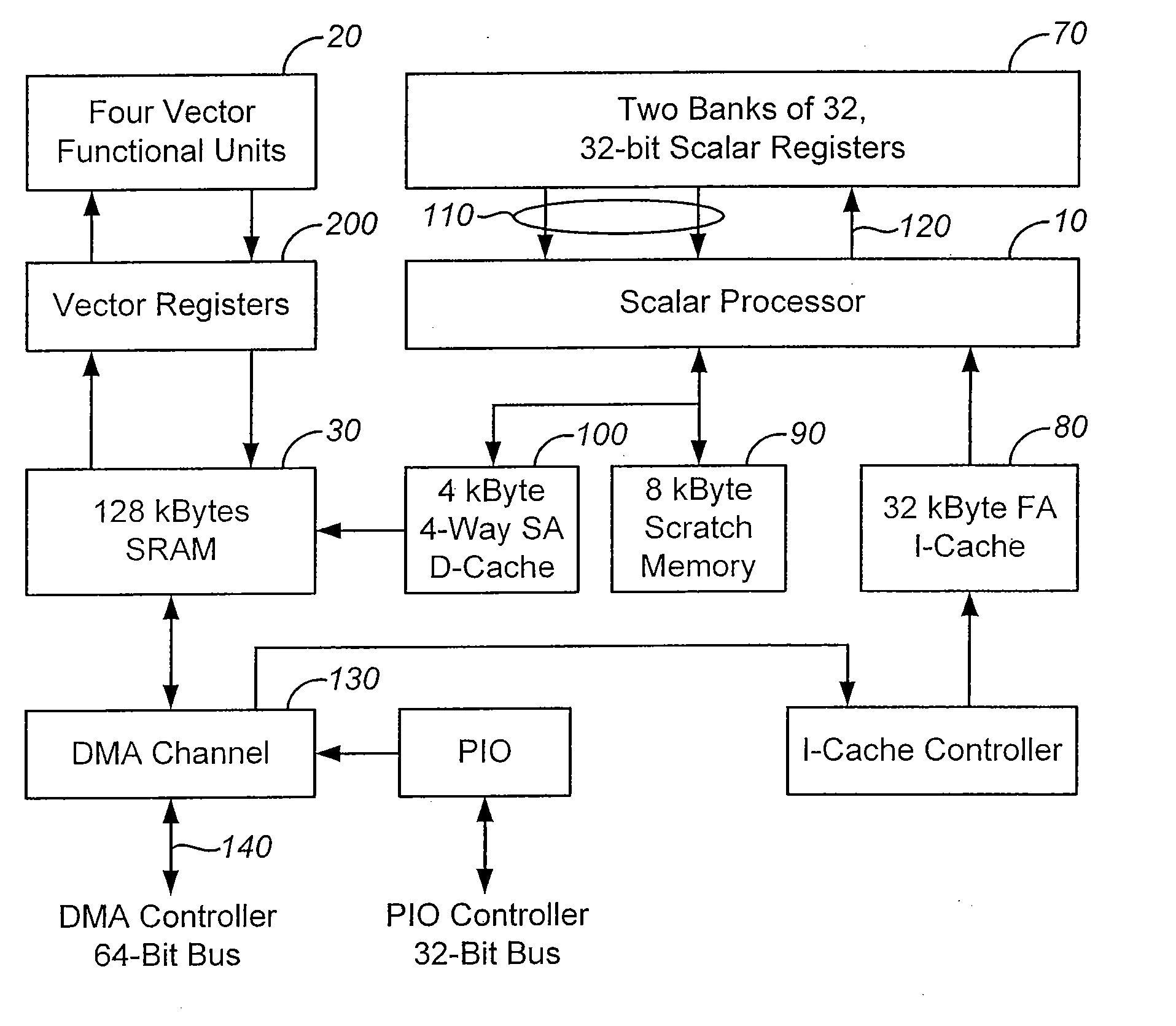

Instructions for Vector Processor

InactiveUS20080059760A1Limited instruction widthGreat instruction widthConditional code generationRegister arrangementsRapid processingInformation provision

A vector processor includes a set of vector registers for storing data to be used in the execution of instructions and a vector functional unit coupled to the vector registers for executing instructions. The functional unit executes instructions using operation codes provided to it which operation codes include a field referencing a special register. The special register contains information about the length and starting point for each vector instruction. A series of new instructions to enable rapid handling of image pixel data are provided.

Owner:MEADLOCK JAMES W MEAD

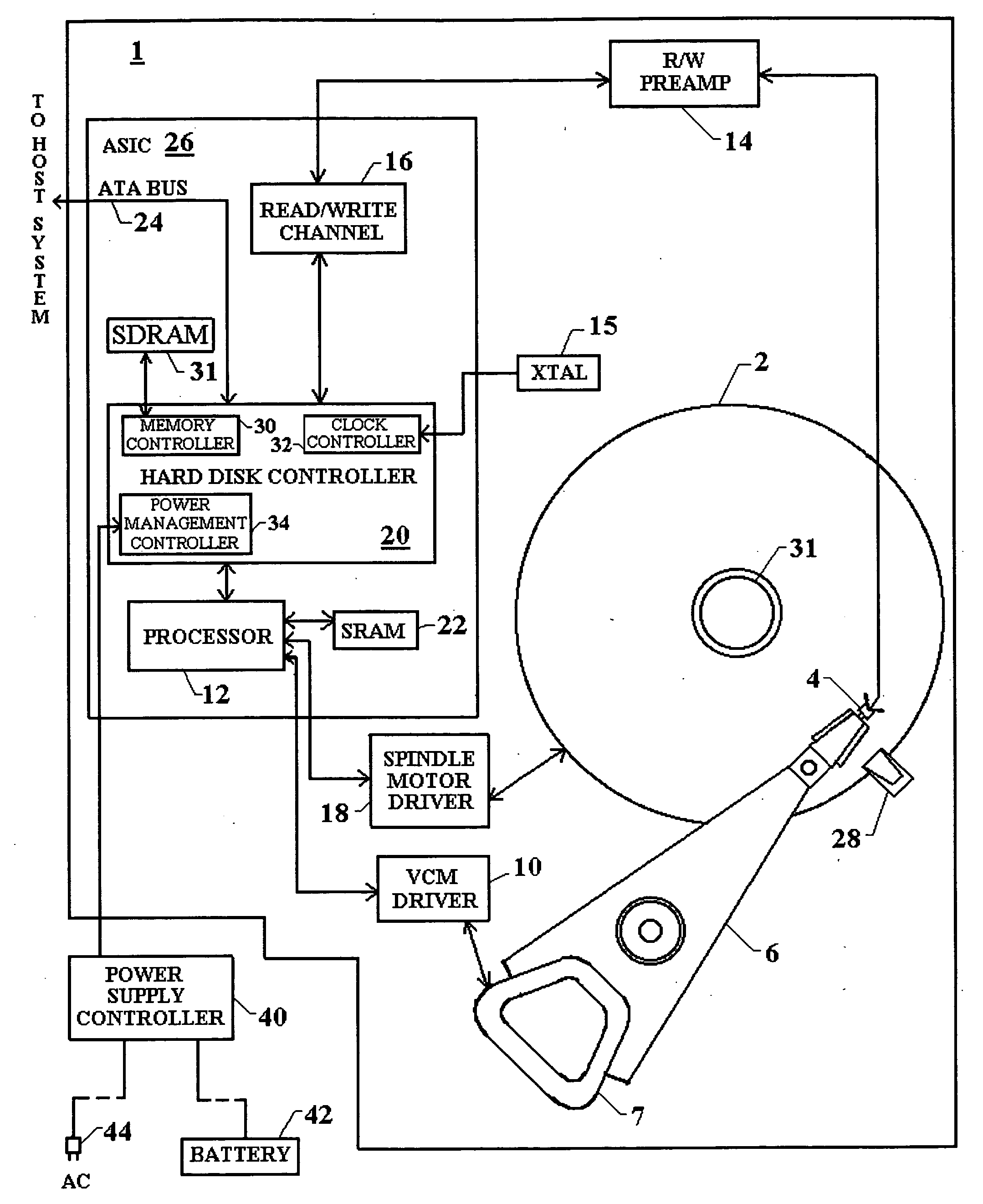

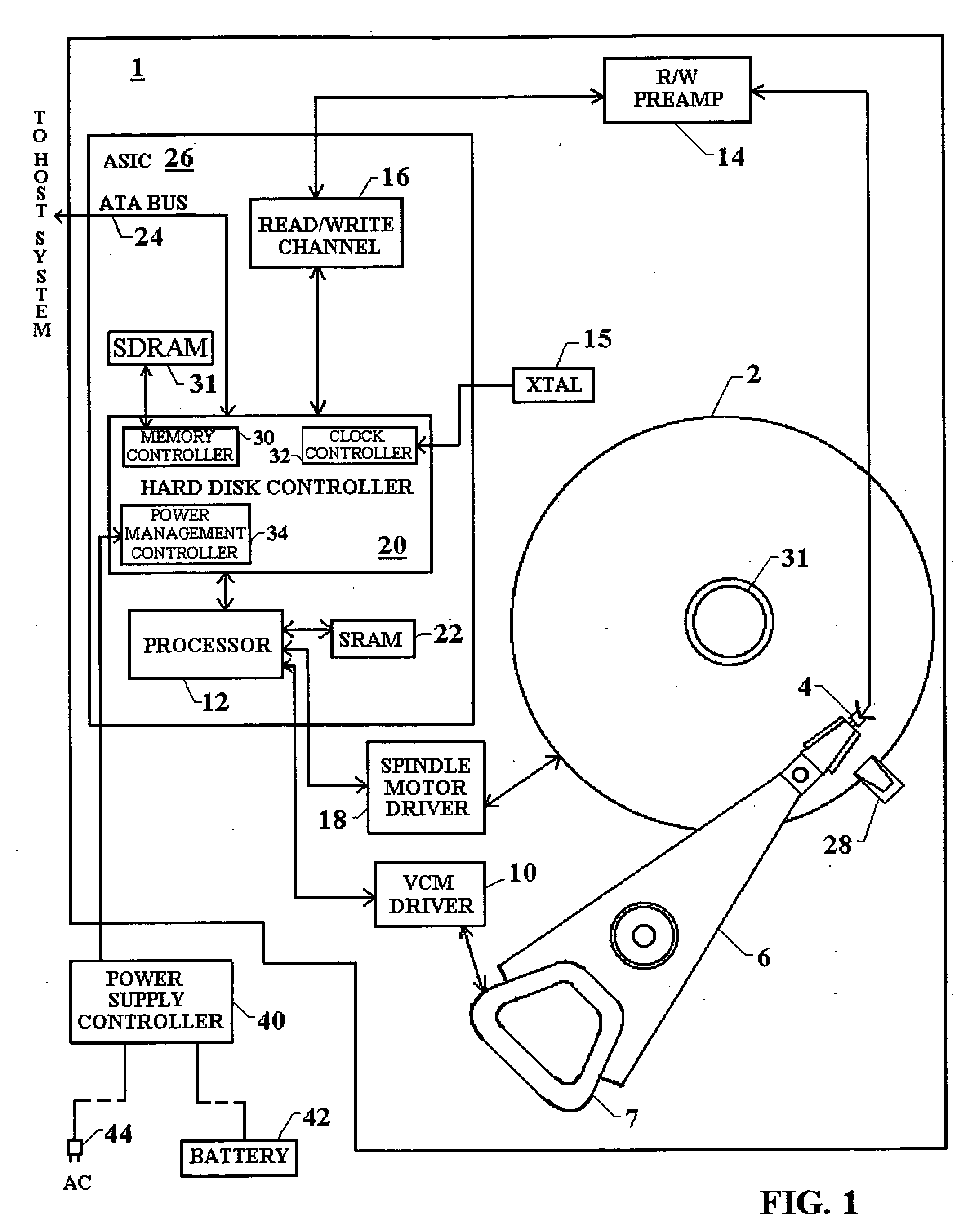

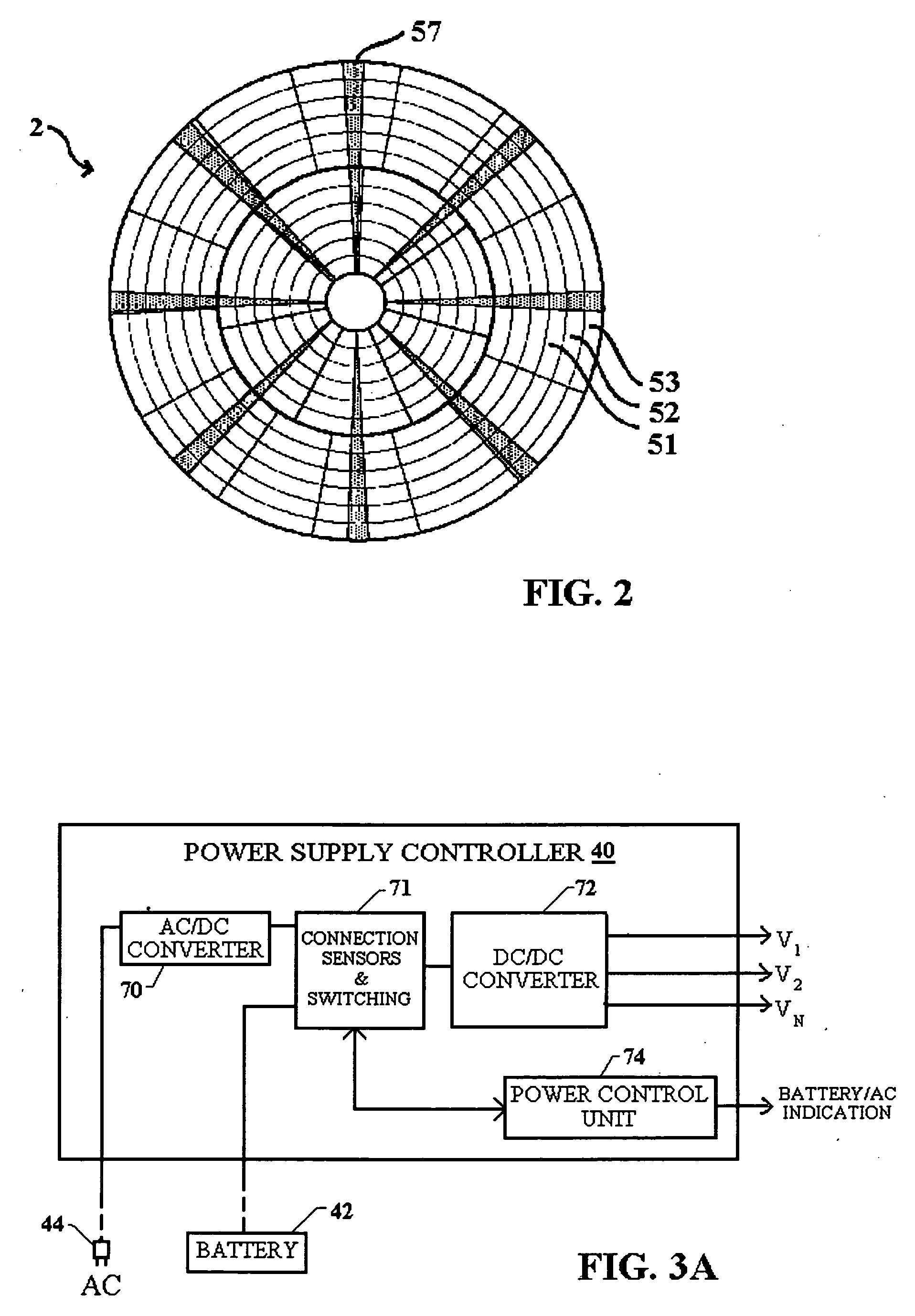

Variable power consumption levels in a hard disk drive

InactiveUS20050144491A1Improve life expectancyReduce switching frequencyEnergy efficient ICTDisposition/mounting of recording headsHard disc driveMemory interface

Attributes of a hard disk drive are stepped between different power consumption levels to optimize the trade-off between minimizing power consumption and maximizing performance depending on whether AC or battery power is used. One attribute is the clock speed which can be changed for a number of disk drive components including the processor, the external interface bus and the memory interface bus. The system power supply voltage can further be changed in a number of components integrated together on an application specific integrated circuit (ASIC). Further, spindle motor rotation speed can be changed, or the spindle motor spun-down. Further, actuator movement by the VCM can be controlled to provide faster movement during track seek operations when high performance is desired. Additionally, write-back caching parameters are adjusted based on the source of power for the hard drive, be it battery, AC power, or a combination.

Owner:PANASONIC CORP

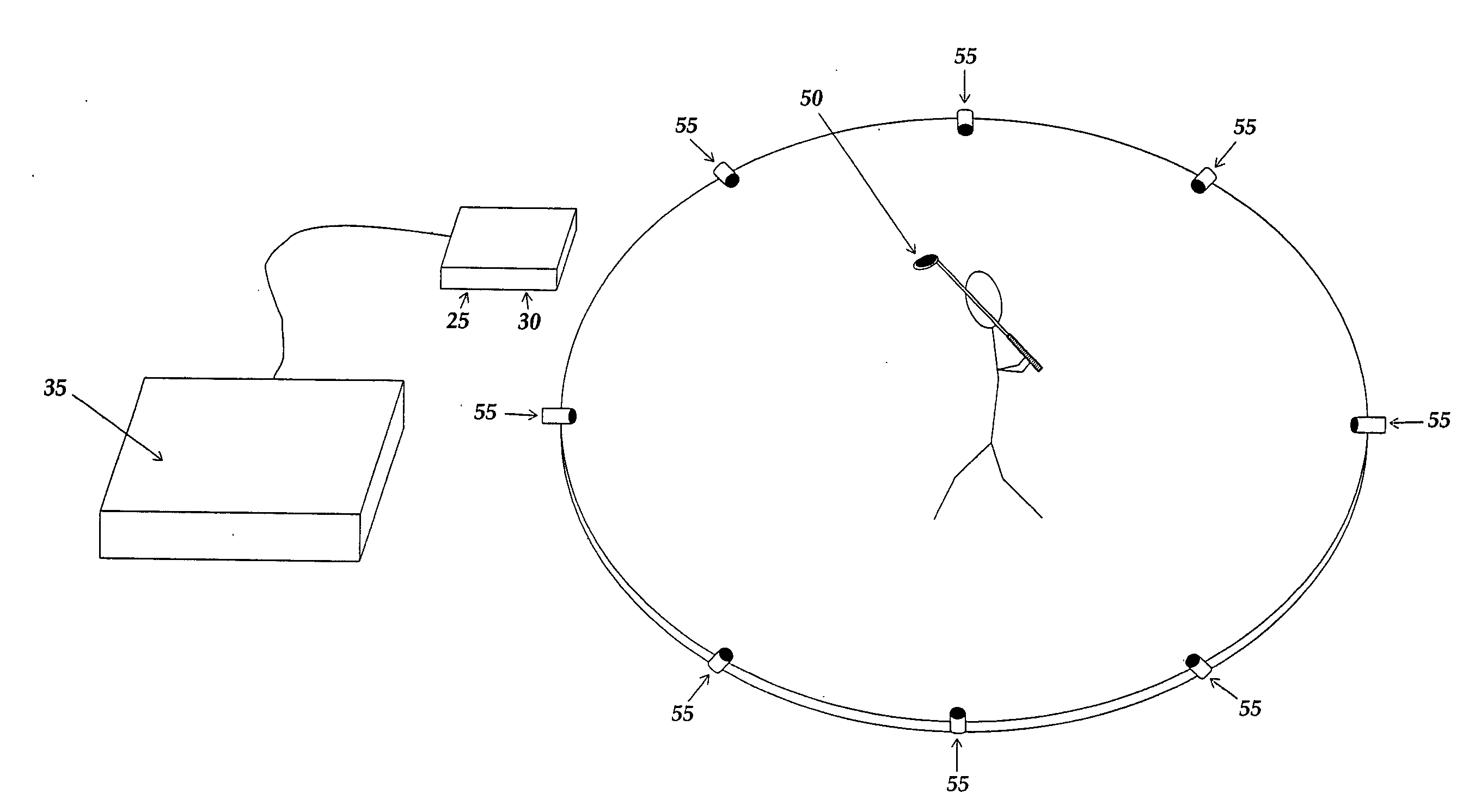

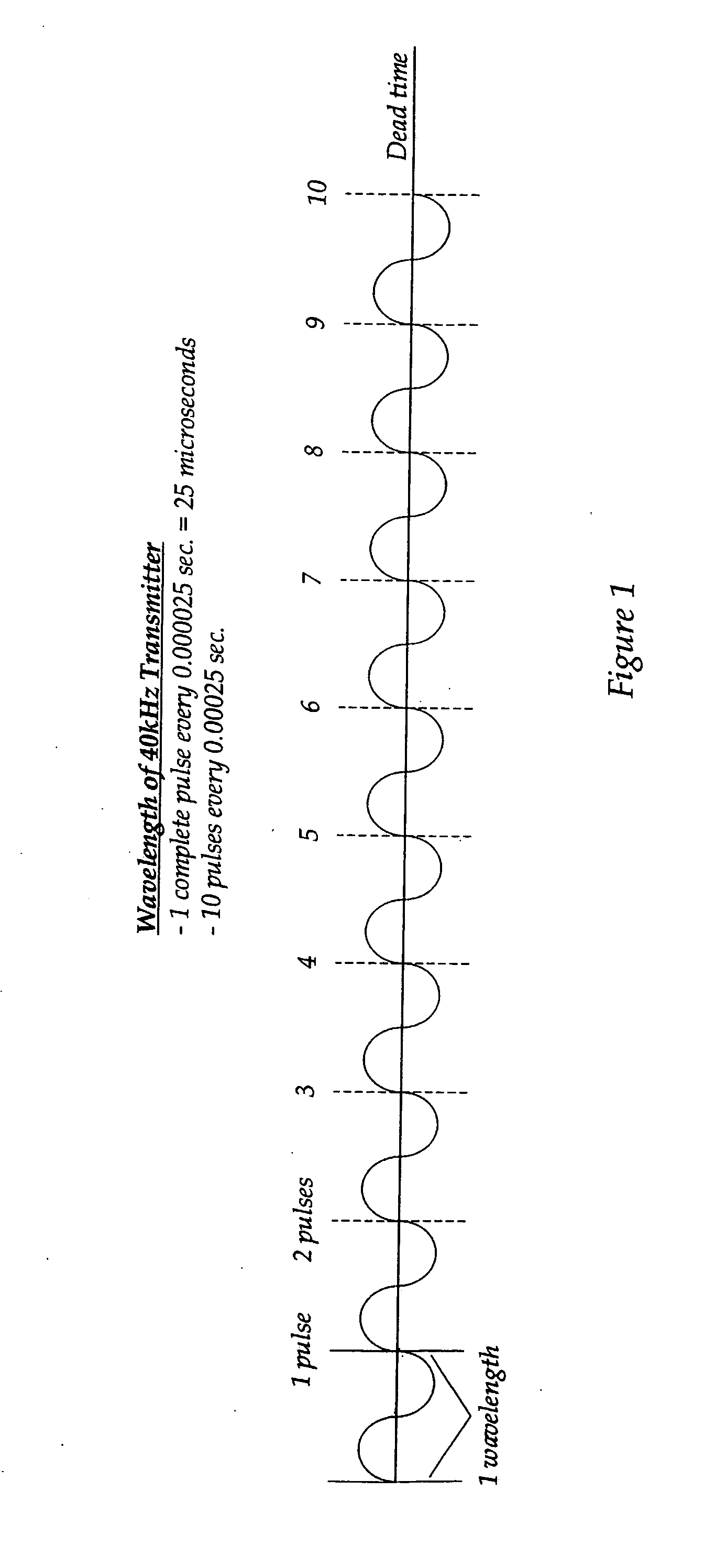

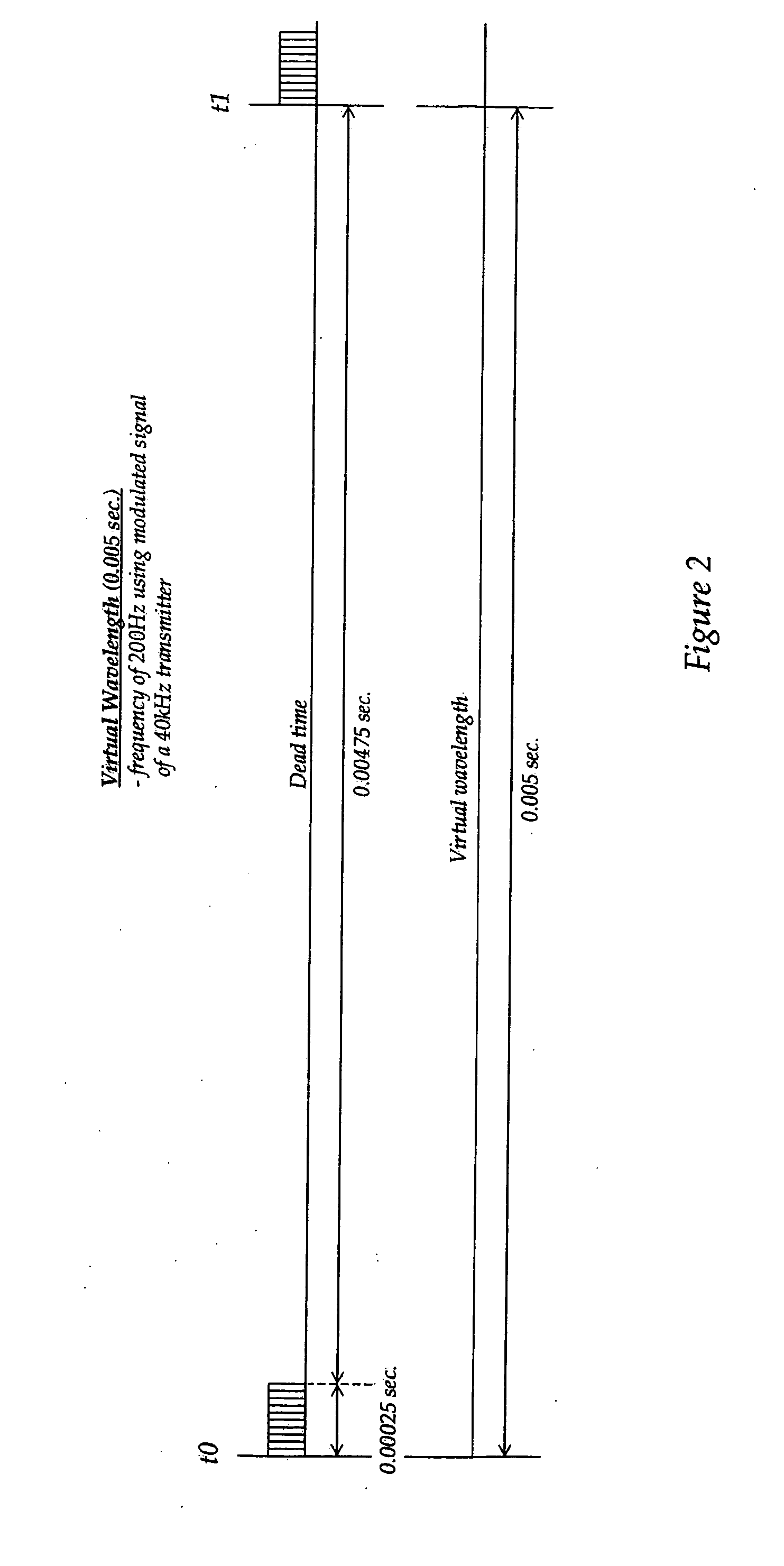

Frequency matched relative position tracking system

InactiveUS20070237029A1Save energyProlong transmitter lifeDirection finders using ultrasonic/sonic/infrasonic wavesPosition fixationTransceiverTriangulation

A method and system for relative positional tracking of a signal source is disclosed that requires no phase synchronization between the tracked source and tracking system. A signal source transmits a repeating signal. The virtual wavelength of the repeating signal establishes zones of coverage. The system's sampling rate (or sync clock) corresponds to the frequency of the repeated signal. One or more ultrasonic transceivers placed within the desired coverage area capture the transmitted signal. Before tracking begins, a coordinate system origin (X=0, Y=0, Z=0) is established so that all tracking calculations are relative to the origin. Relative time-of-flight measurements are made by comparing the received signals against a sync clock. Tracking is accomplished by triangulating distance measurements received from the ultrasonic transceivers.

Owner:HUP

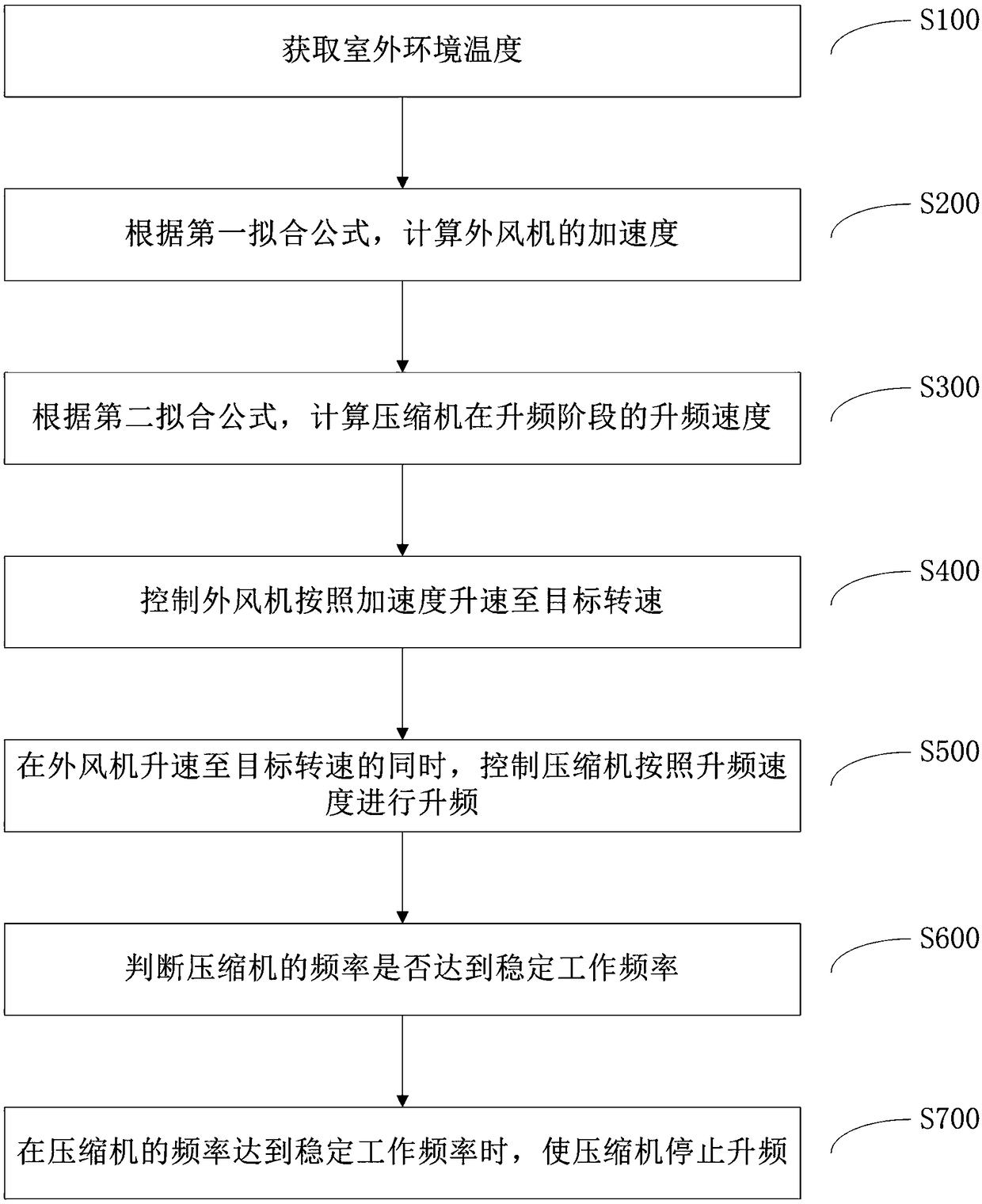

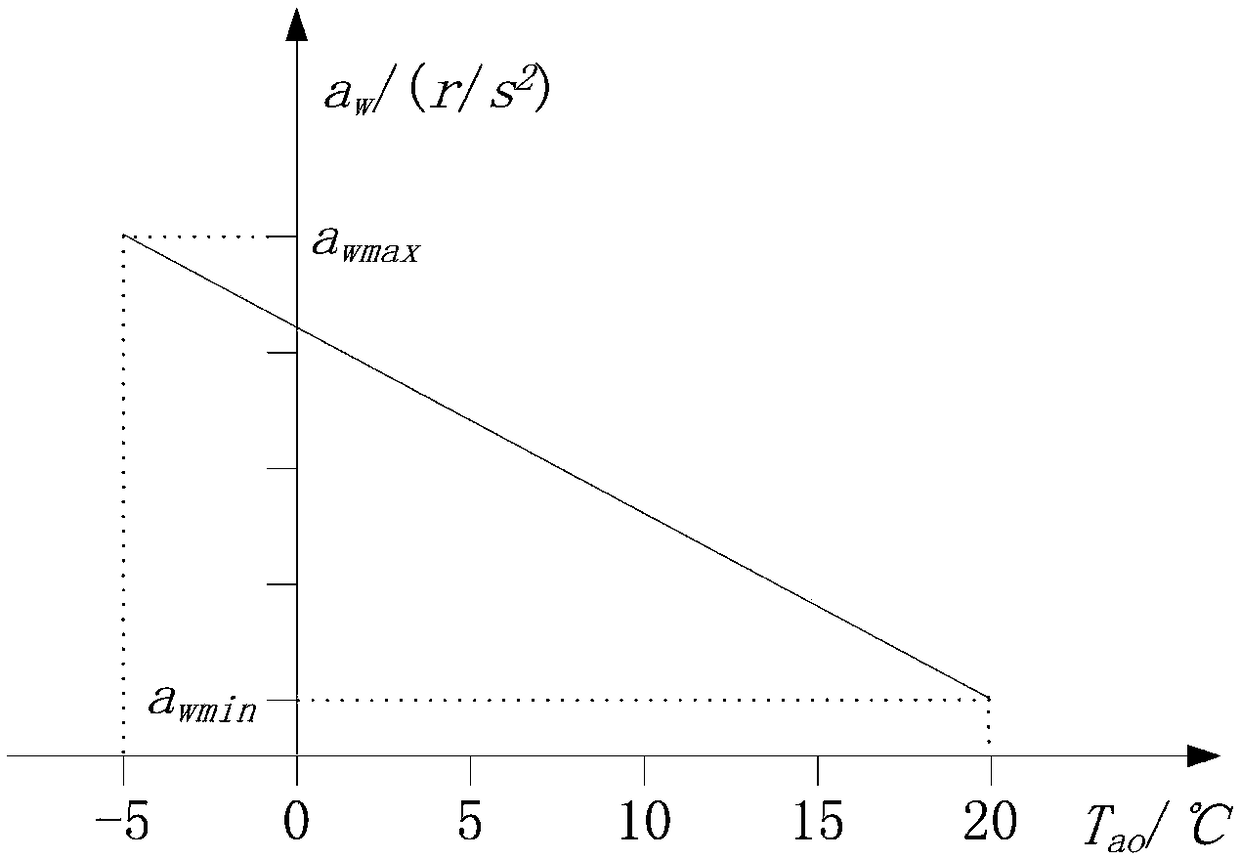

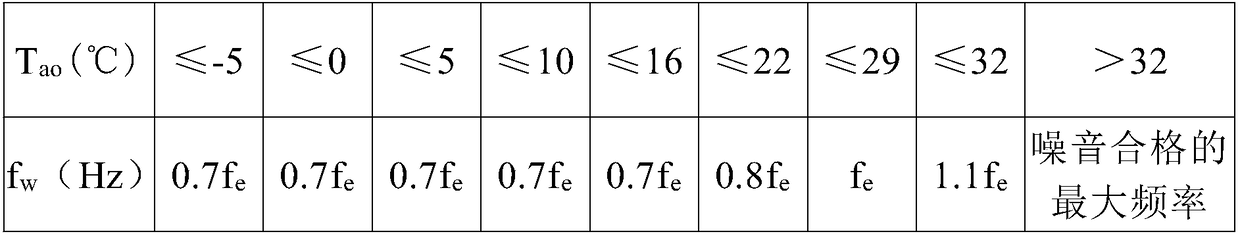

Air conditioner control method in heating mode

InactiveCN108759022AGuaranteed heating effectIncrease clock speedMechanical apparatusSpace heating and ventilation safety systemsControl mannerControl mode

The invention relates to the technical field of air conditioners, in particular to an air conditioner control method in a heating mode. The air conditioner control method in the heating mode aims to solve the problems of poor universality and poor user experience of an existing air conditioner control method. The control method includes the steps that an outdoor ambient temperature is obtained; anaccelerated speed of an external fan is calculated according to a first fitting formula; a frequency ascending speed of a compressor in a frequency ascending stage is calculated according to a secondfitting formula; the external fan is controlled to accelerate to a target rotational speed according to the accelerated speed; and preferably, the compressor is controlled to perform frequency ascending according to the frequency ascending speed while the external fan accelerates to the target rotational speed according to the accelerated speed. According to the control mode, the air conditionercontrol method in the heating mode can improve the universality of the air conditioner and improve the use experience of a user.

Owner:QINGDAO HAIER AIR CONDITIONER GENERAL CORP LTD

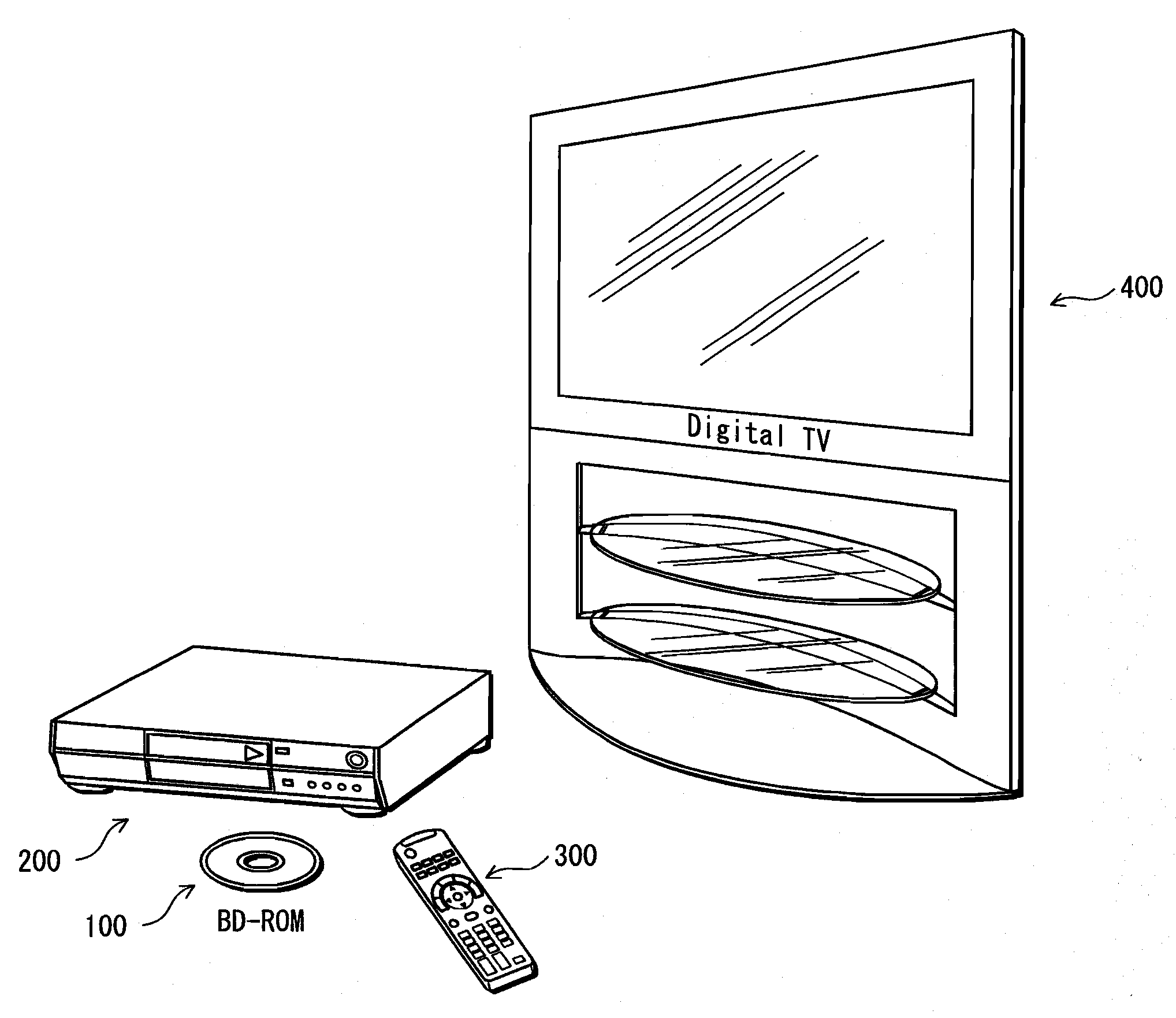

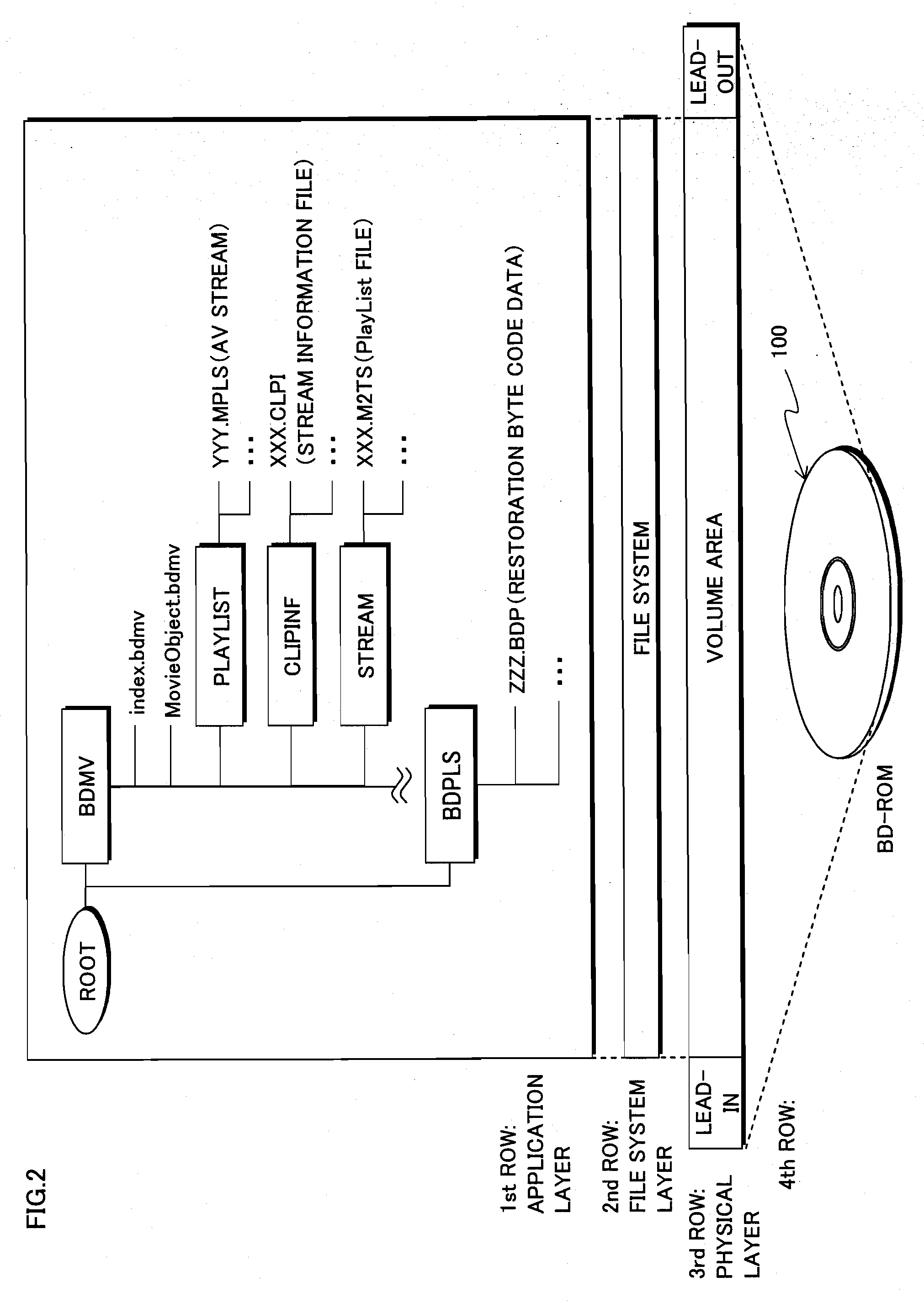

Recording medium, playback apparatus, recording apparatus, playback method, and recording method

ActiveUS20090116818A1Reduce processing loadIncrease loadTelevision system detailsRecording carrier detailsMultiplexingComputer graphics (images)

Provided is a recording medium which enables special playback processing such as fast-forward / rewind although part of the AV stream recorded therein is transformed. An AV stream, a first EP map, and a second EP map are recorded on the recording medium. In the AV stream, part of the multiplexed stream including a first video stream and a second video stream is transformed; the first EP map indicates one or more entry points of the first video stream; and the second EP map indicates one or more entry points of the second video stream. In the AV stream, TS packets constituting I-pictures, of the first video stream, indicated by every 4N-th entry point in the first EP map, and TS packets constituting I-pictures, of the secondary video stream, indicated by the entry points whose presentation time is closest to the presentation time of any one of the every 4N-th entry point in the first EP map.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

POL system architecture with analog bus

ActiveUS7584371B2Increase heightImprove accuracyProgramme controlDc network circuit arrangementsPoint of loadPower control system

A power control system and method including a plurality of point-of-load regulators (POL) providing corresponding regulated output voltages; a manager for communicating control signals and operational parameters with said point-of load regulators; a digital bus to carry control signals therebetween; and an analog bus to carry operational parameters therebetween. Analog sensing circuits and a mutliplexer on the POL communicate operational parameters to and from the manager via the analog bus and are controlled via the digital bus. The operational parameters include output voltage, output current, over voltage, temperature, amplifier or comparator offset, and amplifier gain. The analog sensing circuits are calibrated by trim registers on the POL under digital control by the manager.

Owner:INFINEON TECH AMERICAS CORP

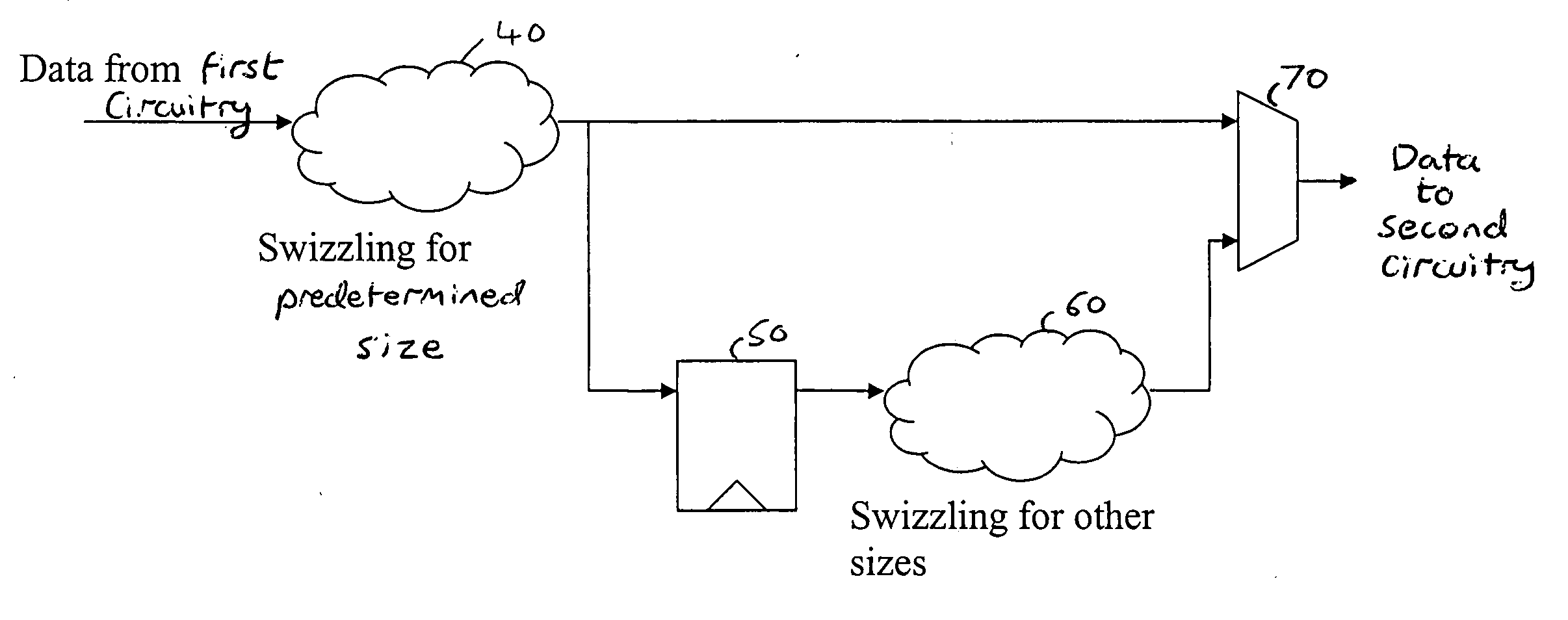

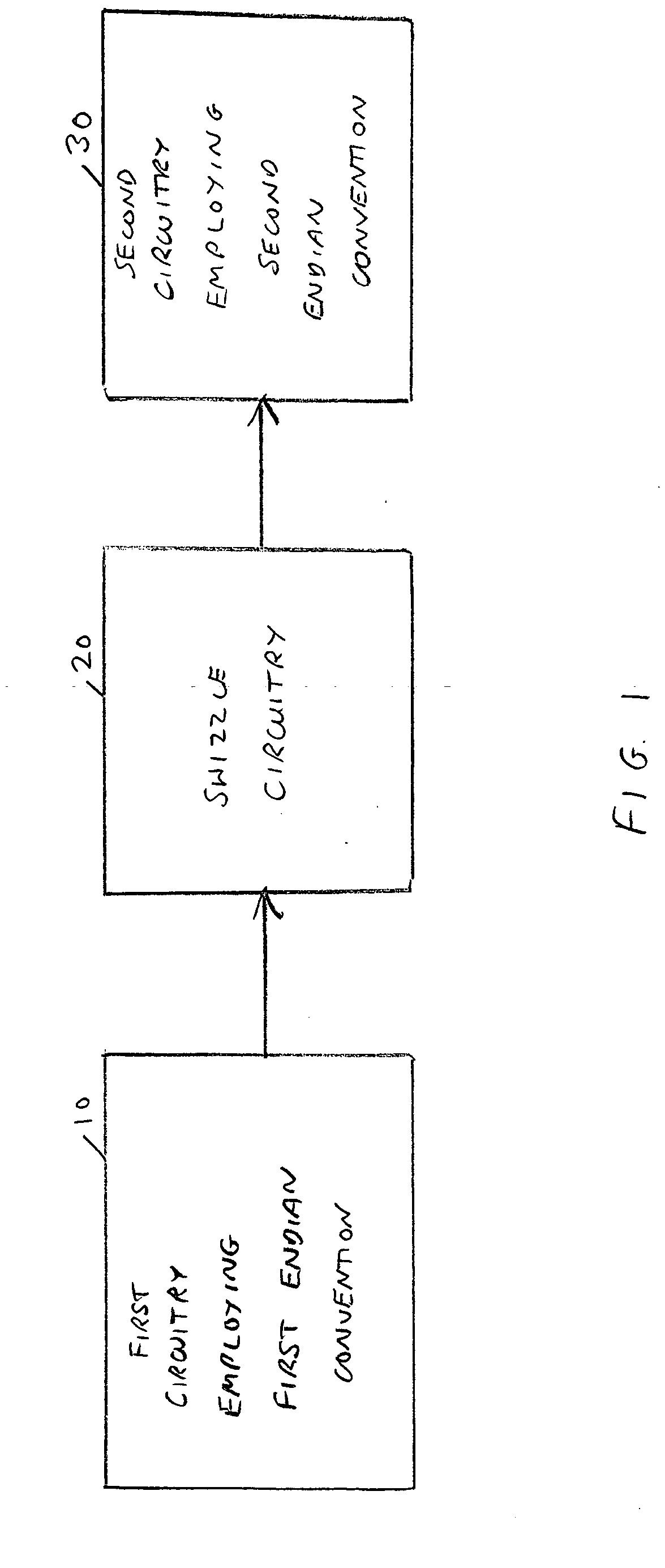

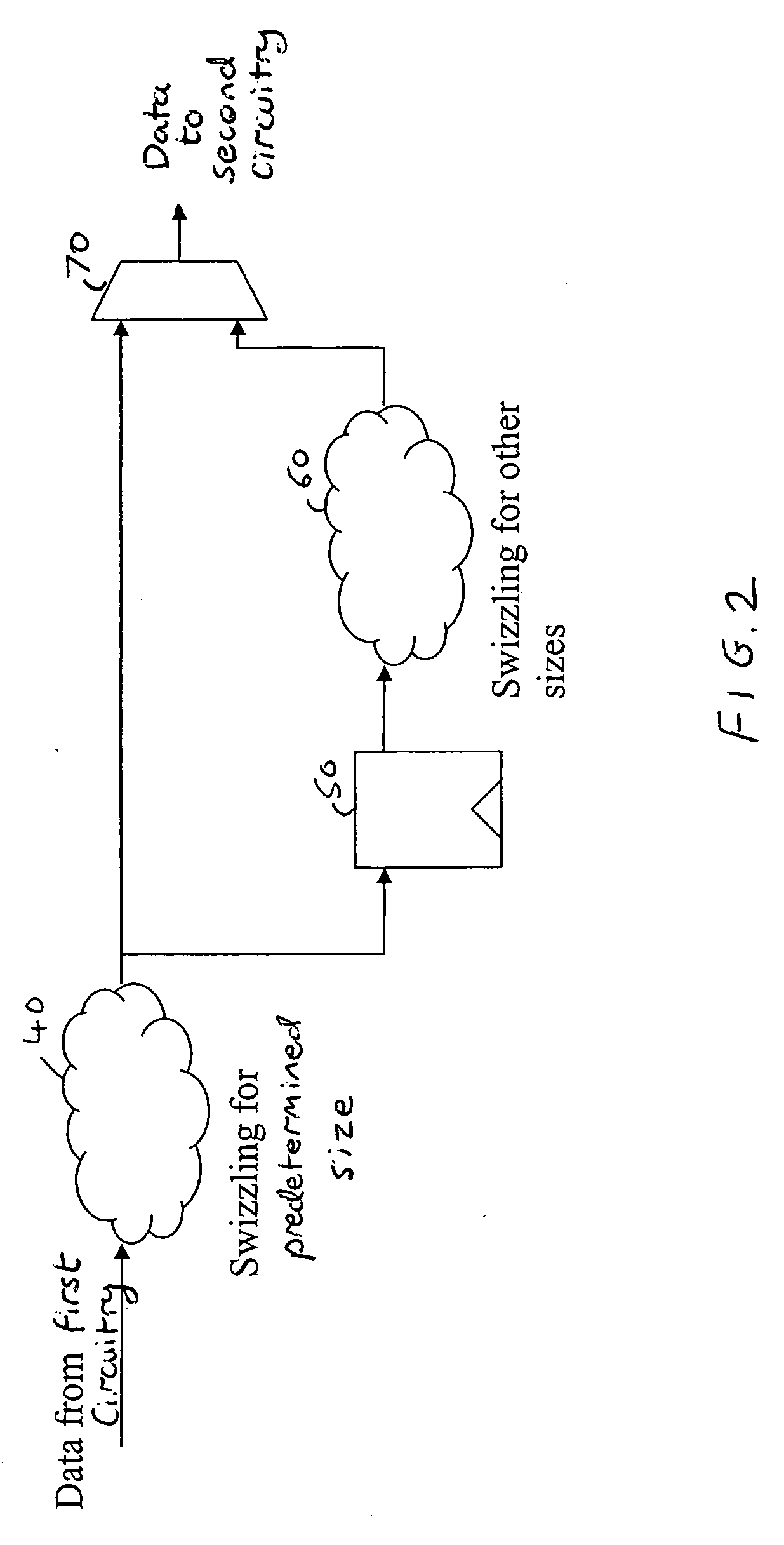

Data processing apparatus and method for converting data values between endian formats

ActiveUS20080148029A1Reduce complexityHigh speedDigital data processing detailsDigital computer detailsCritical path methodData value

A data processing apparatus and method are provided for converting data values from a first endian format to a second endian format. Swizzle circuitry is provided within the data processing apparatus for receiving a block of data containing at least one data value, and for converting each data value in the block from the first endian format to the second endian format. The swizzle circuitry comprises first swizzle circuitry for performing a re-ordering operation on the block of data assuming the at least one data value contained therein is of a first predetermined size, in order to produce re-ordered data. Further, second swizzle circuitry is provided which is responsive to an indication that the at least one data value is of a size different to the first predetermined size to perform an additional re-ordering operation on the re-ordered data having regard to the size of the at least one data value in order to convert each data value to the second endian format. The swizzle circuitry is responsive to an indication that the at least one data value is of the first predetermined size to output the re-ordered data produced by the first swizzle circuitry, whereas otherwise the swizzle circuitry outputs the data produced by the second swizzle circuitry. This can reduce the complexity of swizzle circuitry provided on a critical path, by optimising the swizzle circuitry to handle endian conversion for data values of the first predetermined size, at the expense of data values that are of other sizes requiring more time for the endian conversion operation to be completed.

Owner:ARM LTD

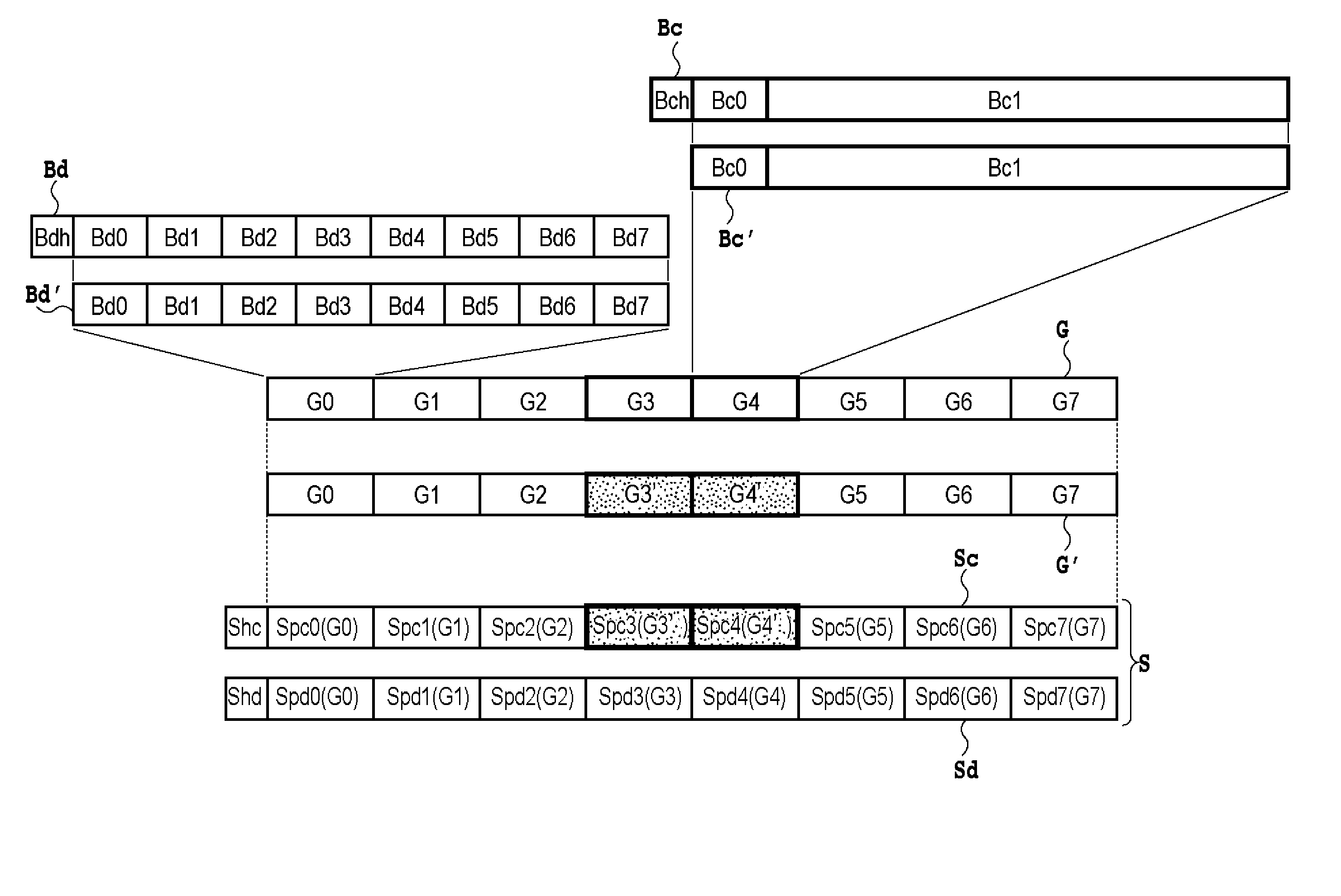

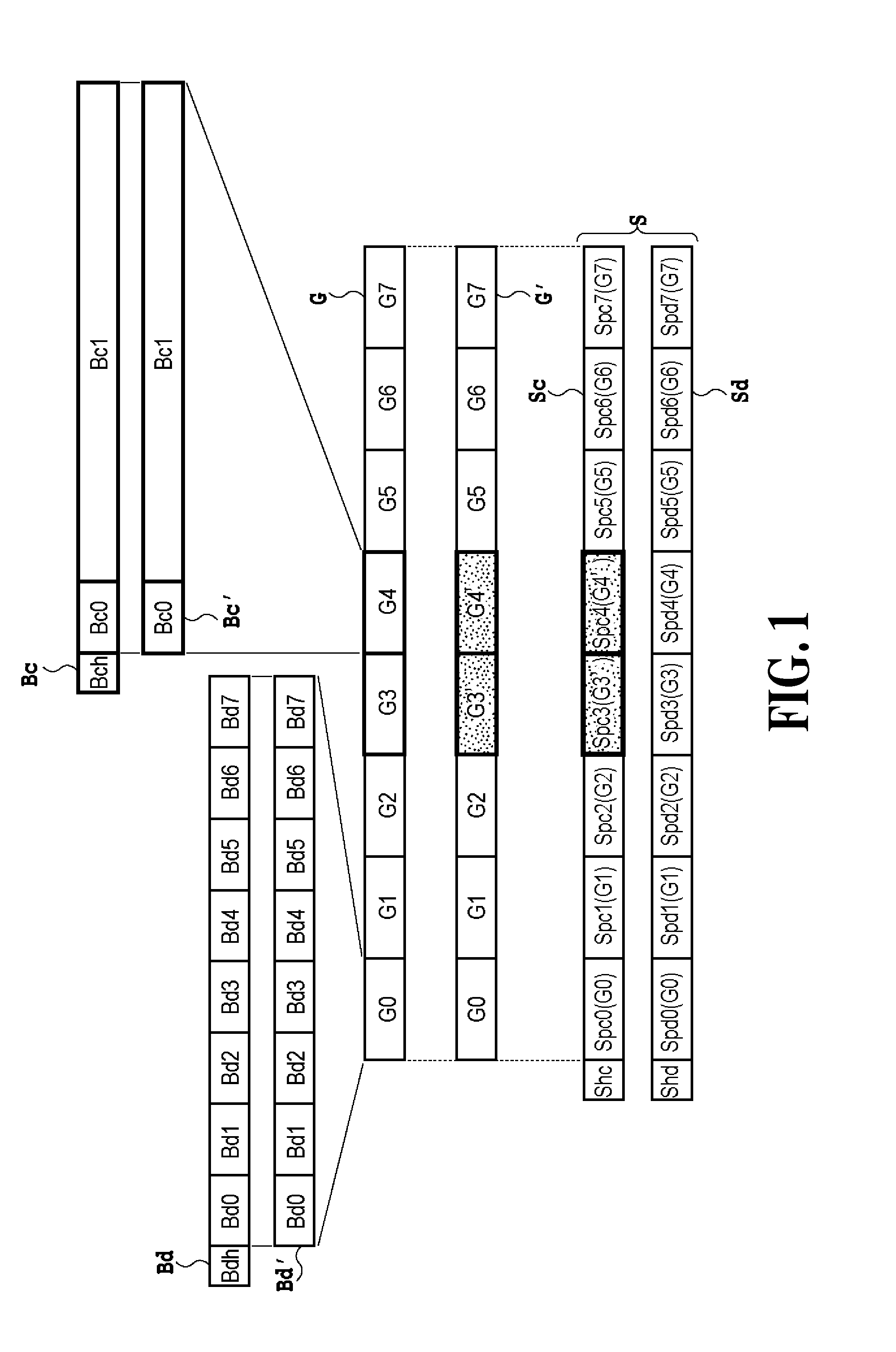

Signal Block Sequence Processing Method And Signal Block Sequence Processing Apparatus

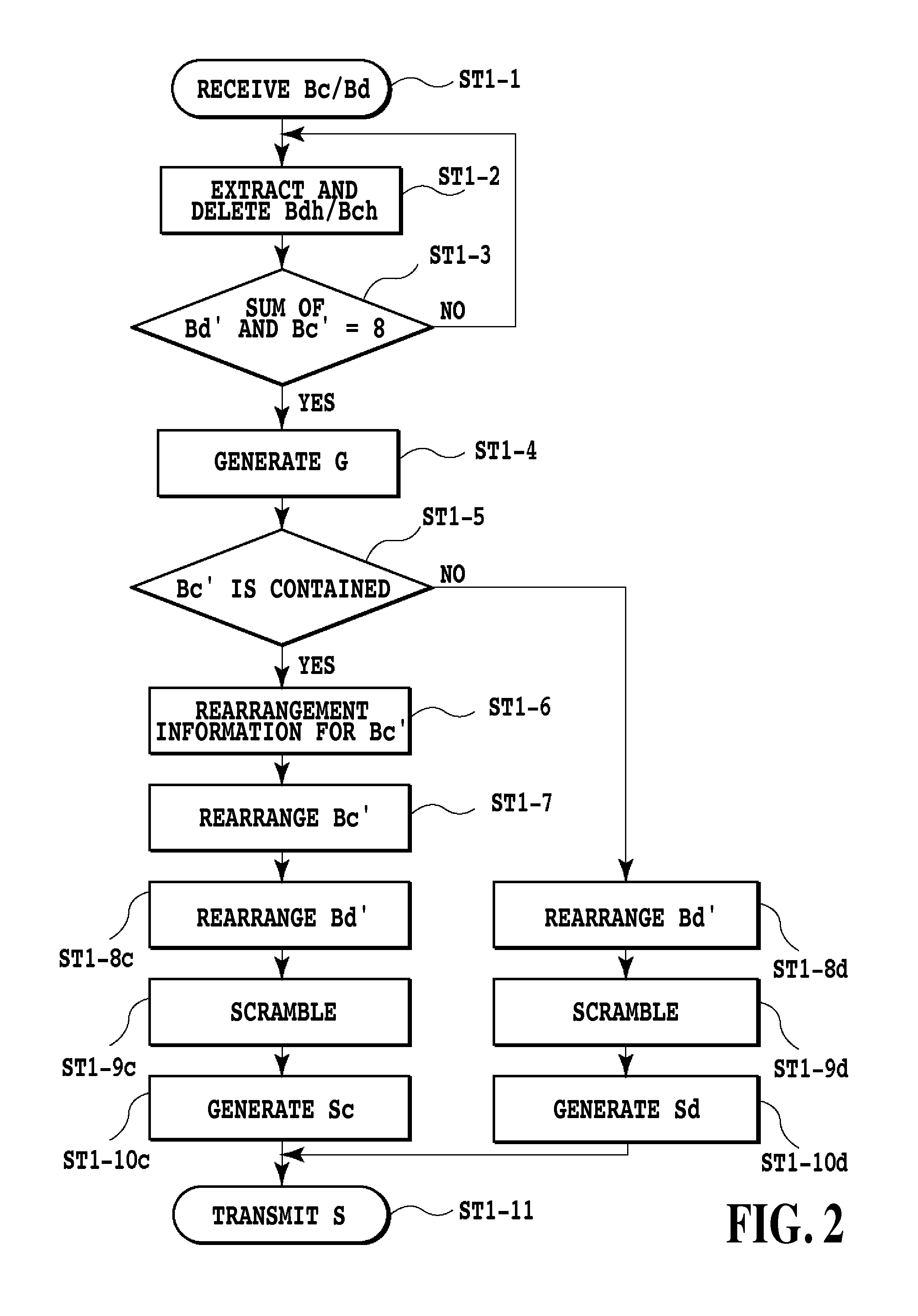

ActiveUS20110013690A1Increase clock speedIncreased error robustnessError preventionTime-division multiplexComputer hardwareSequence processing

The present invention provides a signal block sequence processing method. According to the method, signal block headers (Bch, Bdh) are deleted from each sequence of signal blocks (B) each composed of the signal block header indicating whether a signal block payload is a control block payload (Bc′) containing a control code is contained or a data block payload (Bd′) containing data is contained. The resultant signal blocks are formed into one group (G). Each control block payload in the group is provided with position determination information indicating the position of the control block payload in the group. The signal block payloads are rearranged in accordance with a signal block payload rearrangement rule. The rearranged signal block payloads are contained in a super-block payload (Sc), to which a super-block header (Shc) indicative of containment of control block payloads is added. The resultant super-block (S) is output.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

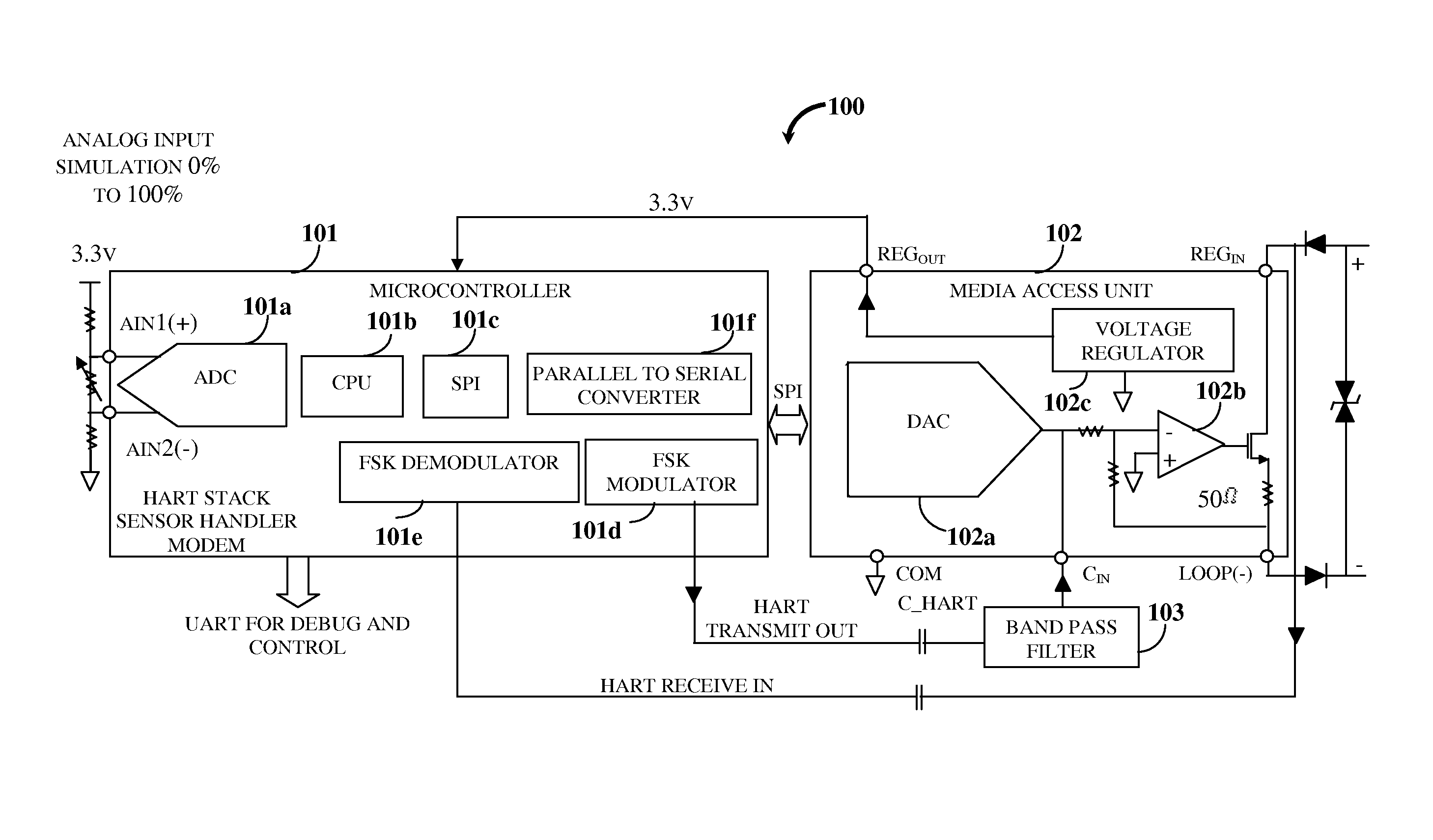

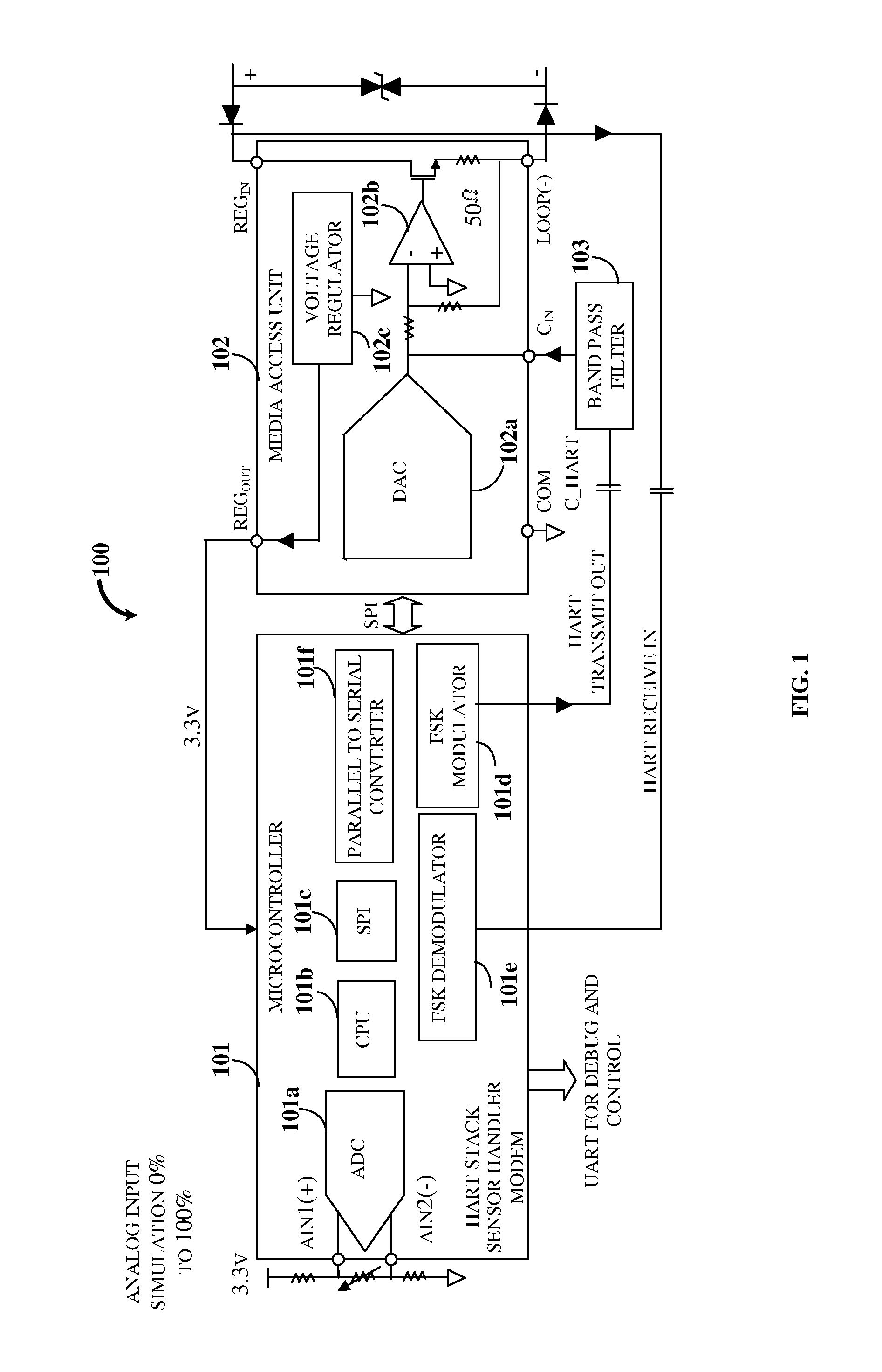

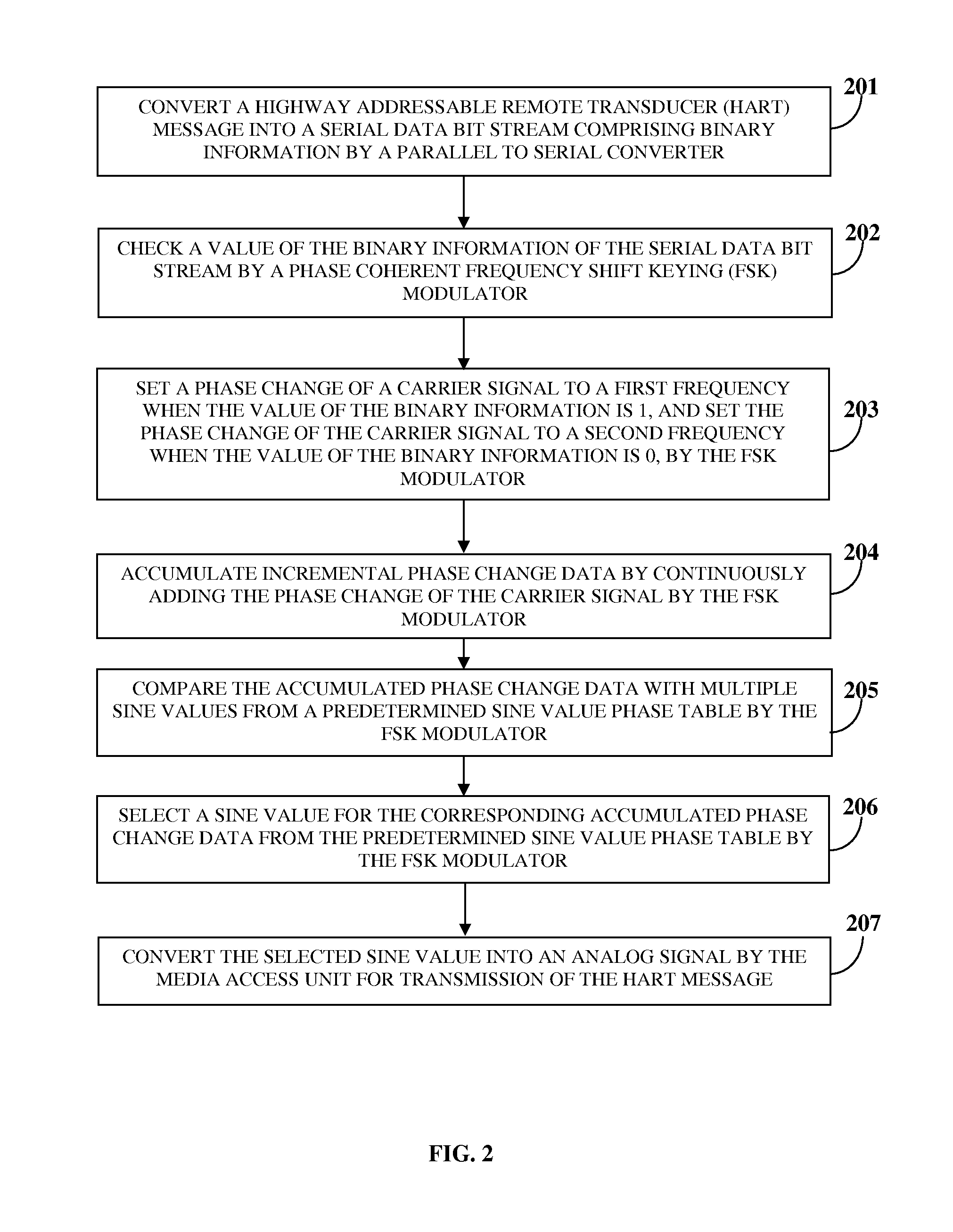

Resource optimization by implementing multiple instances of a soft modem with a single microcontroller

ActiveUS9203665B1Reduce operating powerReduce power consumptionTransmission control/equlisationFrequency-modulated carrier systemsMicrocontrollerModem device

A method and a highway addressable remote transducer (HART) soft modem device for modulating and demodulating one or more analog signals with HART messages are provided. A phase coherent frequency shift keying (FSK) modulator modulates and transmits the analog signals, and a phase coherent FSK demodulator receives and demodulates the analog signals. The FSK modulator outputs 1 or 0 for transmission. With oversampling and low pass filtering, digital modulation performed by the FSK modulator results in low jitter and a good signal to noise ratio. The FSK demodulator applies a fast energy detect algorithm and dynamically reduces or increases a clock speed of a central processing unit (CPU) of the HART soft modem device for reducing power consumption of the CPU. Furthermore, the HART soft modem device uses direct memory access and runs multiple instances of a HART soft modem integrated within a microcontroller to reduce an overall power consumption.

Owner:SMART EMBEDDED SYST

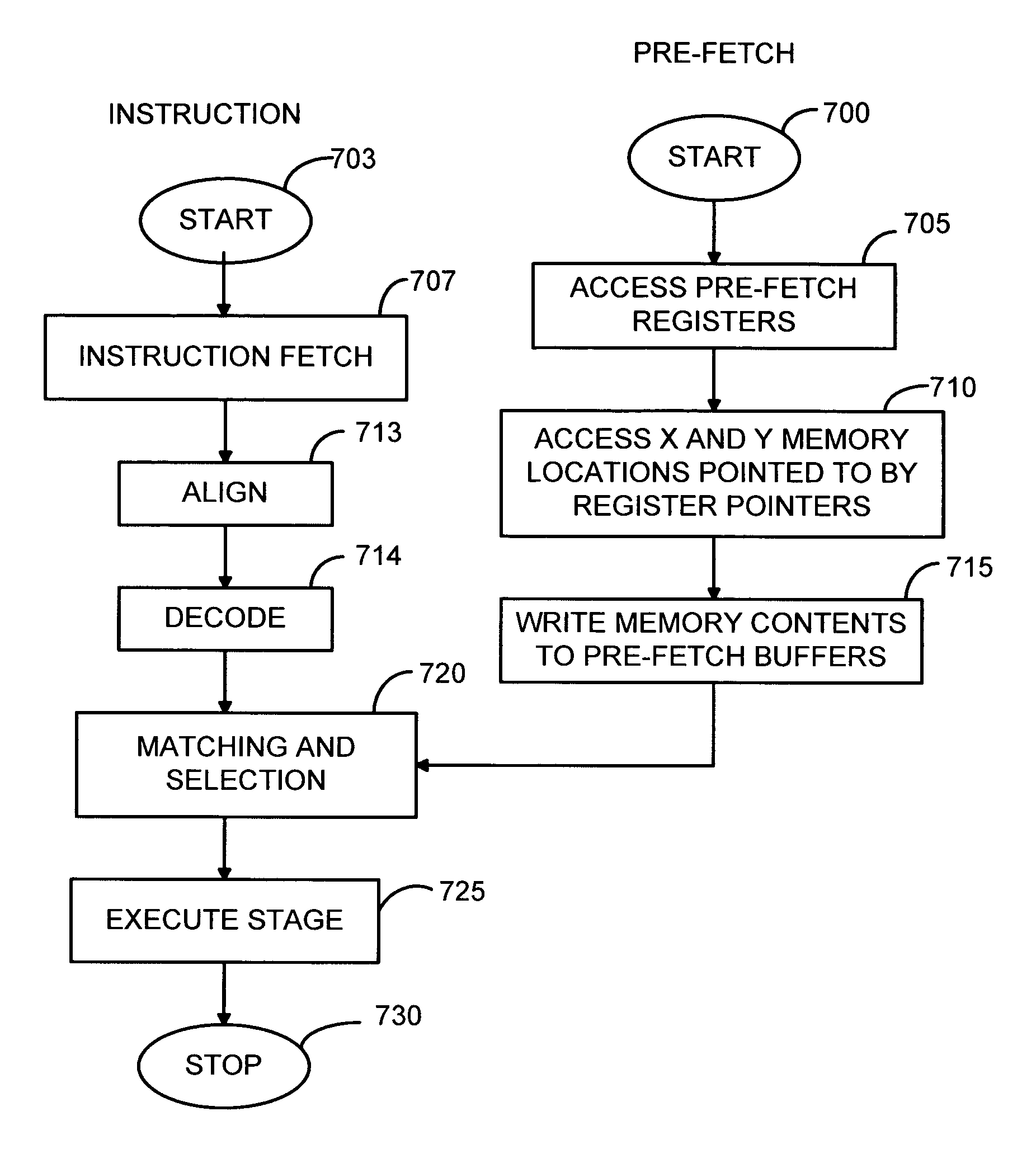

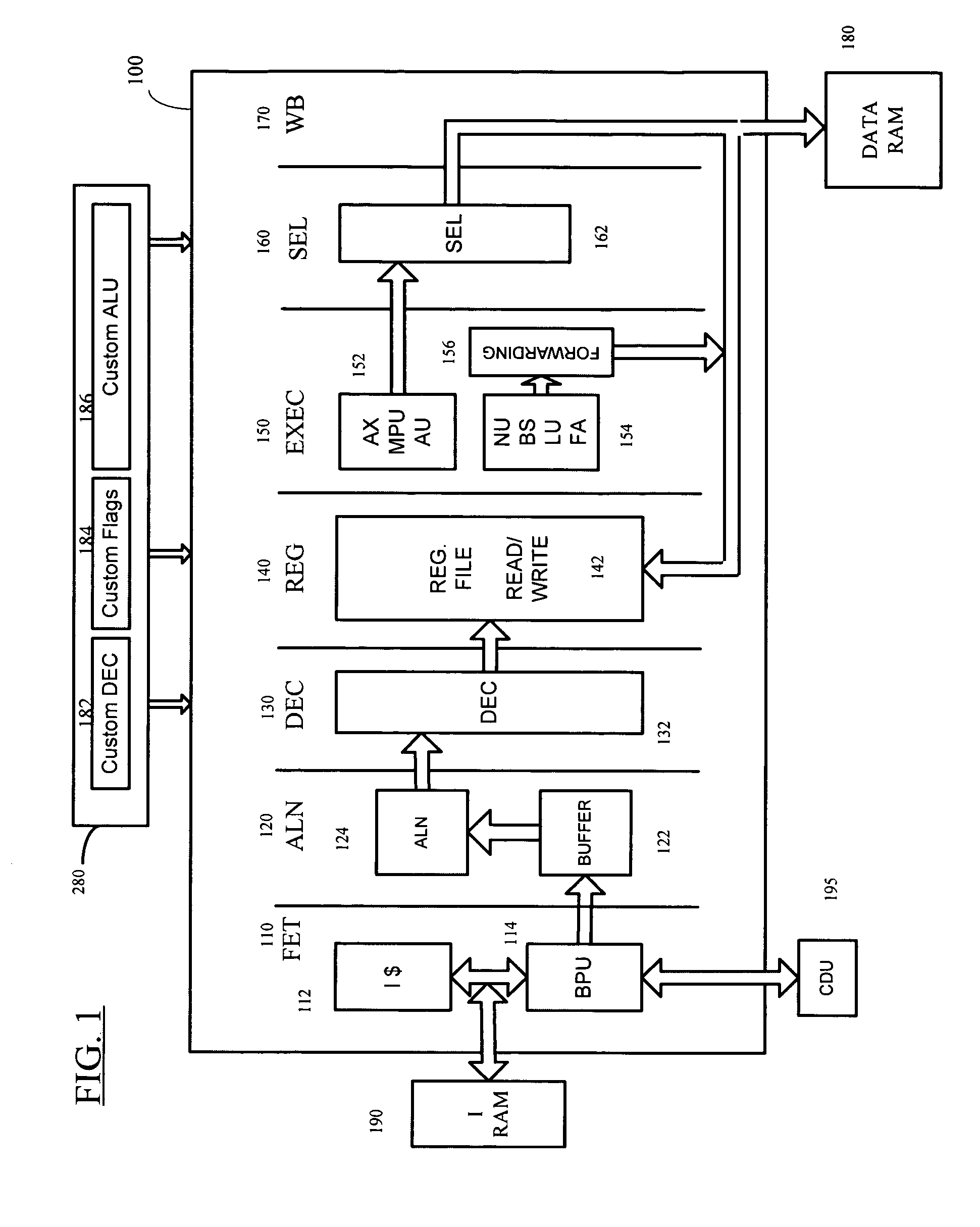

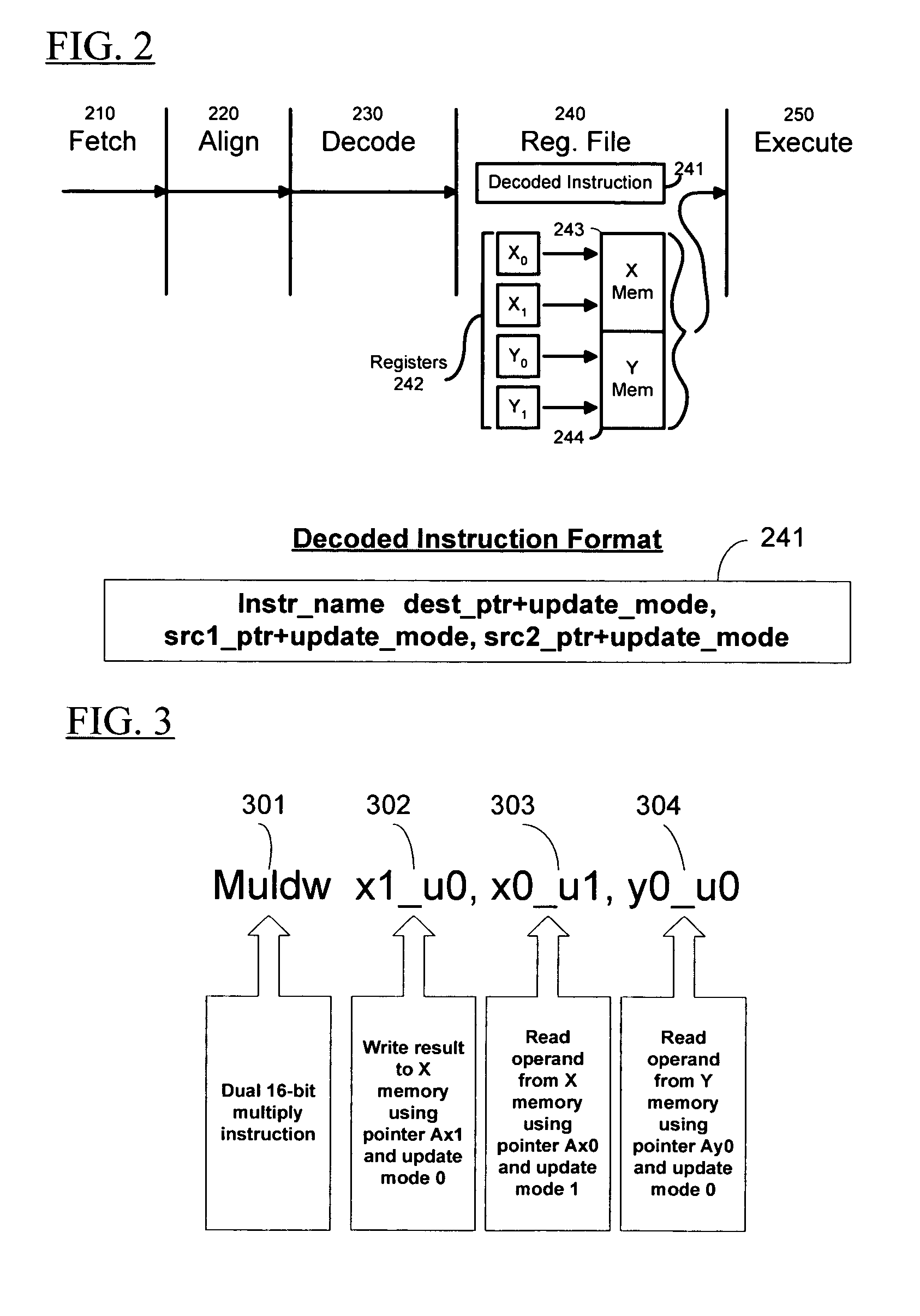

Microprocessor architecture including zero impact predictive data pre-fetch mechanism for pipeline data memory

InactiveUS20050278505A1Impact speedIncrease clock speedEnergy efficient ICTError detection/correctionOperandExecution unit

A microprocessor architecture including a predictive pre-fetch XY memory pipeline in parallel to the processor's pipeline for processing compound instructions with enhanced processor performance through predictive prefetch techniques. Instruction operands are predictively prefetched from X and Y based on the historical use of operands in instructions that target X and Y memory. After the compound instruction is decoded in the pipeline, the pre-fetched operand pointer, address and data is reconciled with the operands contained in the actual instruction. If the actual data has been pre-fetched, it is passed to the appropriate execute unit in the execute stage of the processor pipeline. As a result, if the prediction is correct, the data to use for access can be selected and the data selected fed to the execution stage without any addition processor overhead. This pre-fetch mechanism avoids the need to slow down the clock speed of the processor or insert stalls for each compound instruction when using XY memory.

Owner:ARC INT LTD

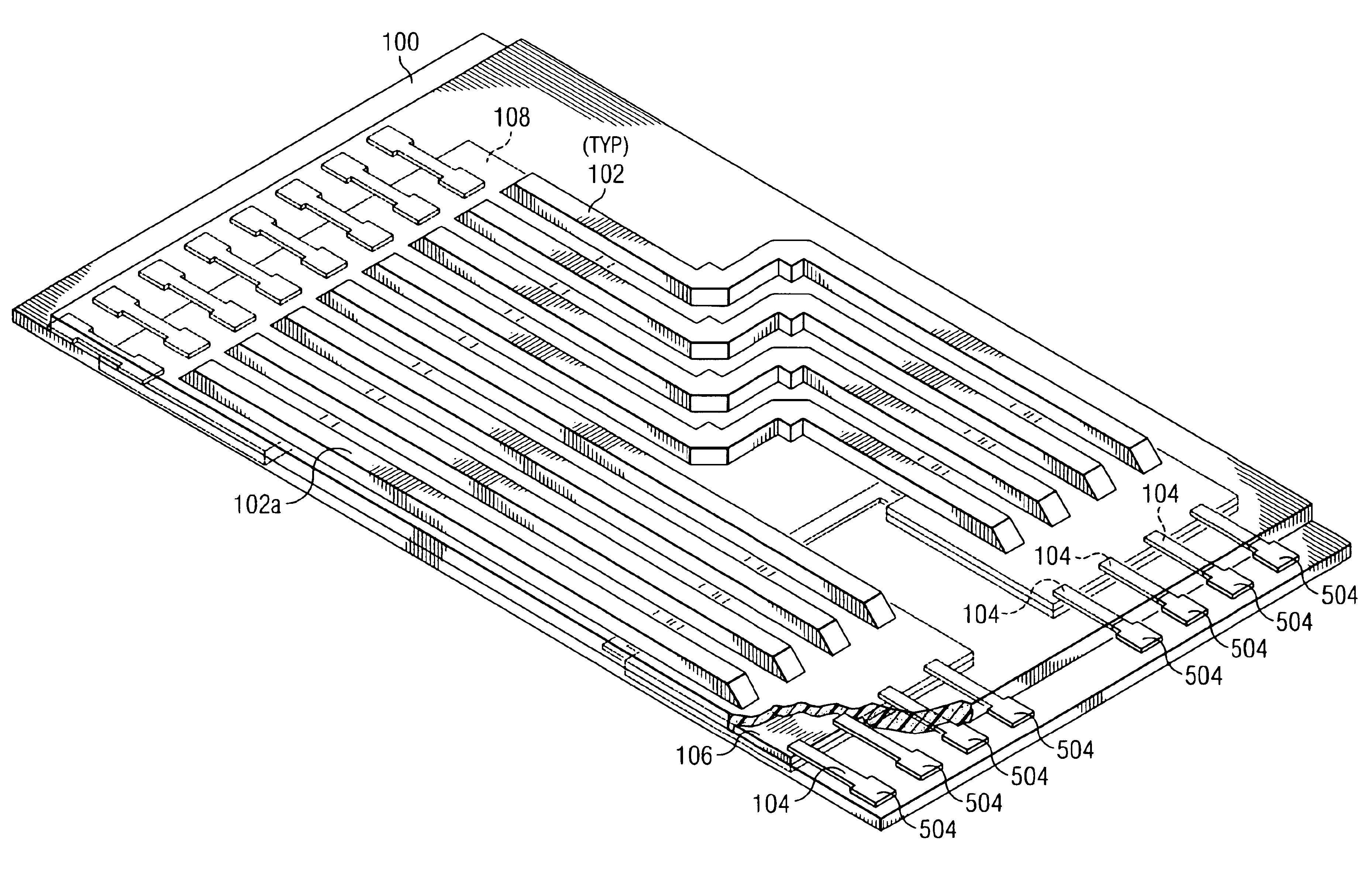

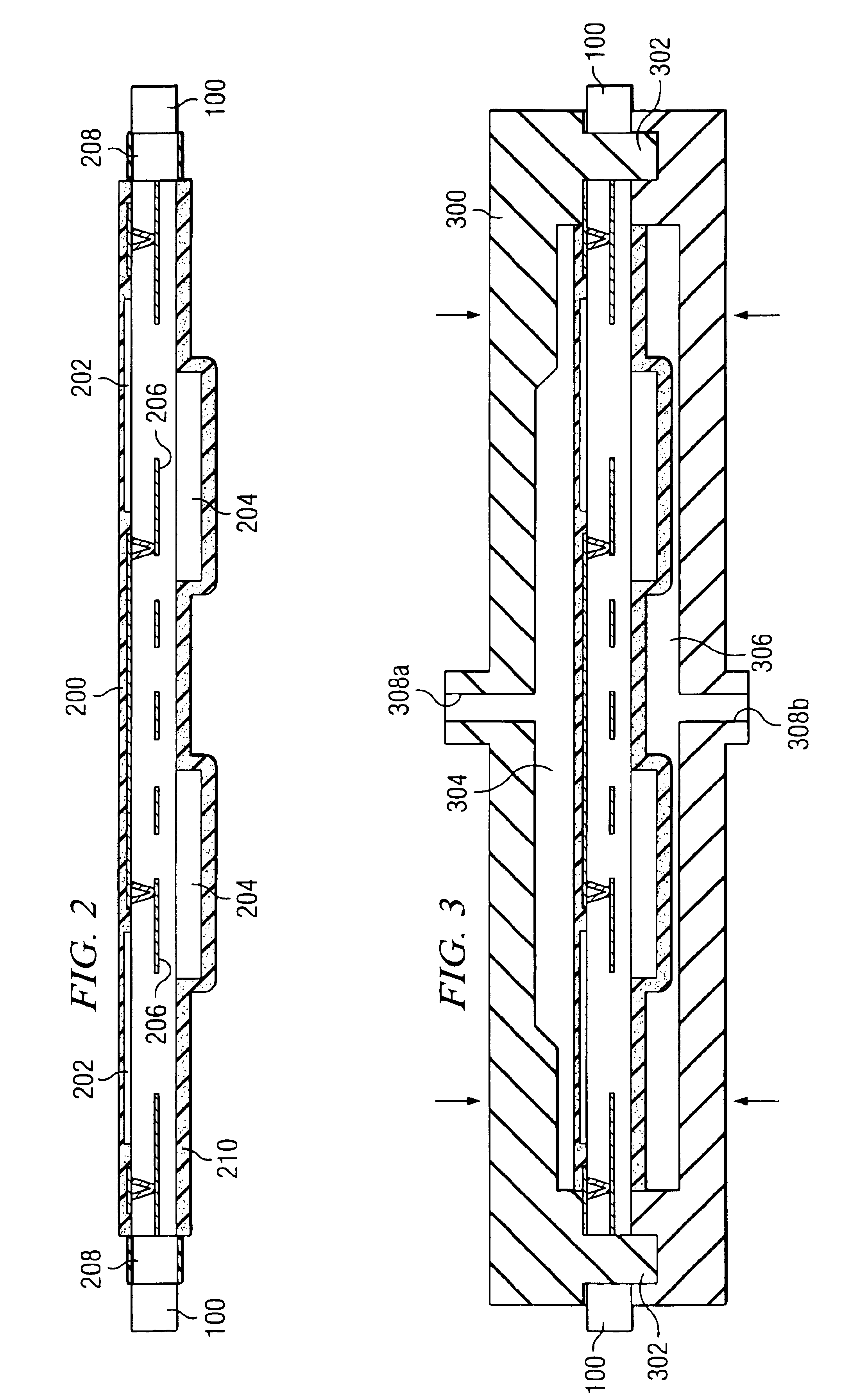

Method for forming an optical printed circuit board

InactiveUS6865307B1High-speed optical communicationEliminate bottlenecksCircuit optical detailsPhotosensitive materialsEngineeringWaveguide

According to one embodiment of the invention, a method includes providing a printed circuit board having a plurality of optoelectronic components coupled to a first side of the printed circuit board, forming a first clad layer outwardly from the first side of the printed circuit board, coupling an injection molding mold to the first side of the printed circuit board, injecting a material into the mold in liquid form, and after the material is solidified, decoupling the injection molding mold from the first side of the printed circuit board, thereby forming an optical waveguide outwardly from the first clad layer. The method may also include forming a second clad layer outwardly from the optical waveguide, and forming a metal layer outwardly from the second clad layer. In lieu of injection molding, stamping may be performed to form the core layer of the optical waveguide.

Owner:LOCKHEED MARTIN CORP

Method and system for managing data center power usage based on service commitments

ActiveUS7739388B2Reduce power consumptionReduce rateDigital data processing detailsDigital computer detailsData centerClock rate

A method of managing data center power usage based on service commitments. A power and capacity management utility measures performance characteristics of applications hosted by a data center that include power consumption and transaction processing time. When the performance characteristics are above (or below) a first pre-defined target range, the utility decreases (or increases, respectively) a clock rate and processor voltage of one or more active servers. When the performance characteristics are within the first target range and the clock speed is above (or below) a second pre-defined target range, the utility activates (or deactivates, respectively) one or more inactive (or active, respectively) servers. When the size of an inactive server pool is above a third pre-defined target range, the utility moves inactive servers to an unallocated server pool. When the size of the inactive server pool is below the third target range, the utility allocates additional servers.

Owner:TWITTER INC

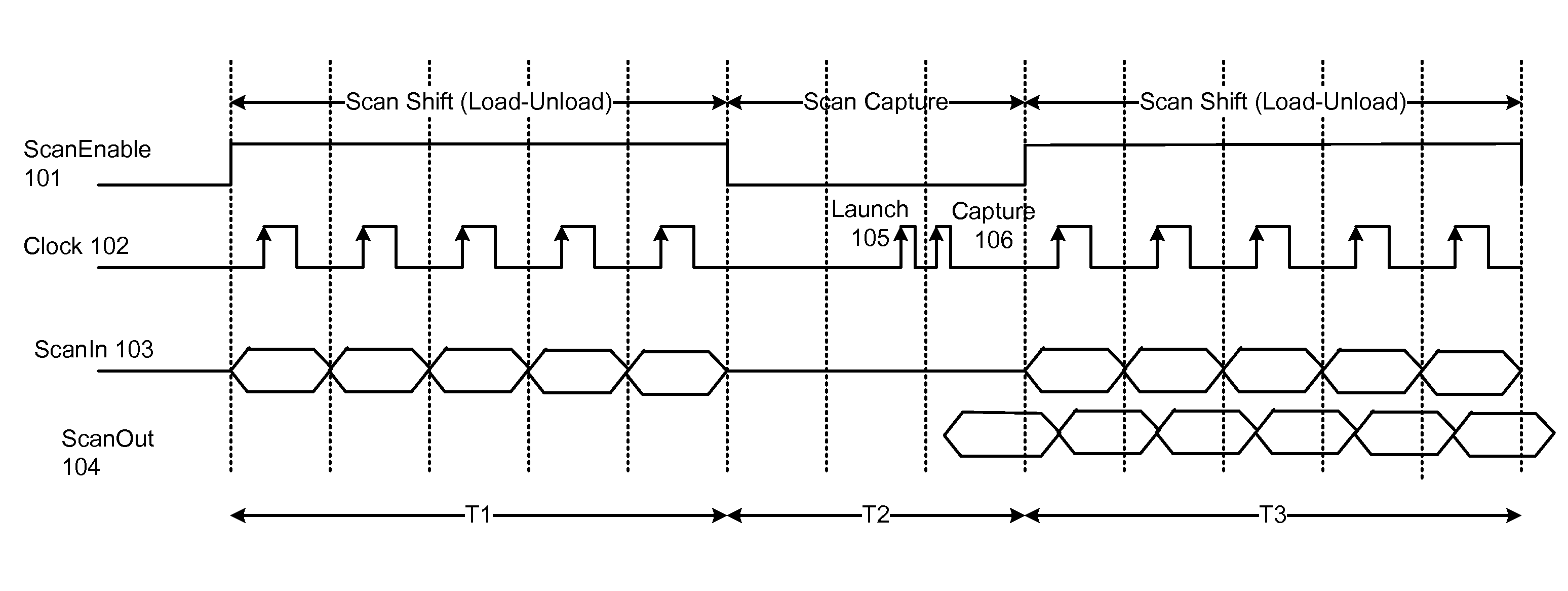

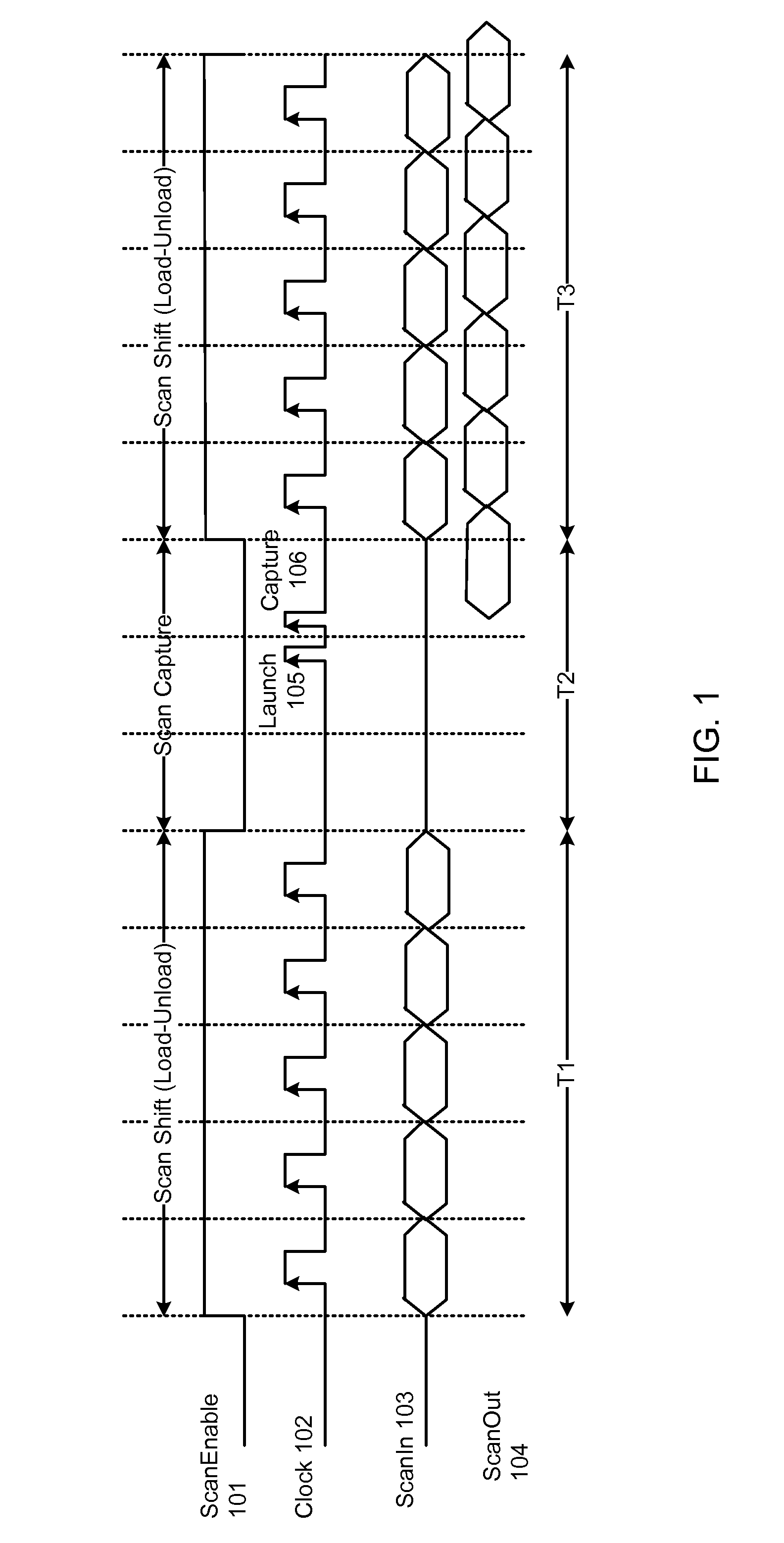

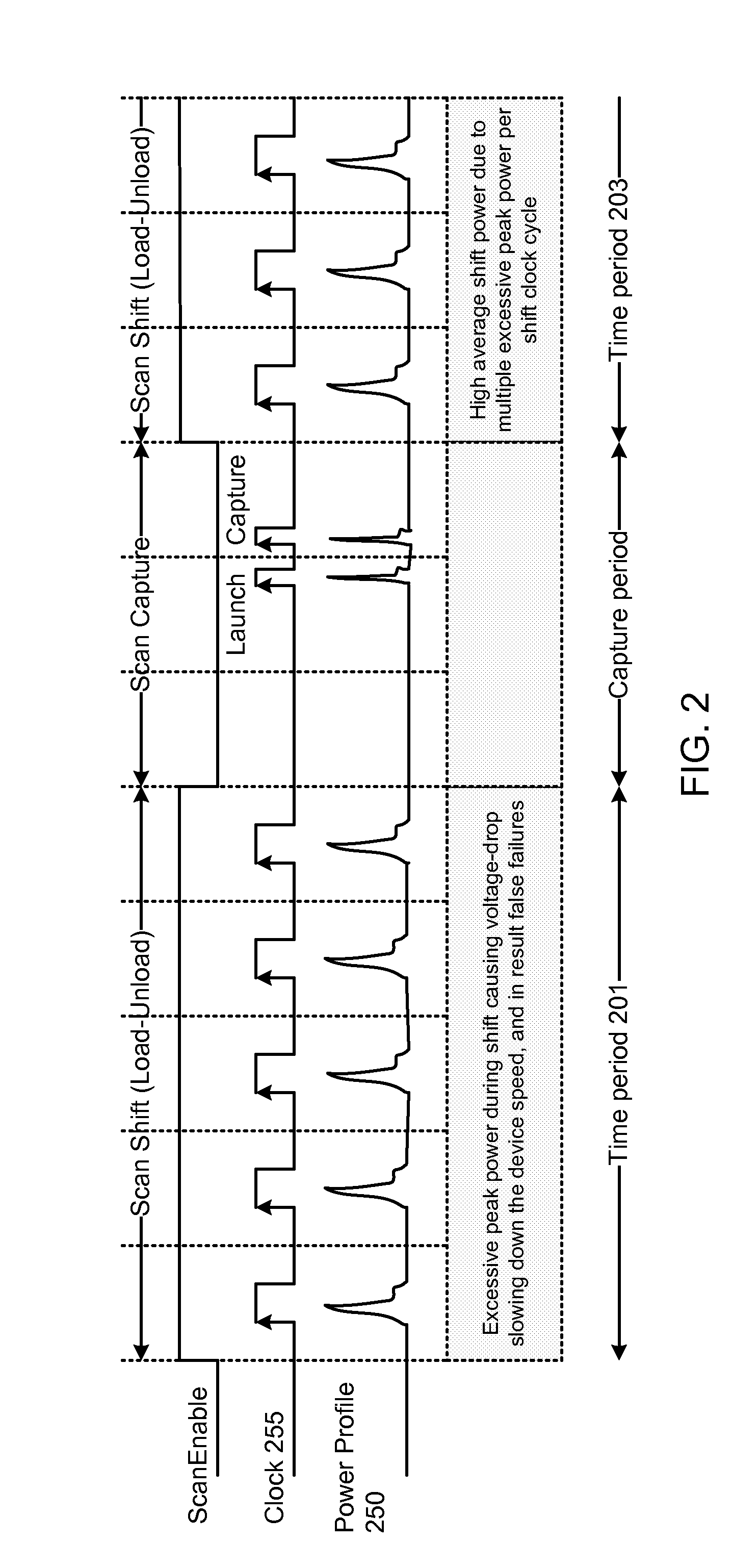

System for reducing peak power during scan shift at the global level for scan based tests

ActiveUS20140189455A1Reduce peak powerReduce decreaseElectronic circuit testingMultiplexingClock tree

A method for reducing peak power during a scan shift cycle is presented. The method comprises multiplexing a test clock with a functional clock on a integrated circuit at the root of a clock tree. The method also comprises adding a plurality of delay elements on a clock path, wherein the clock path is a signal resulting from the multiplexing. Further, the method comprises routing the clock path to a plurality of cores and a cache, e.g., an L2C cache, on the integrated circuit. Finally the method comprises staggering the test clock received by each of the plurality of cores and the cache by employing the delay elements during a scan shift cycle.

Owner:NVIDIA CORP

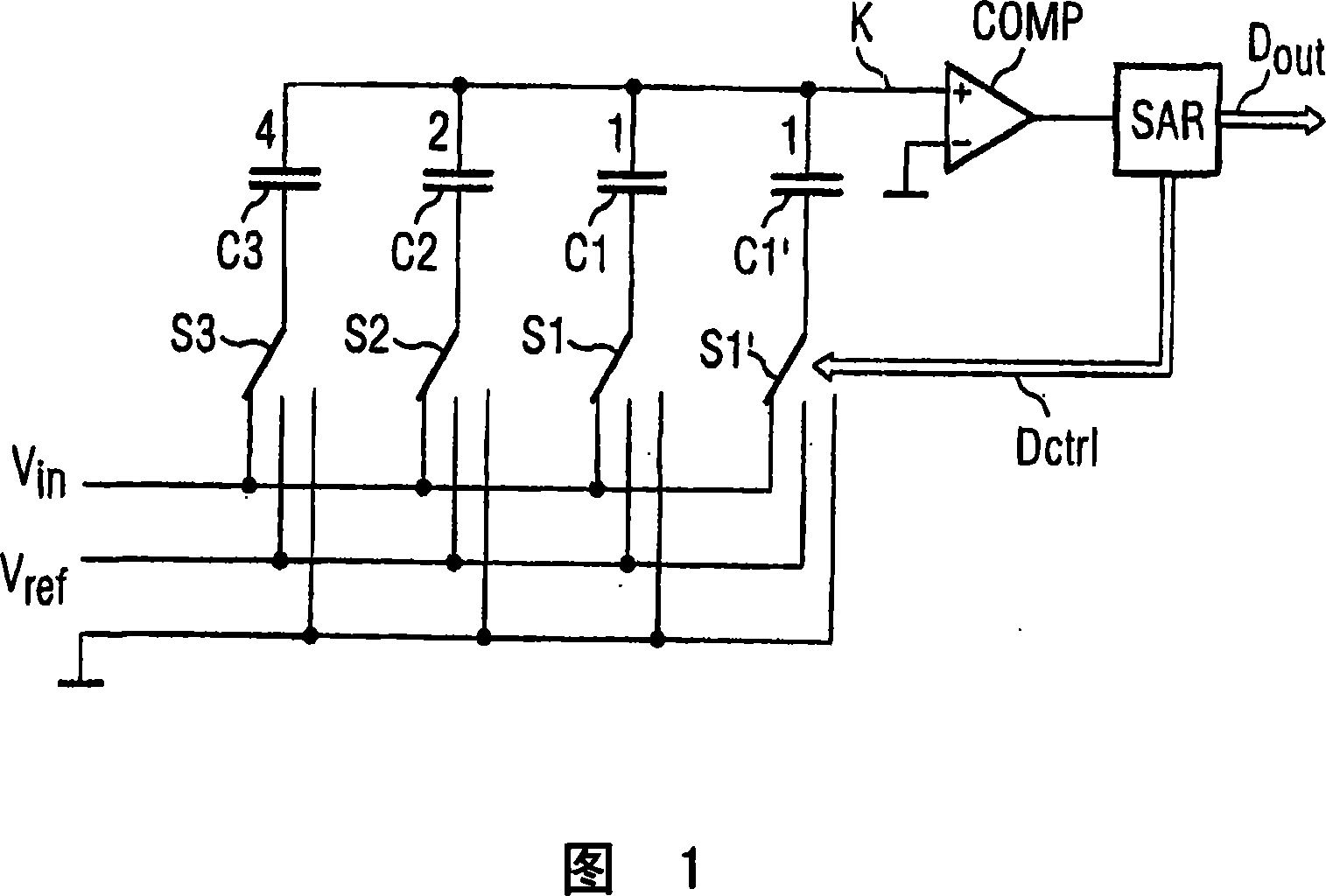

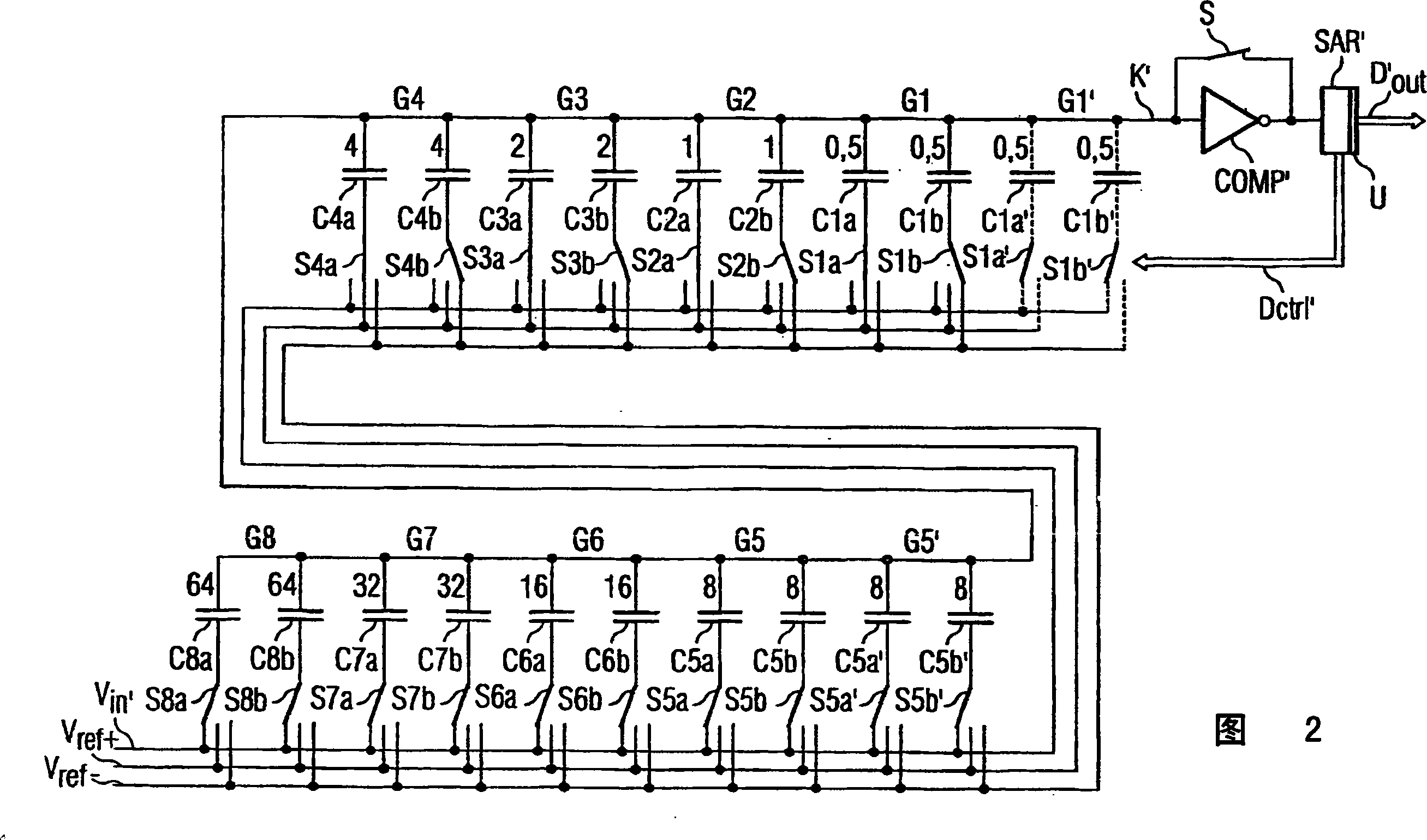

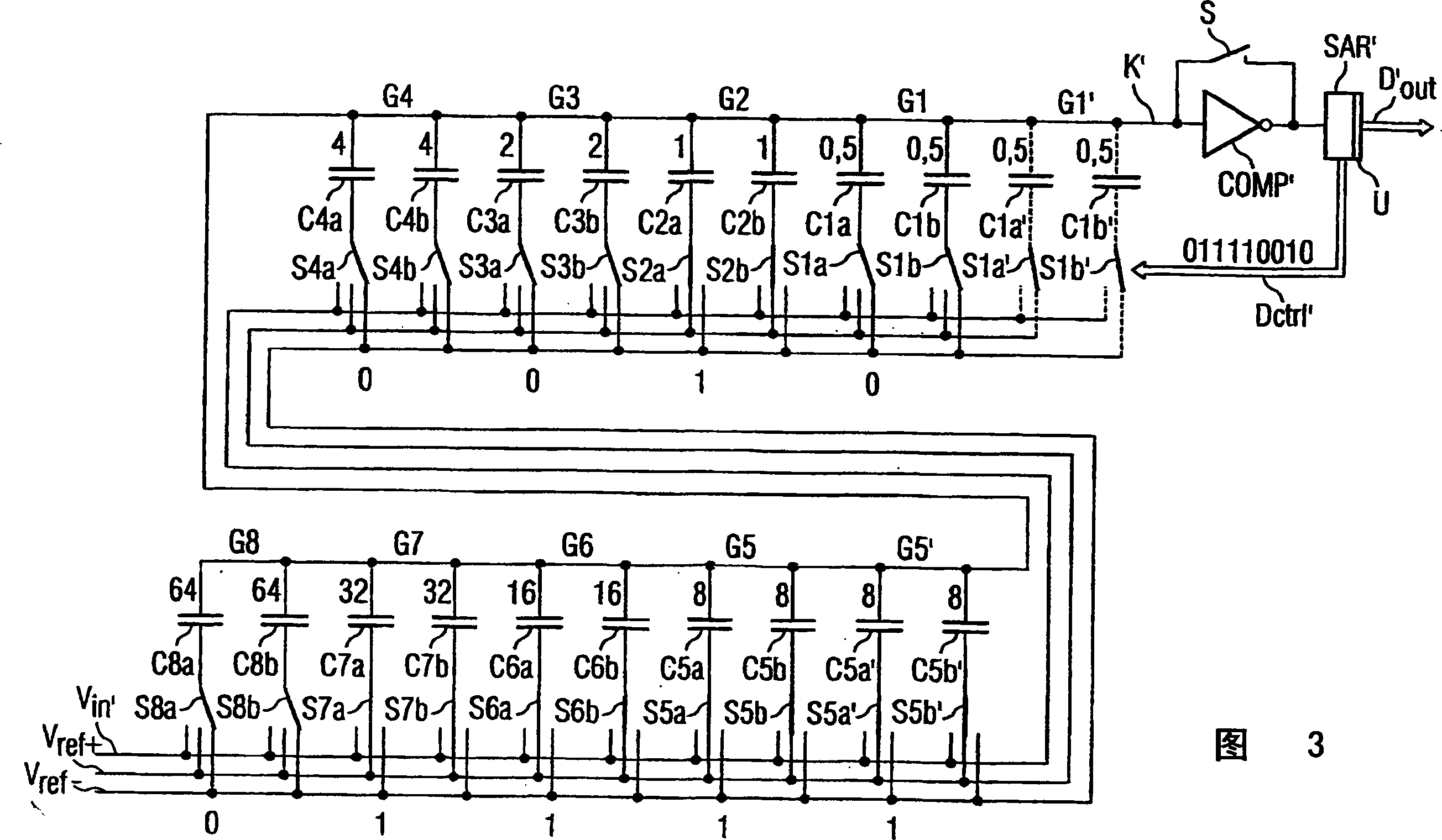

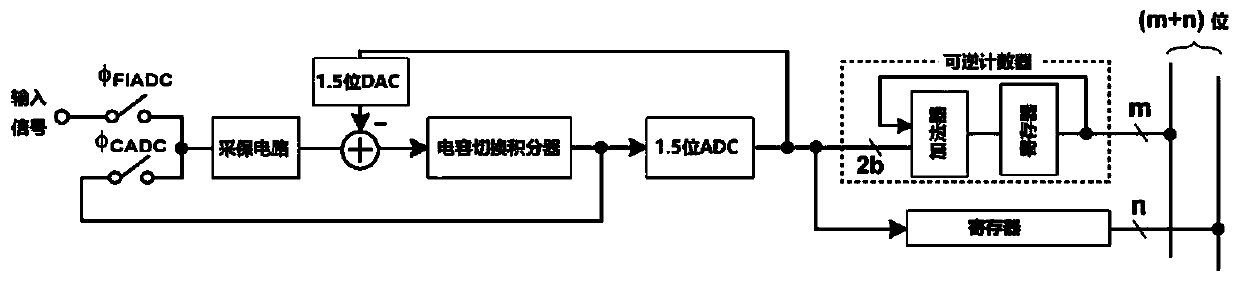

Analog/digital conversion using successive approximation and redundant weighting

InactiveCN101098147ASimple configurationIncrease clock speedAnalogue/digital conversionElectric signal transmission systemsEngineeringDigital converter

Illustrative binary networks for analog / digital converters are described. For instance, an analog / digital converter may operate in accordance with a principle of successive approximation, and may include a plurality of N+1 circuit nodes each representing one of N binary weights and M>=1 redundant binary weights, wherein each binary weight corresponds to a different position of a redundant binary code formed as part of the approximation. Illustrative methods of operation of the binary network and / or the analog / digital converter are also described.

Owner:LANTIQ DEUT GBMH

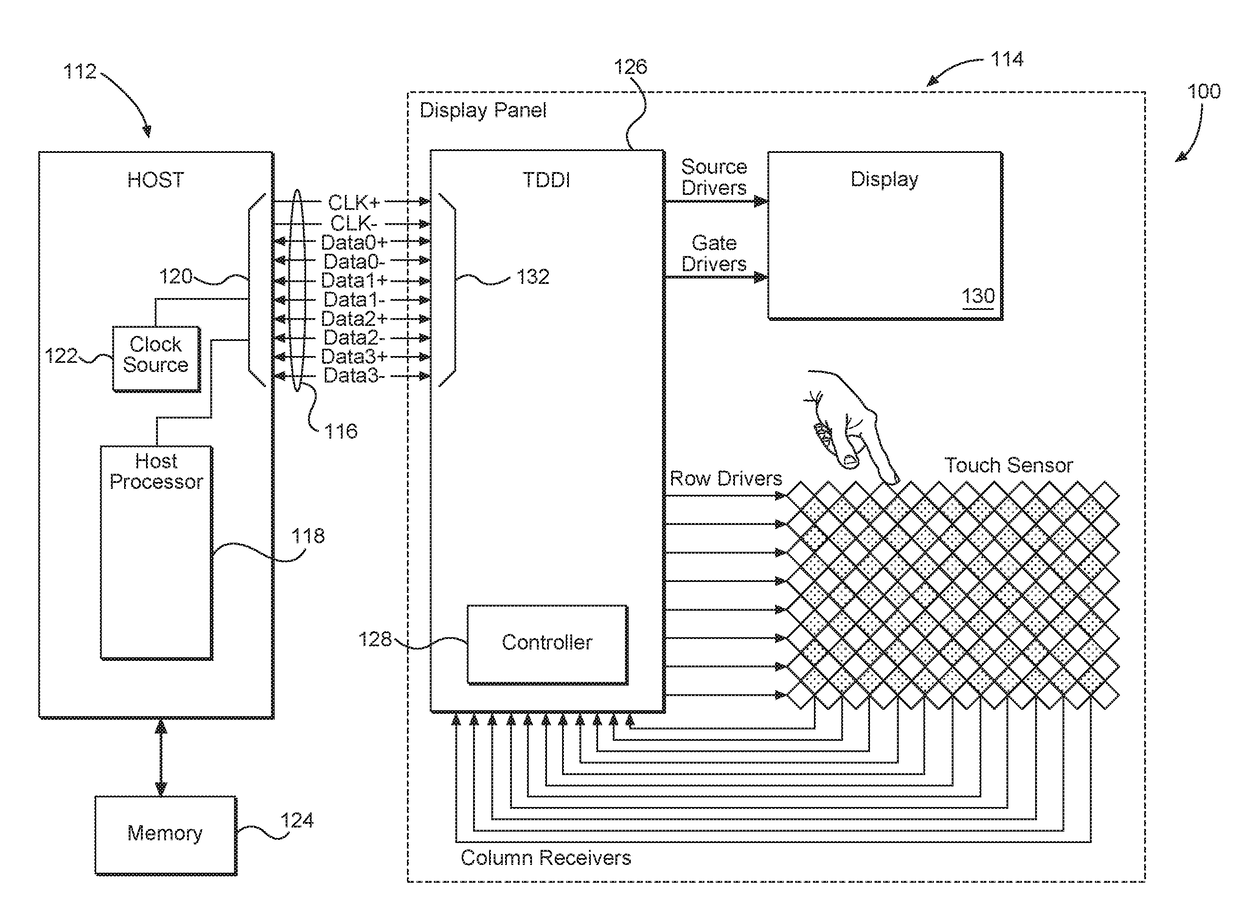

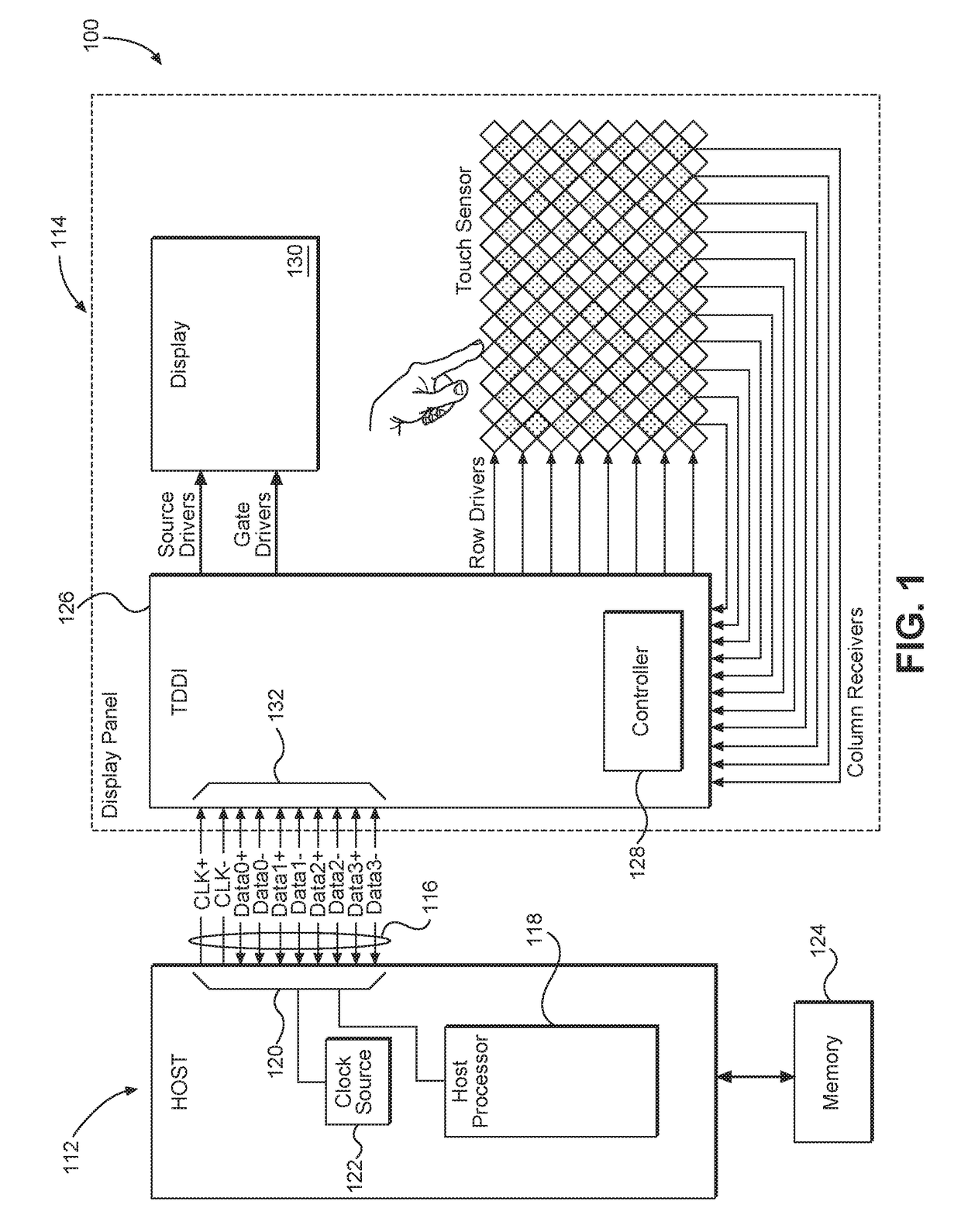

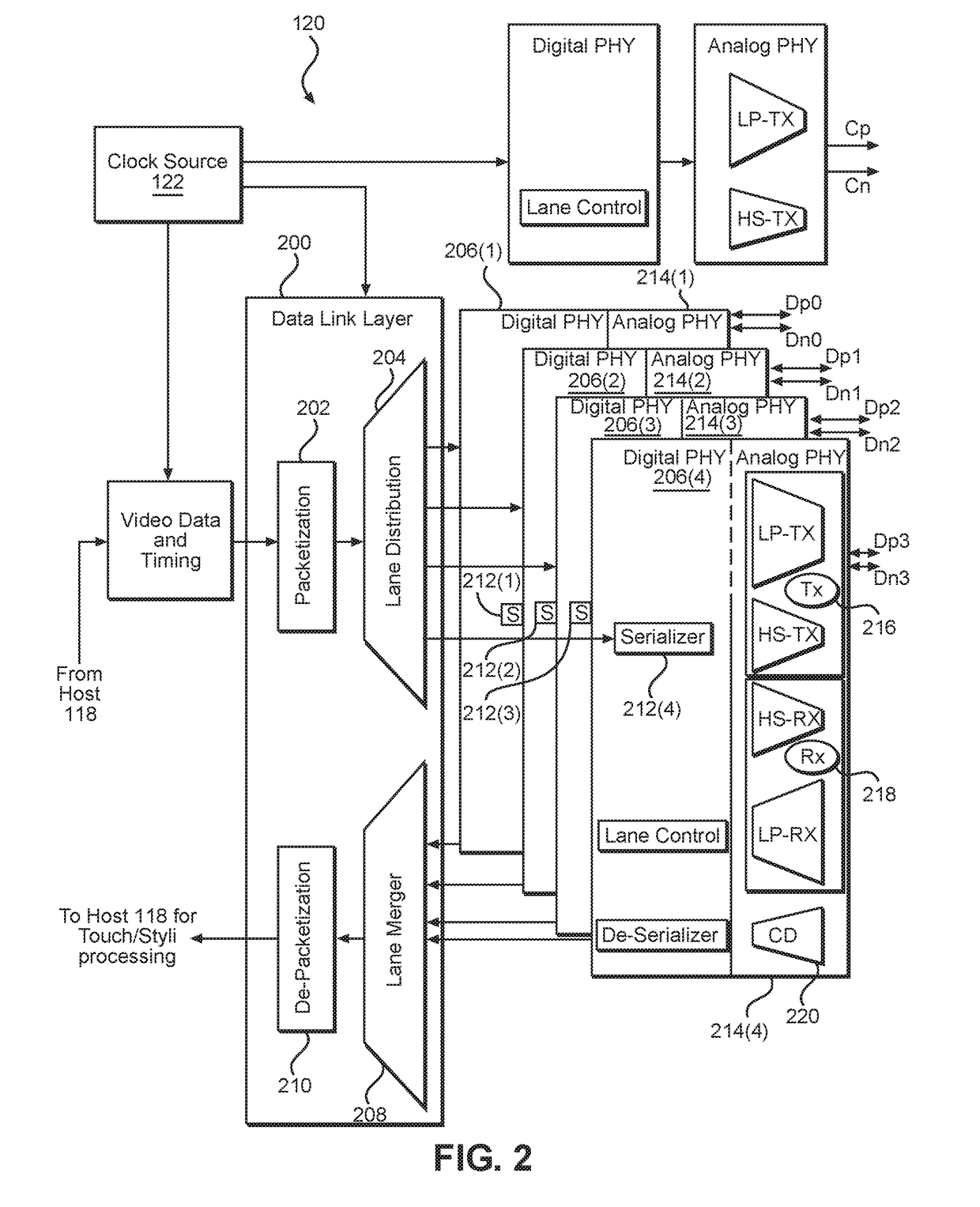

Variable rate display interfaces

ActiveUS20170315652A1High bandwidthIncrease clock speedGenerating/distributing signalsInput/output processes for data processingComputer hardwareTouchscreen

Variable rate display interfaces are disclosed. In an exemplary aspect, a high-speed reverse data transfer is enabled over plural lanes of a display serial interface (DSI) bus during blanking periods. Further increases in bandwidth of each high-speed reverse data transfer may be achieved by increasing DSI clock speed during the blanking periods. Since a display relies on a host clock to send reverse data, the frequency of the reverse data is increased, which effectively increases the bandwidth of reverse channel lanes. By increasing the reverse bandwidth over existing pins in the DSI bus, more data may be transferred to the host, including raw touch / stylus data rather than processed data. The raw data may then be processed by the host's relatively powerful processors. By shifting the processing to the host, the need for a powerful touch screen controller (TSC) and / or a powerful touch display driver integrated circuit (TDDI) may be avoided.

Owner:QUALCOMM INC

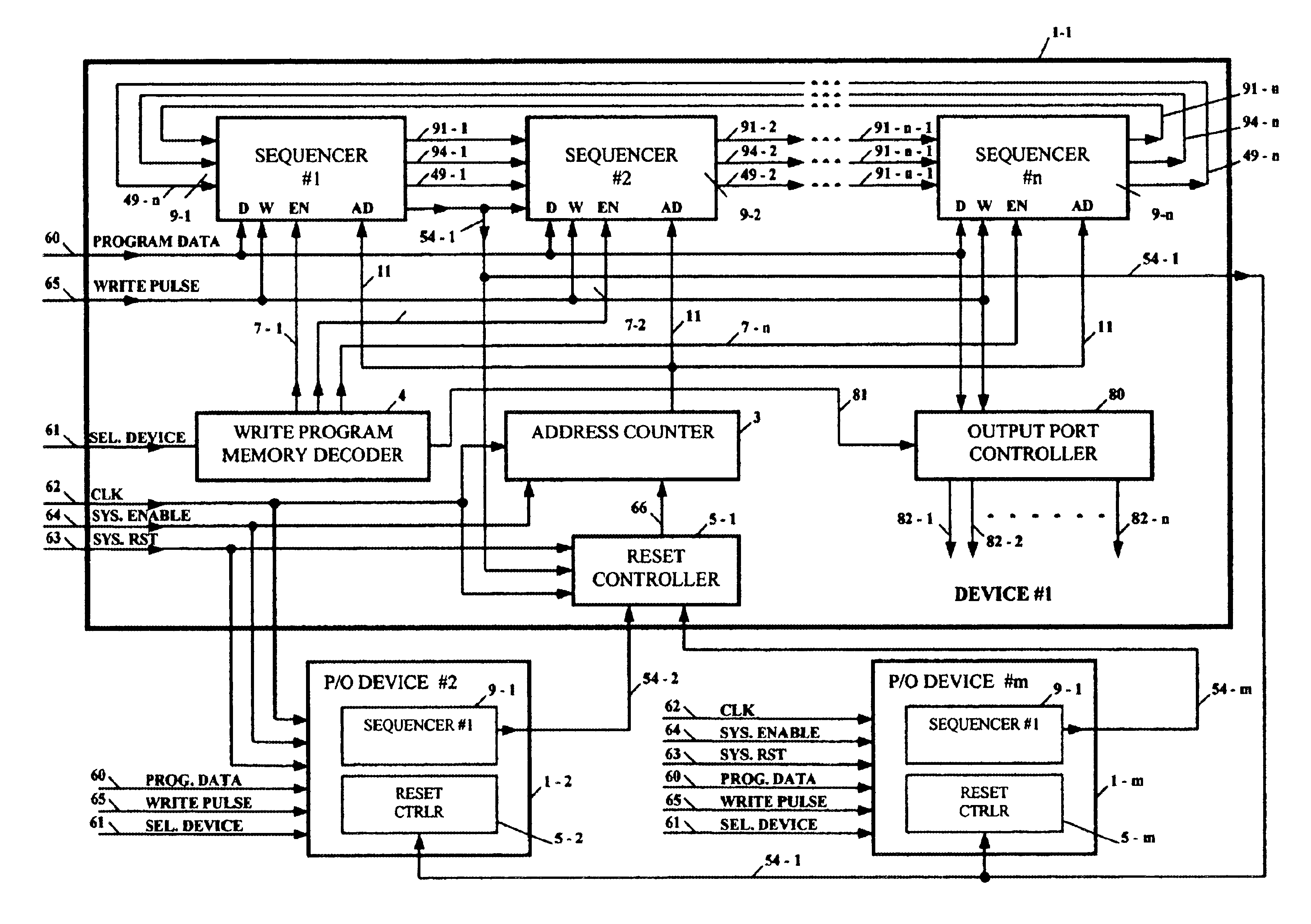

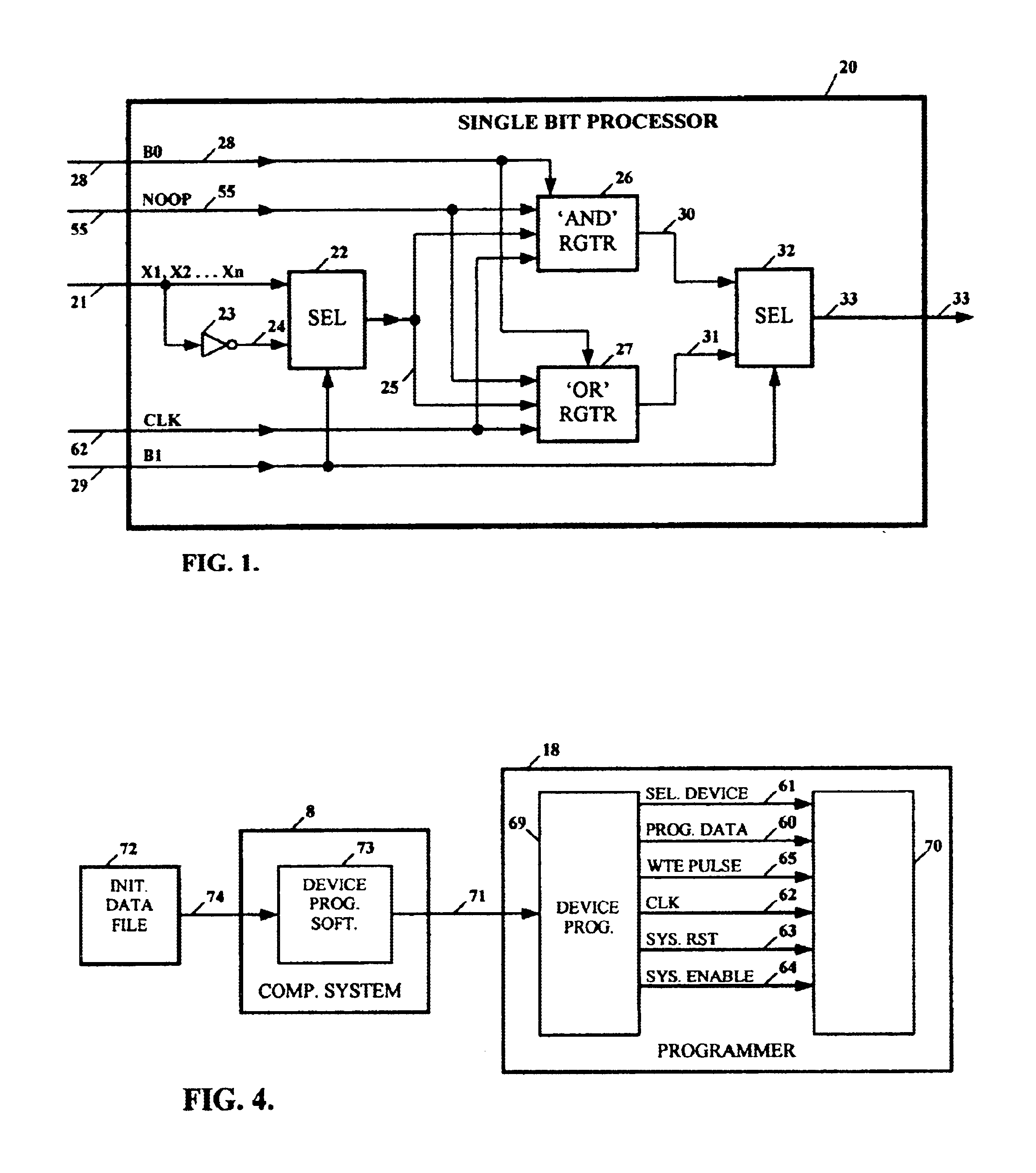

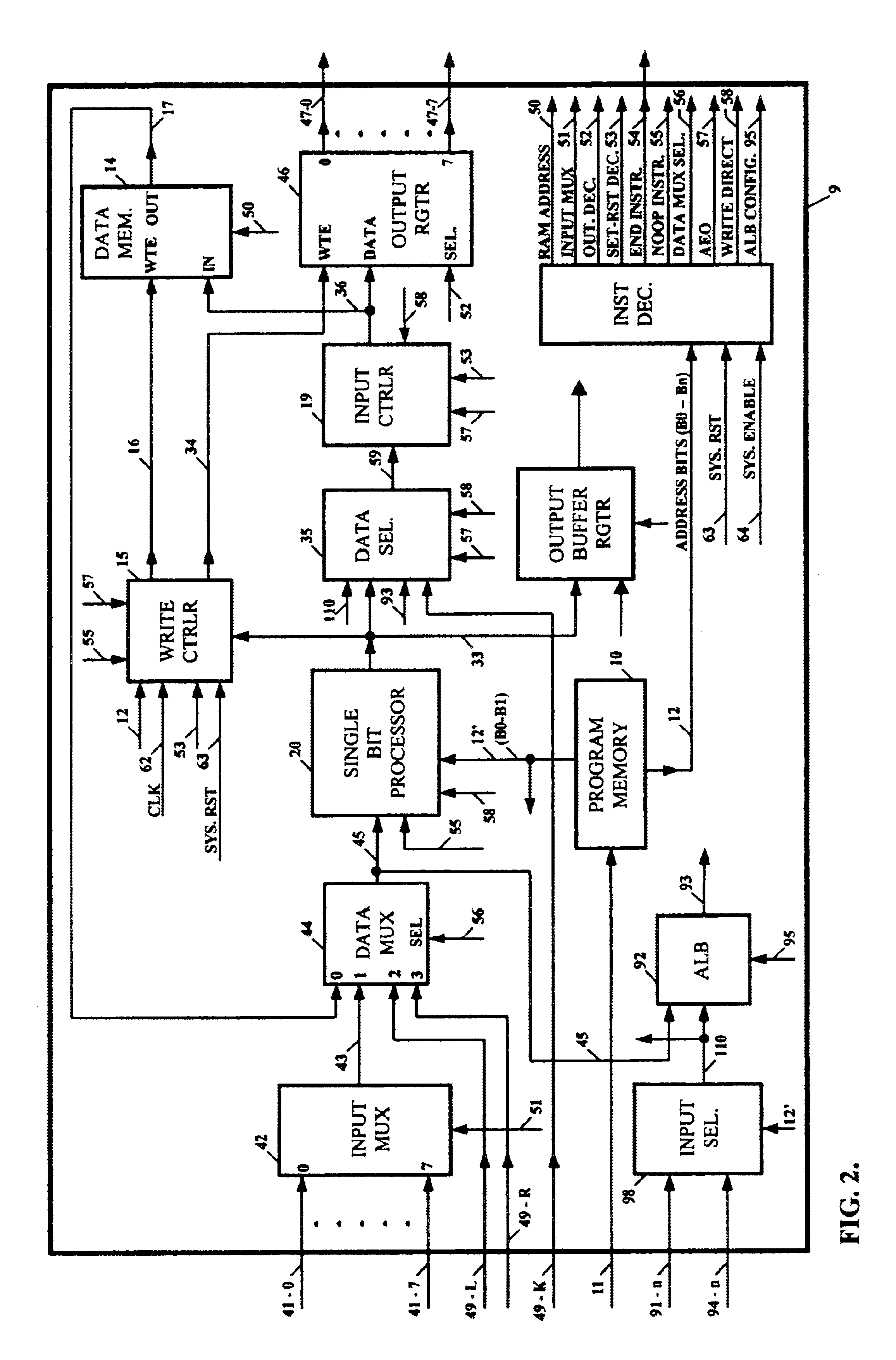

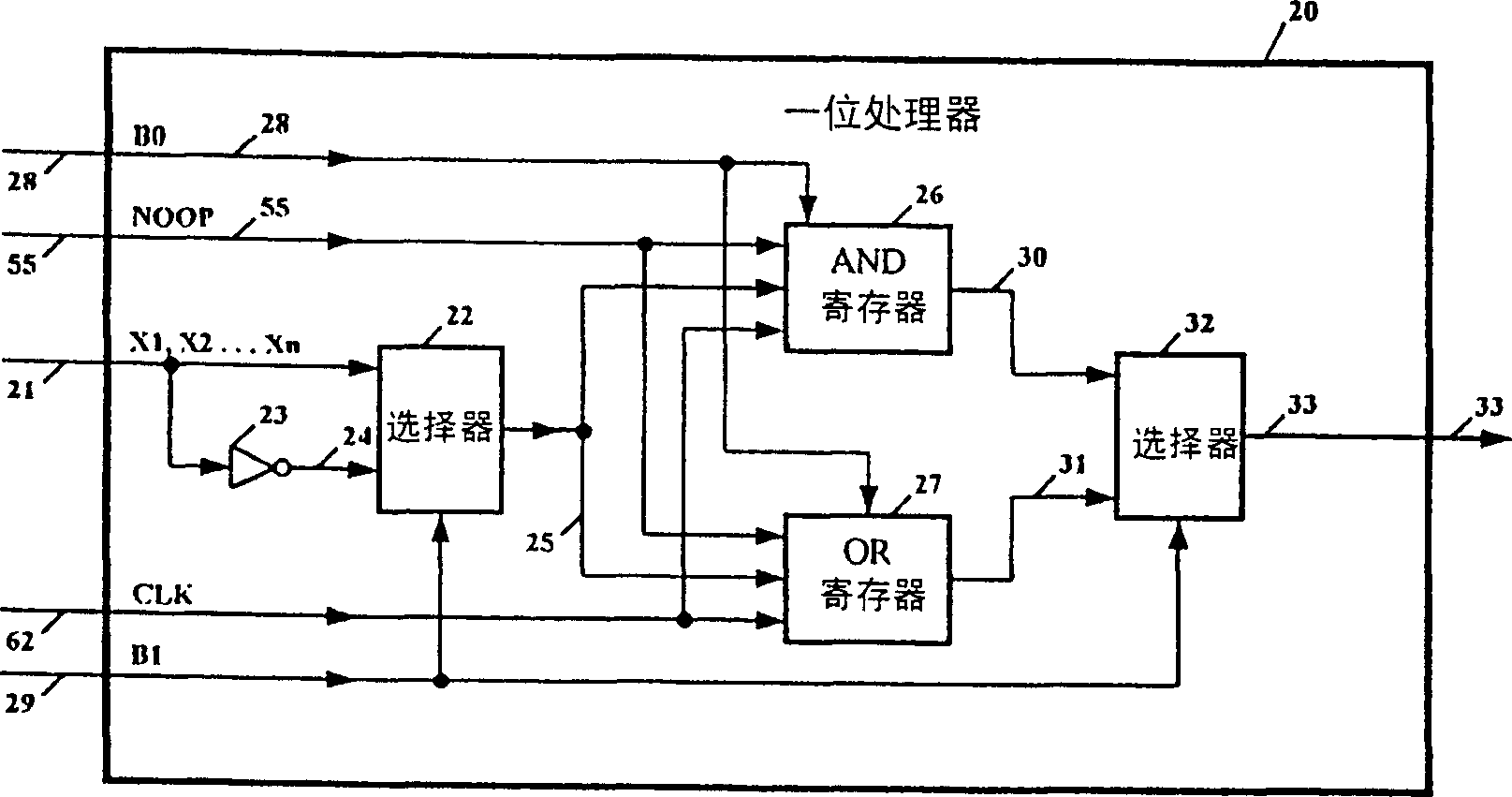

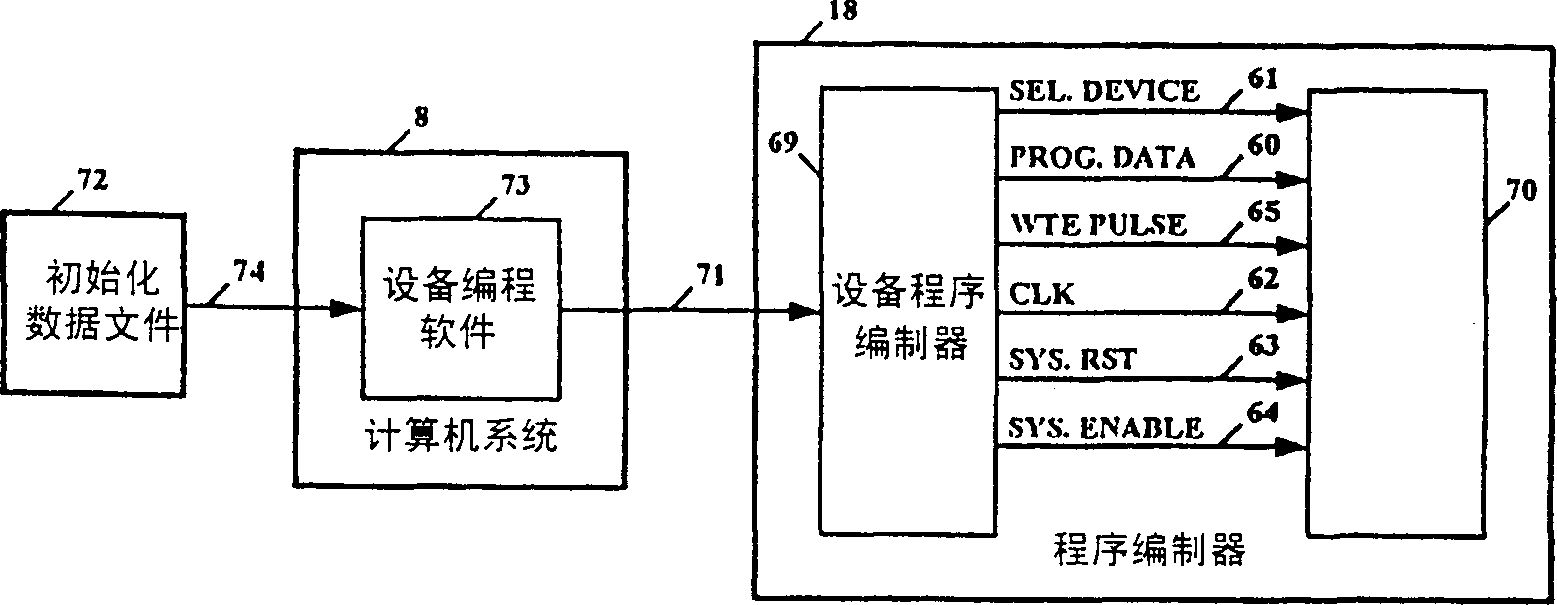

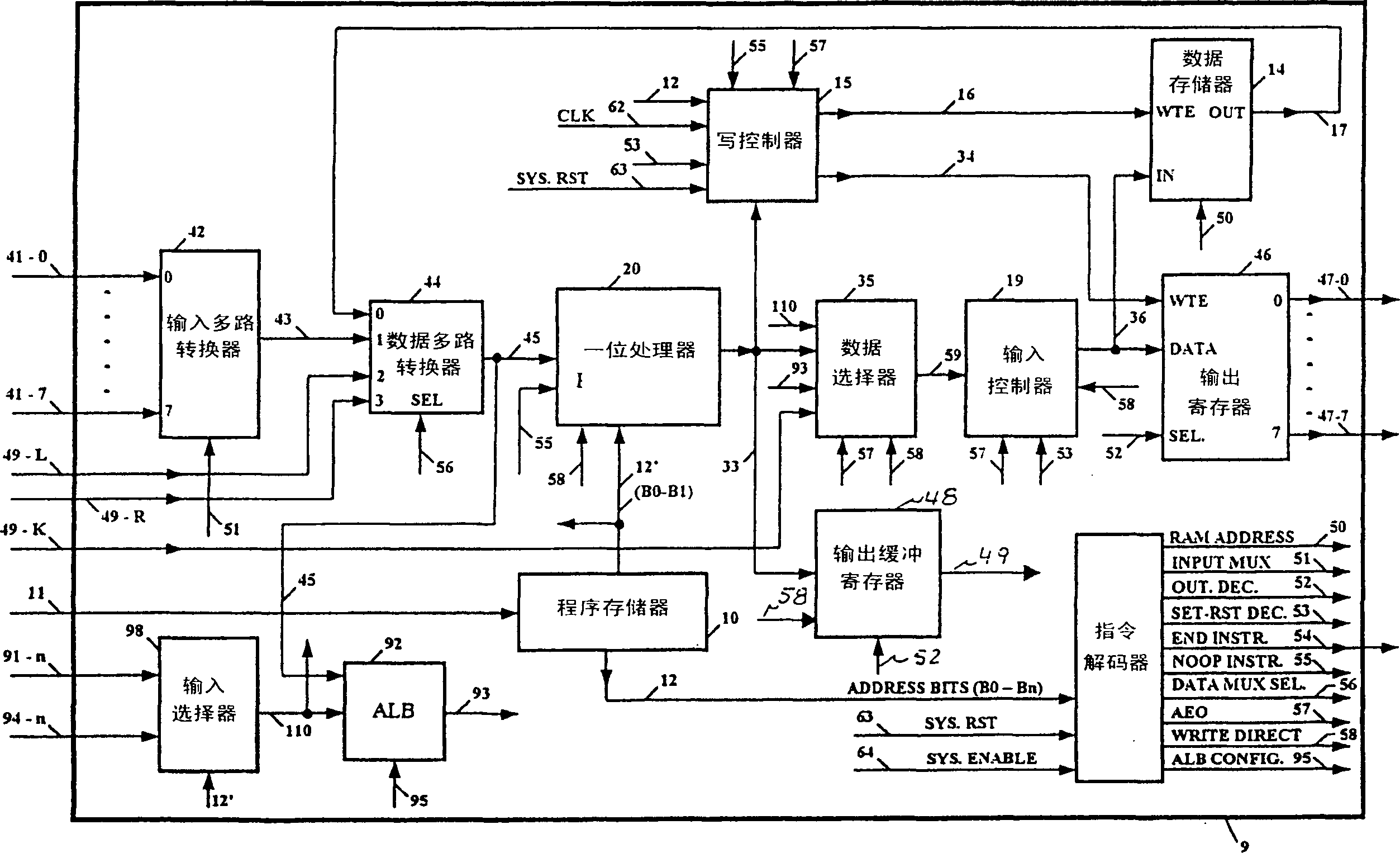

Compiler synchronized multi-processor programmable logic device with direct transfer of computation results among processors

InactiveUS6915410B2Improve overall utilizationEasy to handleSingle instruction multiple data multiprocessorsMultiple digital computer combinationsControl signalProgrammable logic device

A system for designing and implementing digital integrated circuits utilizing a set of synchronized sequencers that permit quick and efficient parallel processing of system level designs. The system and method converts digital schematics and hardware description language (HDL) based designs into a set of logic equations and single bit arithmetic-logic operations executed by a set of parallel operating sequencers. The system includes software for converting netlists and HDL designs into Boolean logic equations, and a compiler for distributing these logic equations between multiple sequencers. Each sequencer is comprised of a logic processor and the associated program memory for storing the executable code of the assigned Boolean logic equations and data memory for storing the results of processing of logic equations. To synchronize execution of logic equations by multiple sequencers, all program memories are addressed by one common address register. The processing of logic equations is arranged in such a manner that their outputs can be read by synchronized read instructions in the interconnected sequencers, eliminating any need for control signals.

Owner:HYDUKE STANLEY M

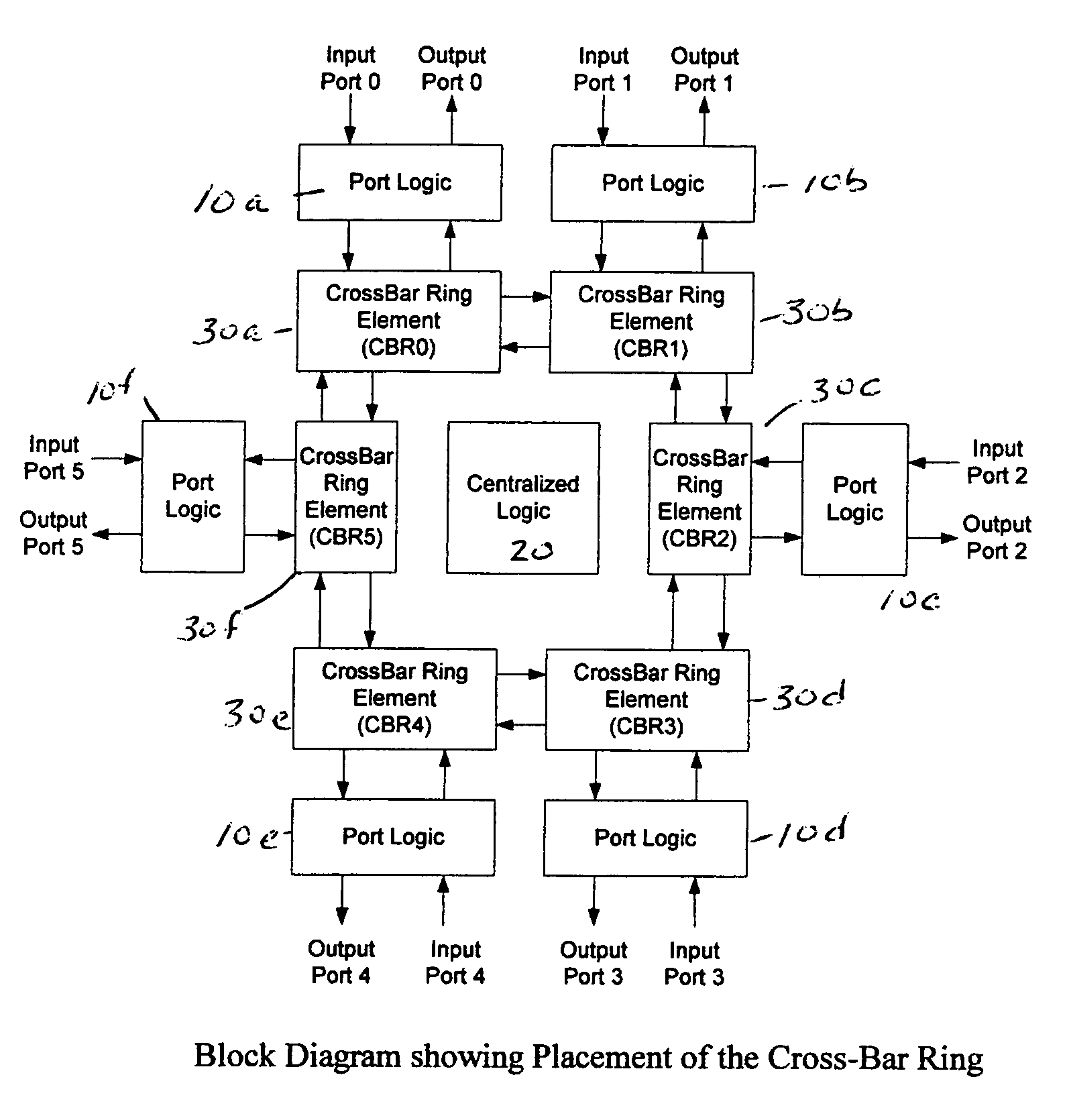

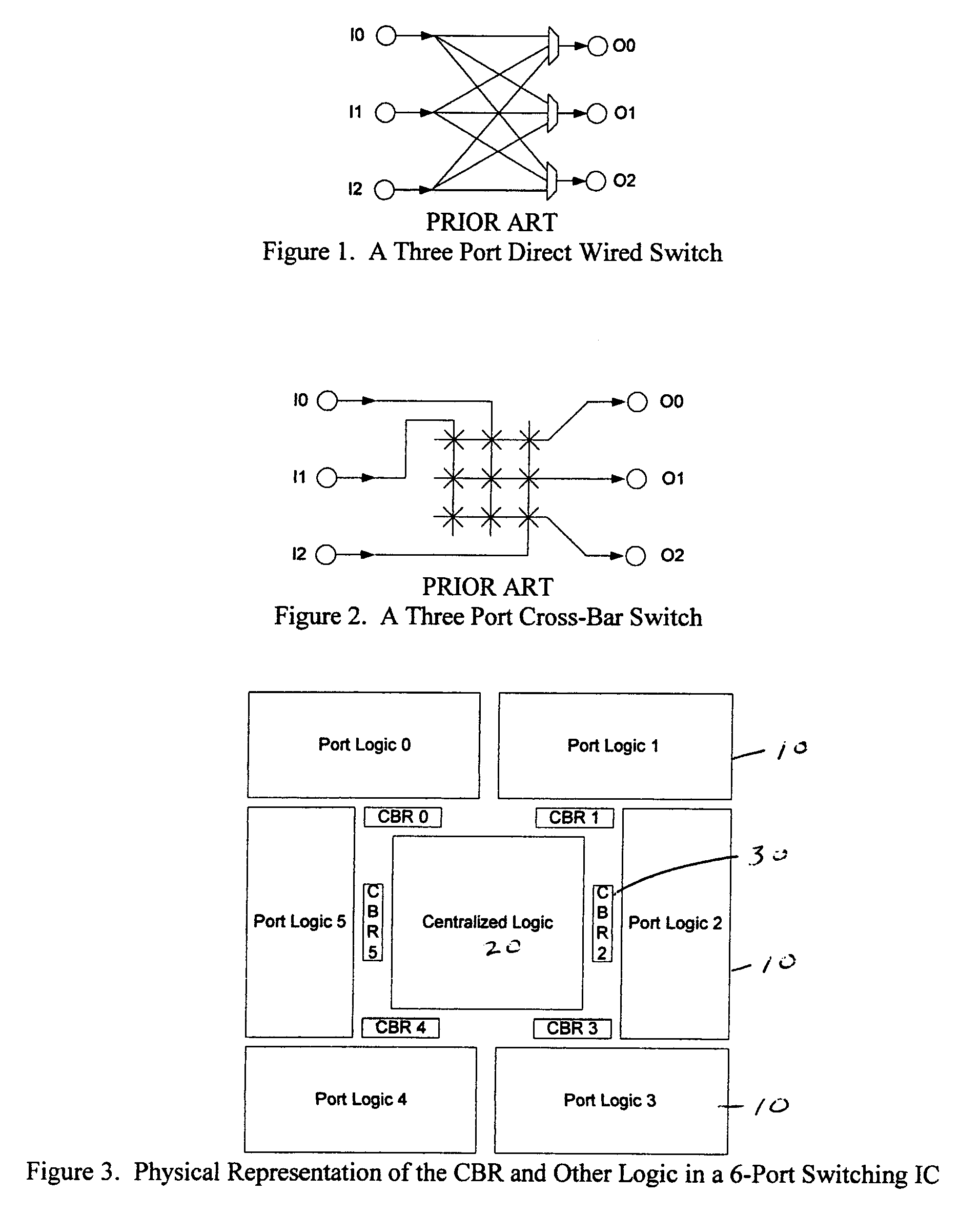

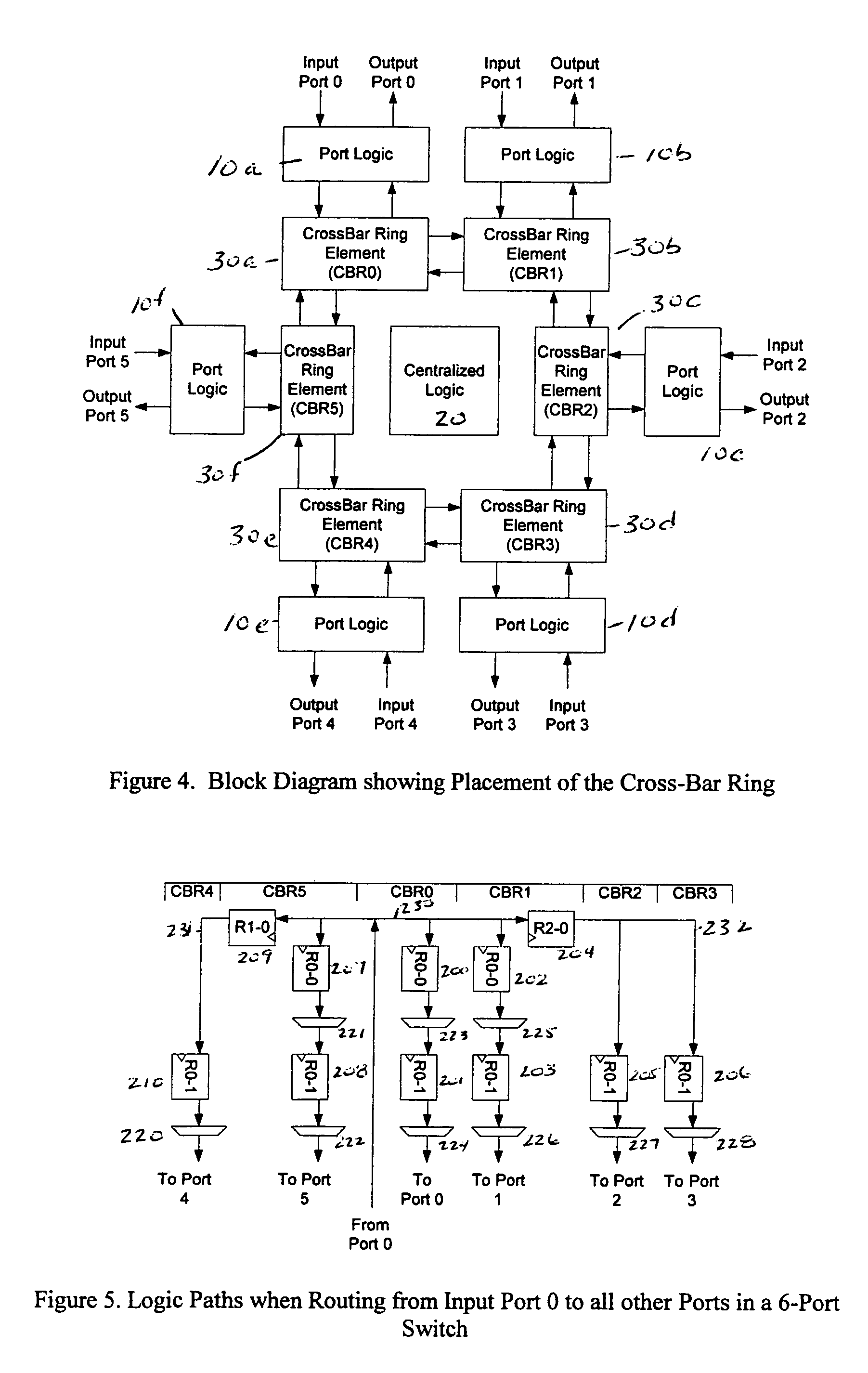

Communication mechanism

ActiveUS7155557B2Improve distributionAid in placement and routingTransmissionMemory systemsEngineeringSemiconductor

The invention provides an interconnection architecture for semiconductor devices. Cross bar switches are traditionally placed in the center of the IC. However, this location may also be the preferred location for the centralized logic in the IC. This invention, known as a cross bar ring or CBR, provides cross bar switch functionality in a manner that can be easily distributed around the chip. Typically, it can fit in the routing channels between other functional blocks, thereby allowing other centralized functions to be placed in the center of the IC. The CBR is defined so that it can be partitioned into separate modules, which greatly aids in the placement and routing of wires. Furthermore, the architecture is defined such that the CBR can use storage elements, allowing it to be pipelined so that the wire distances can be increased while still maintaining a high internal clock speed. The use of storage elements also allows the CBR to provide a deterministic delay between any two locations on the IC, and can, if desired, insure a constant delay regardless of source and destination.

Owner:CALLAHAN CELLULAR L L C

Digital circuit implementation by means of parallel sequencers

InactiveCN1422406AReduce the number of instructionsIncrease clock speedSingle instruction multiple data multiprocessorsMultiple digital computer combinationsControl signalData memory

A system for designing and implementing digital integrated circuits utilizing a set of synchronized sequencers that permit quick and efficient parallel processing of system level designs. The system and method converts digital schematics and hardware description language (HDL) based designs into a set of logic equations and single bit arithmetic-logic operations executed by a set of parallel operating sequencers. The system includes software for converting netlists and DHL designs into Boolean logic equations, and a compiler for distributing these logic equations between multiple sequencers. Each sequencer is comprised of a logic processor and the associated program memory for storing the executable code of the assigned Boolean logic equations and data memory for storing the results of processing of logic equations. To synchronize execution of logic equations by multiple sequencers, all program memories are addressed by one common address register. The processing of logic equations is arranged in such a manner that their outputs can be read by synchronized read instructions in the interconnected sequencers, eliminating any need for control signals.

Owner:斯坦利 M 海杜克

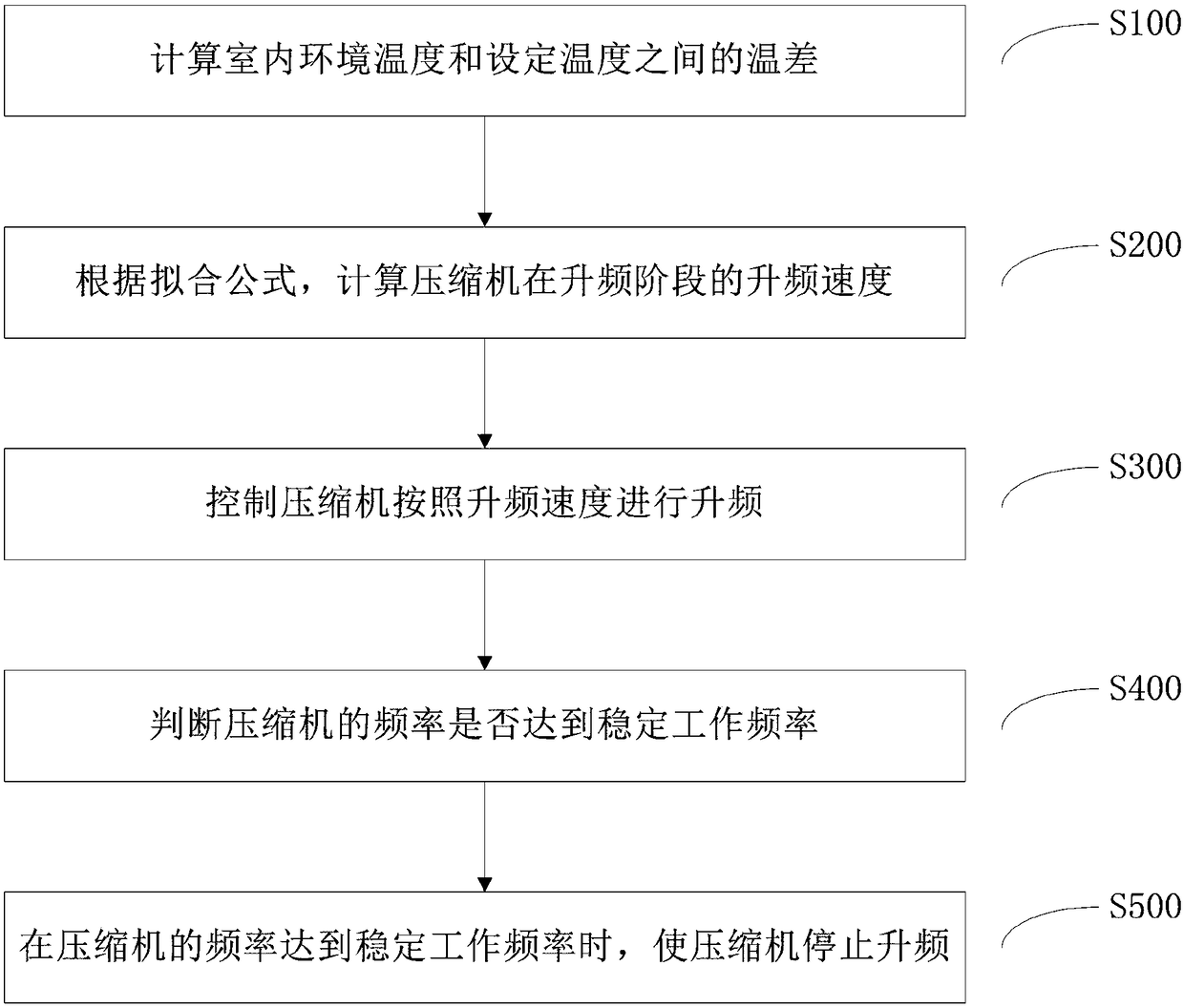

Control method of air conditioner

PendingCN108548289AImprove experienceIncrease clock speedMechanical apparatusSpace heating and ventilation safety systemsTemperature differenceControl theory

The invention relates to the technical field of air conditioners, in particular to a control method of an air conditioner. Through the control method, the problems of poor universality and poor user experience existing in an existing air conditioner control method can be solved. The control method comprises the steps that the temperature difference between indoor environment temperature and the set temperature is calculated; according to a fitting formula, frequency raising speed of a compressor in the frequency raising stage is calculated; and the compressor is controlled to raise frequency according to the frequency raising speed, specifically, the fitting formula is determined according to the corresponding relation between the temperature difference and the frequency raising speed of the compressor. The fitting formula is determined in advance, then the frequency raising speed of the compressor in the frequency raising stage is calculated according to the fitting formula, and thenthe compressor is controlled to raise the frequency according to the frequency raising speed. Through the control method of the air conditioner, the universality of the air conditioner and use experience of a user can be improved.

Owner:QINGDAO HAIER AIR CONDITIONER GENERAL CORP LTD

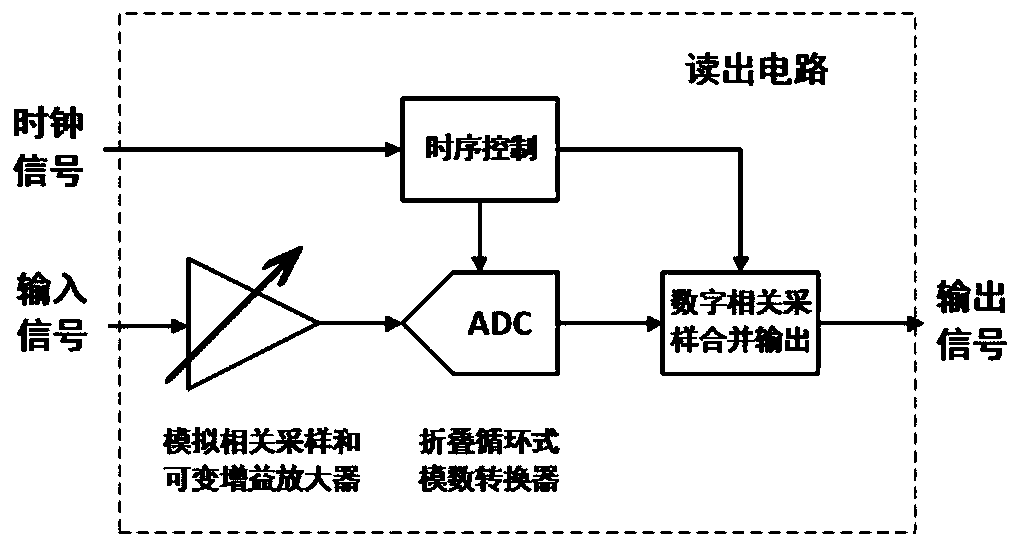

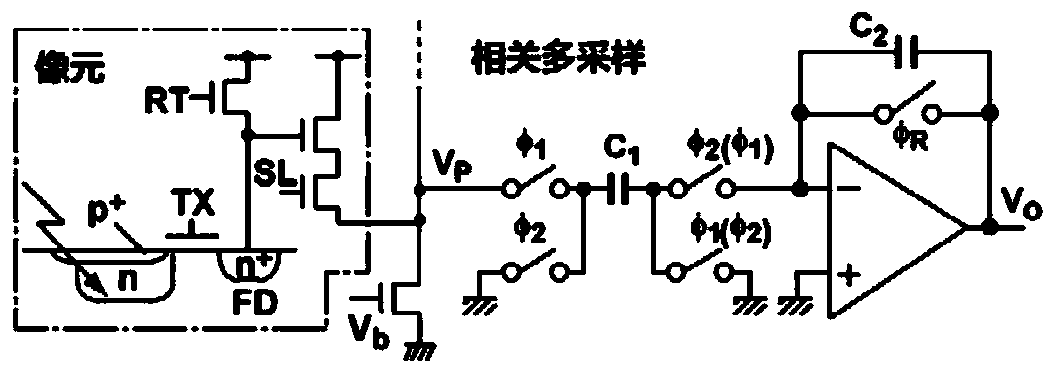

High dynamic range reading circuit based on backside illuminated image sensor

ActiveCN111556266AReduce noiseImprove dynamic rangeTelevision system detailsColor television detailsHemt circuitsA d converter

The invention discloses a high dynamic range reading circuit based on a backside illuminated image sensor, which comprises an analog correlation sampling and programmable gain amplifier, and is characterized in that a voltage signal read from a pixel is amplified and then transmitted to a lower-level analog-to-digital converter through a switch switching strategy of multiple times of sampling andholding and adjustment to a set gain; the folding circulating analog-to-digital converter is used for quantizing the signals subjected to preceding-stage preventive large sampling; the digital correlation sampling merging logic circuit is used for obtaining a real digital quantized signal; the time sequence control circuit is used for controlling the analog-to-digital converters in each column line by line; an input signal sequentially passes through the analog correlation sampling and programmable gain amplifier, the folding circulation type analog-to-digital converter and the digital correlation sampling merging logic circuit and then outputs a quantized signal, and a clock signal passes through the sequential control circuit and then is input into the folding circulation type analog-to-digital converter and the digital correlation sampling merging logic circuit. Quantization errors are reduced, the dynamic range is enlarged, and the overall power consumption and area of the readingcircuit are reduced.

Owner:XI AN JIAOTONG UNIV