Patents

Literature

52 results about "Cross bar switch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

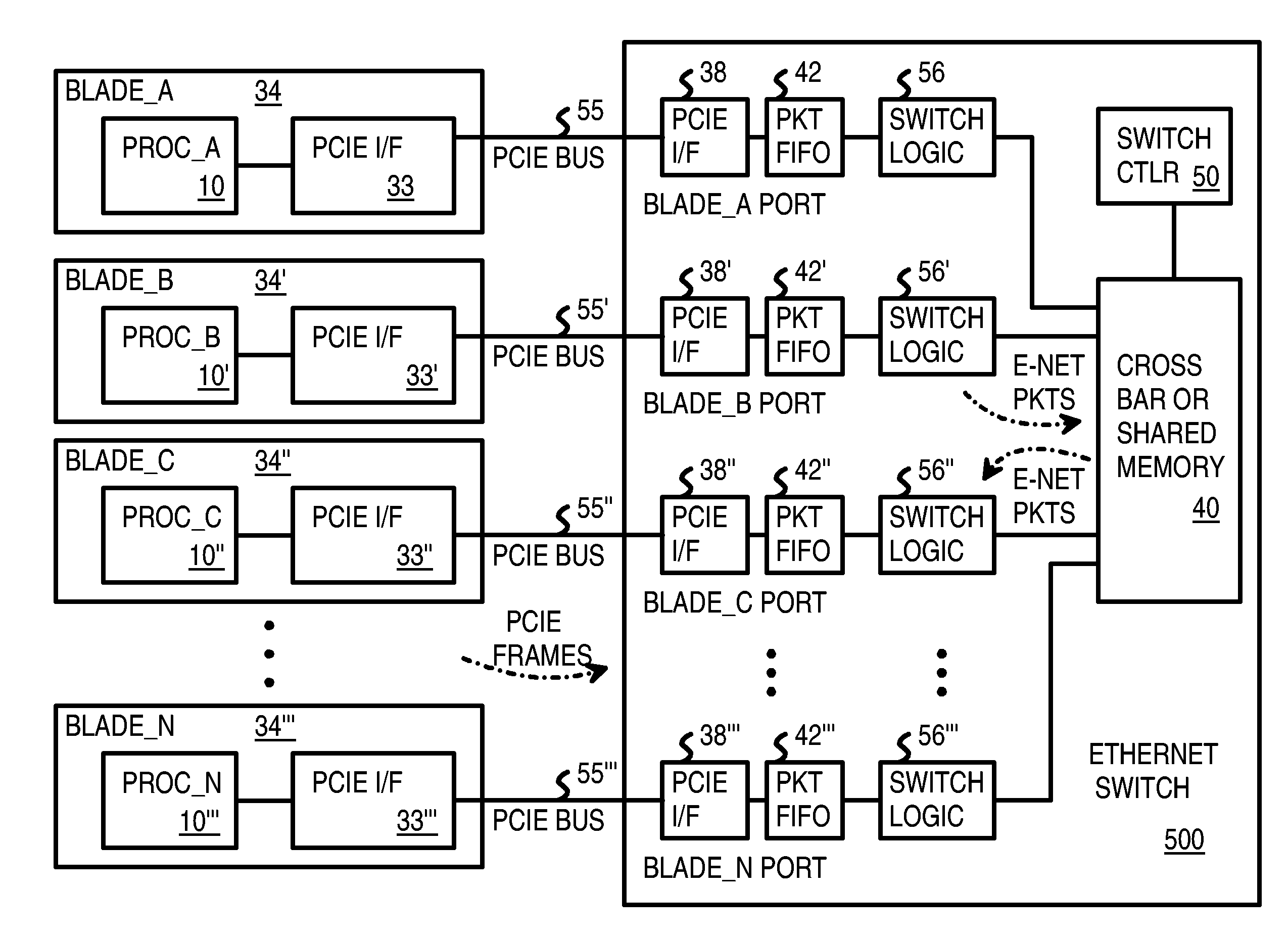

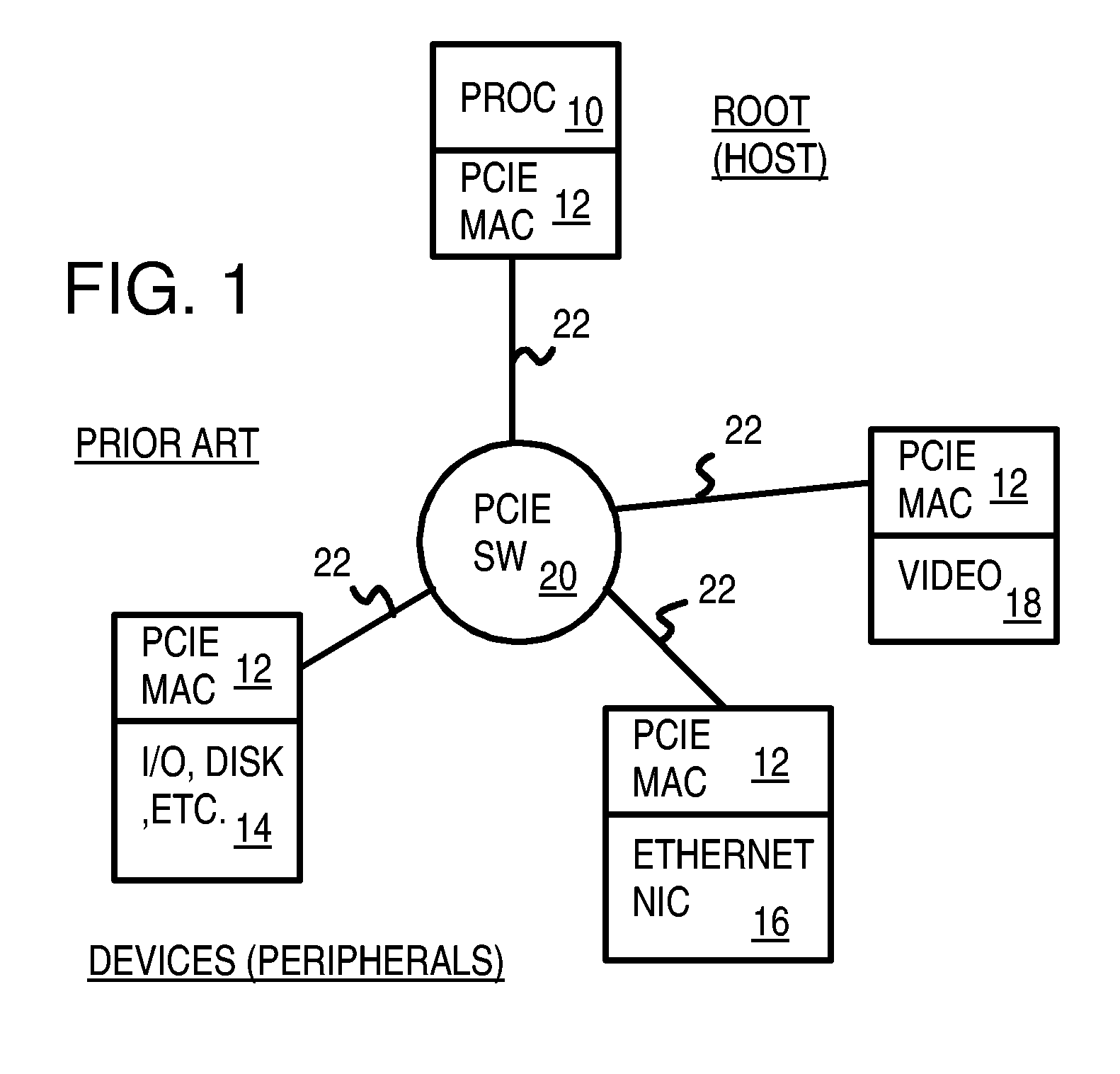

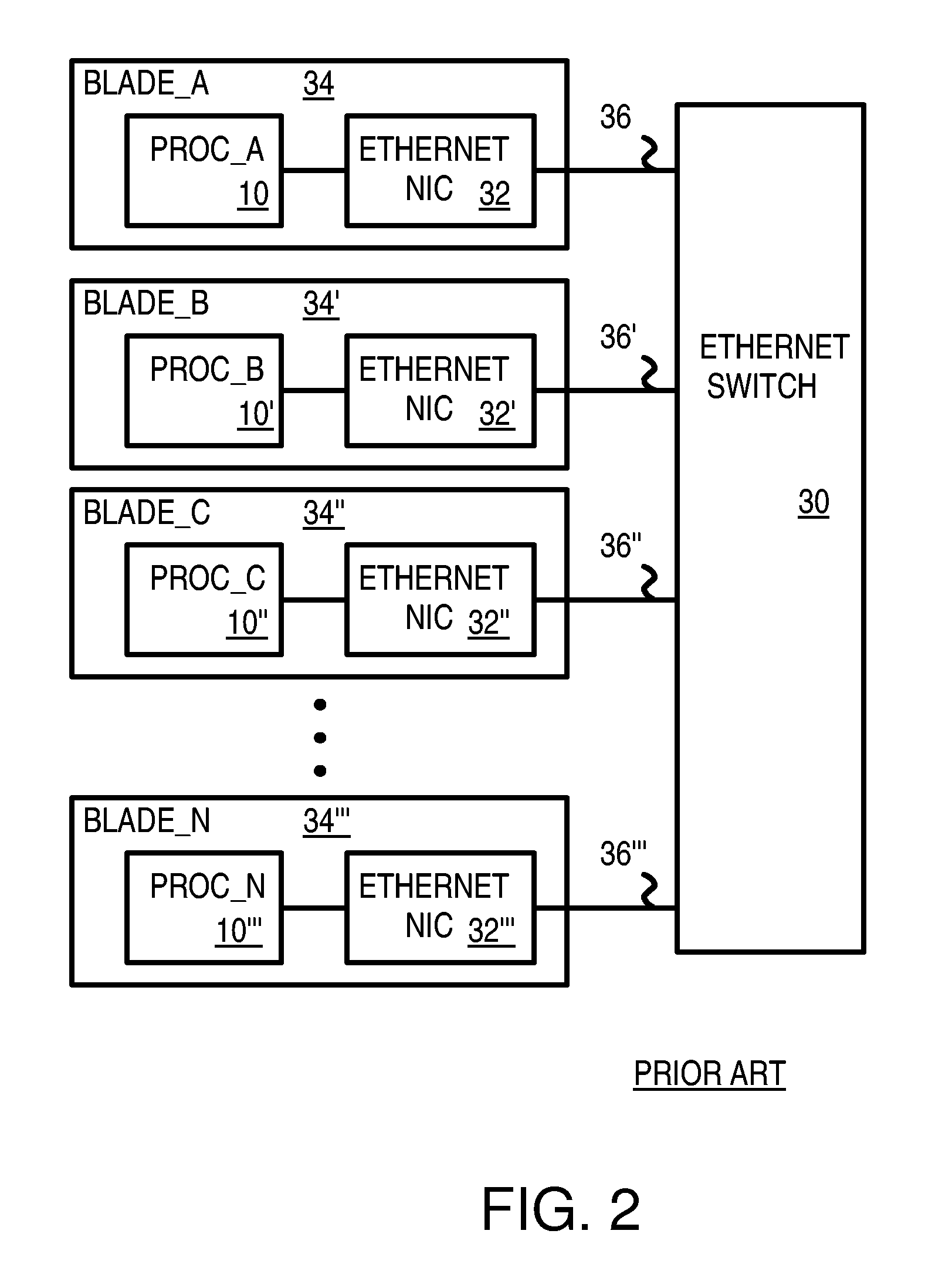

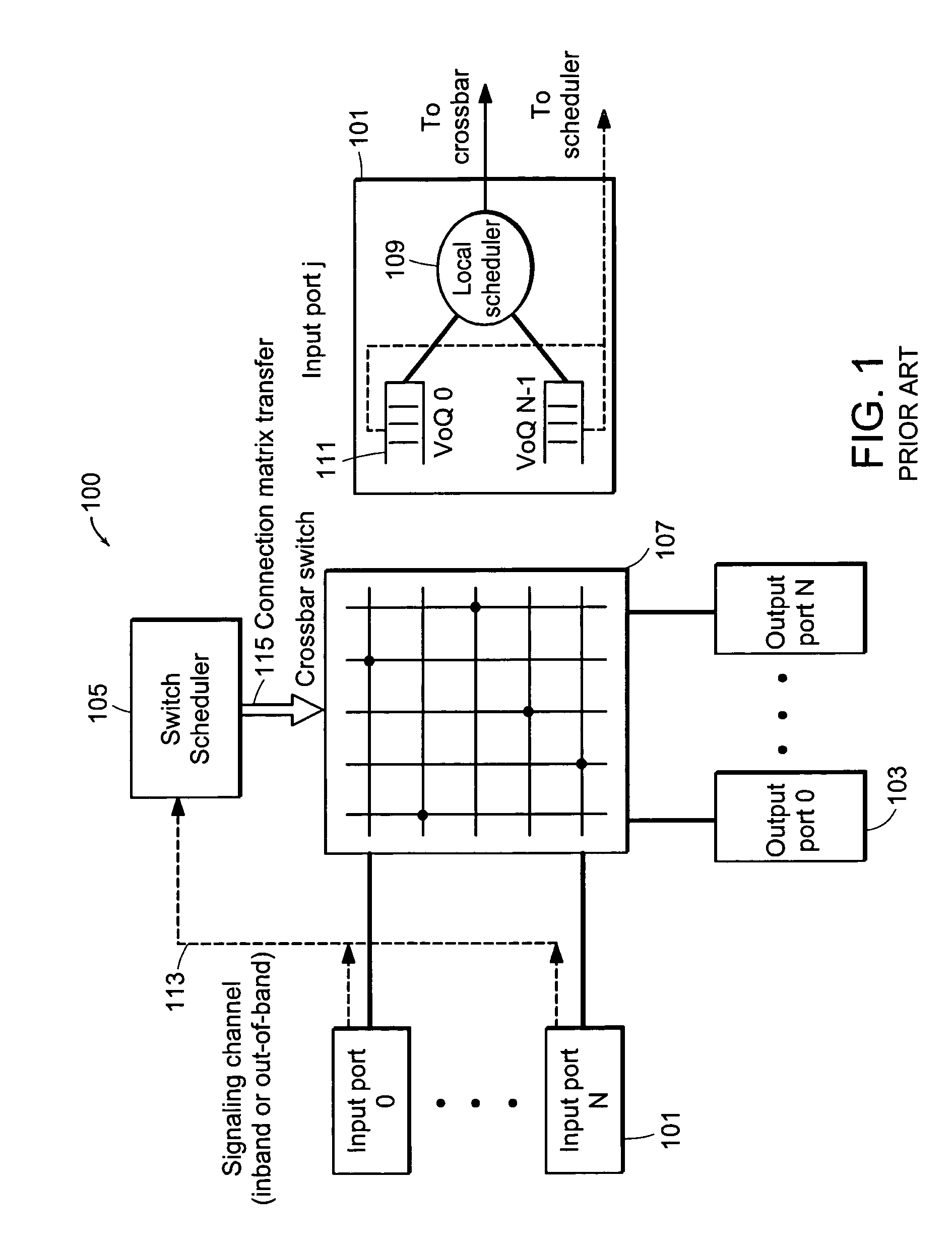

Pseudo-ethernet switch without ethernet media-access-controllers (MAC's) that copies ethernet context registers between PCI-express ports

A Pseudo-Ethernet switch has a routing table that uses Ethernet media-access controller (MAC) addresses to route Ethernet packets through a switch fabric between an input port and an output port. However, the input port and output port have Peripheral Component Interconnect Express (PCIE) interfaces that read and write PCI-Express packets to and from host-processor memories. When used in a blade system, host processor boards have PCIE physical links that connect to the PCIE ports on the Pseudo-Ethernet switch. The Pseudo-Ethernet switch does not have Ethernet MAC and Ethernet physical layers, saving considerable hardware. The switch fabric can be a cross-bar switch or can be a shared memory that stores Ethernet packet data embedded in the PCIE packets. Write and read pointers for a buffer storing an Ethernet packet in the shared memory can be passed from input to output port to perform packet switching.

Owner:DIODES INC

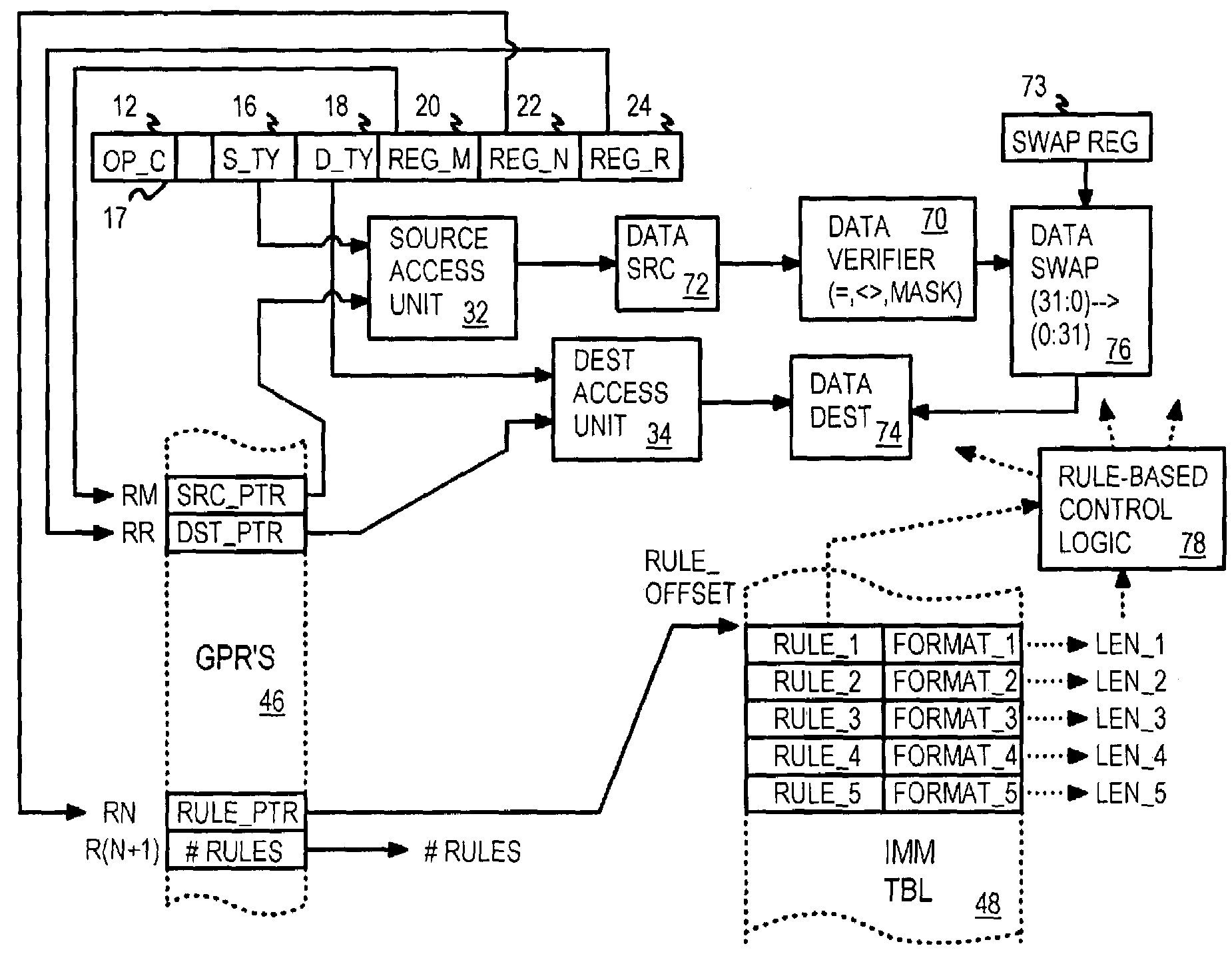

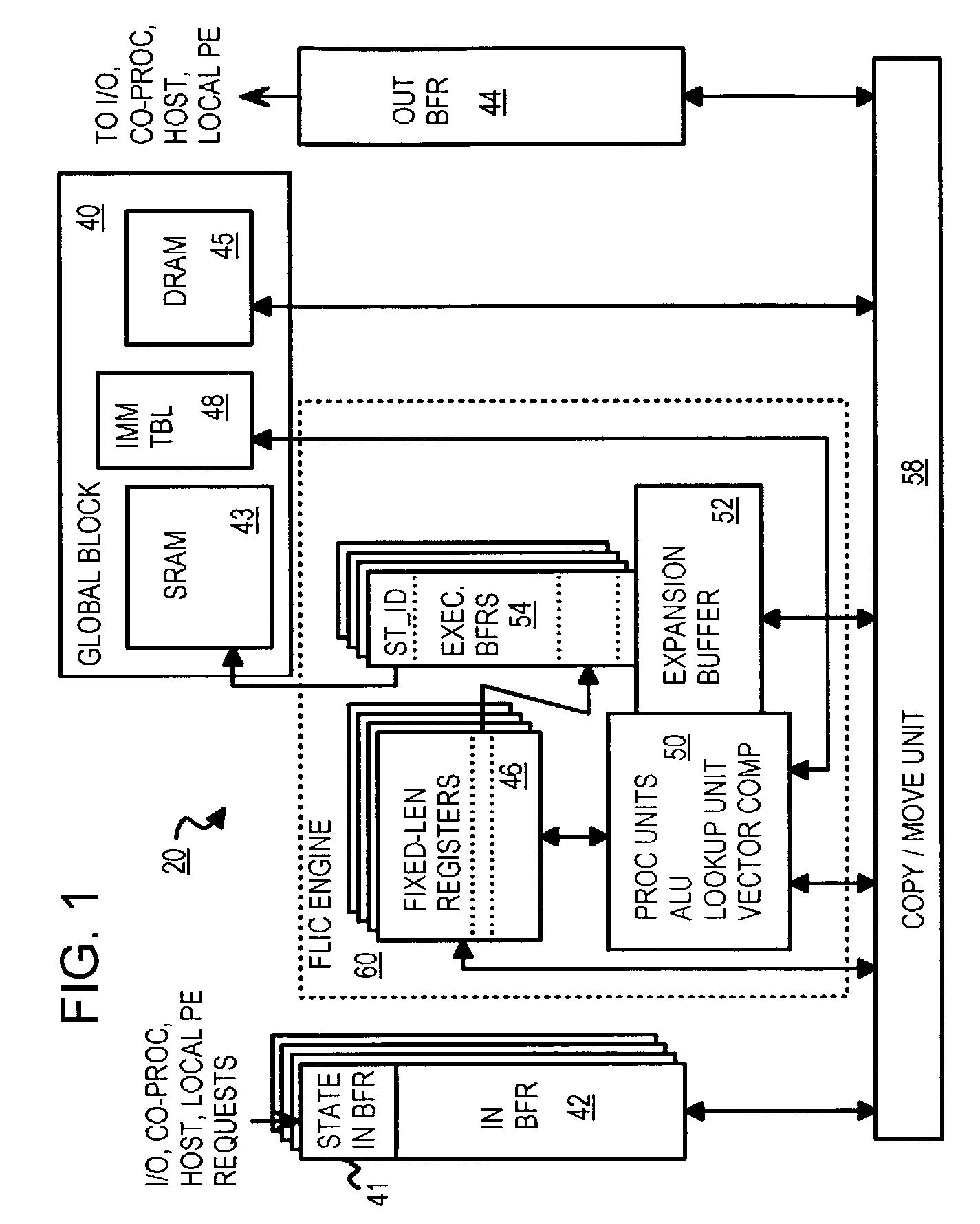

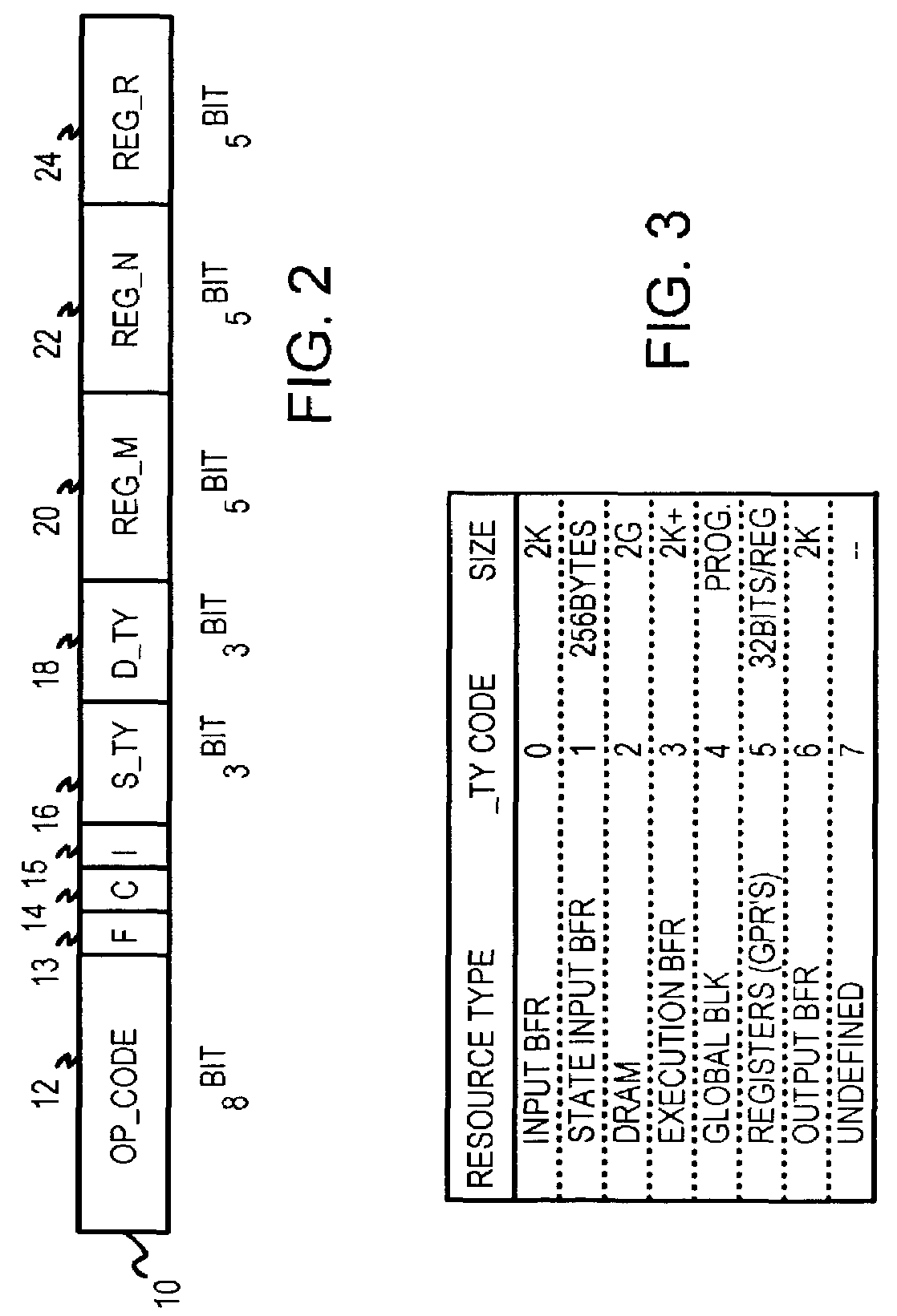

Native copy instruction for file-access processor with copy-rule-based validation

InactiveUS7191318B2Digital computer detailsSpecific program execution arrangementsCrossbar switchGeneral purpose

A copy instruction executed by a functional-level instruction-set computing (FLIC) processor copies a variable-length data block from one resource to another resource through a cross-bar switch. Resources include general-purpose registers, input, output, and execution buffers, DRAM, SRAM, and other memory. A copy-with-validate instruction has an operand pointing to a first rule in an immediate rule table. The first rule controls validation of a first data-item in the data being copied. Validation includes range and equality checking of the data-item. The value of the data-item or the current offset can be written to a register. A format field in the rule indicates the size of the data-item, or the size is read from the data-item for variable-size formats. The current offset is incremented by the size. The next data-item is validated by a next rule, and other rules in the immediate table control validation of other data-items in the data block.

Owner:RPX CORP

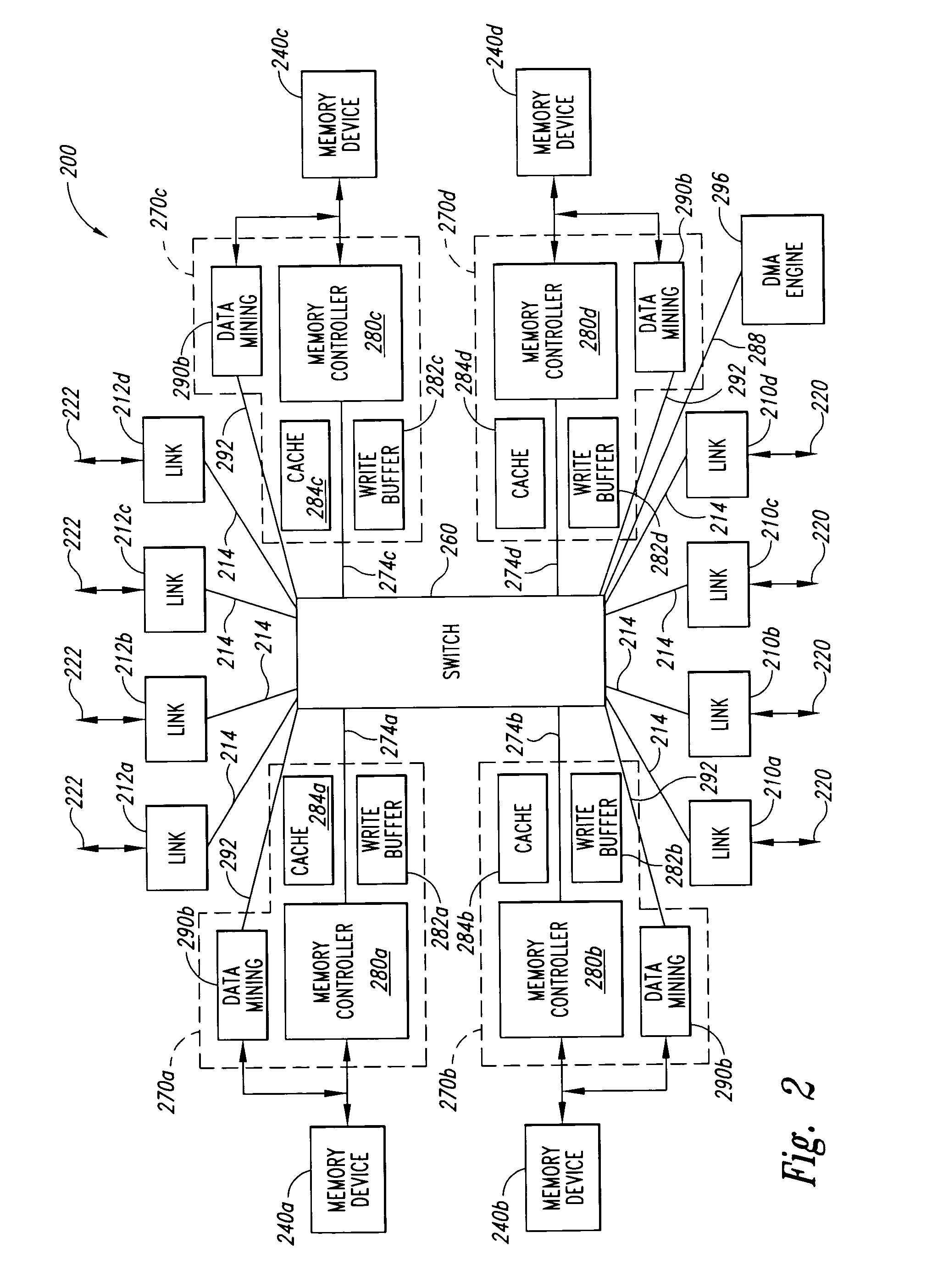

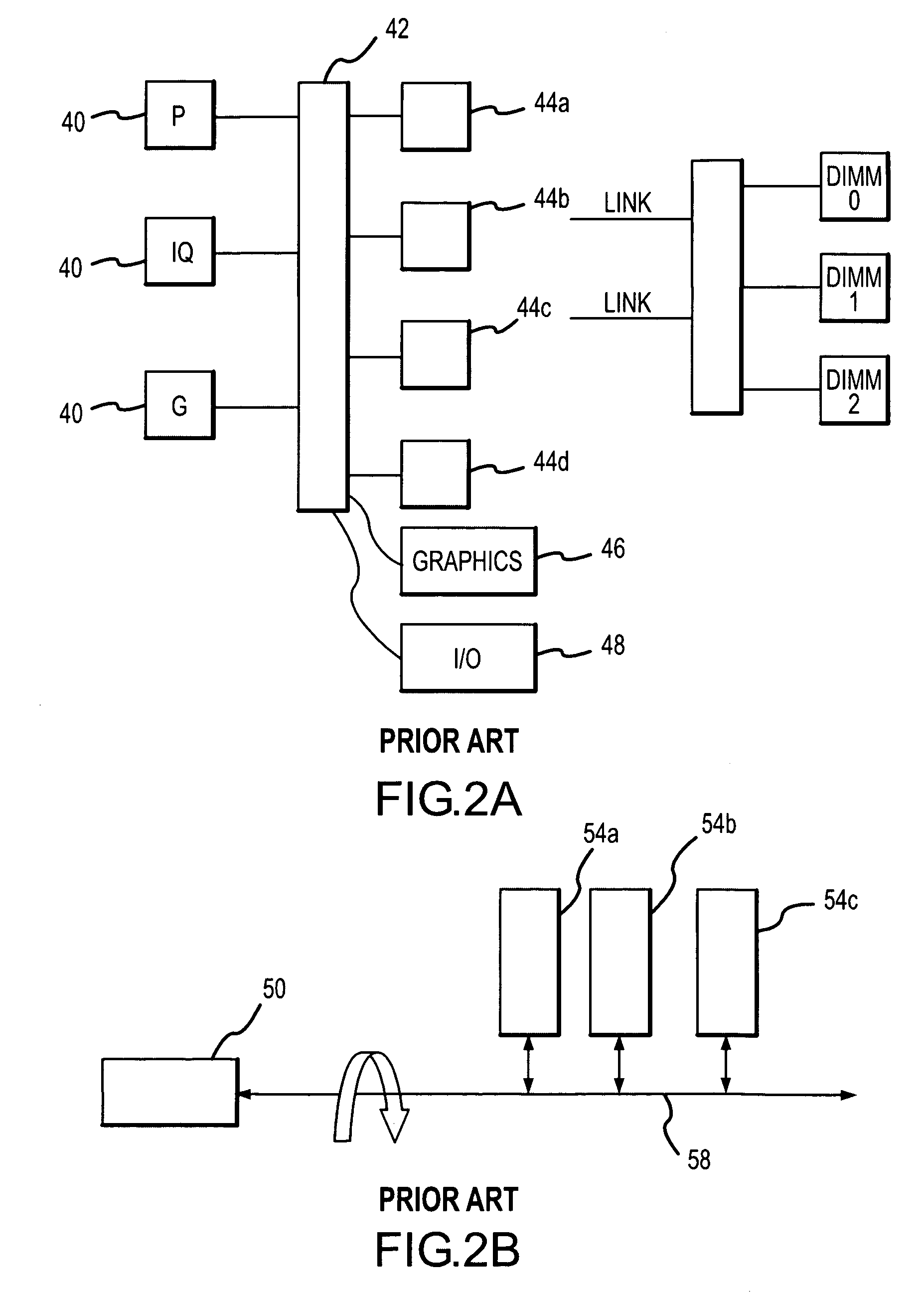

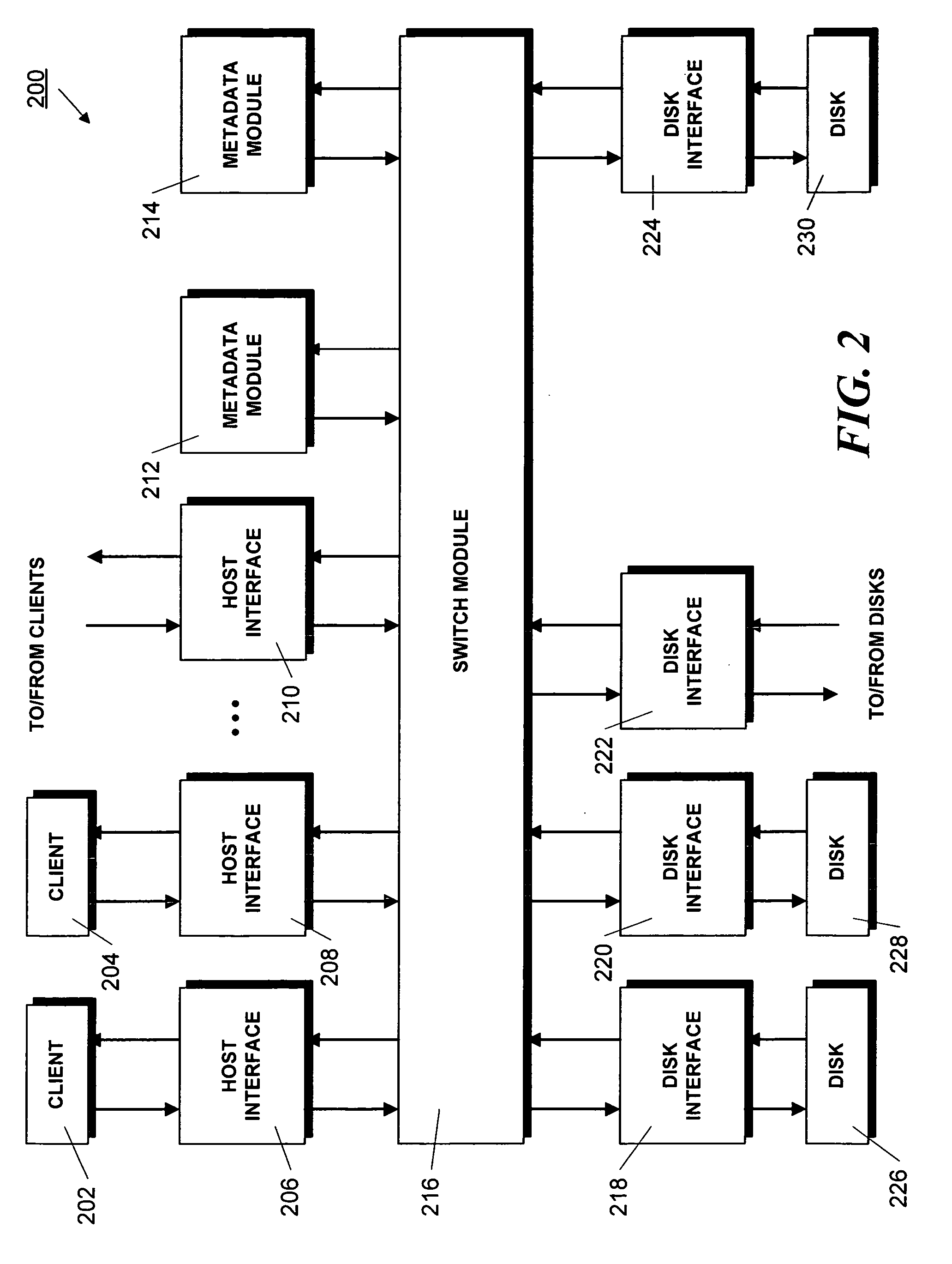

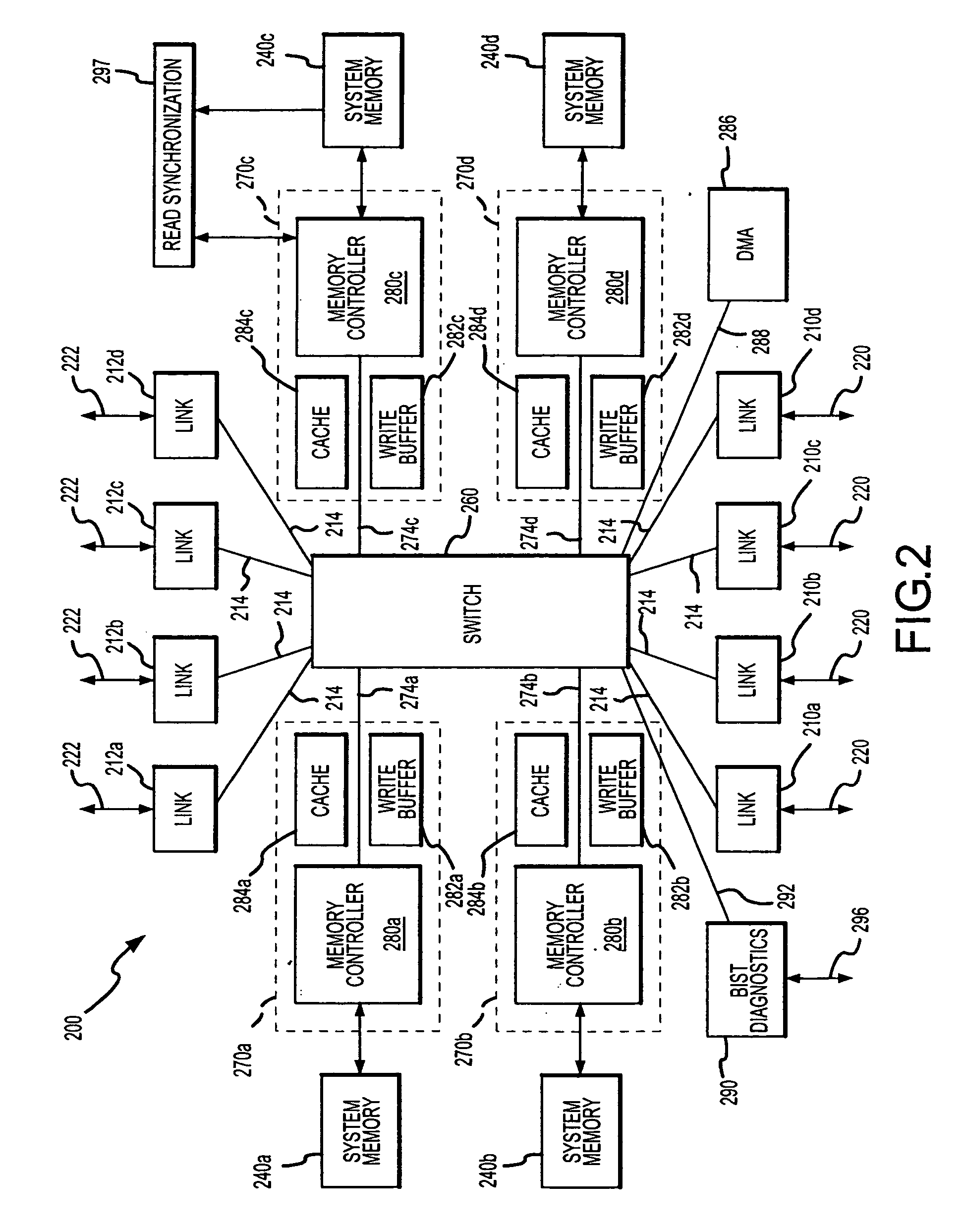

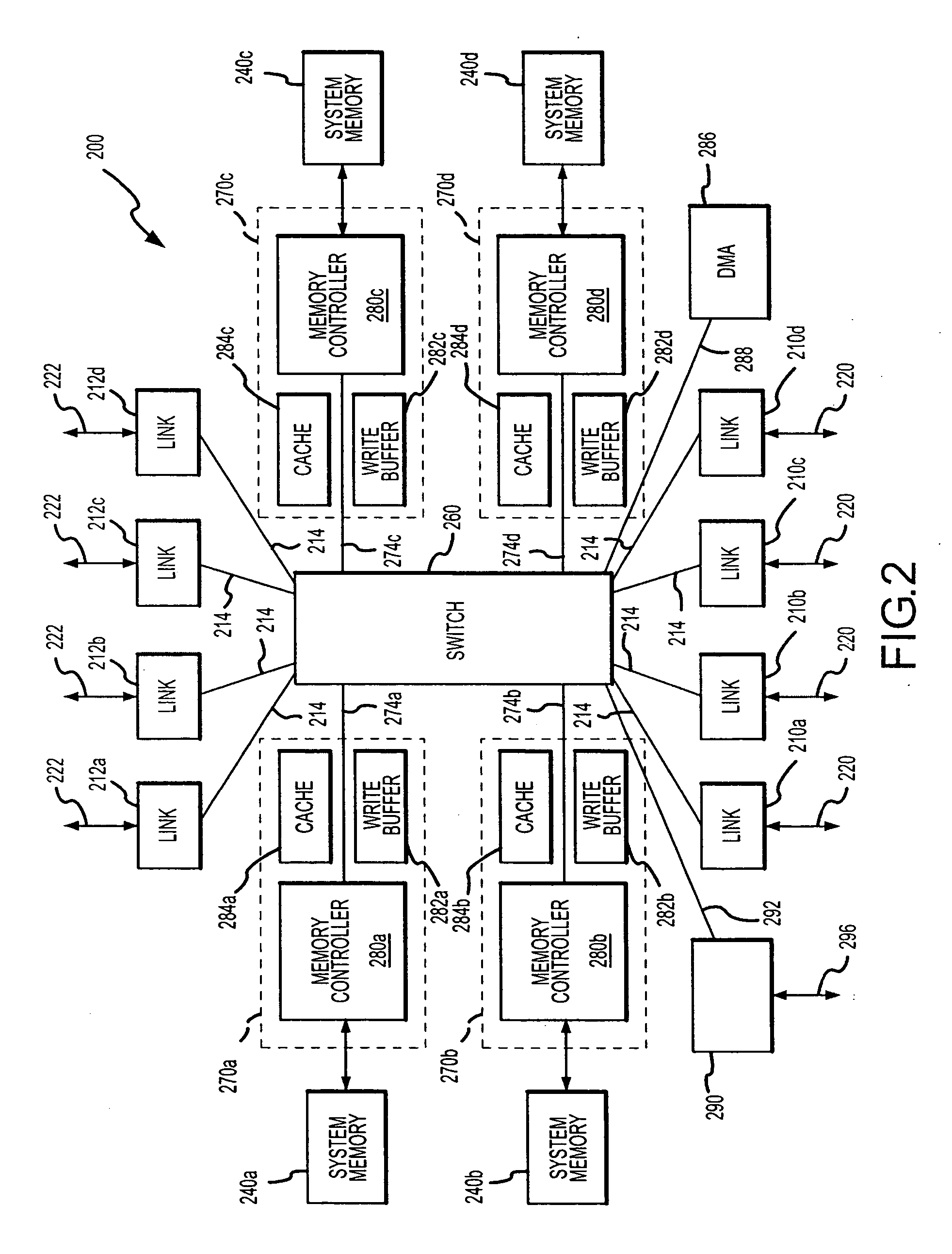

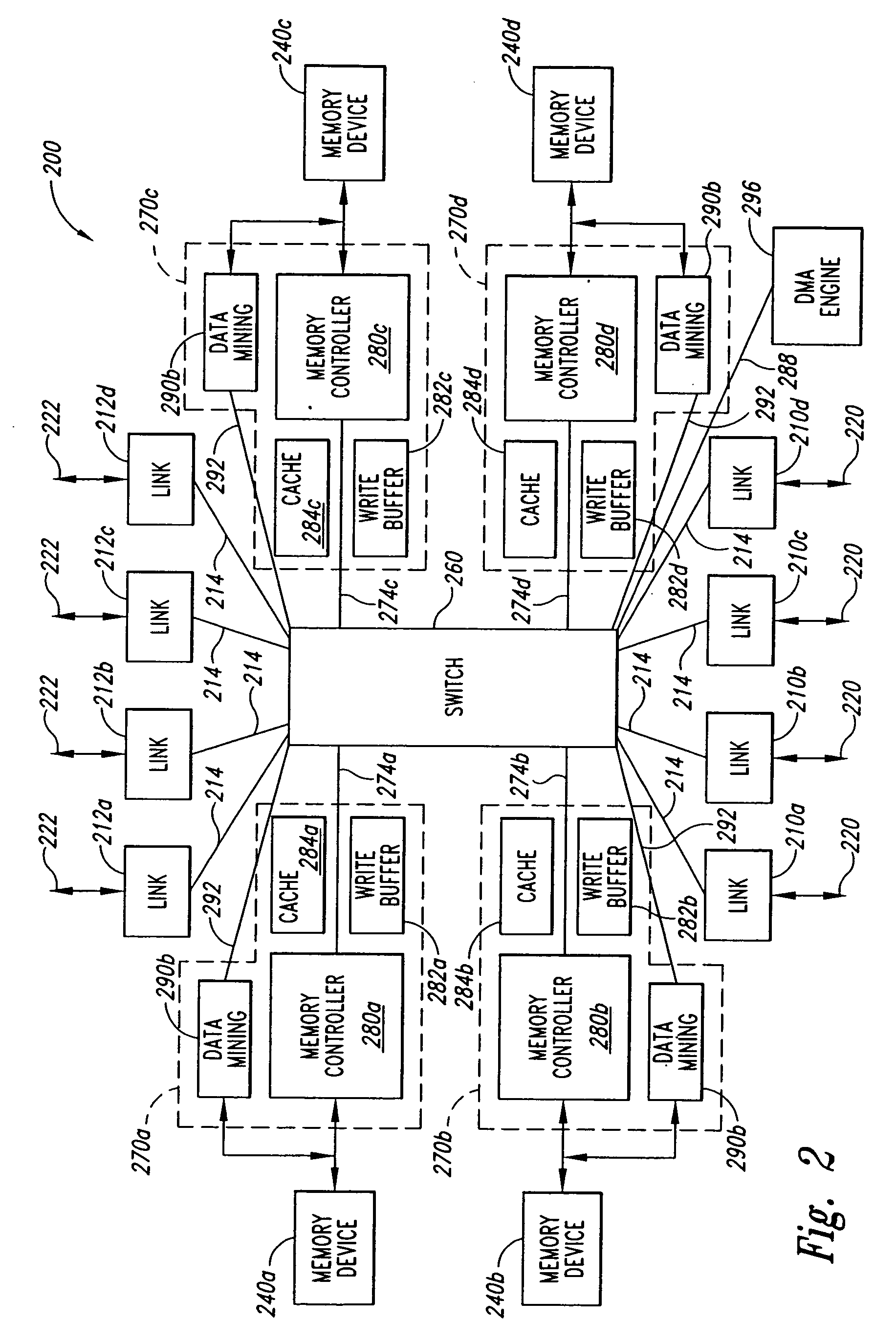

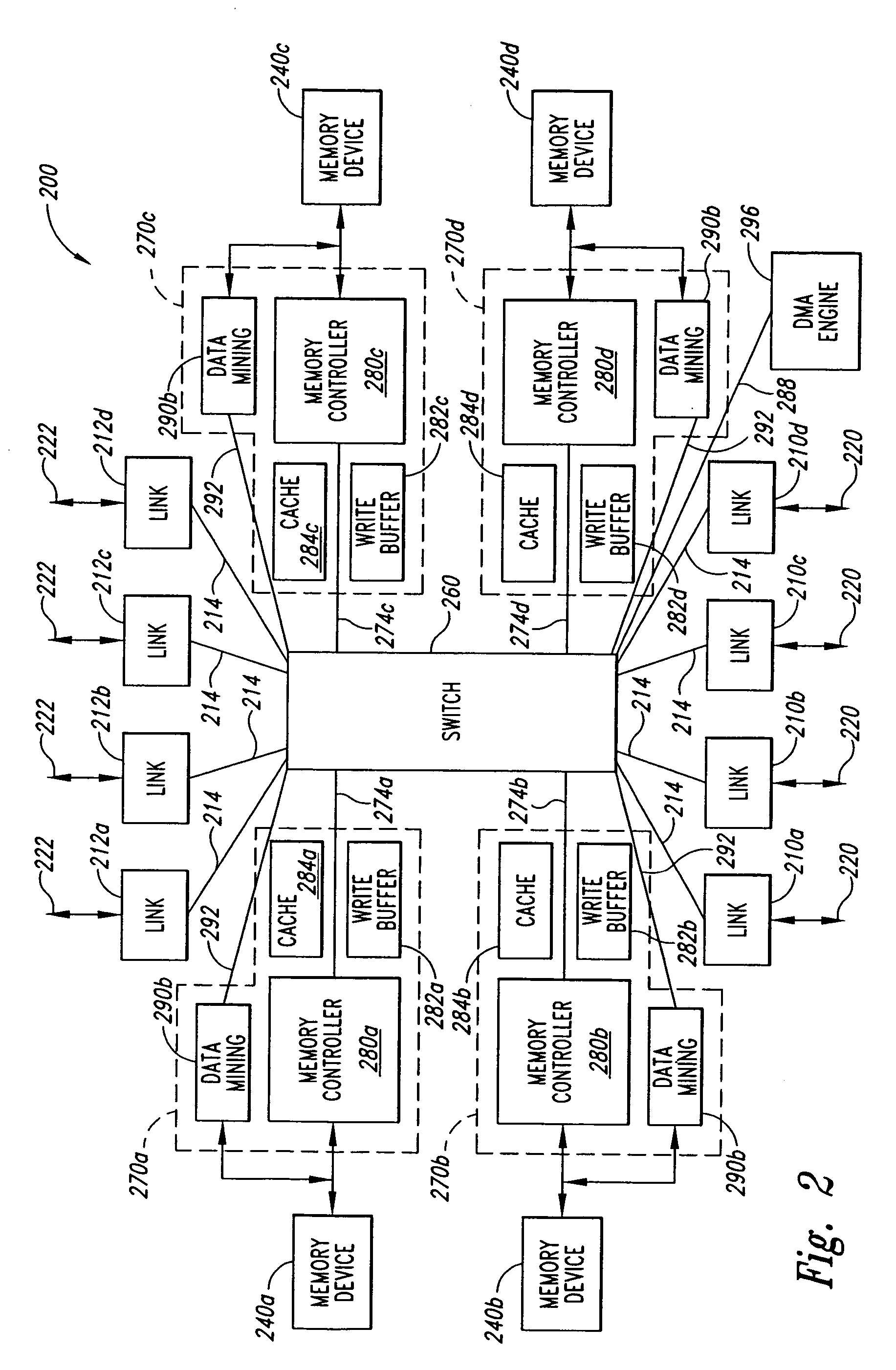

Memory module and method having on-board data search capabilities and processor-based system using such memory modules

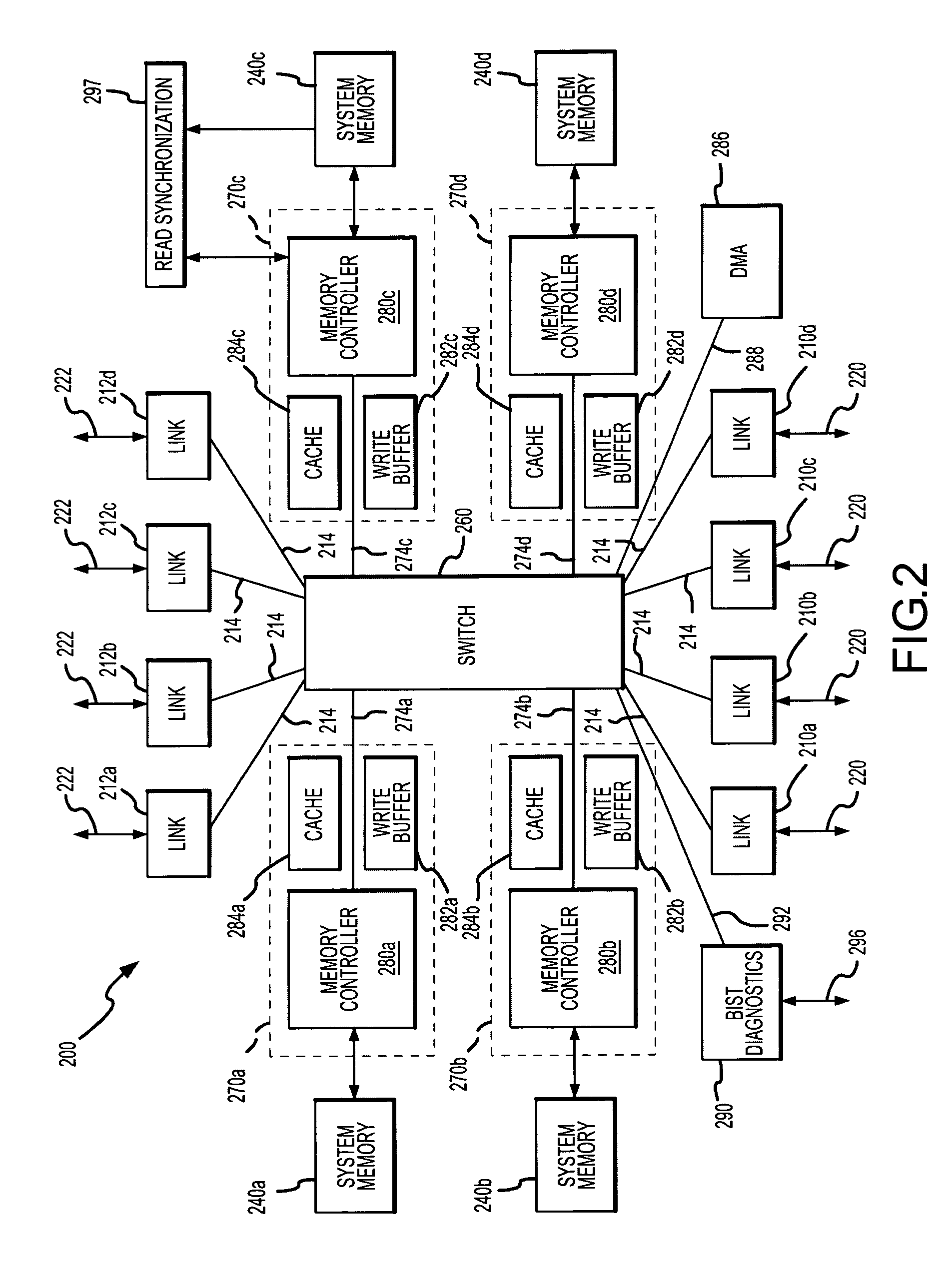

InactiveUS20050050237A1Faster rateDigital data information retrievalStatic storageCrossbar switchWrite buffer

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory interfaces coupled to respective memory devices, and a cross-bar switch coupling any of the link interfaces to any of the memory interfaces. Each memory interface includes a memory controller, a write buffer, a read cache, and a data mining module. The data mining module includes a search data memory that is coupled to the link interface to receive and store at least one item of search data. A comparator receives both the read data from the memory device and the search data. The comparator then compares the read data to the respective item of search data and provides a hit indication in the event of a match.

Owner:MICRON TECH INC

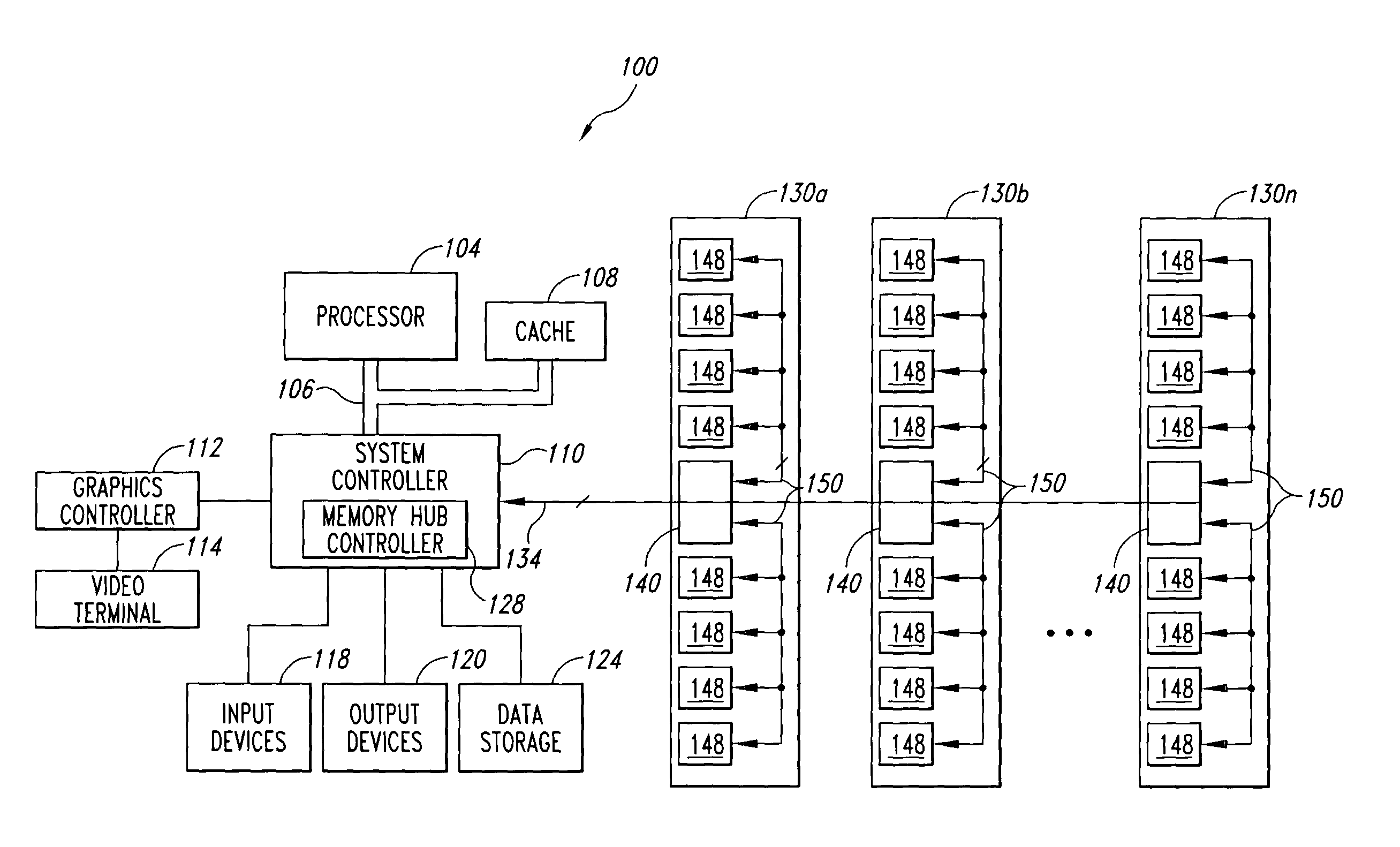

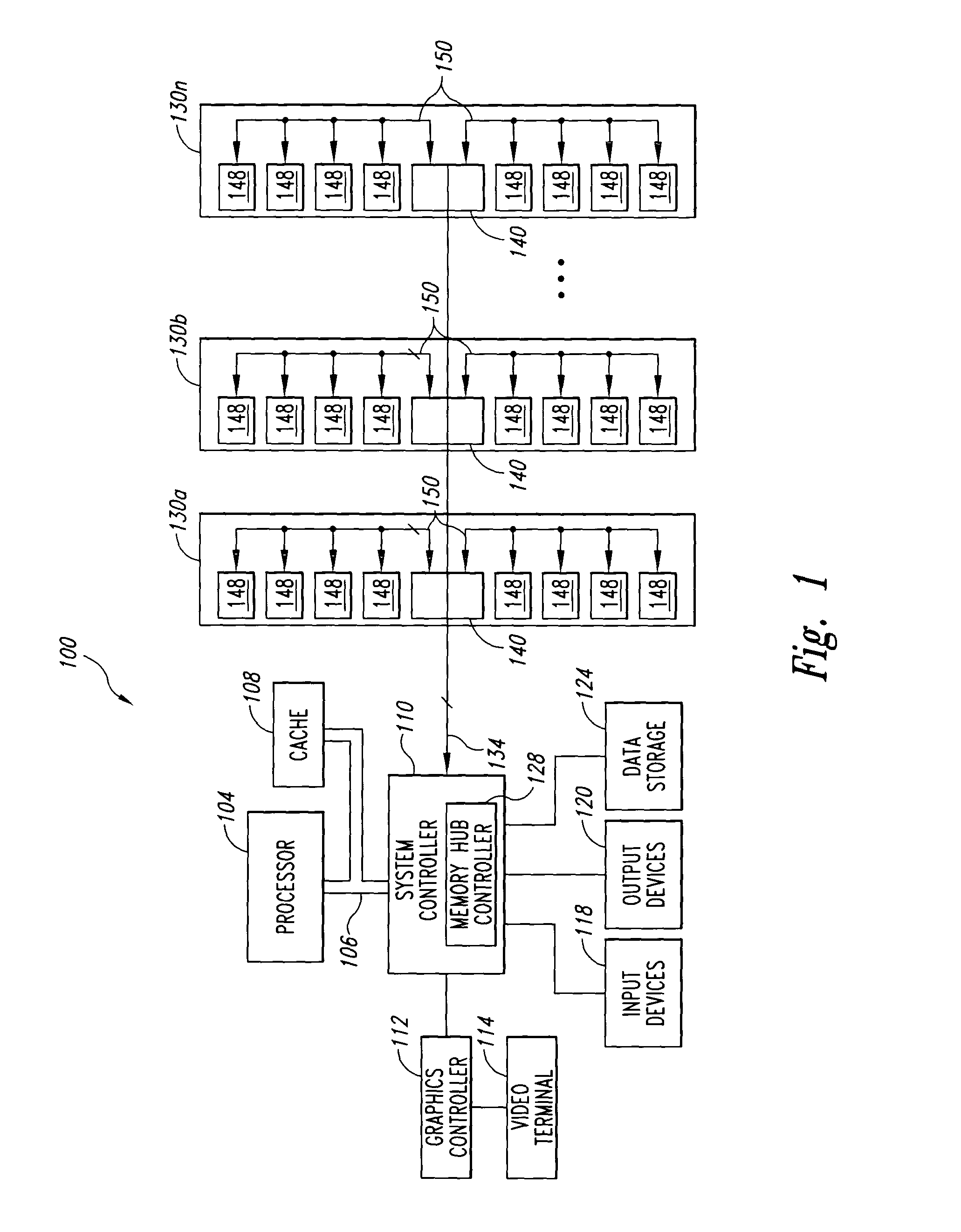

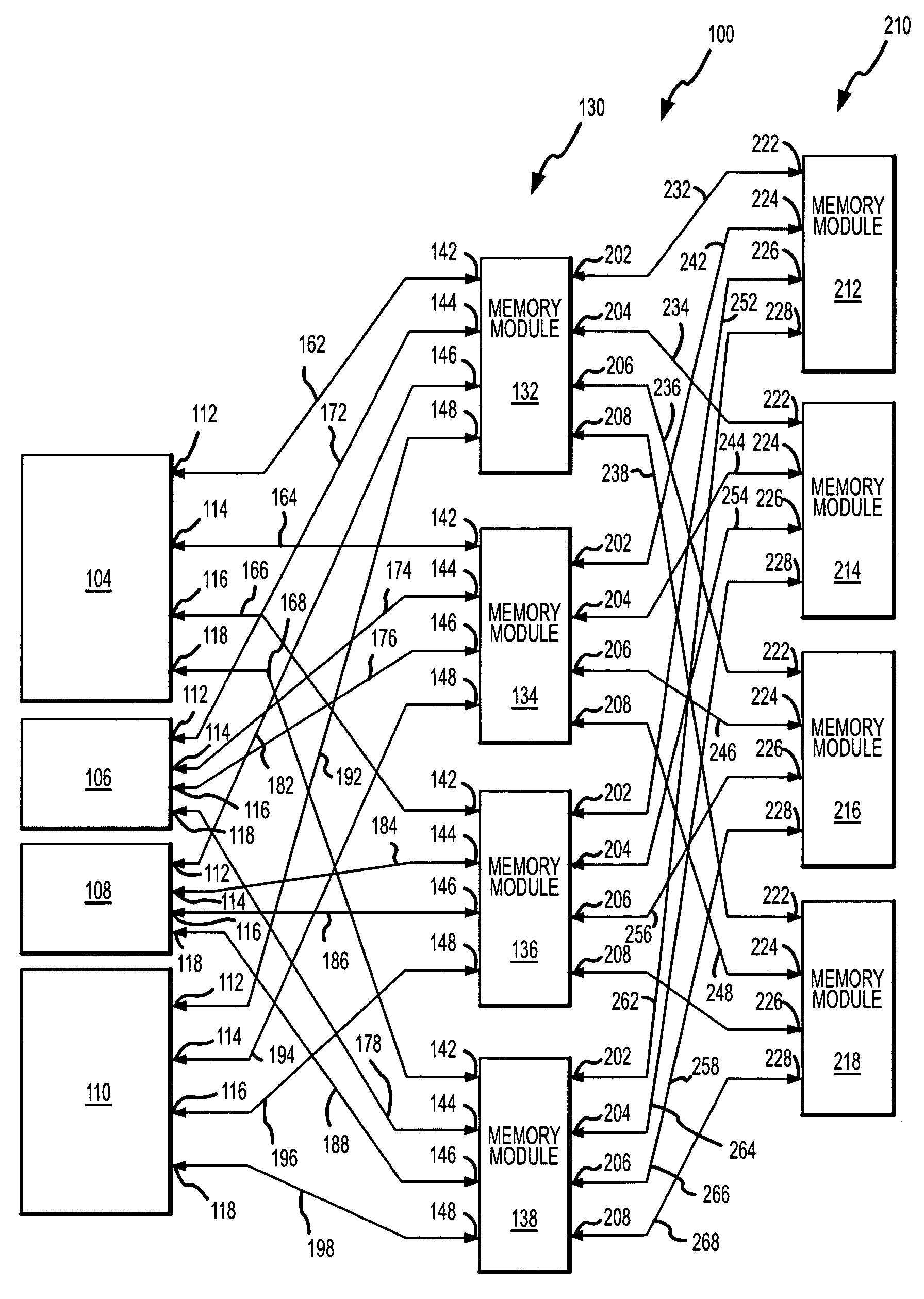

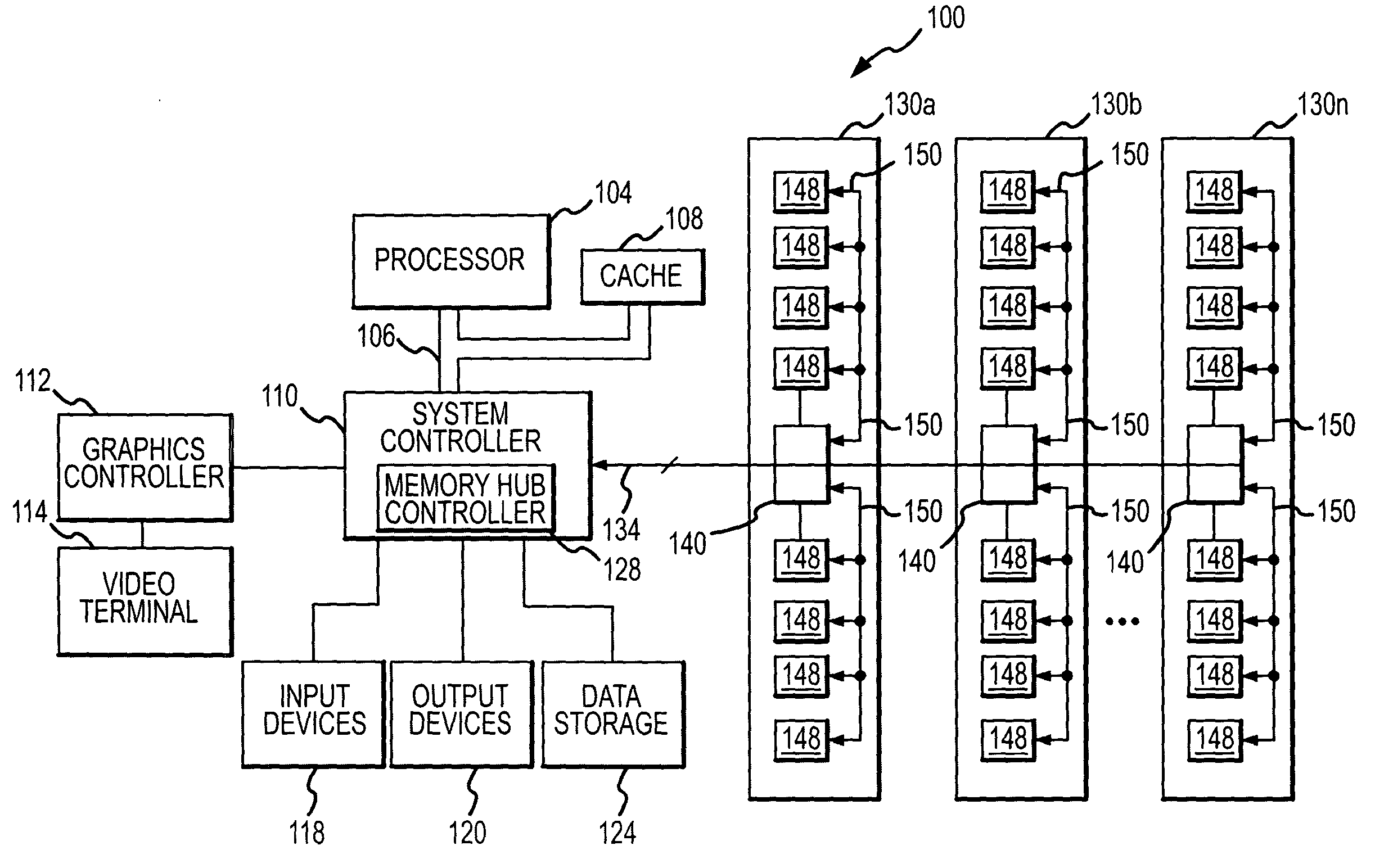

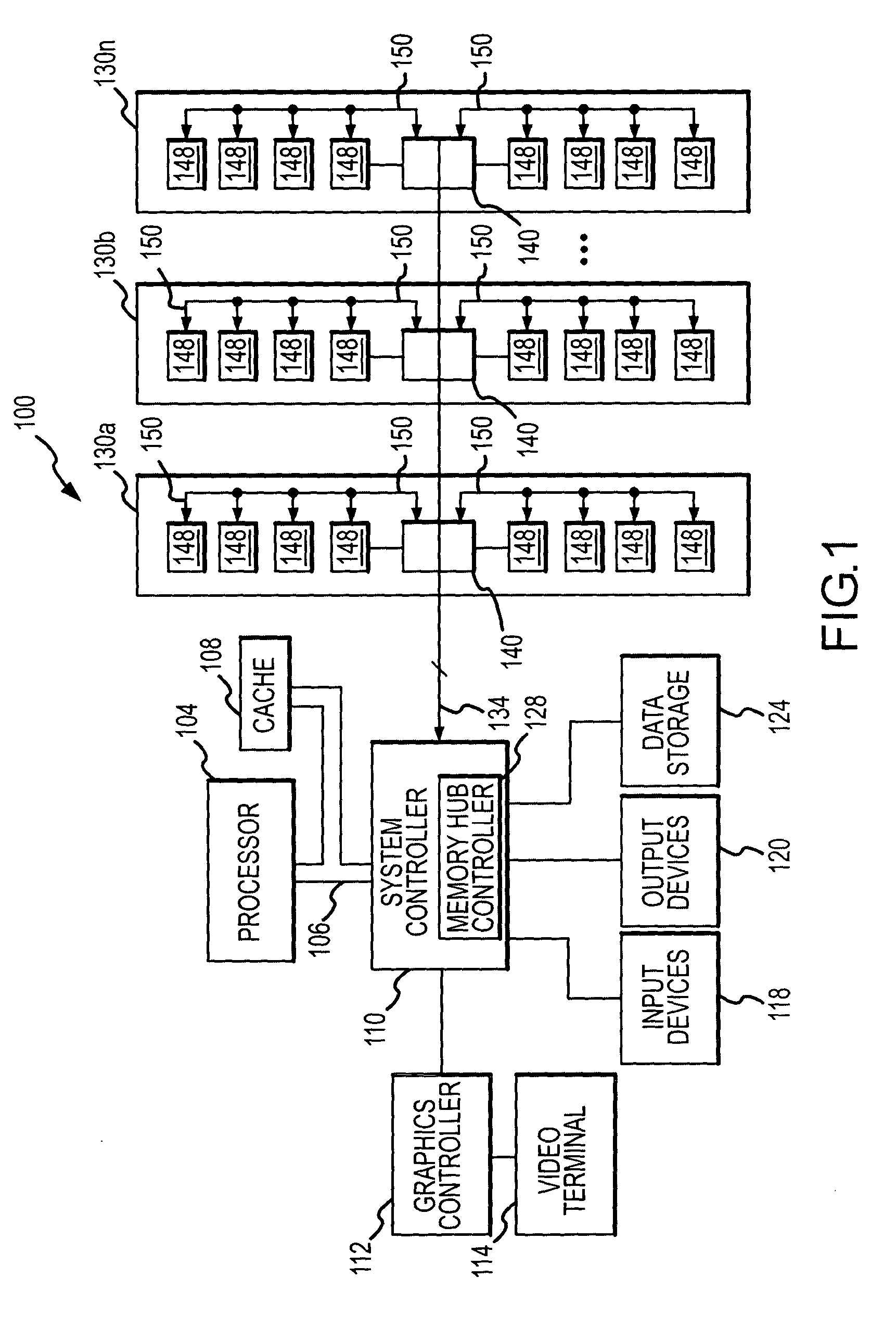

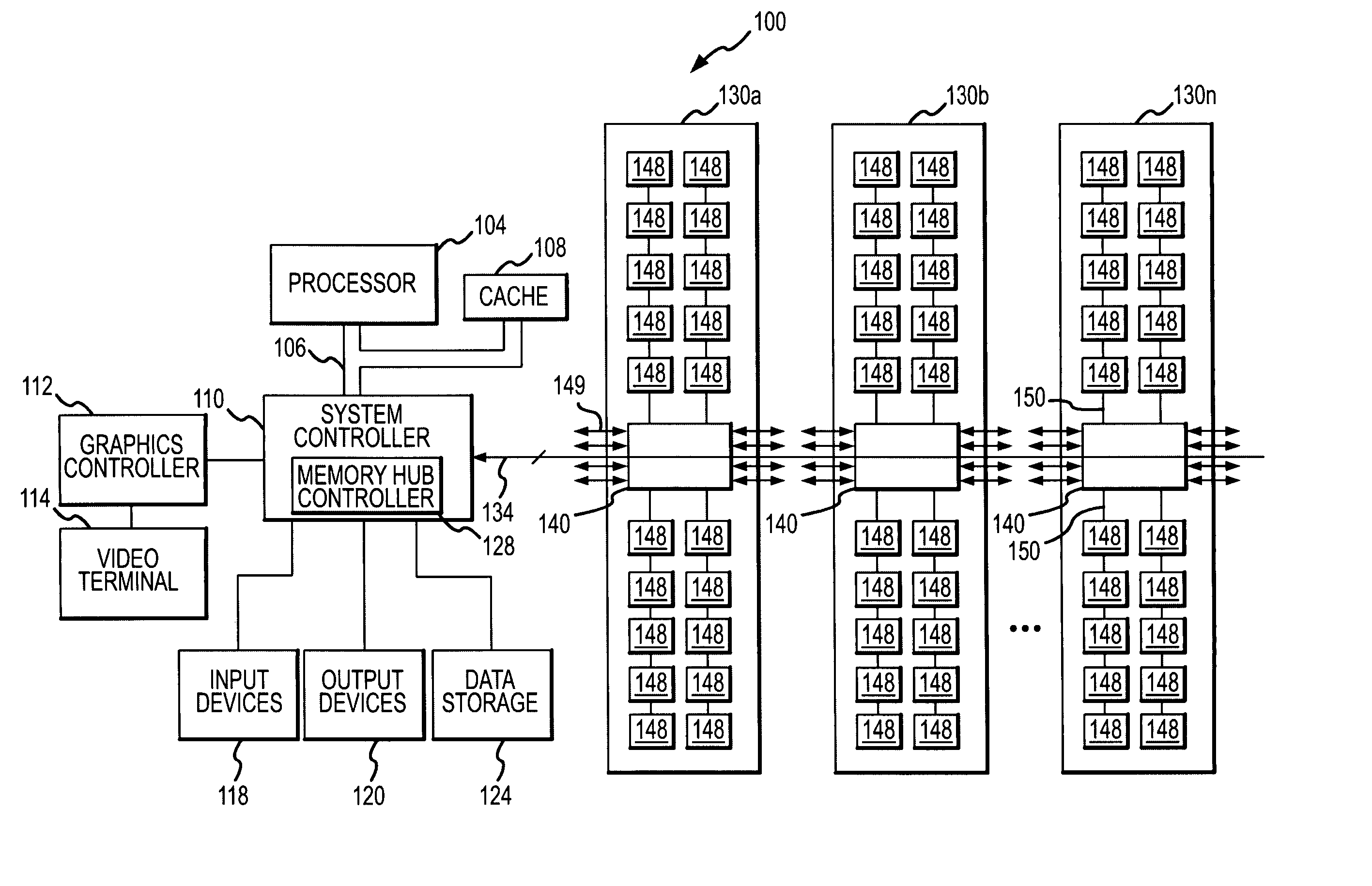

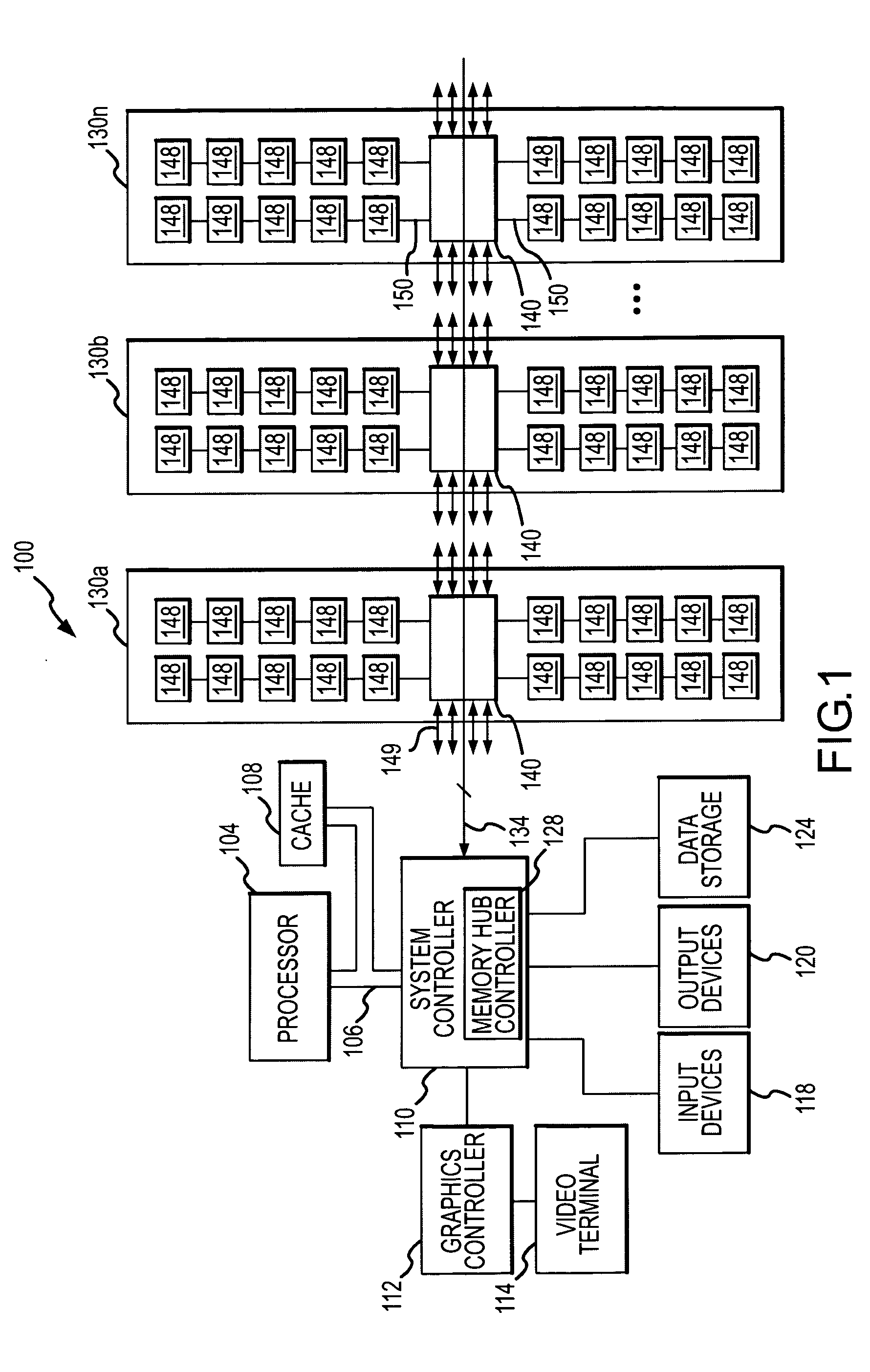

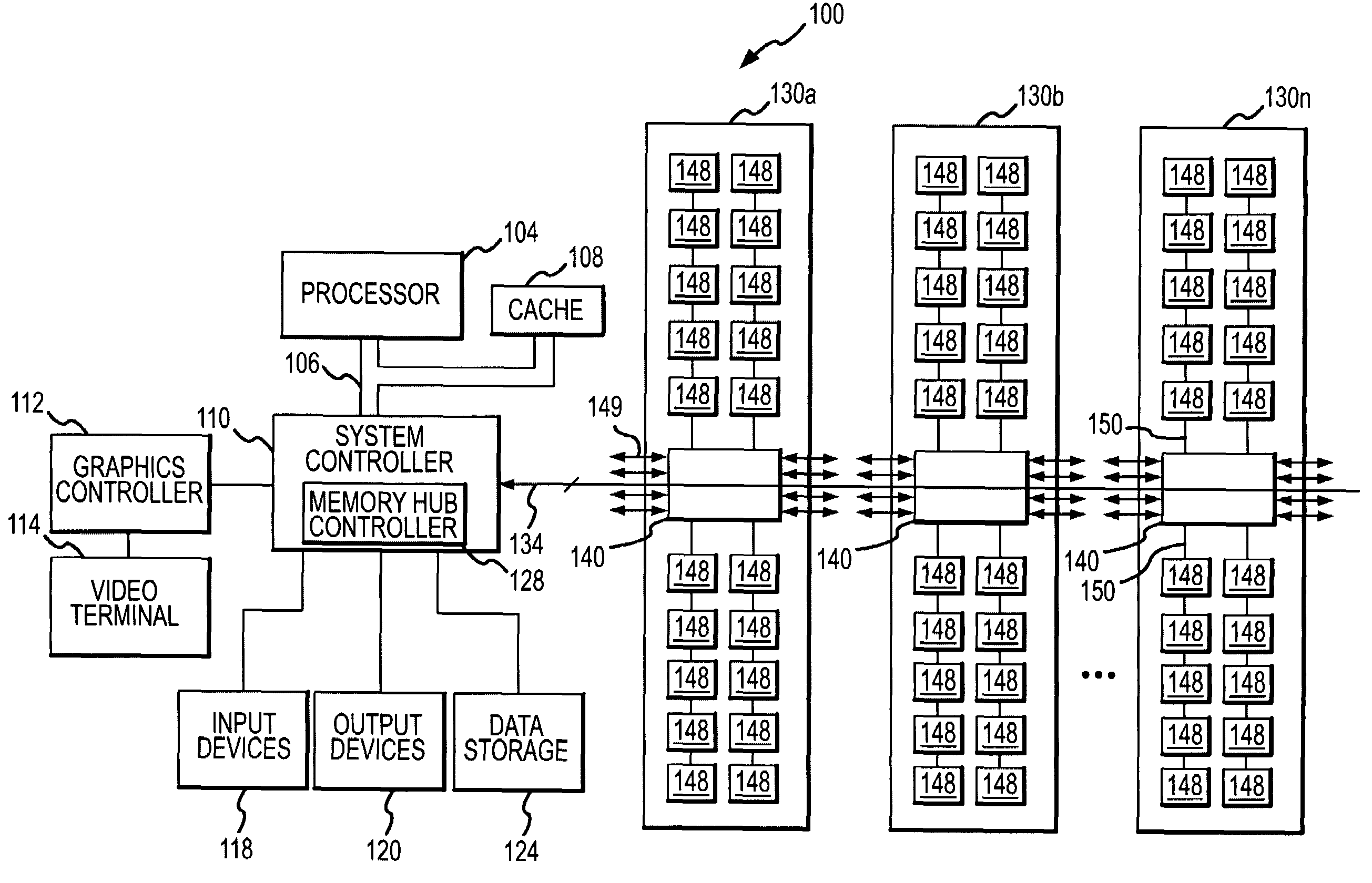

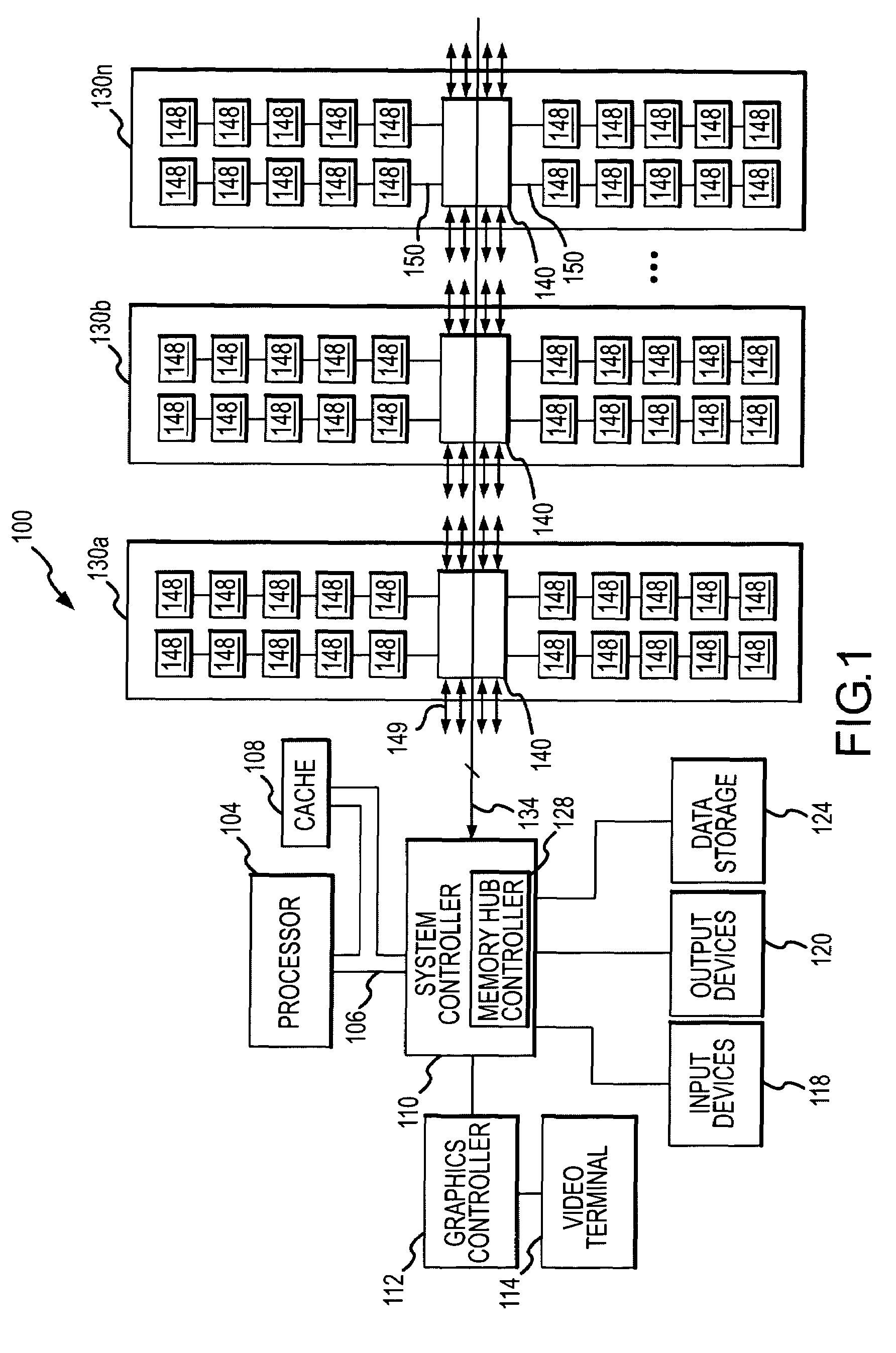

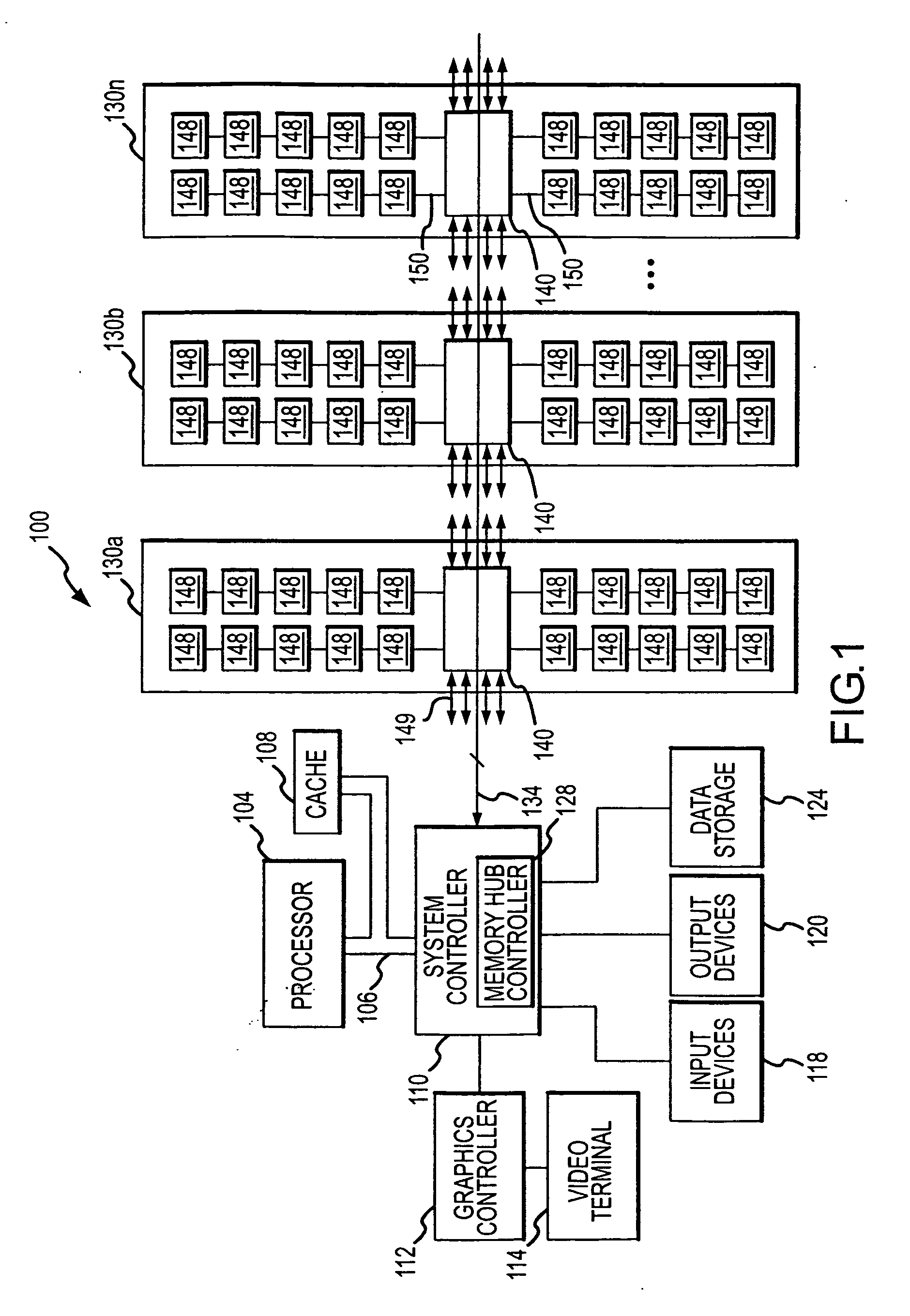

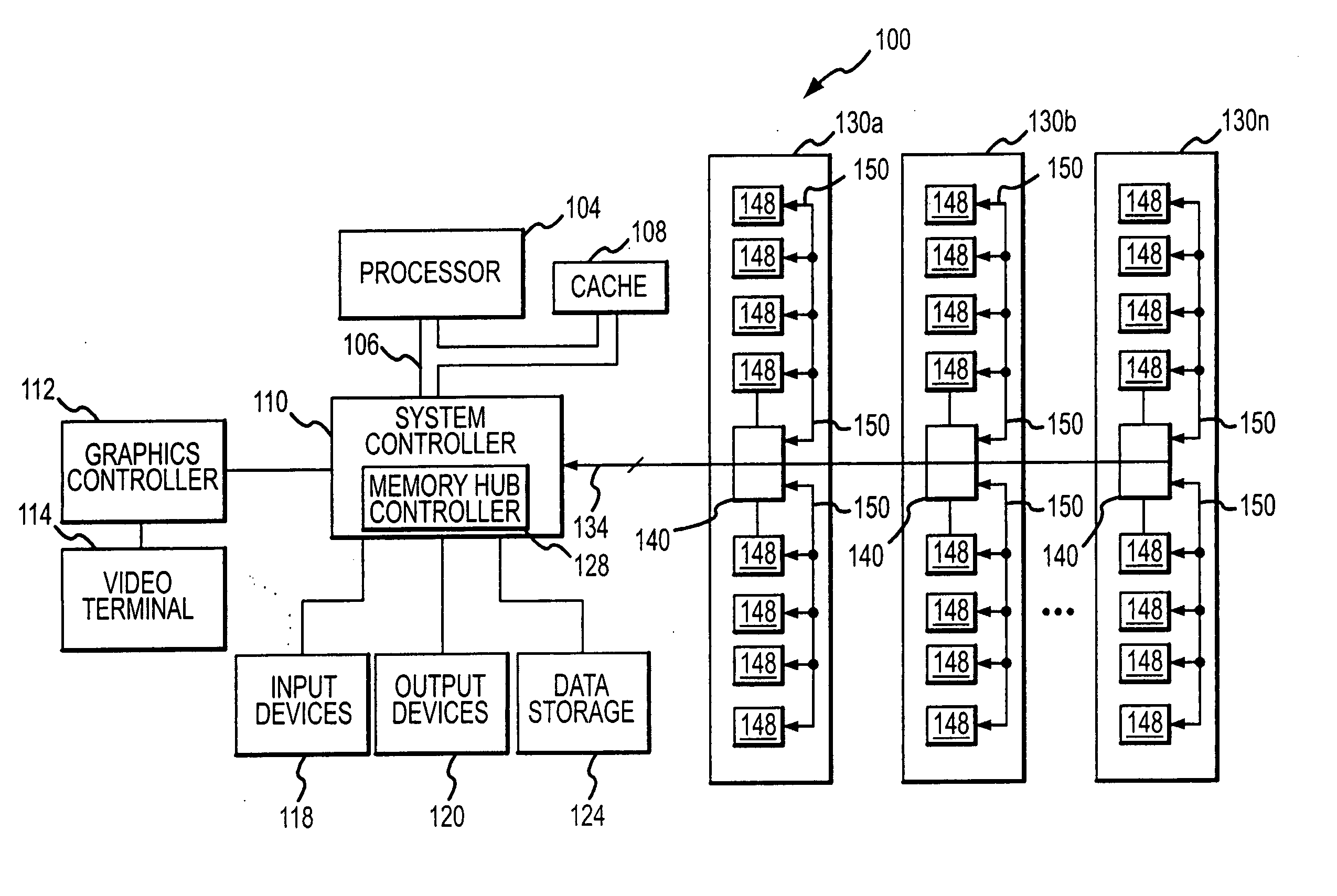

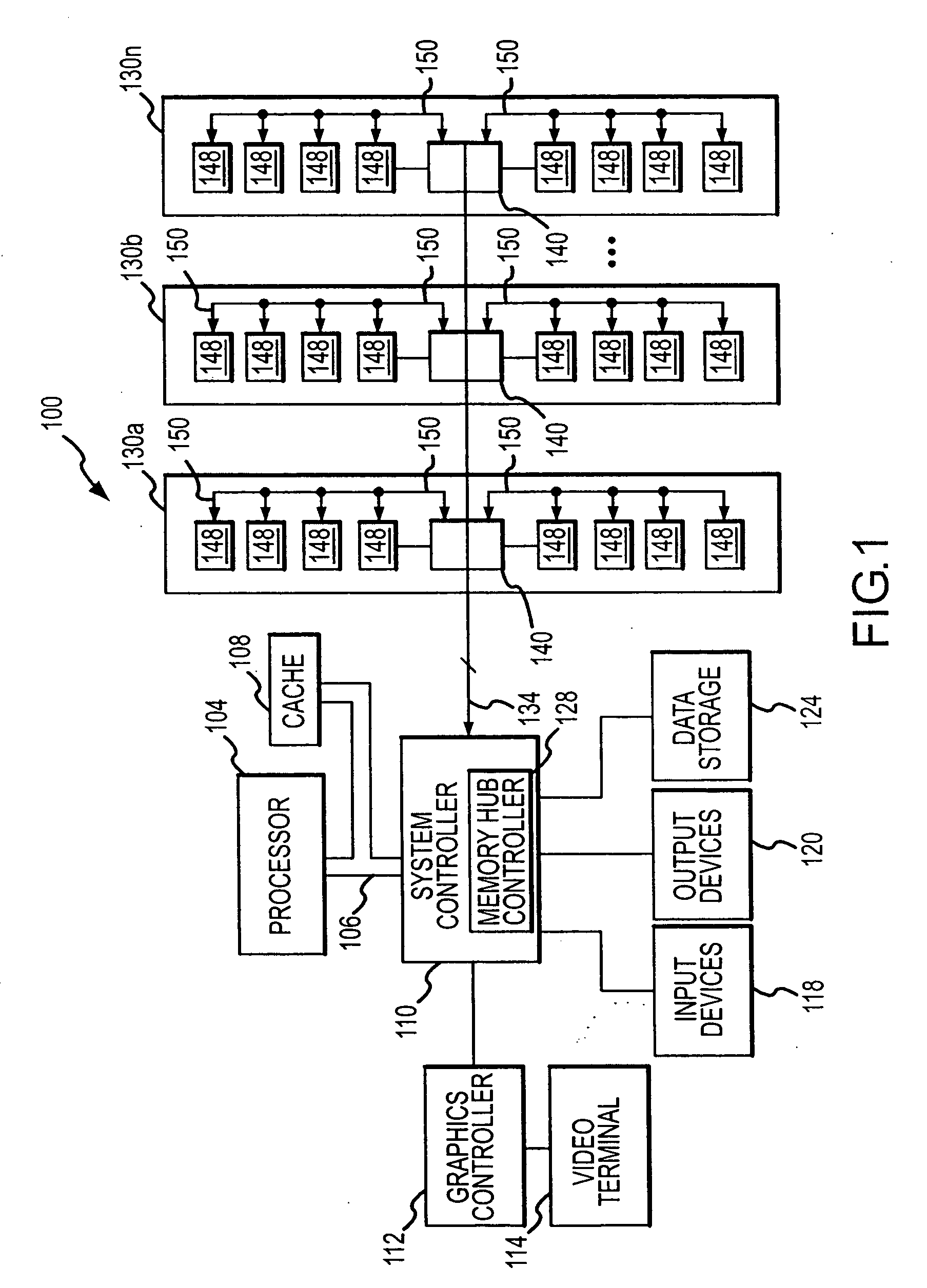

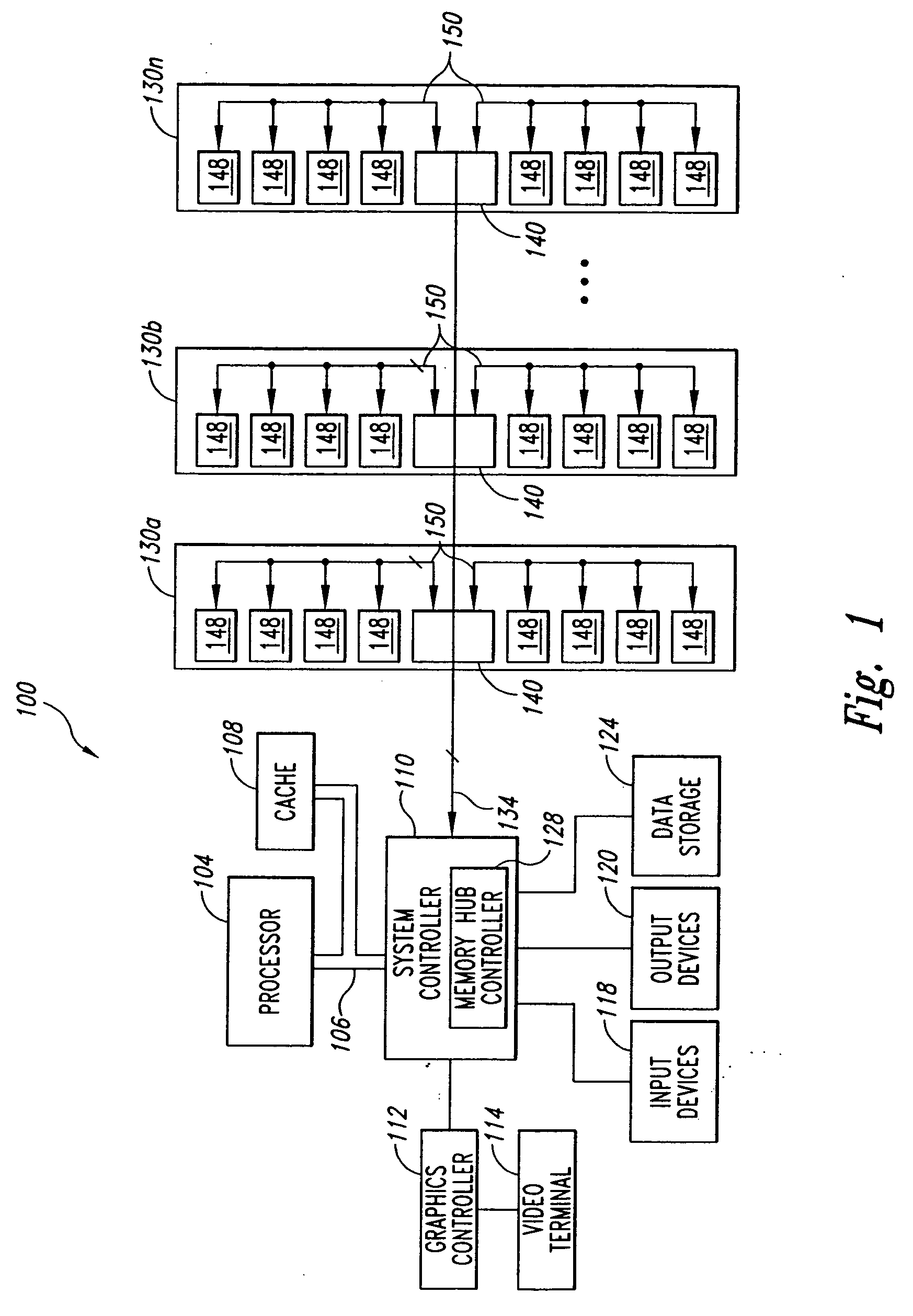

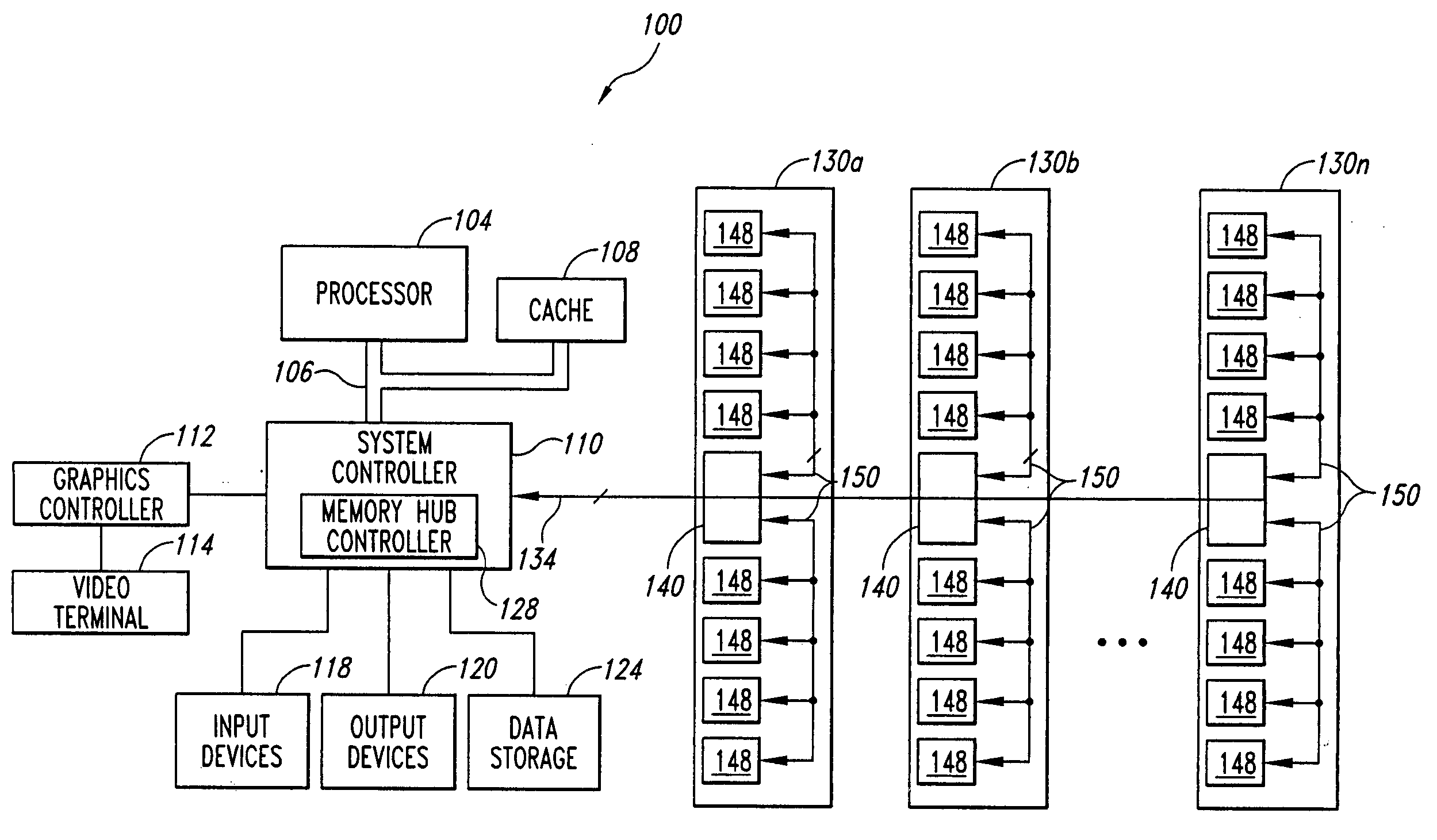

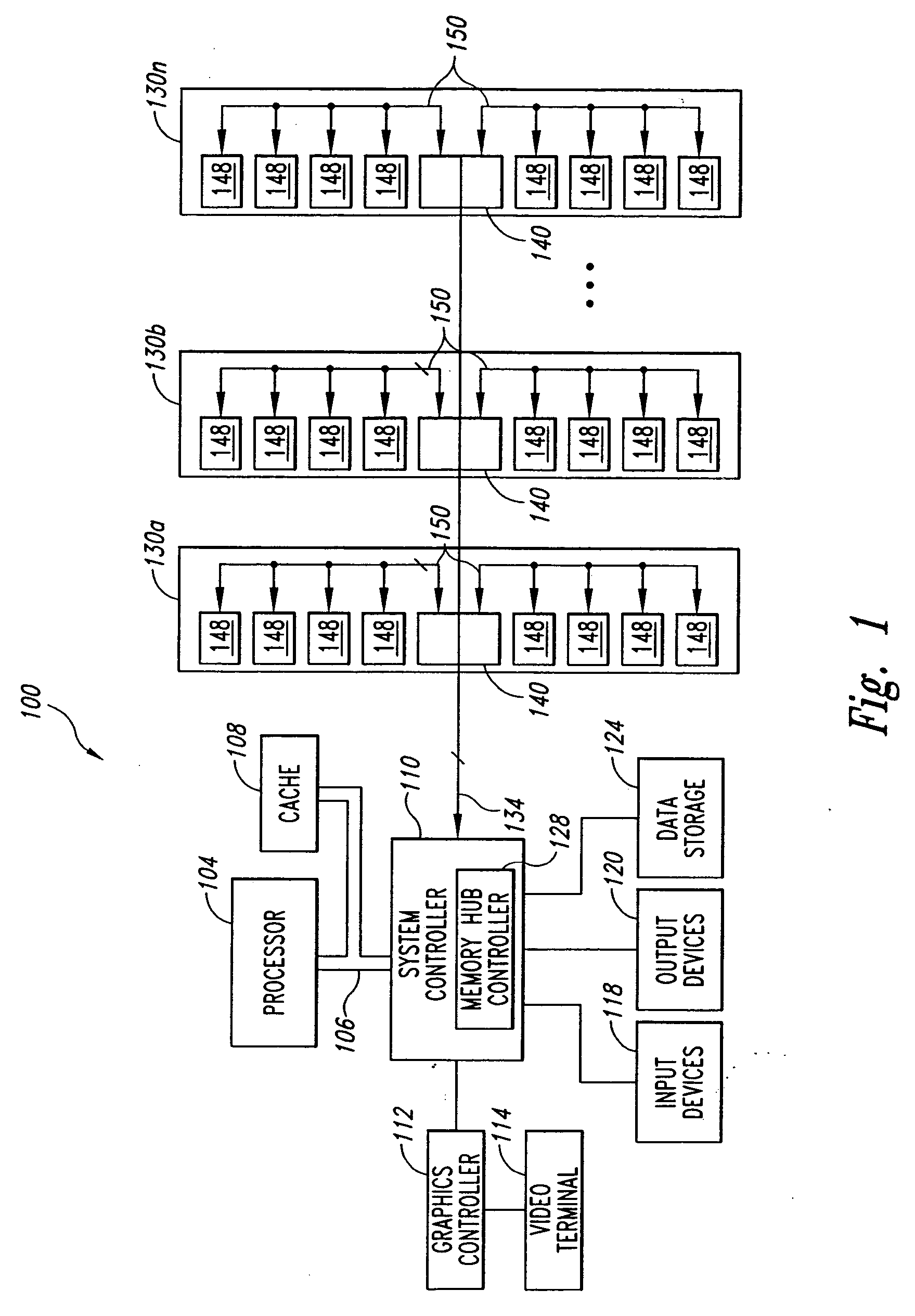

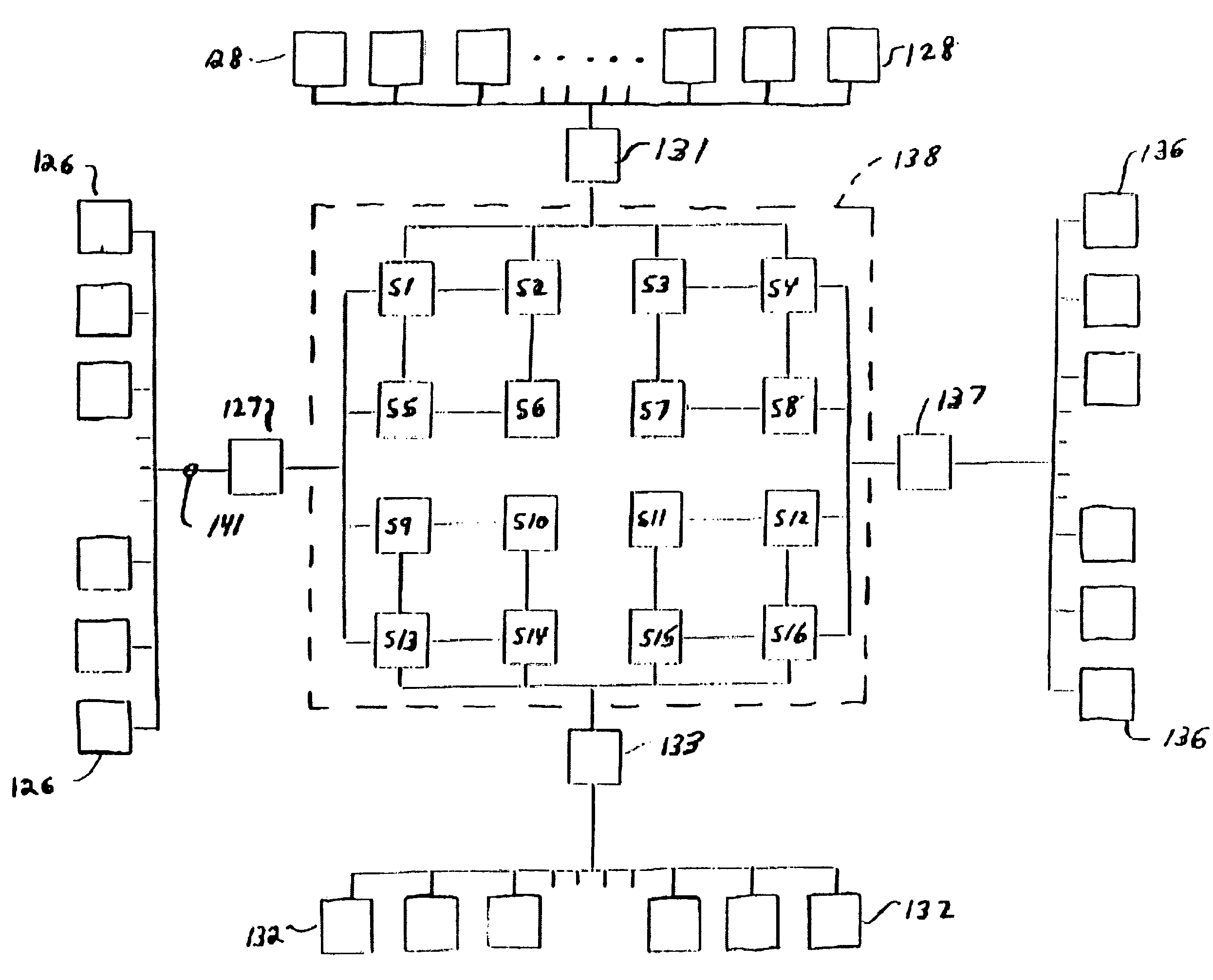

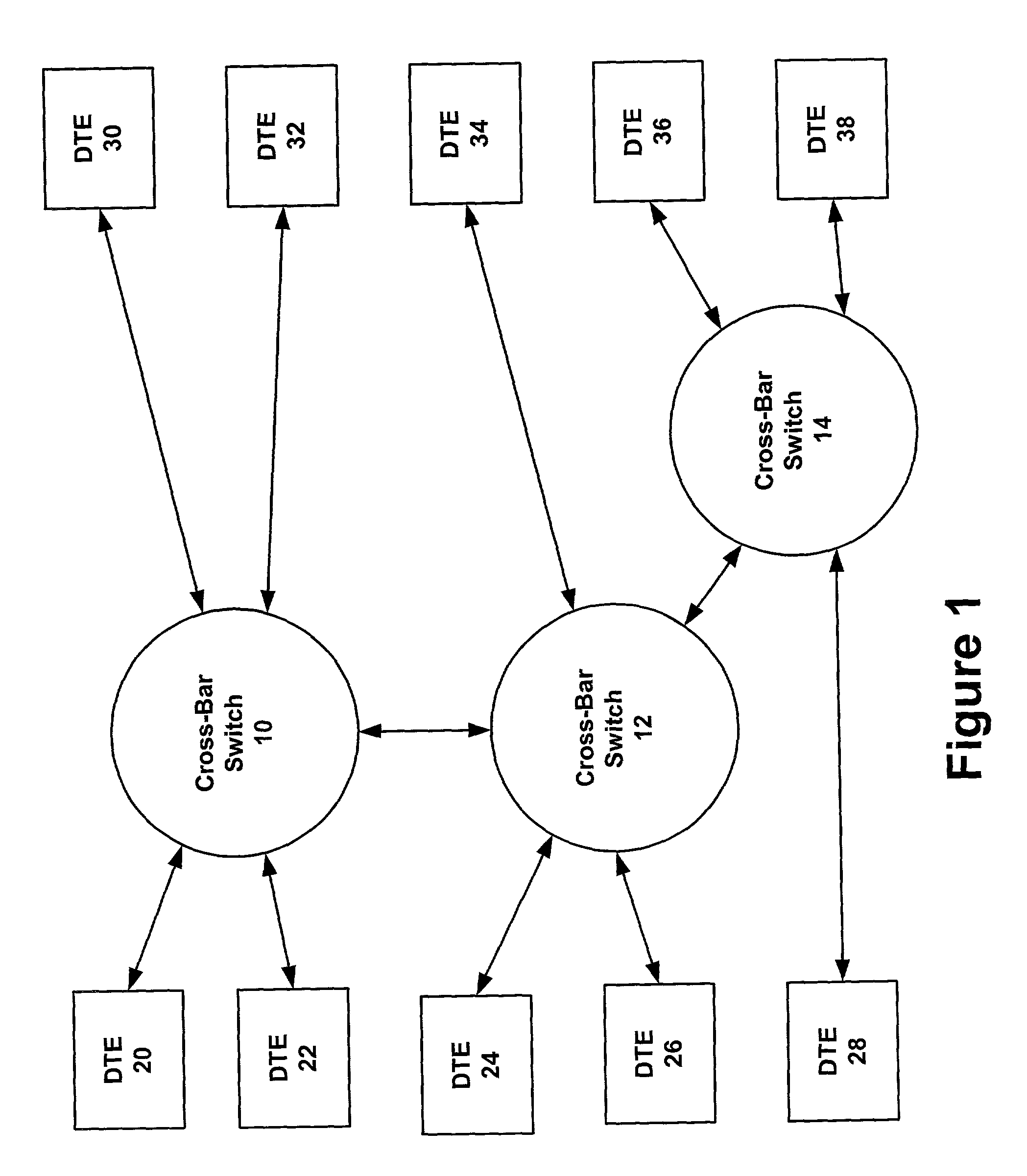

Multiple processor system and method including multiple memory hub modules

InactiveUS7136958B2Low latency memory accessFlexible handlingMemory adressing/allocation/relocationStatic storageElectronic systemsMulti processor

A processor-based electronic system includes several memory modules arranged in first and second ranks. The memory modules in the first rank are directly accessed by any of several processors, and the memory modules in the second rank are accessed by the processors through the memory modules in the first rank. The data bandwidth between the processors and the memory modules in the second rank is varied by varying the number of memory modules in the first rank that are used to access the memory module in the second set. Each of the memory modules includes several memory devices coupled to a memory hub. The memory hub includes a memory controller coupled to each memory device, a link interface coupled to a respective processor or memory module, and a cross bar switch coupling any of the memory controllers to any of the link interfaces.

Owner:ROUND ROCK RES LLC

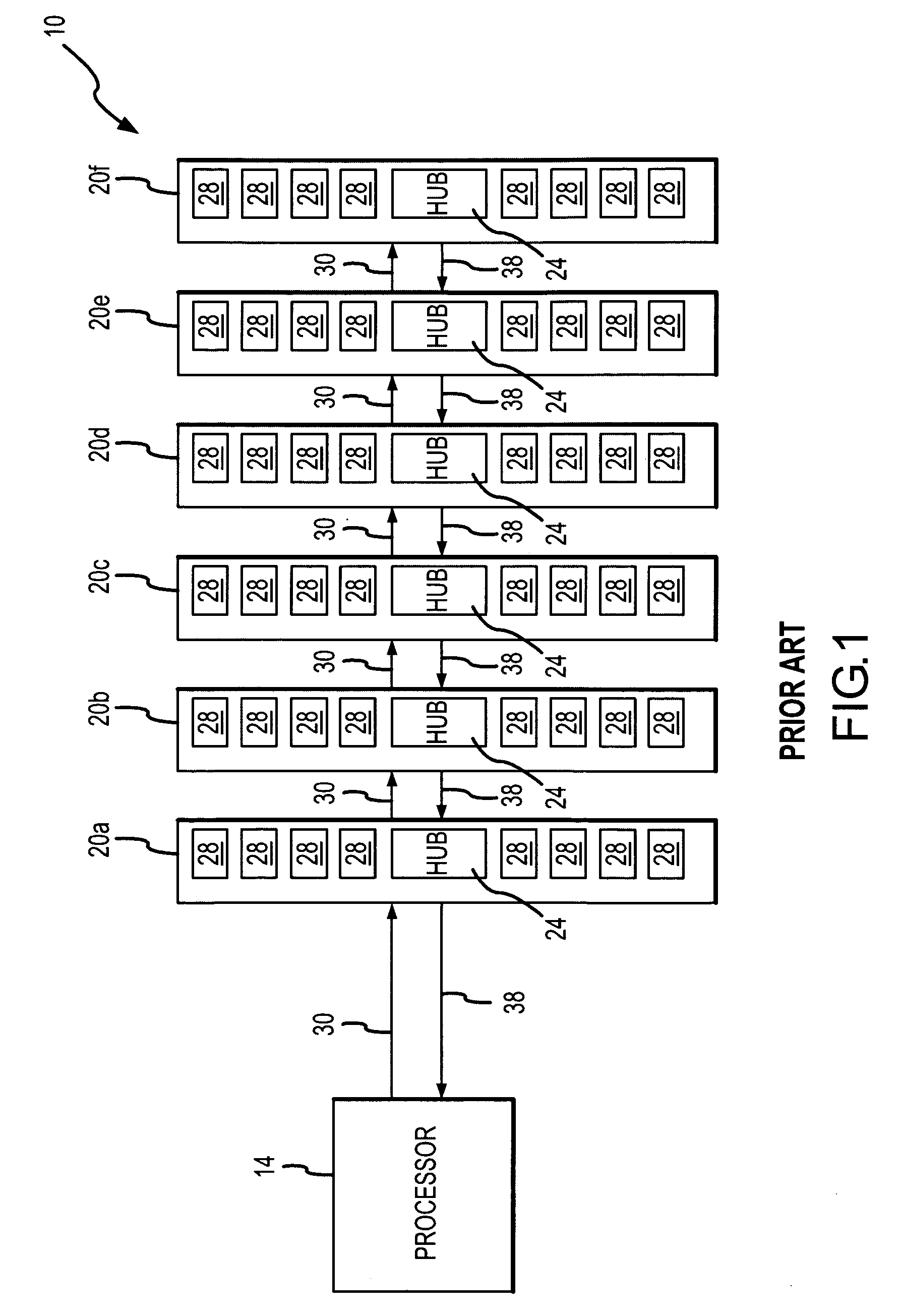

System and method for on-board timing margin testing of memory modules

InactiveUS20050060600A1Increase computing speedElectronic circuit testingError detection/correctionOn boardCrossover switch

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a self-test module. The self-test module includes a pattern generator producing write data having a predetermined pattern, and a flip-flop having a data input receiving the write data. A clock input of the flip-flop receives an internal clock signal from a delay line that receives a variable frequency clock generator. Read data are coupled from the memory devices and their pattern compared to the write data pattern. The delay of the delay line and frequency of the clock signal can be varied to test the speed margins of the memory devices.

Owner:ROUND ROCK RES LLC

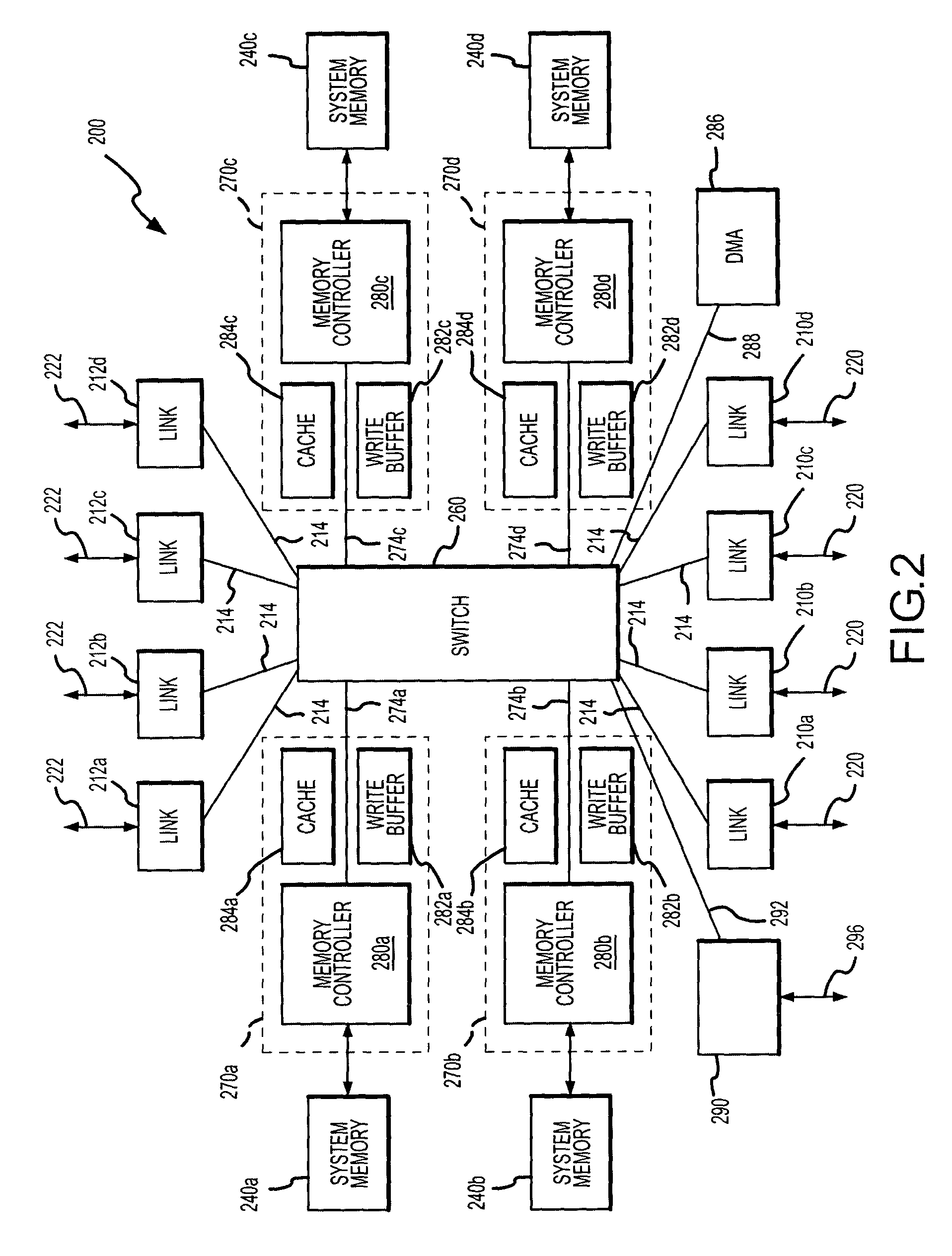

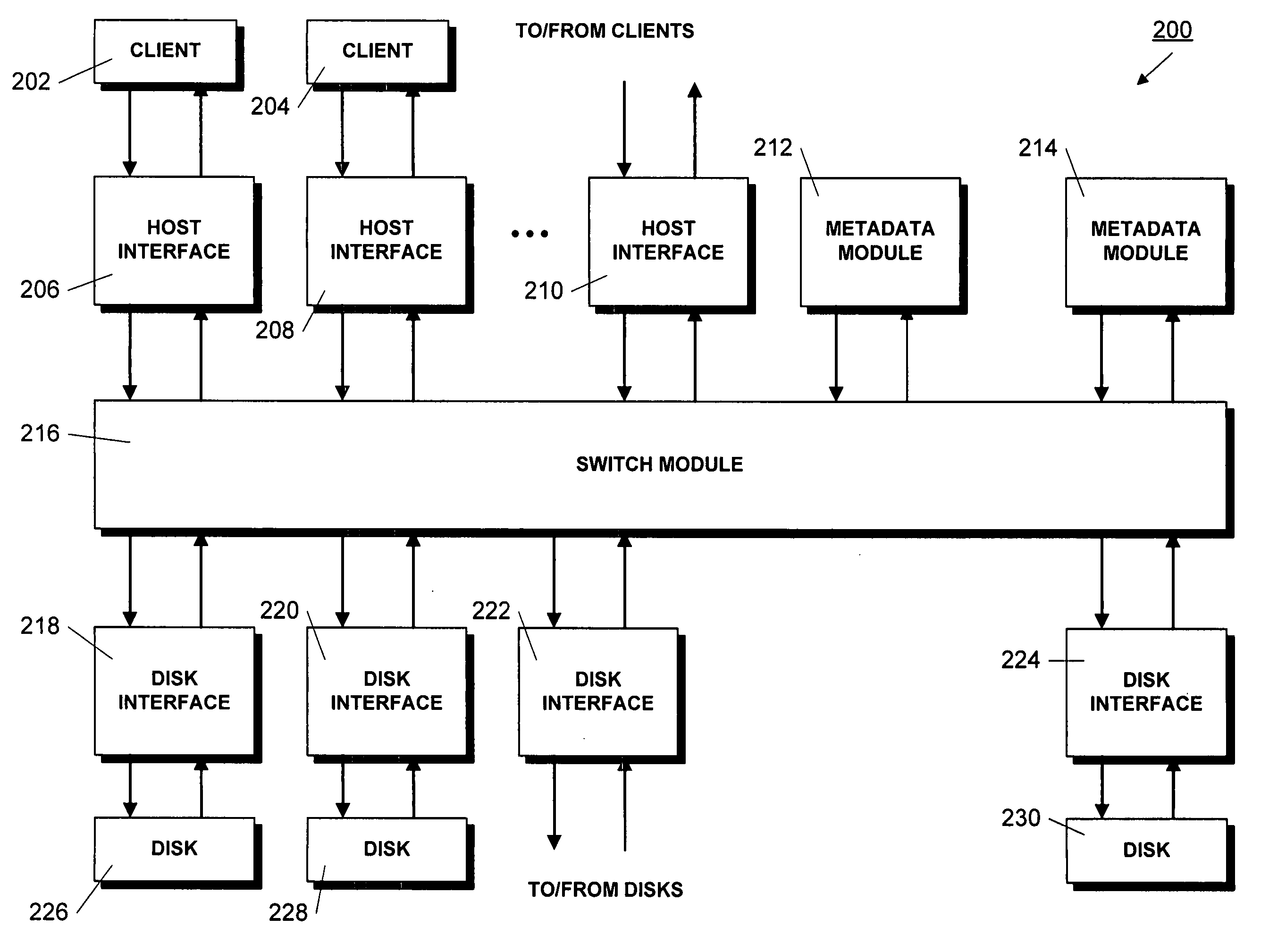

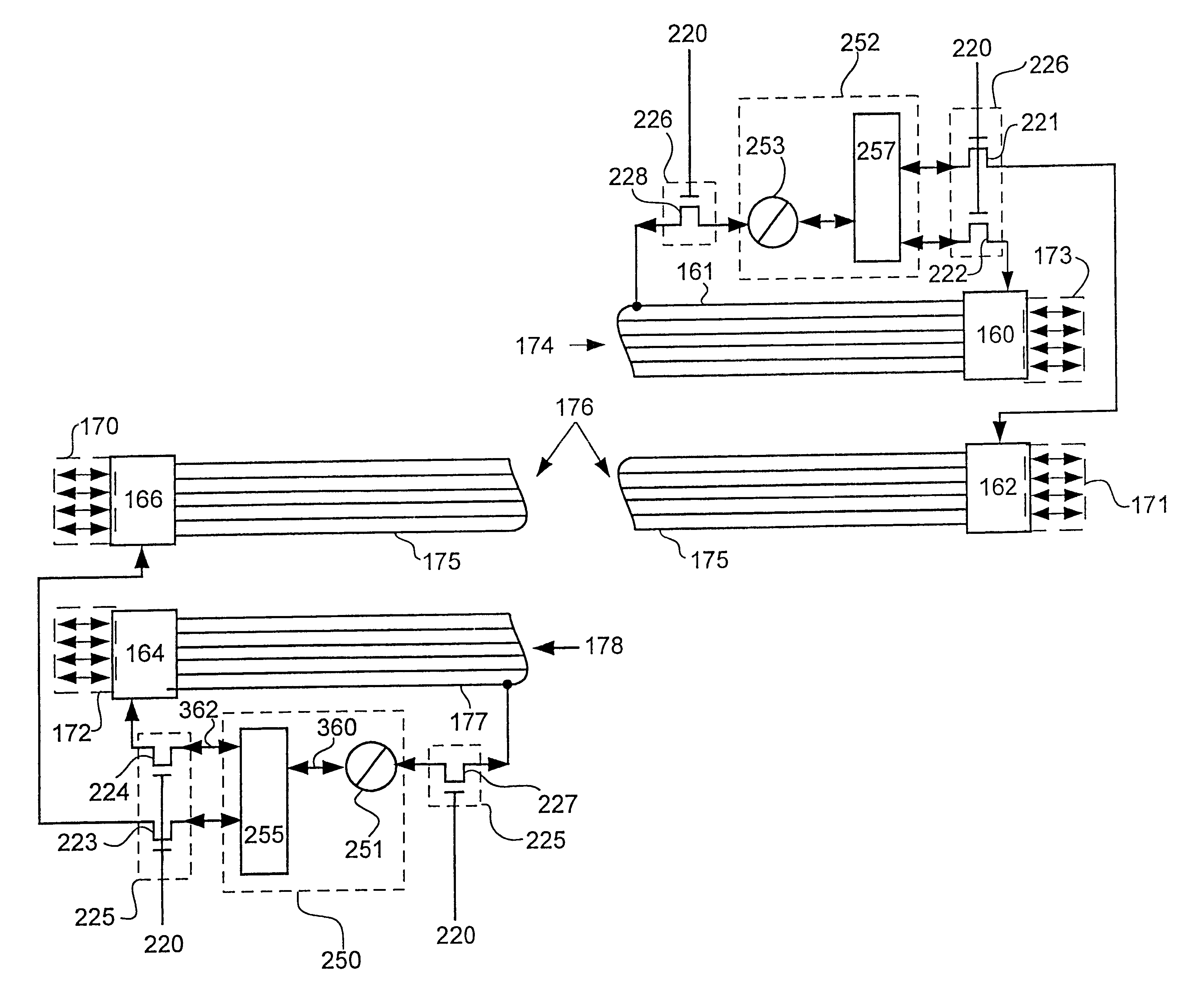

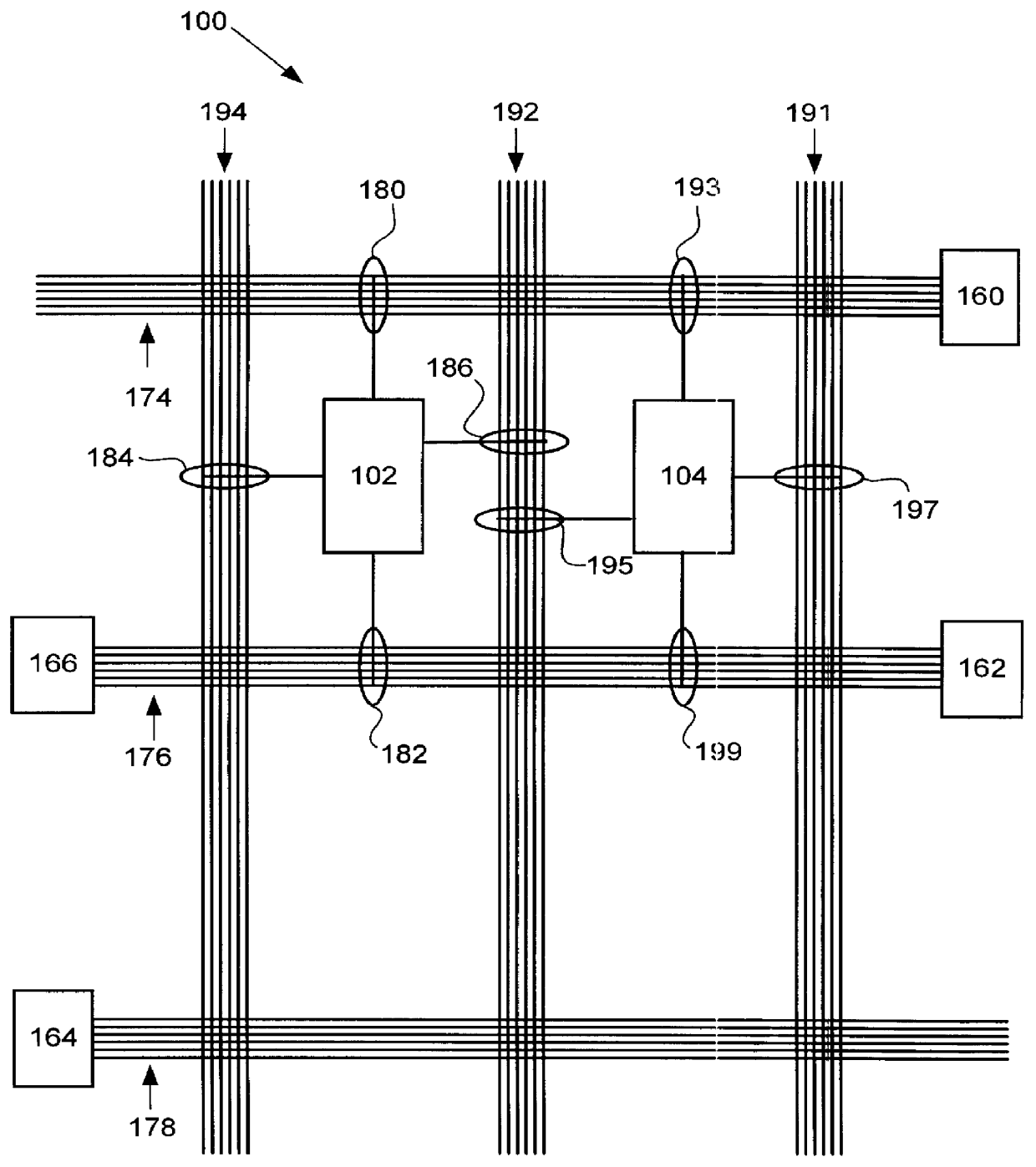

Method and apparatus for implementing high-performance, scaleable data processing and storage systems

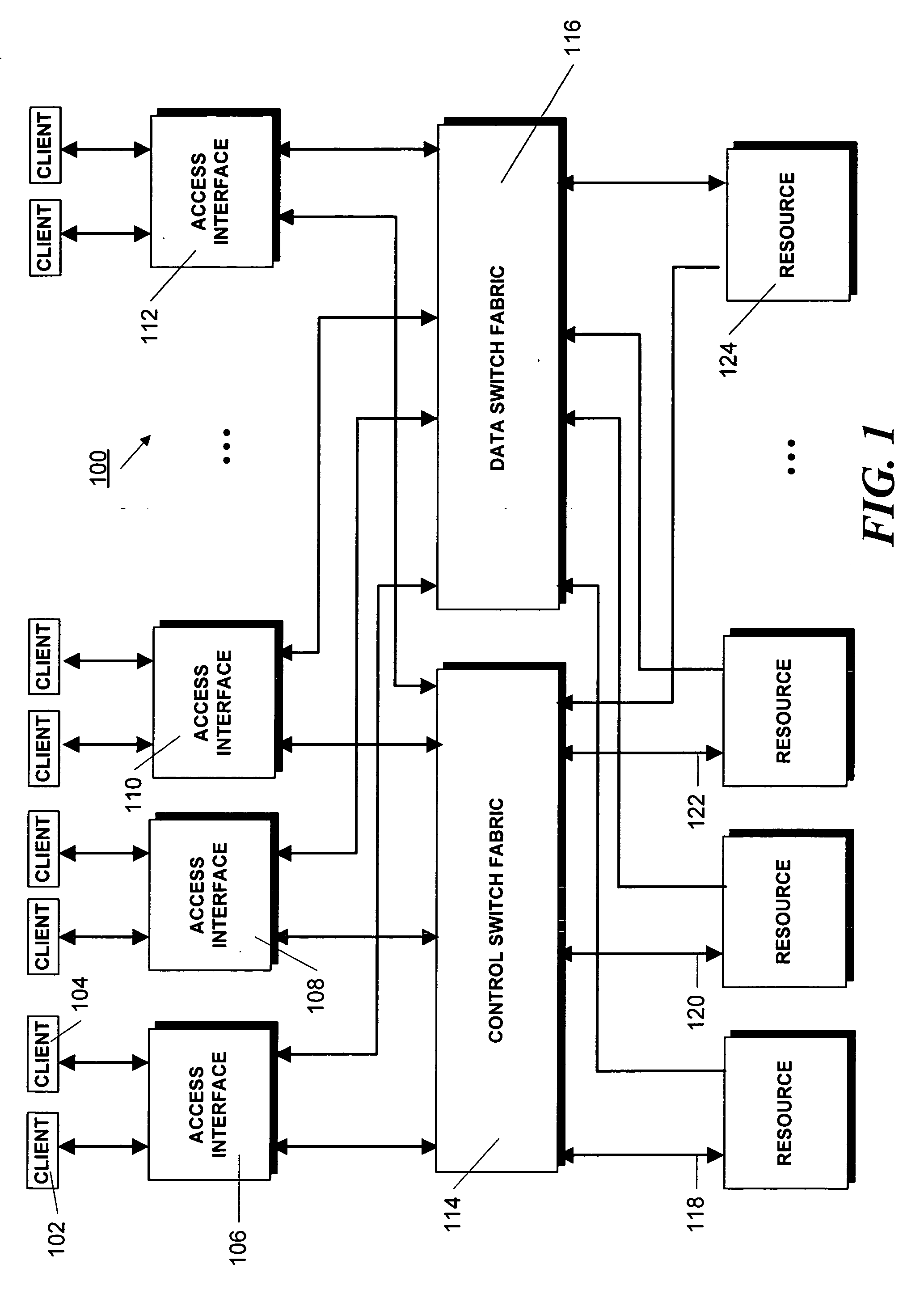

ActiveUS20060161678A1More communication pathEliminate the problemResource allocationMultiple digital computer combinationsResource utilizationResource element

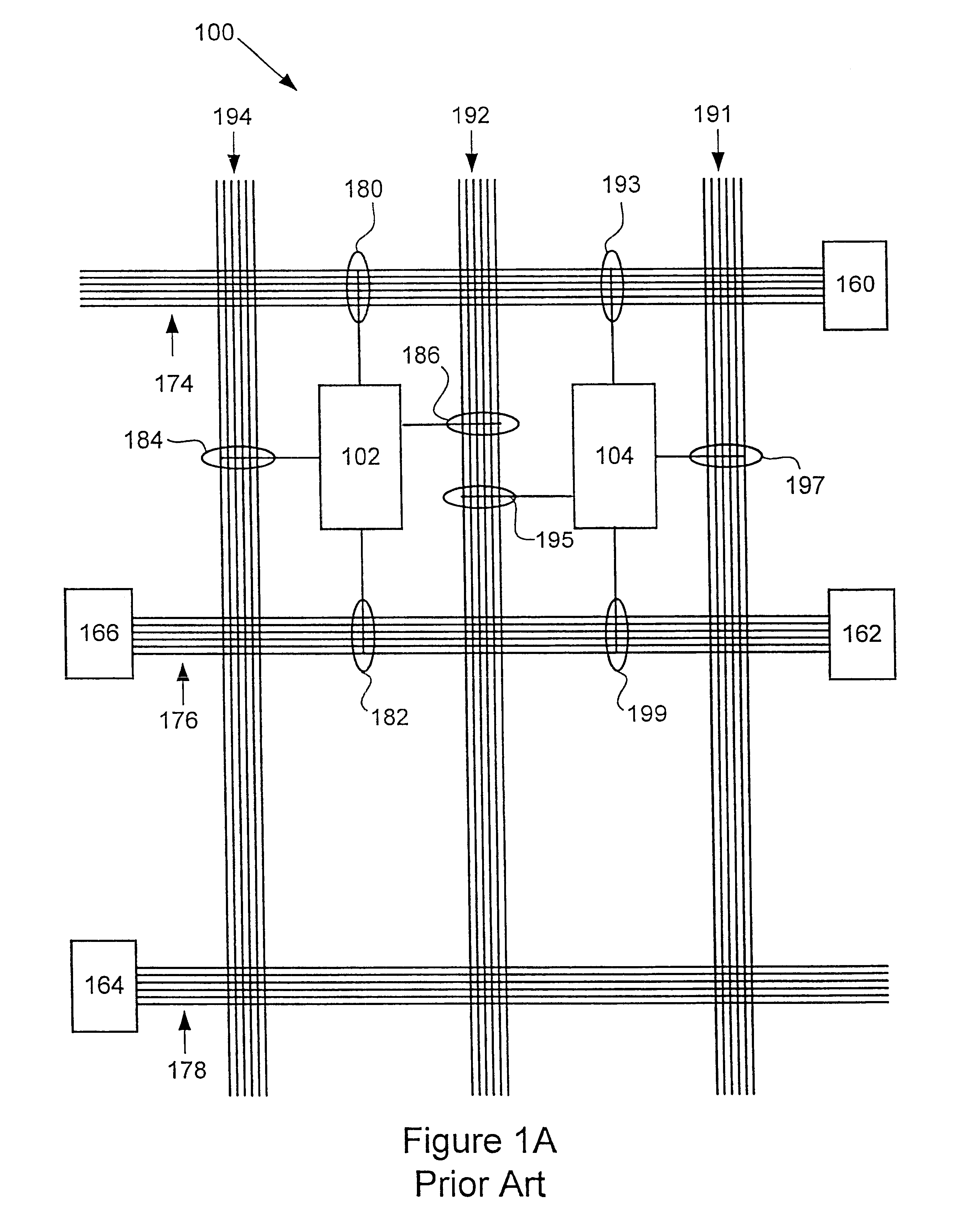

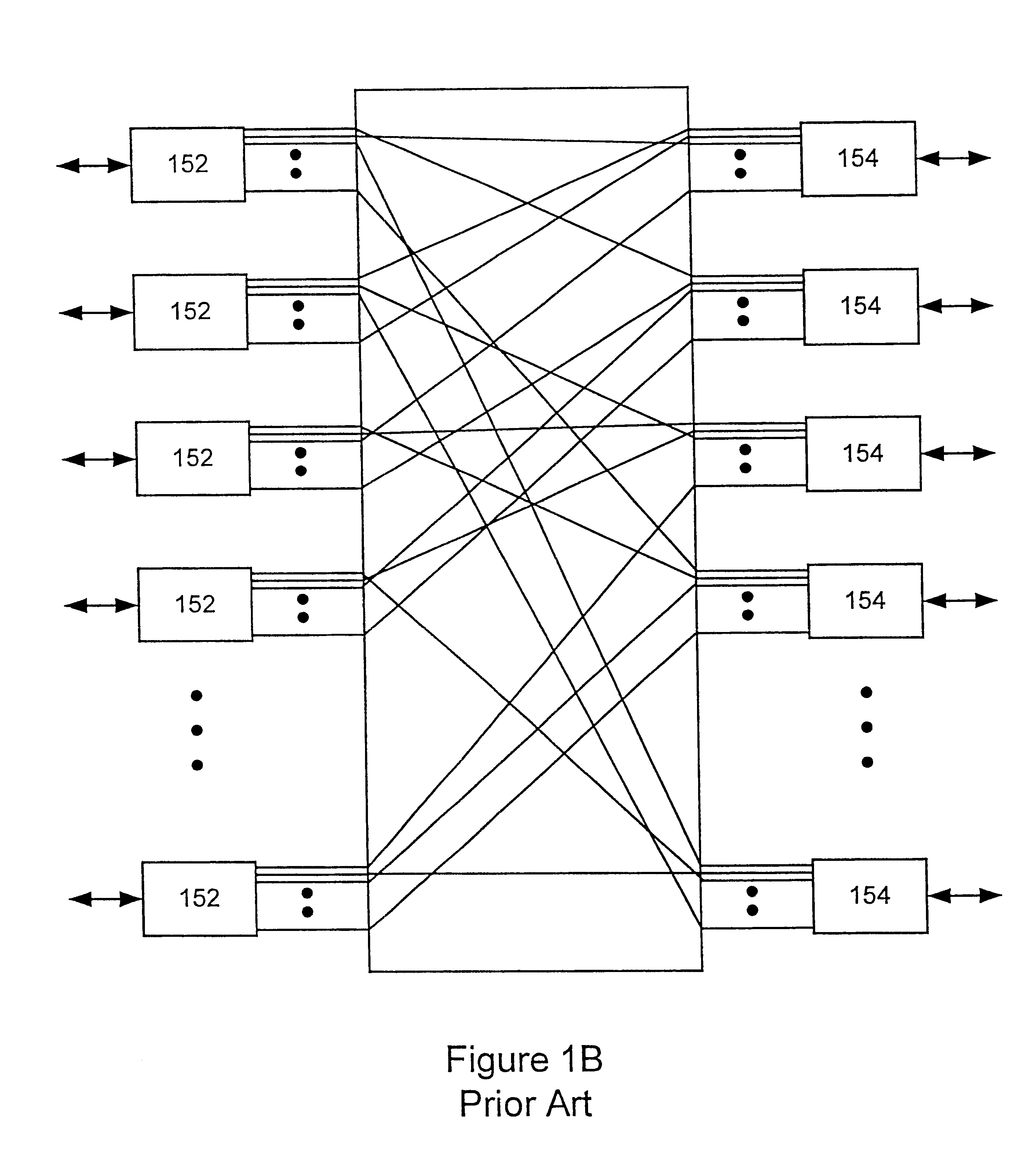

A data system architecture is described that allows multiple processing and storage resources to be connected to multiple clients so as 1) to distribute the clients' workload efficiently across the available resources; and 2) to enable scaleable expansion, both in terms of the number of clients and in the number of resources. The major features of the architecture are separate, modular, client and resource elements that can be added independently, a high-performance cross-bar data switch interconnecting these various elements, separate serial communication paths for controlling the cross-bar switch settings, separate communication paths for passing control information among the various elements and a resource utilization methodology that enables clients to distribute processing or storage tasks across all available resources, thereby eliminating “hot spots” resulting from uneven utilization of those resources.

Owner:EMC CORP

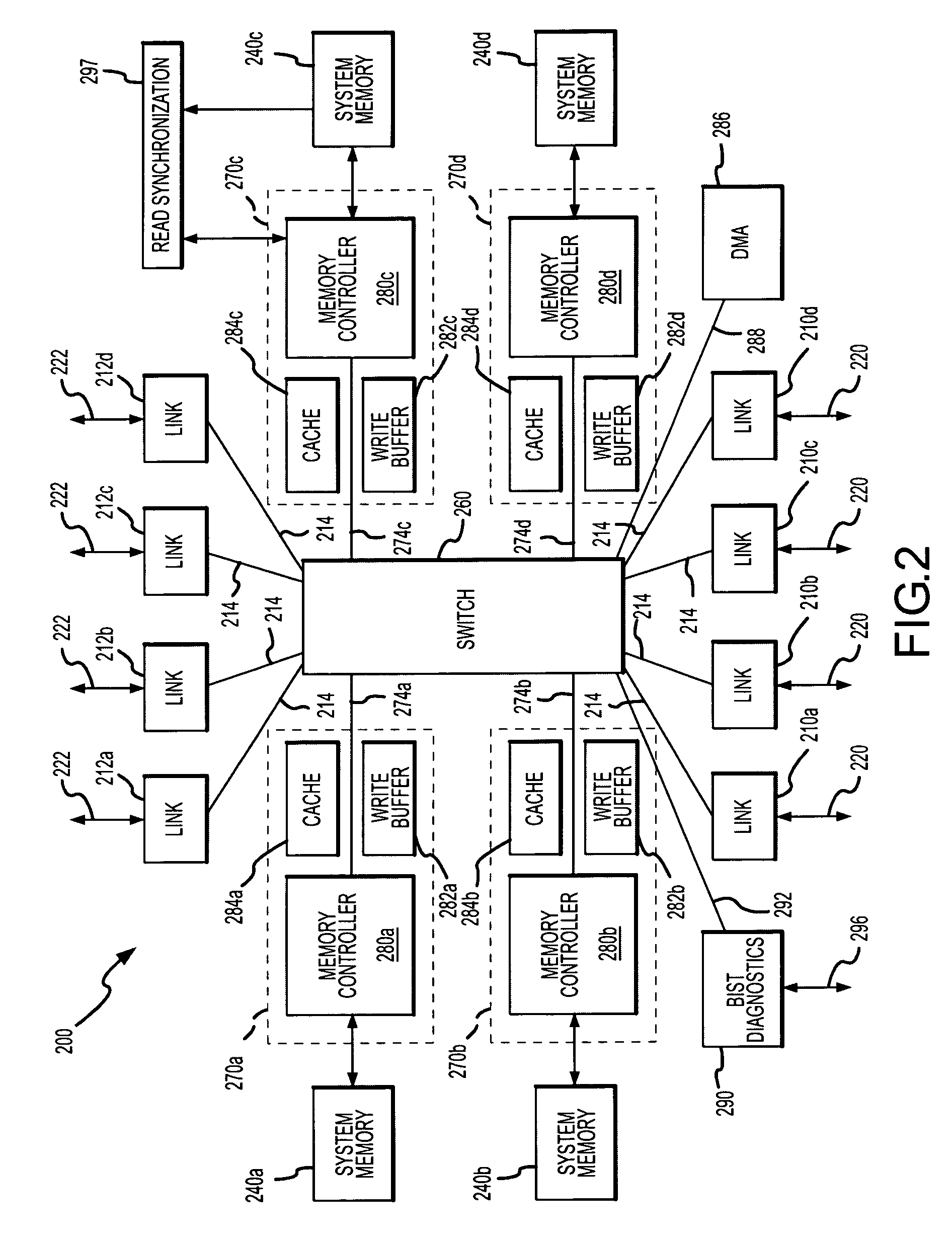

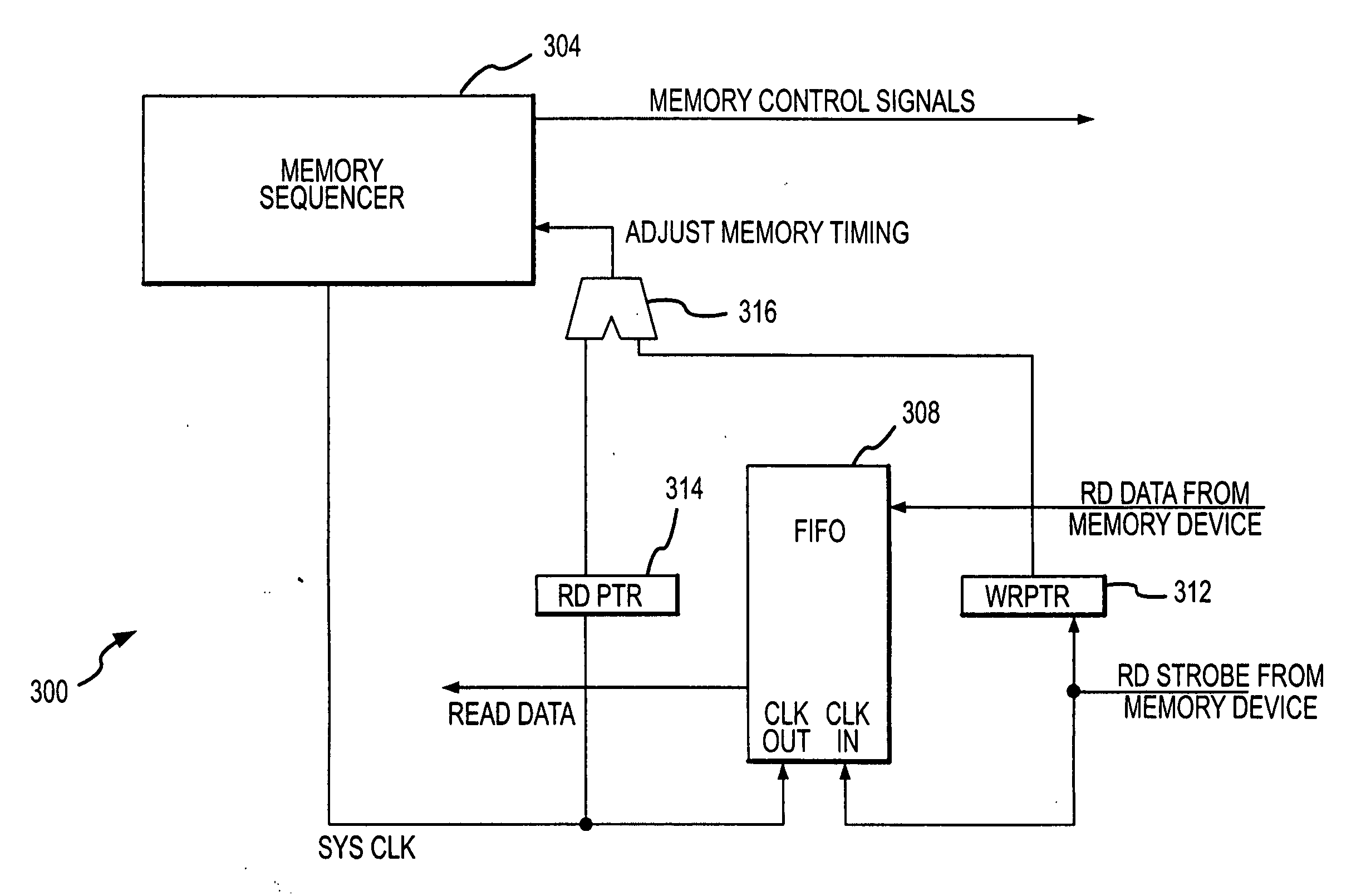

System and method for read synchronization of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a read synchronization module. The read synchronization module includes a write pointer, a read pointer and a buffer. The write pointer is incremented in response to the receipt of read data. The read pointer increments in response to coupling of the read data from the memory hub. A comparator compares the read pointer an the write pointer, and the comparison is used to adjust the memory timing.

Owner:MICRON TECH INC

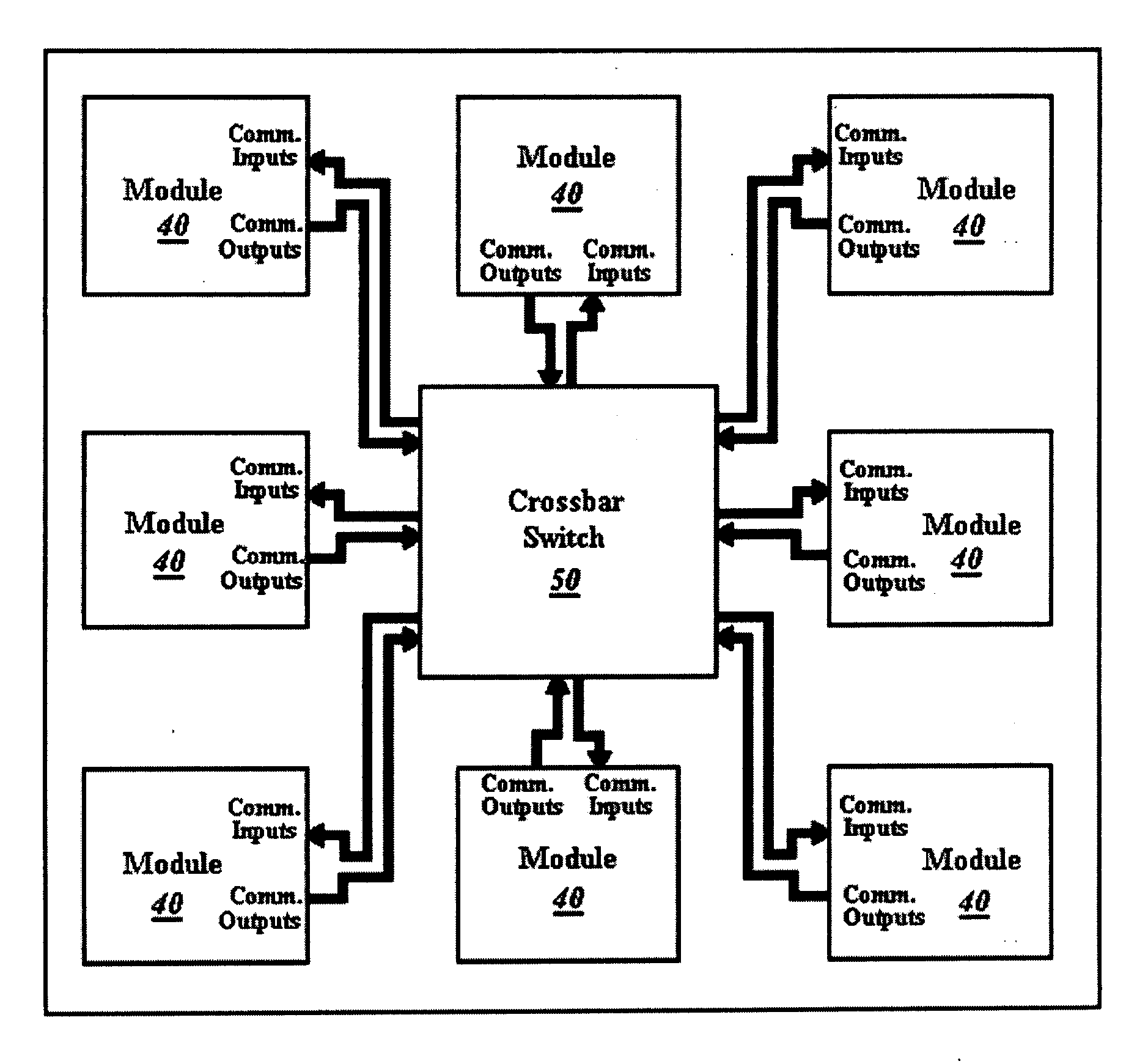

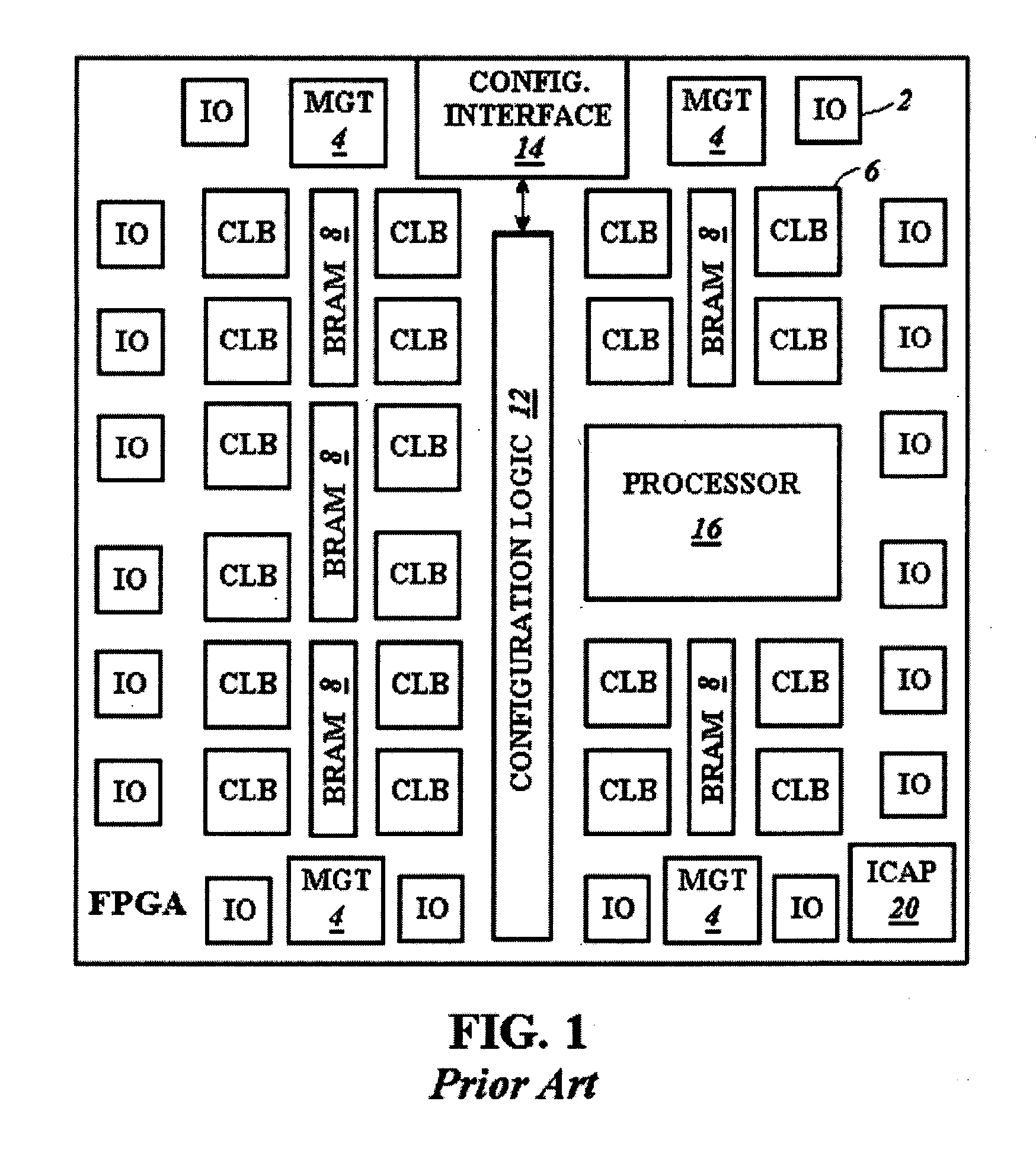

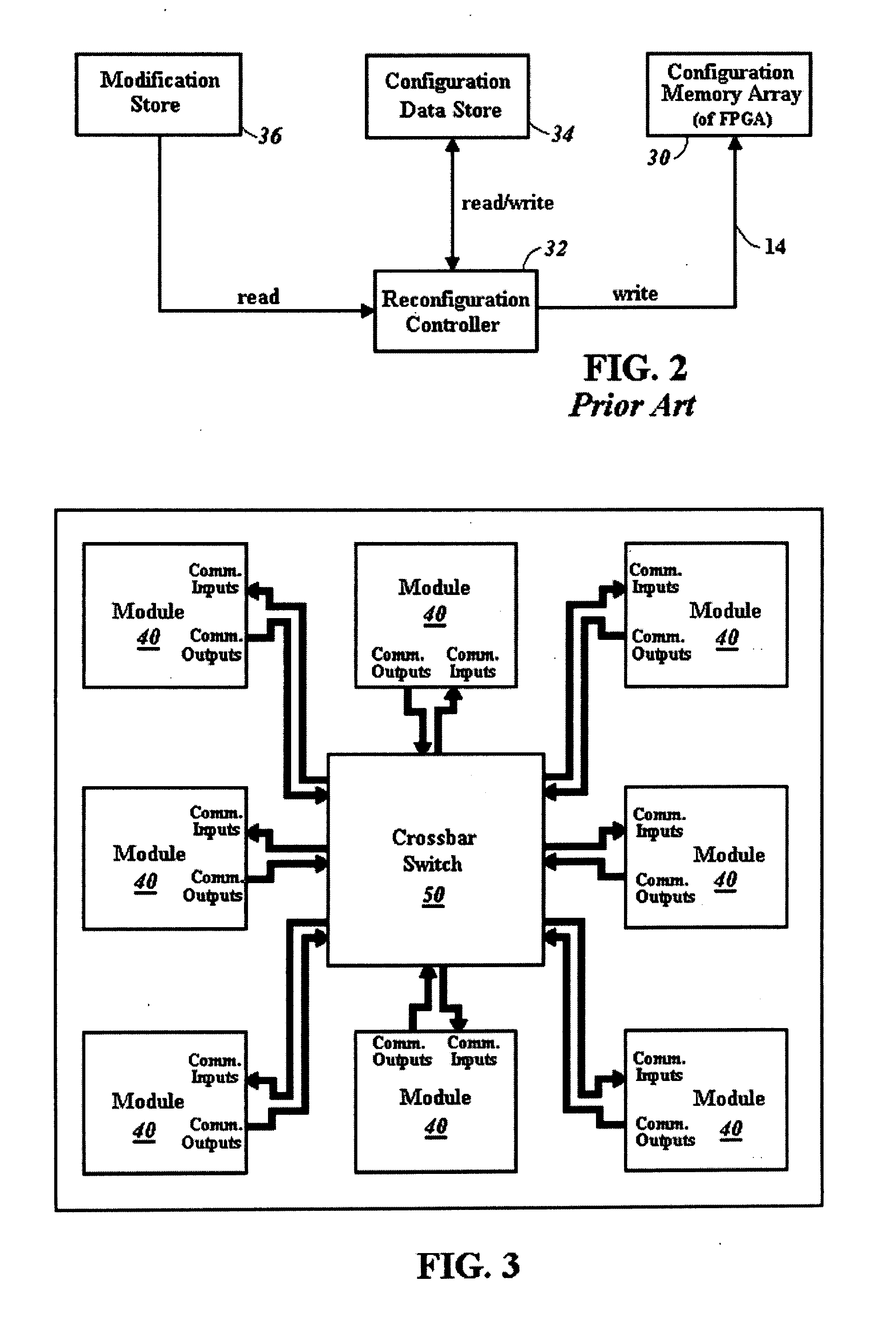

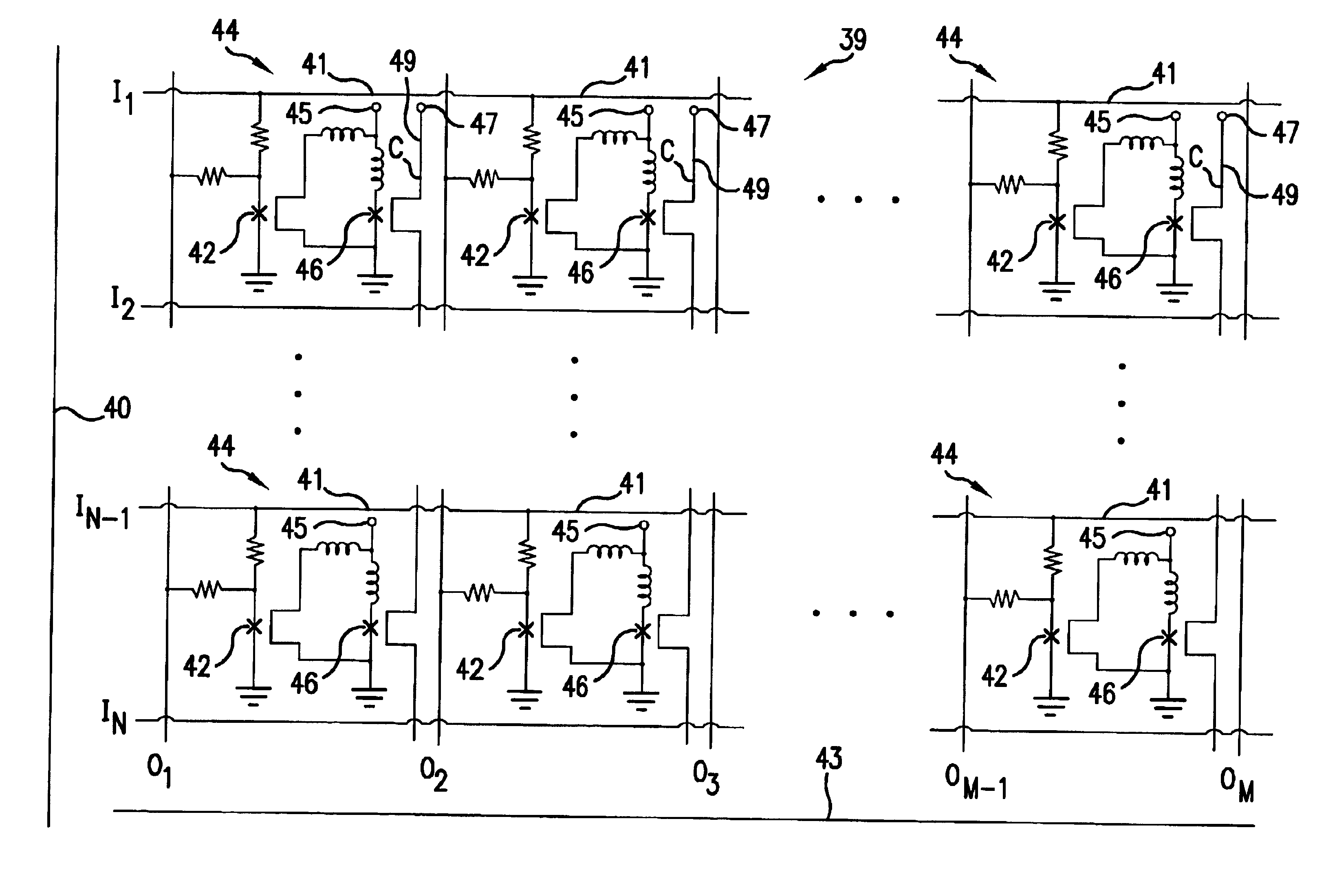

High bandwidth reconfigurable on-chip network for reconfigurable systems

ActiveUS20070200594A1Reduce necessaryExtension of timeSolid-state devicesLogic circuits using elementary logic circuit componentsCrossbar switchTelecommunications link

A crossbar switch is implemented in a reconfigurable circuit, such as a FPGA, instantiated with a number of modules, the crossbar switch providing communication links between the modules. The modules and crossbar switch can be easily updated in a partial reconfiguration process changing only portions of modules and the crossbar switch while other portions remain active. The crossbar switch uses individual wiring to independently connect module outputs and inputs so that asynchronous communications can be used. The crossbar switch can be implemented in different embodiments including a Clos crossbar switch, and a crossbar switch connecting each module output only to a corresponding module input, allowing for a reduction in the amount of FPGA resources required to create the crossbar switches.

Owner:XILINX INC

Superconductive crossbar switch

ActiveUS6960929B2Low powerDetects and resolve conflictMultiplex system selection arrangementsElectronic switchingCrossbar switchGigabit

Owner:BEDARD FERNAND D

Integrated circuit incorporating a programmable cross-bar switch

InactiveUS6404225B1Solid-state devicesLogic circuits using elementary logic circuit componentsEngineeringCrossover switch

An integrated circuit operable in a plurality of switching modes is disclosed. The integrated circuit includes a plurality of direct connectors and a programmable switch unit operable in a plurality of switching modes. The programmable switch unit has a plurality of bi-directional I / O ports selectively connected by way of programmable switch unit internal connectors. The integrated circuit also includes a programmable function unit directly connected to the programmable switch unit by way of the direct connectors. The programmable function unit is programmable configured to operate as required by a selected one of the plurality of switching modes. As required by the selected one of the plurality of switching modes, the programmable function unit directs the programmable switch unit to form internal connections using the programmable switch unit internal connectors such that the programmable switch unit passes signals between selected portions of the plurality of bi-directional I / O ports.

Owner:ALTERA CORP

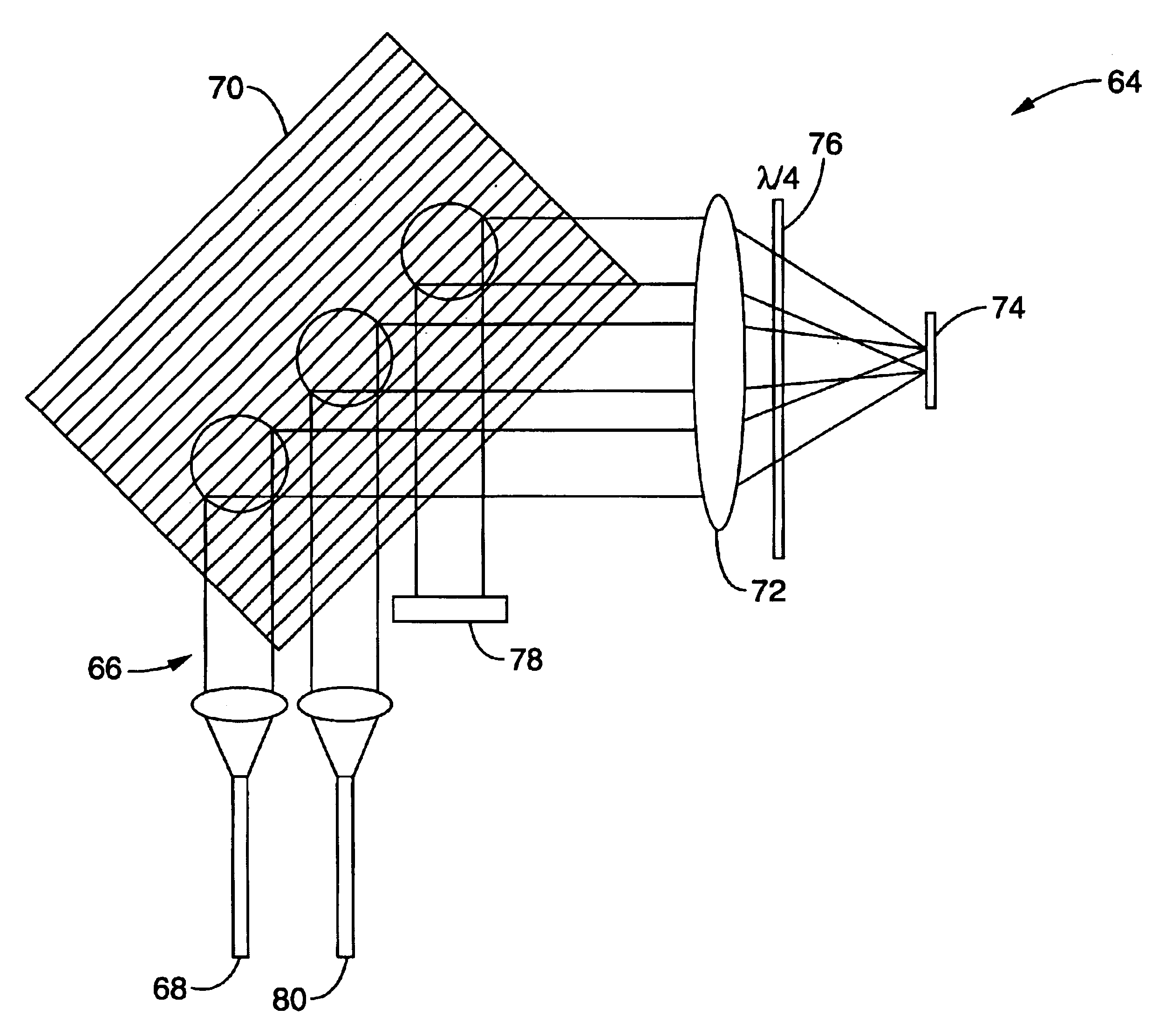

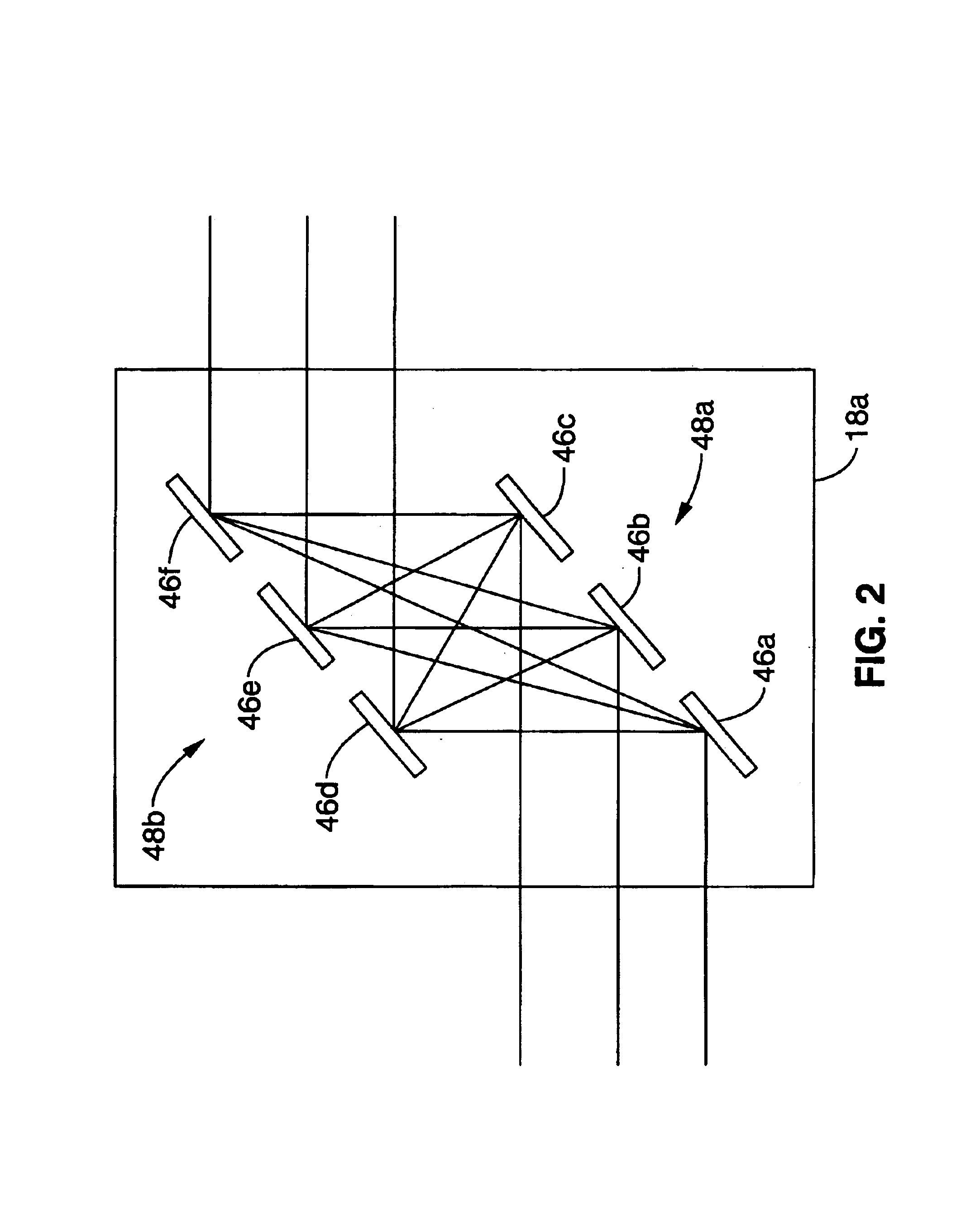

Multi-wavelength cross-connect optical switch

InactiveUS6922239B2High performance featuresReduce lossMultiplex system selection arrangementsRadiation pyrometryFiberGrating

A cross-connect switch for fiber-optic communication networks employing a wavelength dispersive element, such as a grating, and a stack of regular (non-wavelength selective) cross bar switches using two-dimensional arrays of micromachined, electrically actuated, individually-tiltable, controlled deflection micro-mirrors for providing multiport switching capability for a plurality of wavelengths. Using a one-dimensional micromirror array, a fiber-optic based MEMS switched spectrometer that does not require mechanical motion of bulk components or large diode arrays can be constructed with readout capability for WDM network diagnosis or for general purpose spectroscopic applications.

Owner:RGT UNIV OF CALIFORNIA

System and method for read synchronization of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a read synchronization module. The read synchronization module includes a write pointer, a read pointer and a buffer. The write pointer is incremented in response to the receipt of read data. The read pointer increments in response to coupling of the read data from the memory hub. A comparator compares the read pointer an the write pointer, and the comparison is used to adjust the memory timing.

Owner:MICRON TECH INC

System and method for read synchronization of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a read synchronization module. The read synchronization module includes a write pointer, a read pointer and a buffer. The write pointer is incremented in response to the receipt of read data. The read pointer increments in response to coupling of the read data from the memory hub. A comparator compares the read pointer an the write pointer, and the comparison is used to adjust the memory timing.

Owner:MICRON TECH INC

System and method for on-board timing margin testing of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a self-test module. The self-test module includes a pattern generator producing write data having a predetermined pattern, and a flip-flop having a data input receiving the write data. A clock input of the flip-flop receives an internal clock signal from a delay line that receives a variable frequency clock generator. Read data are coupled from the memory devices and their pattern compared to the write data pattern. The delay of the delay line and frequency of the clock signal can be varied to test the speed margins of the memory devices.

Owner:ROUND ROCK RES LLC

Programmable logic device architecture incorporating a dedicated cross-bar switch

InactiveUS6060903ASolid-state devicesLogic circuits using elementary logic circuit componentsCrossbar switchLogic cell

A programmable logic device architecture incorporating a cross-bar switch is disclosed. In a preferred embodiment, a plurality of logic cells is programmably interconnected to form an array of logic cells capable of implementing complex logic functions. A user selectable cross-bar switch block having dedicated programmable connectors is coupled to the array of logic cells by way of a mode control circuit switch. The mode control circuit switch is arranged to couple the dedicated cross-bar switch block to the array of logic cells in a first mode and to de-couple the cross-bar switch block from the array of logic blocks in a second mode.

Owner:ALTERA CORP

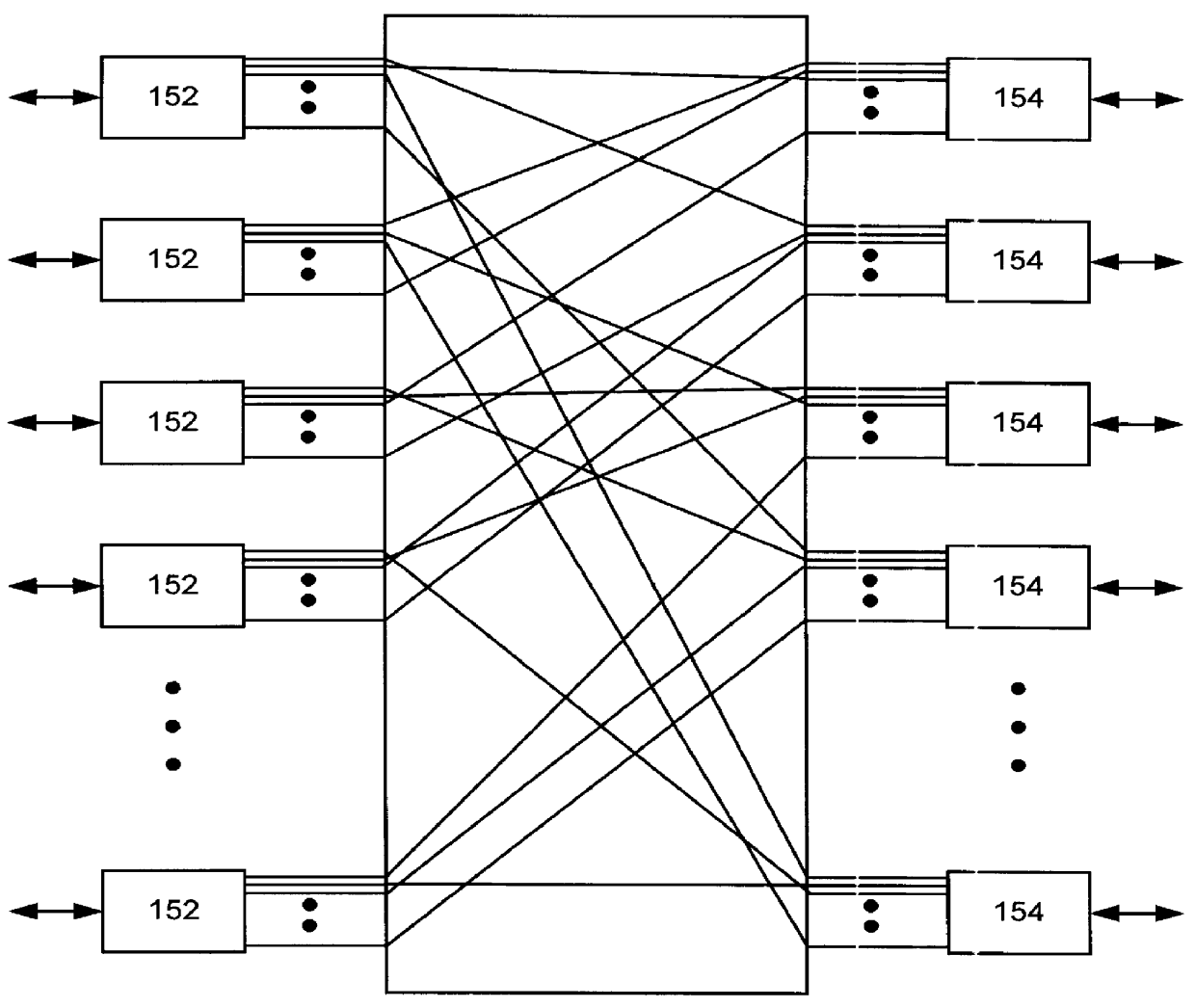

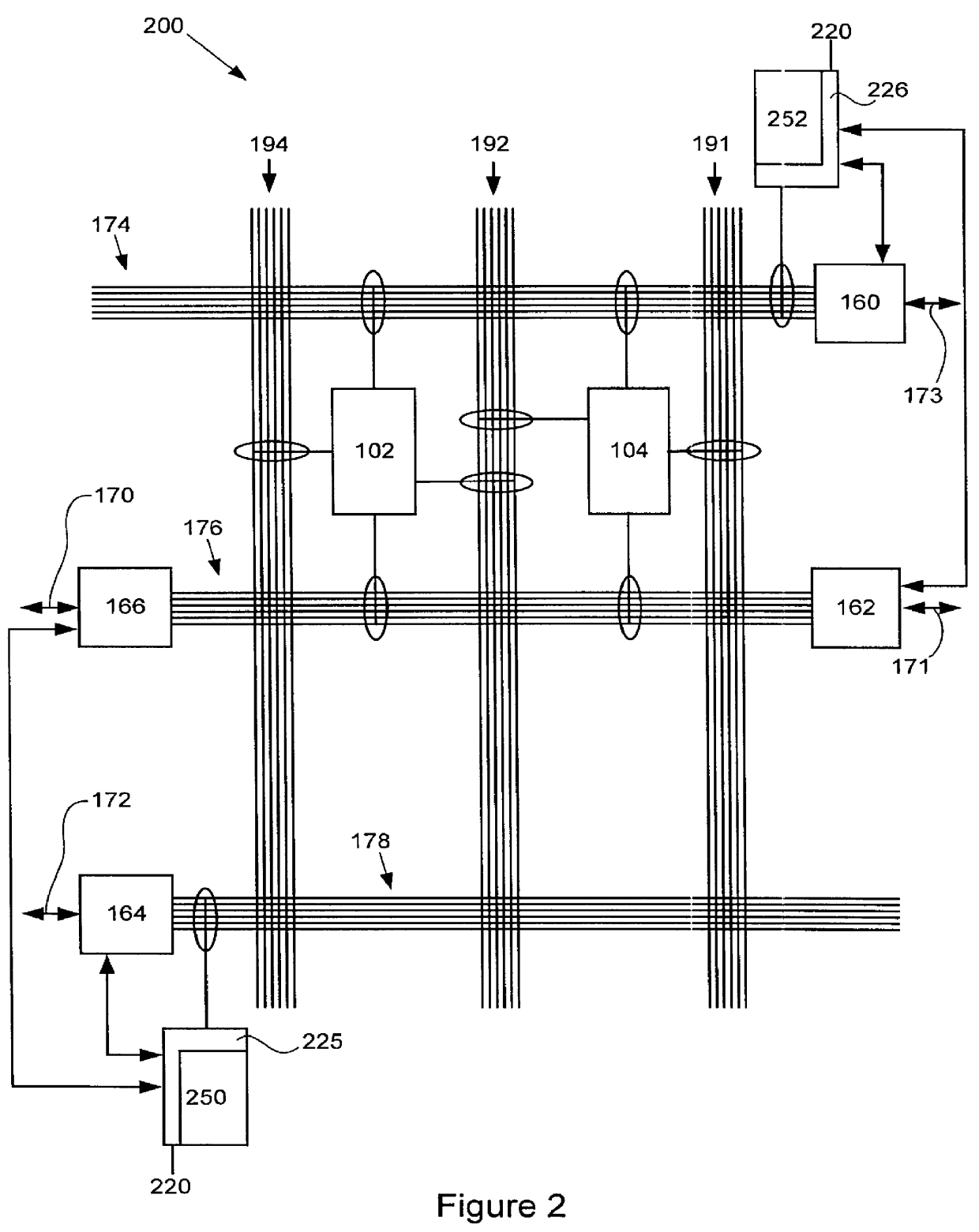

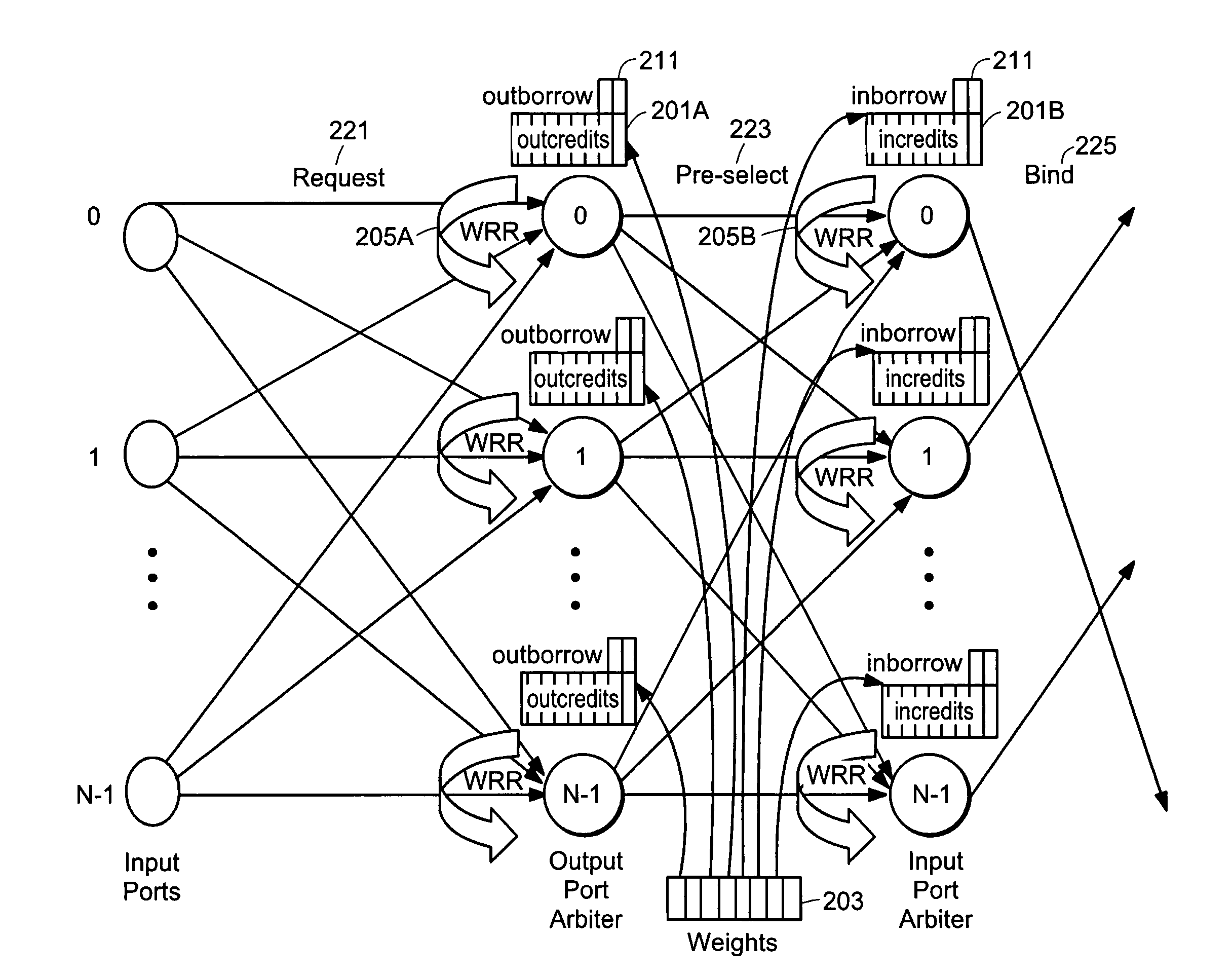

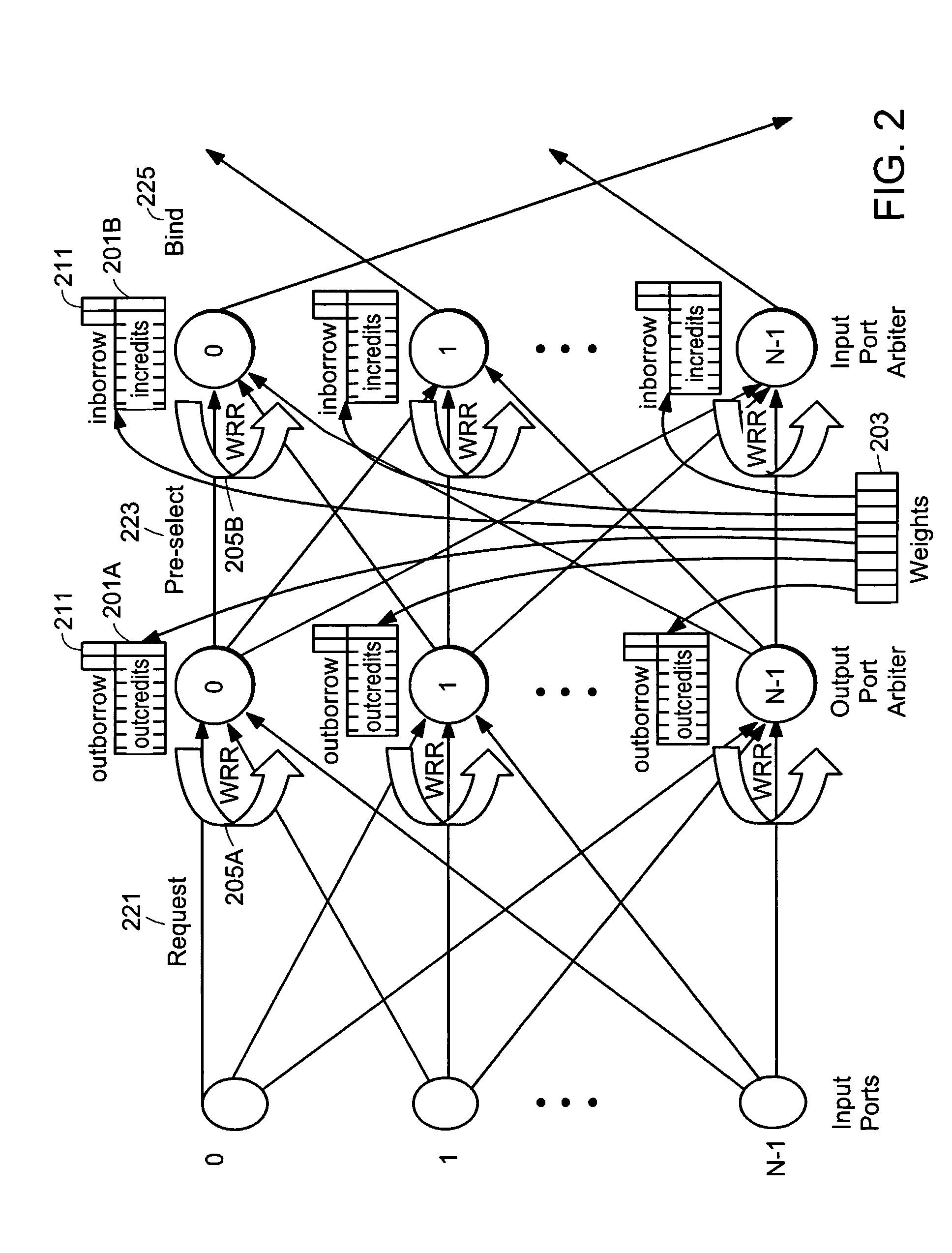

Weighted fair share scheduler for large input-buffered high-speed cross-point packet/cell switches

A switching fabric connects input ports to output ports. Each input has an input pointer referencing an output port, and each output has an output pointer referencing an input port. An arbiter includes input and output credit allocators, and an arbitration module (matcher). The input credit allocator resets input credits associated with input / output pairs and updates the input pointers. Similarly, the output credit allocator resets output credits associated with input / output pairs and updates the output pointers. The matcher matches inputs to outputs based on pending requests and available input and output credits. A scheduler schedules transmissions through the cross-bar switch according to the arbiter's matches.

Owner:TAHOE RES LTD

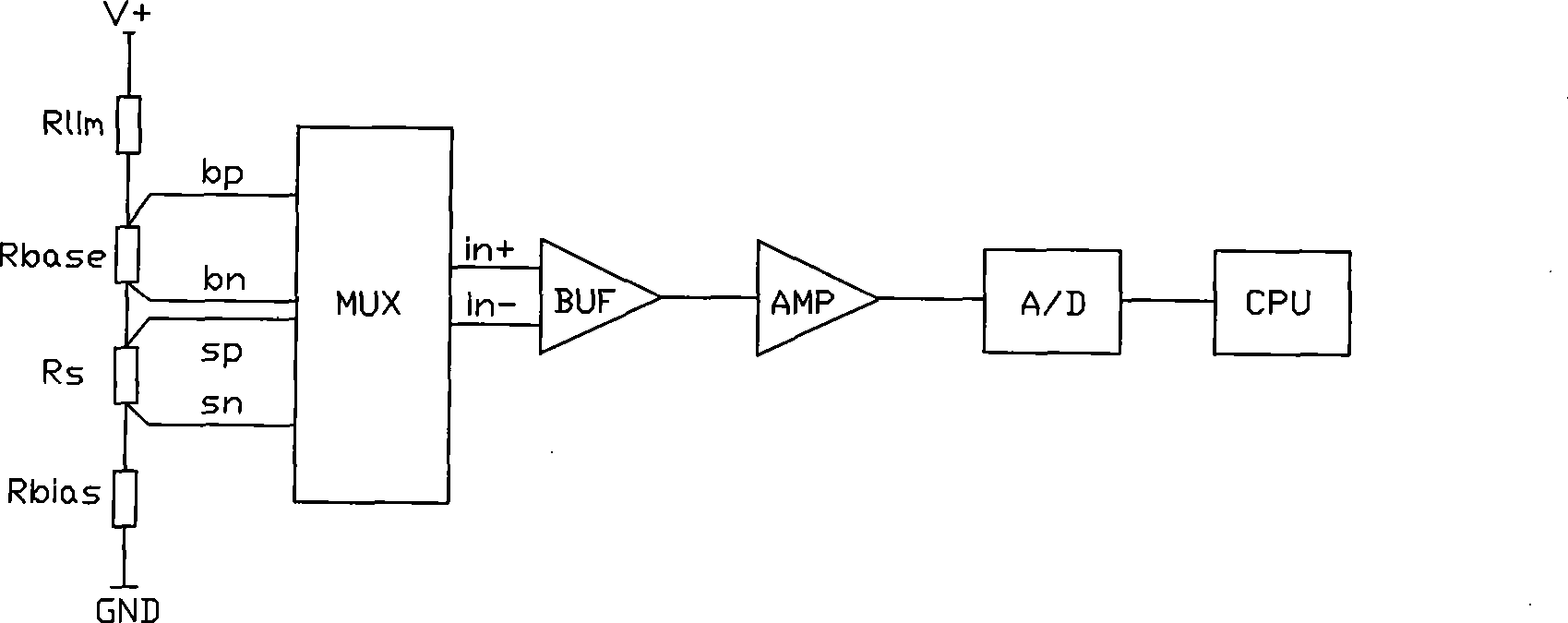

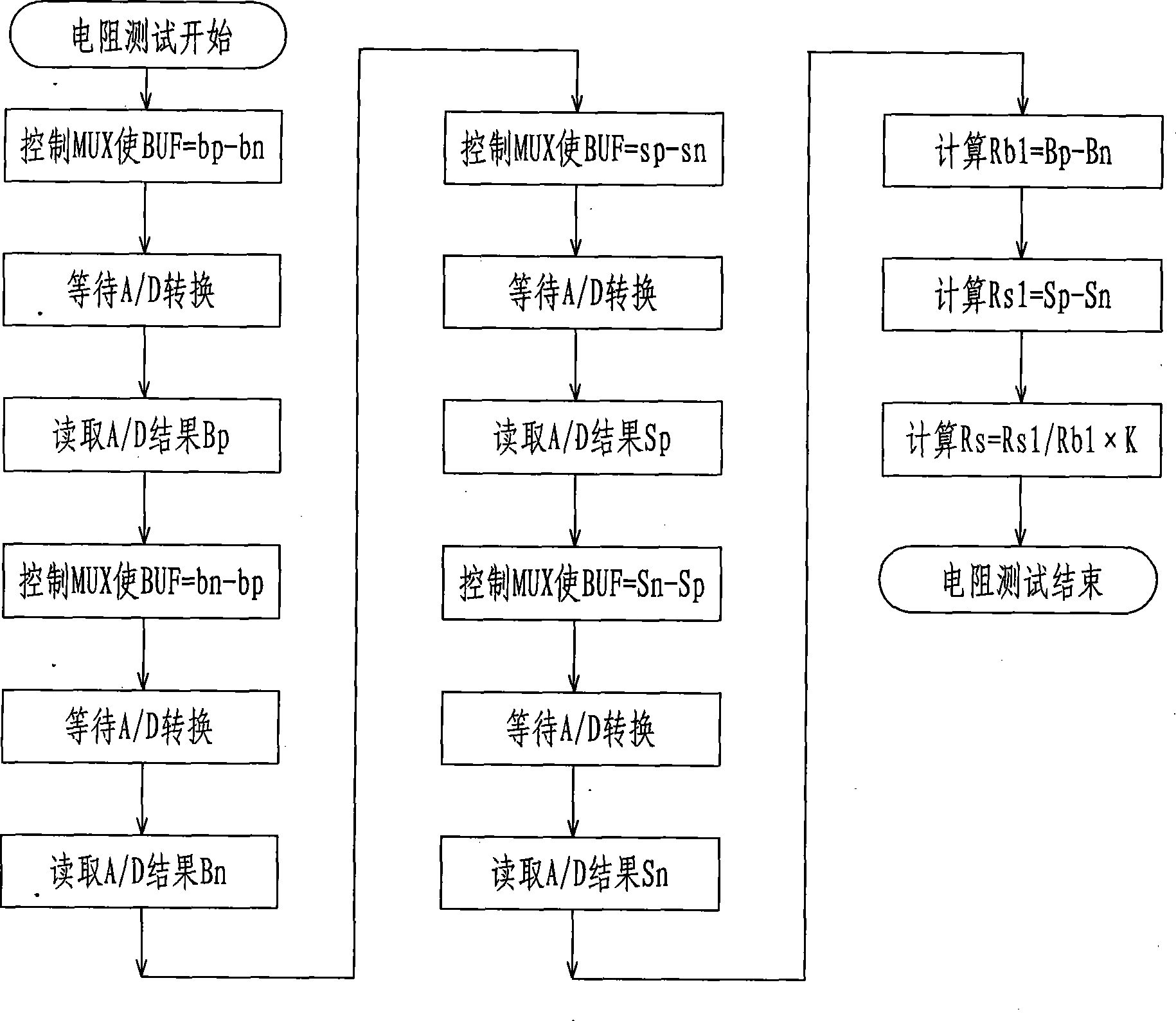

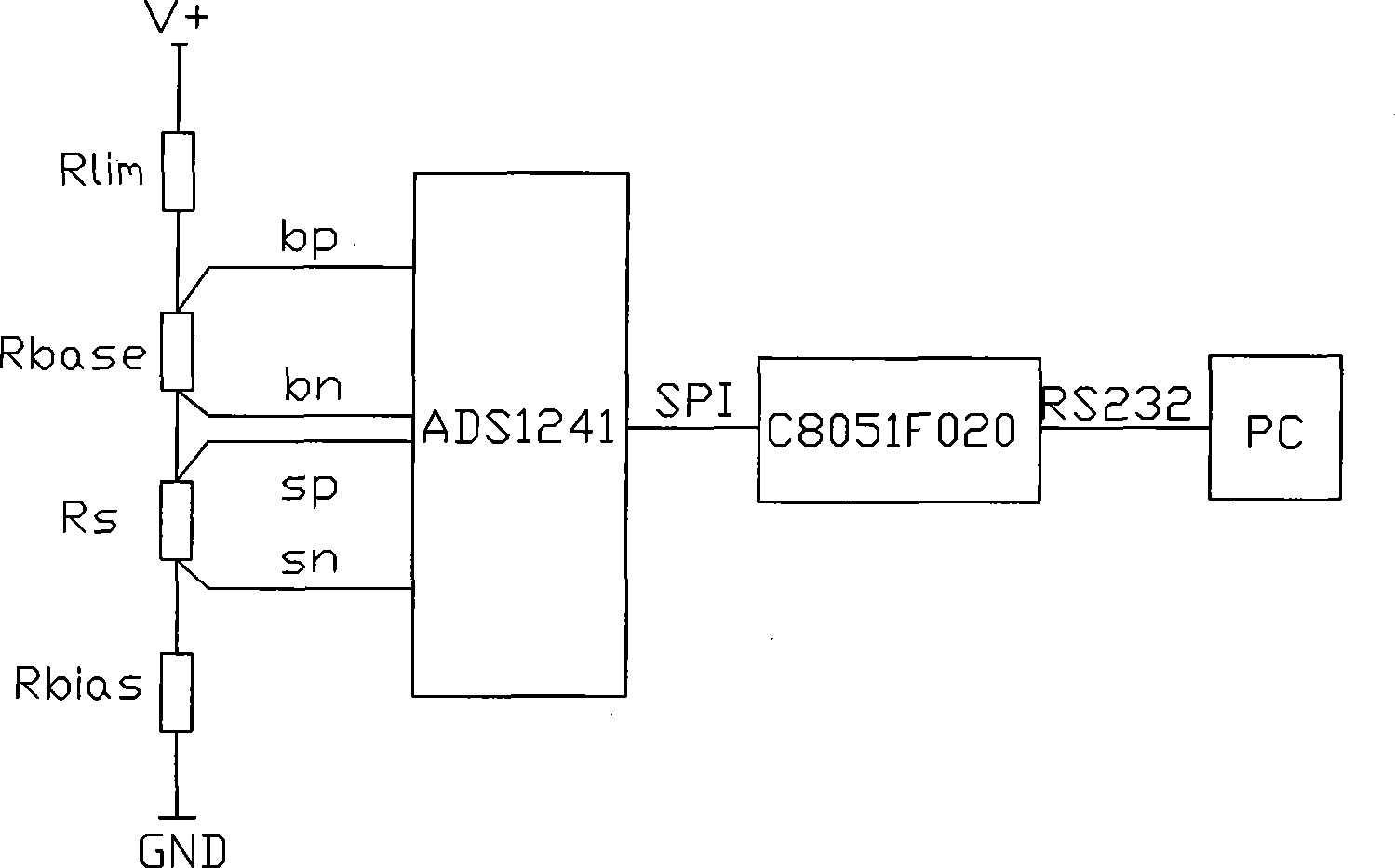

Accurate resistor measuring apparatus and method thereof

InactiveCN101498749AEliminate and avoid measurement errorsHigh measurement accuracyResistance/reactance/impedenceElectrical resistance and conductanceCurrent limiting

The invention relates to a precise resistance measuring device. One end of a resistor to be measured is connected to the anode of a power supply through a reference resistor and a current-limiting resistor, and the other end is grounded through a bias resistor; four input ends of a cross bar switch are respectively connected to two ends of the reference resistor and the resistor to be measured, and two output ends of the cross bar switch are respectively connected to the same-phase input end and the reverse-phase input end of a signal amplification circuit; the signal amplification circuit is connected to the data signal input end of a central processor through an A / D converter; the data signal output end of the central processor is connected with a memory; the control signal output end of the central processor is connected with the control signal input end of the cross bar switch to control the two output ends of the cross bar switch to sequentially output positive and negative voltage of two ends of the reference resistor and positive and negative voltage of two ends of the resistor to be measured; the positive and negative voltage of two ends of the reference resistor and the resistor to be measured is stored in the memory by the central processor through the processing by the signal amplification circuit and the A / D conversion by the A / D converter; and the central processor transfers the positive and negative voltage difference of the reference resistor and the positive and negative voltage difference of the resistor to be measured and carries out calculation to obtain the resistance value of the resistor to be measured.

Owner:CAMA LUOYANG ENVIRONMENTAL MEASUREMENT

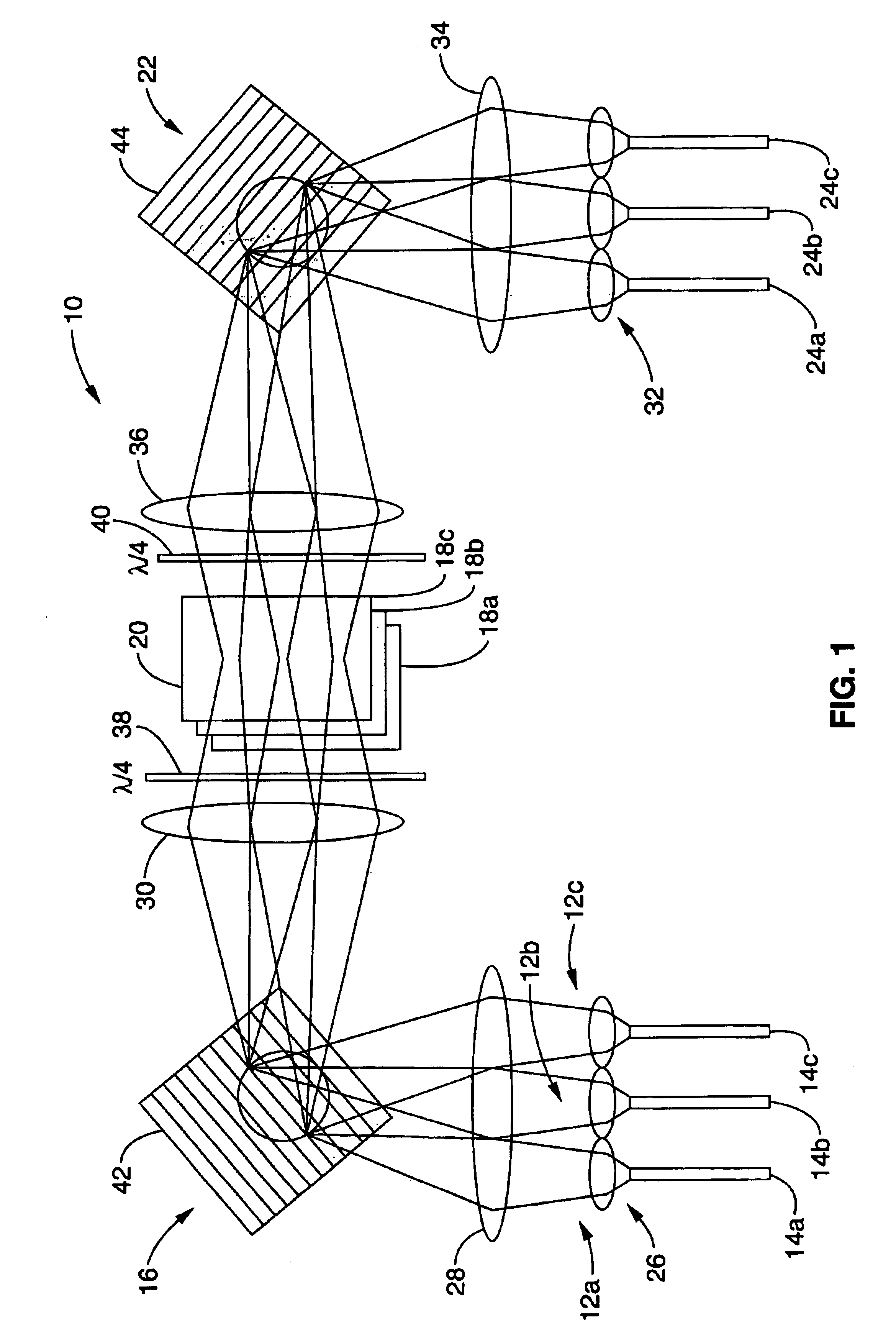

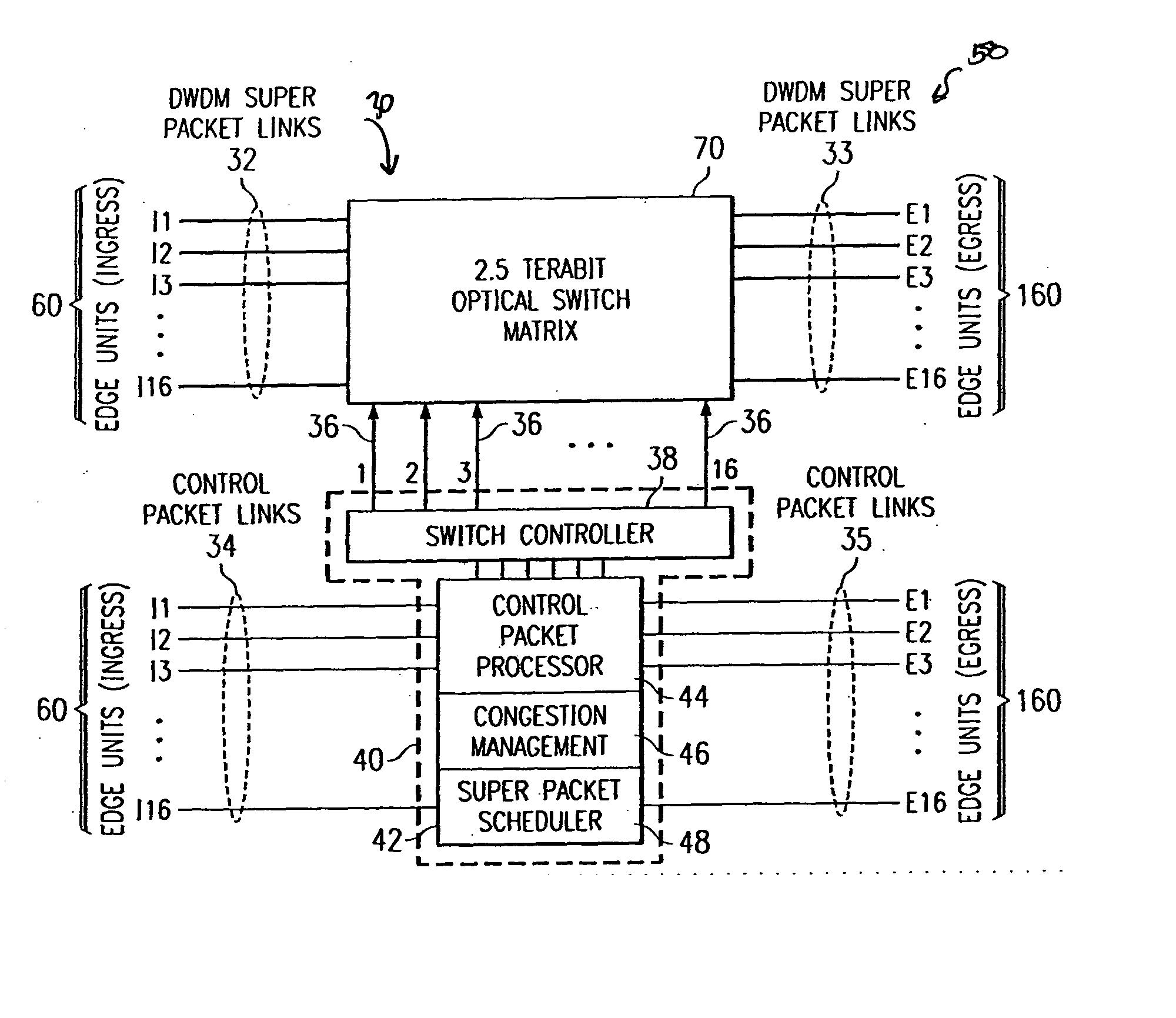

Apparatus and method for optical switching at an optical switch fabric

InactiveUS20060083460A1Increasing router/switch capacityImprove scalabilityMultiplex system selection arrangementsCoupling light guidesPath switchingOptical switch

Embodiments of the present invention provide a system and method for providing non-blocking routing of optical data through an optical switch fabric. The optical switch fabric can include an optical switching matrix with a plurality of inputs intersecting with a plurality of outputs. A path switch can be located at each intersection that is operable to switch data arriving on an input to a particular output. The path switches can be configurable to create a plurality of unique paths through the optical switching matrix to allow routing in a non-blocking manner. Another aspect of the present invention can provide a system and method for providing non-blocking routing through an optical cross-bar switch. The optical cross-bar switch includes a plurality of input links, a plurality of output links and a plurality of switching elements. Each switching element can include a plurality of path switches connecting each of the input links to at least one of the output links and the plurality of switching elements can be configured to create a plurality of unique paths through the optical cross-bar switch.

Owner:UNWIRED BROADBAND INC

Memory module and method having on-board data search capabilities and processor-based system using such memory modules

InactiveUS20050146943A1Faster rateDigital data information retrievalDigital storageCrossbar switchWrite buffer

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory interfaces coupled to respective memory devices, and a cross-bar switch coupling any of the link interfaces to any of the memory interfaces. Each memory interface includes a memory controller, a write buffer, a read cache, and a data mining module. The data mining module includes a search data memory that is coupled to the link interface to receive and store at least one item of search data. A comparator receives both the read data from the memory device and the search data. The comparator then compares the read data to the respective item of search data and provides a hit indication in the event of a match.

Owner:JEDDELOH JOSEPH M

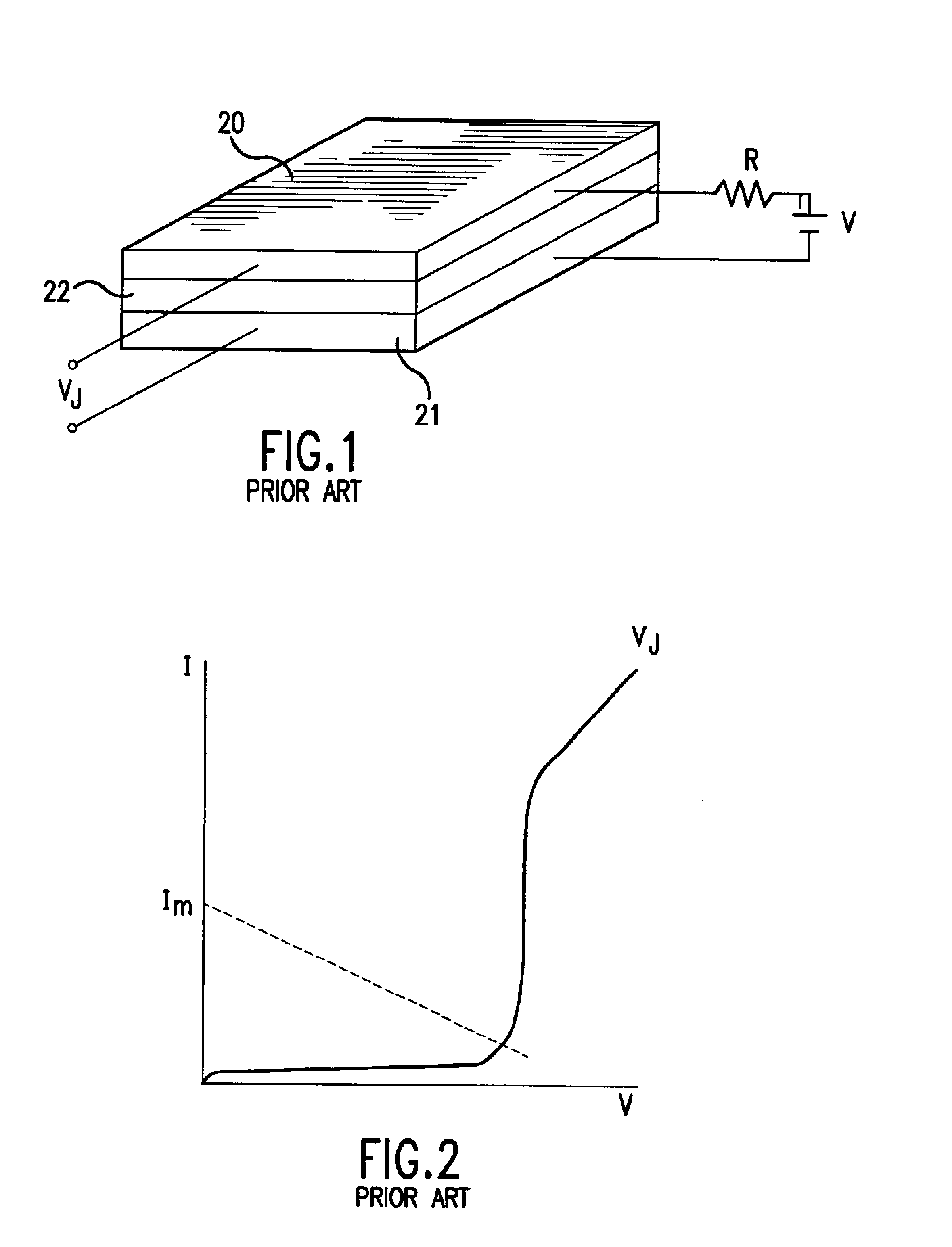

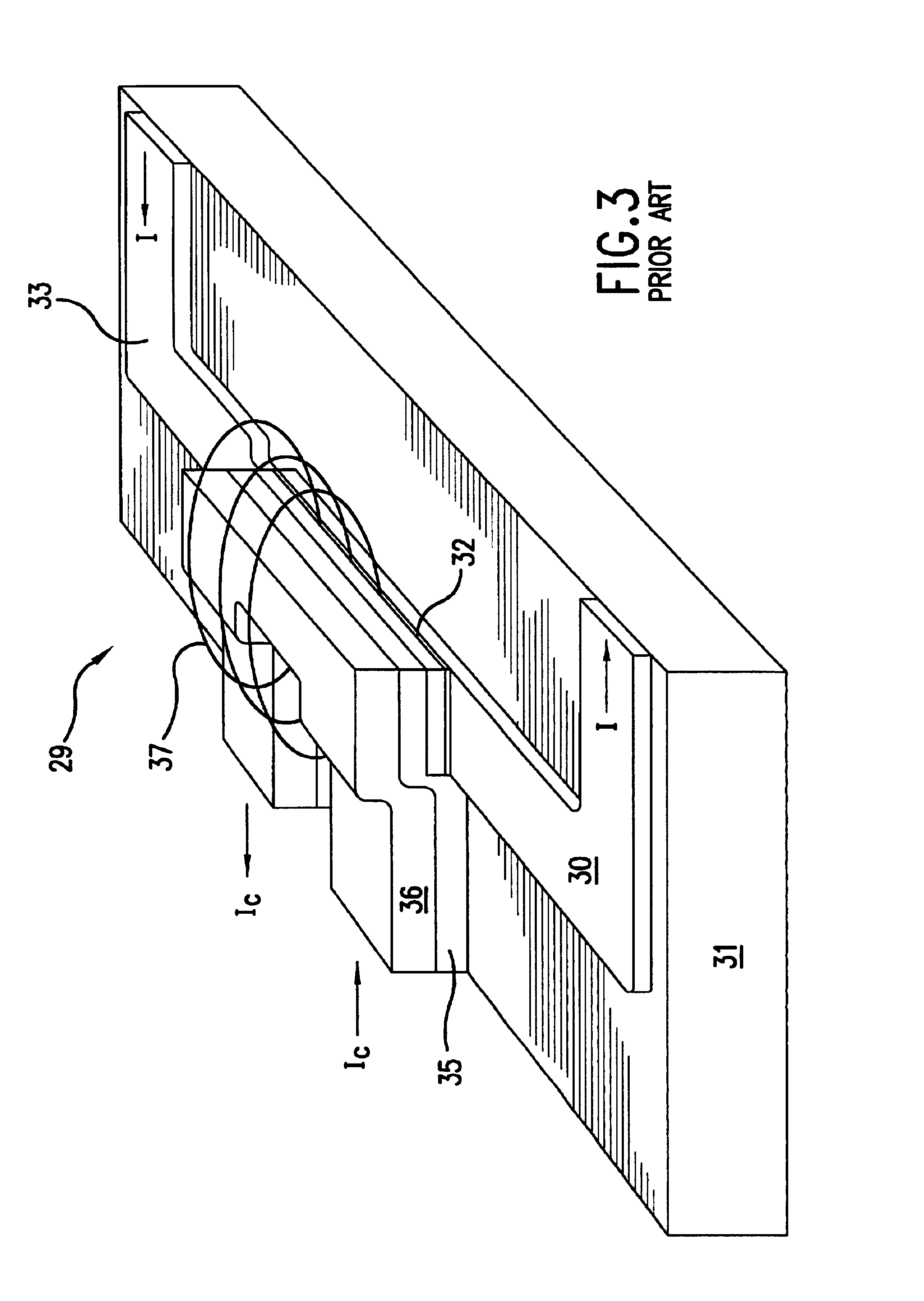

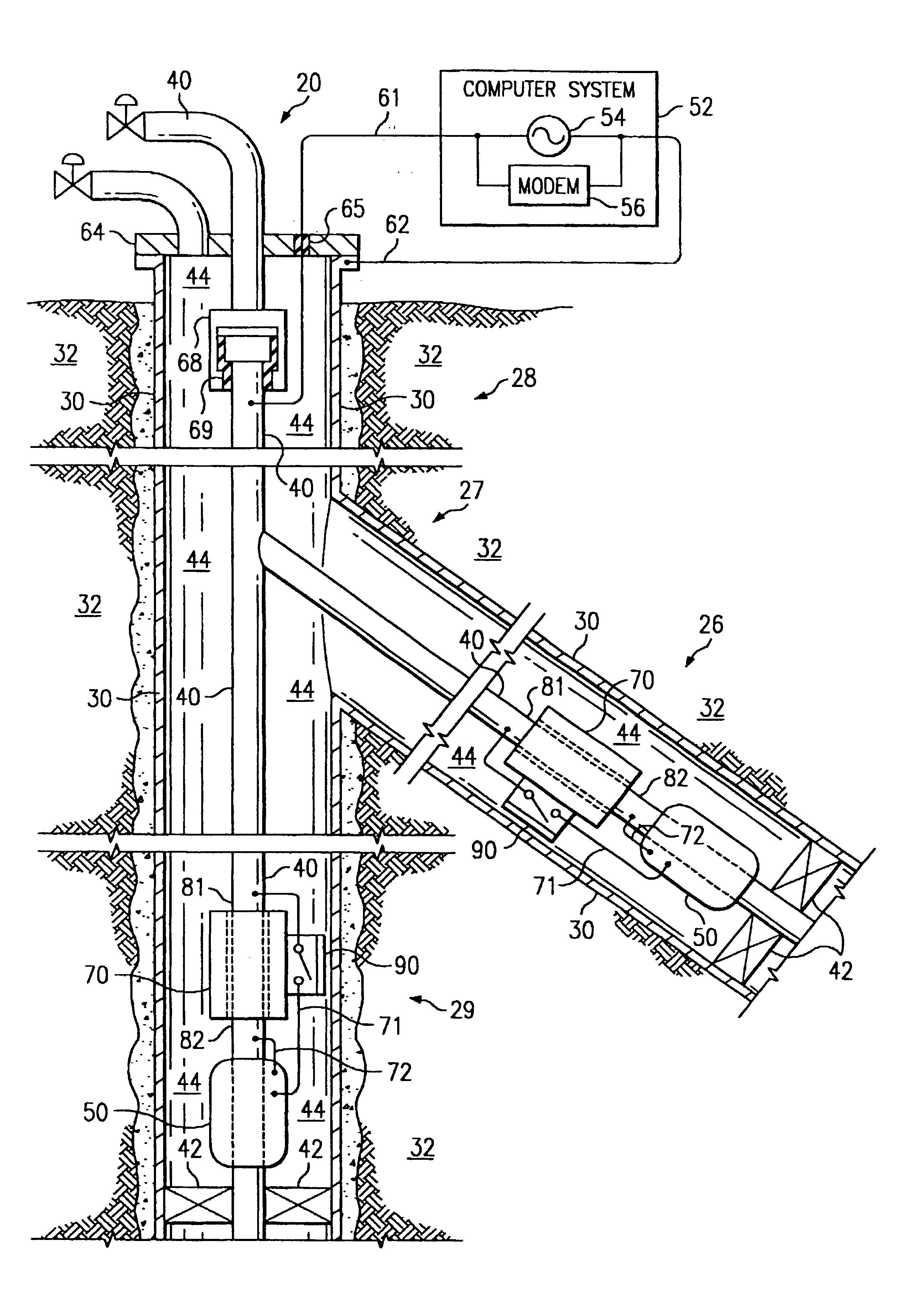

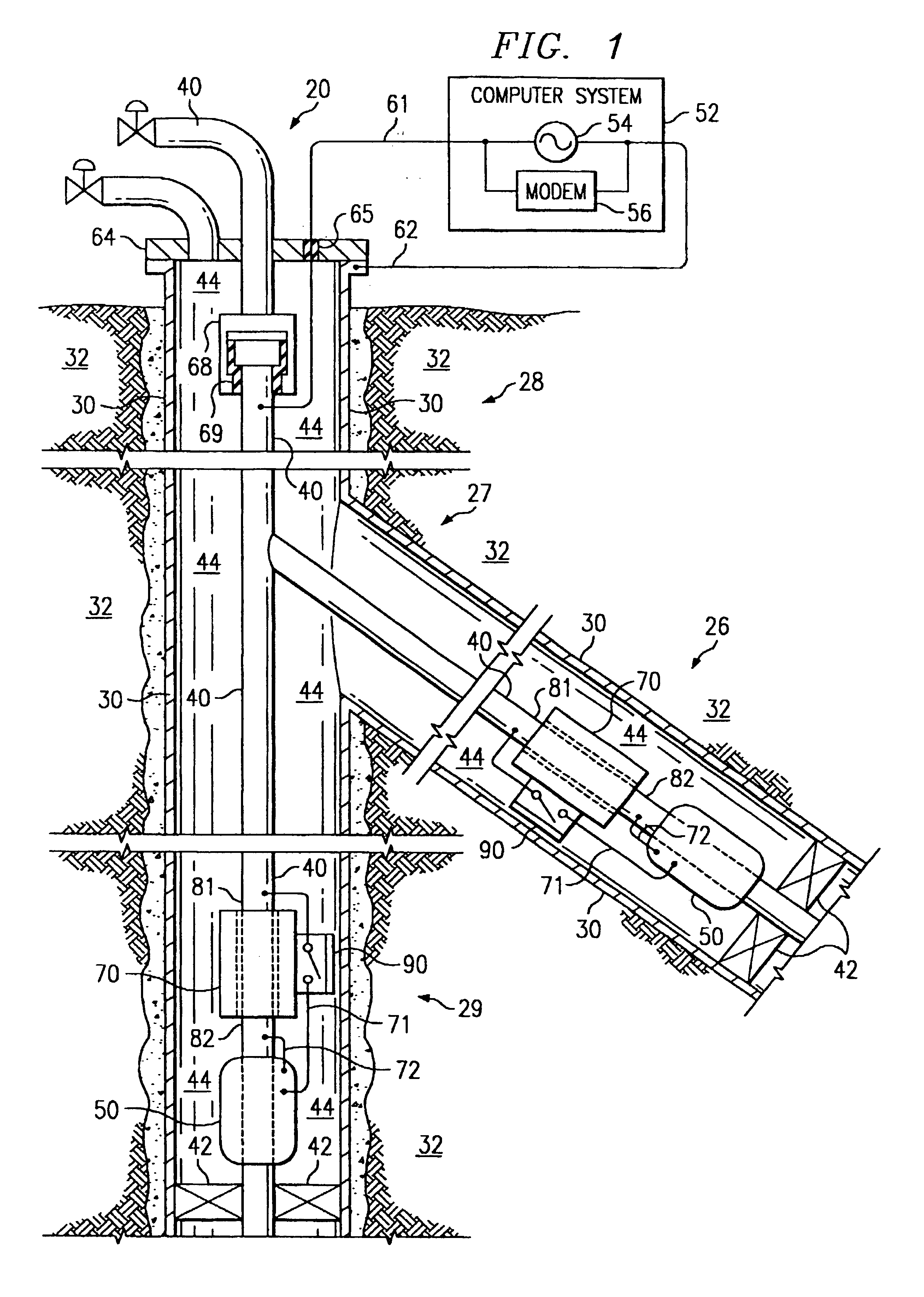

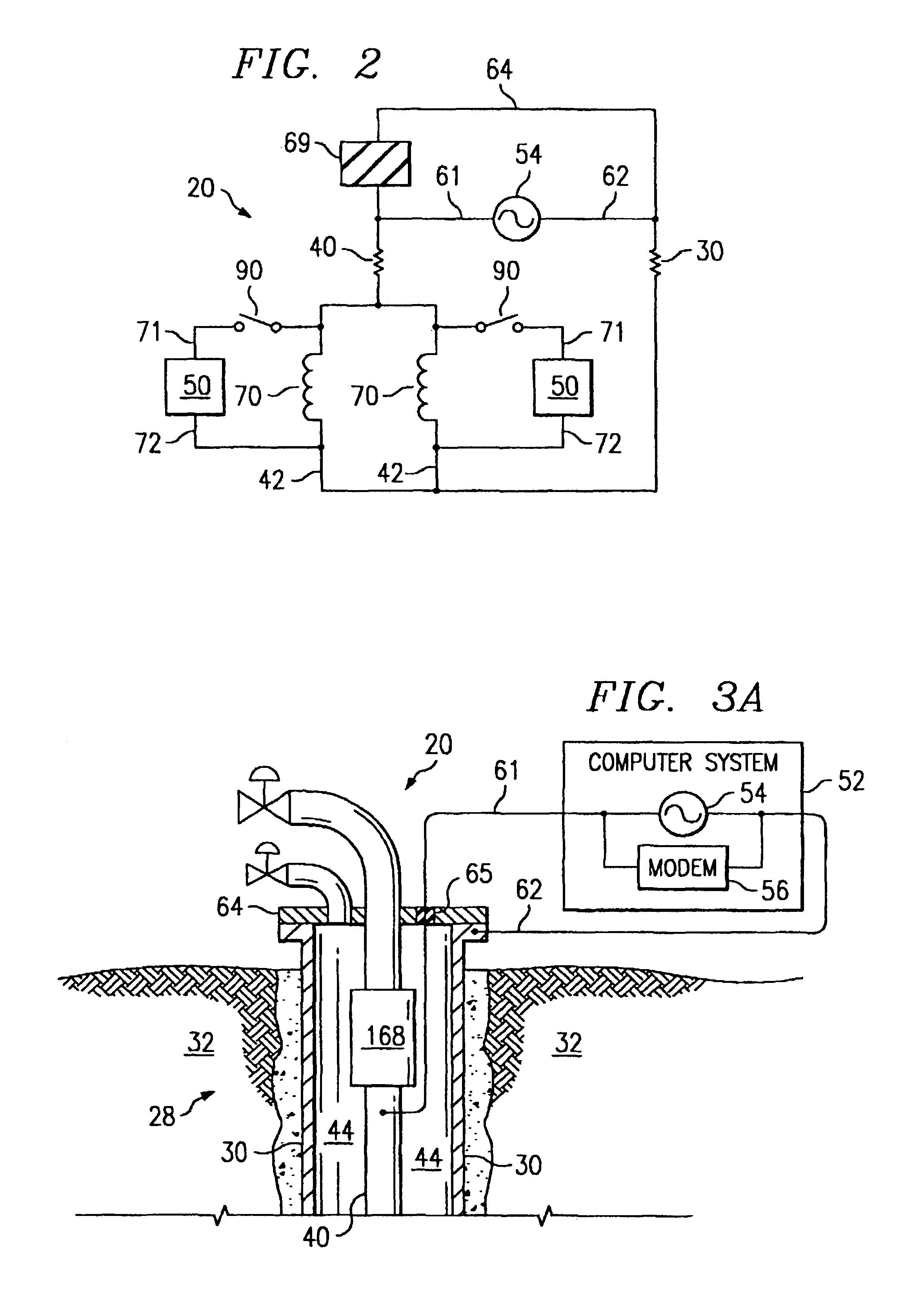

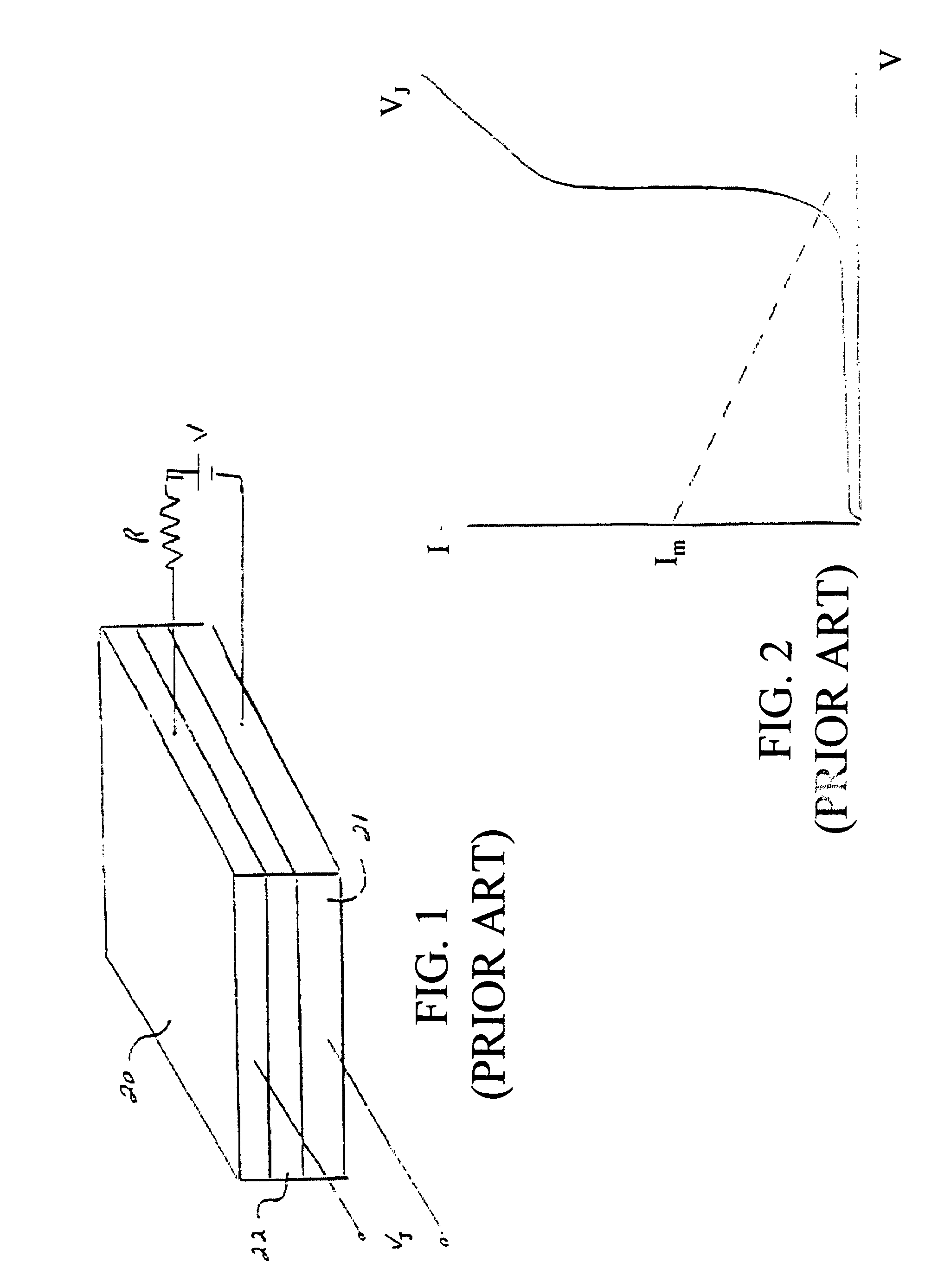

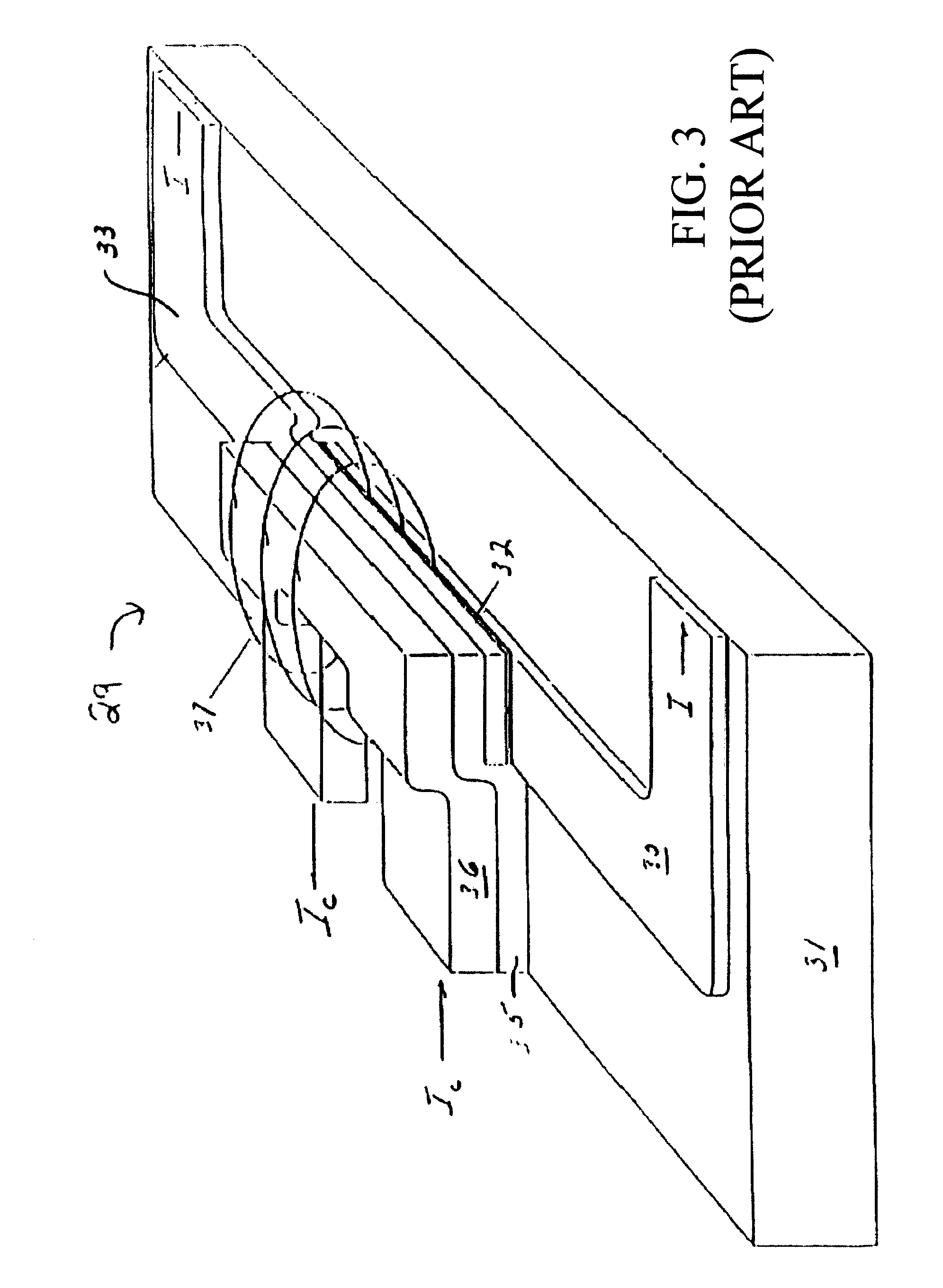

Wireless power and communications cross-bar switch

A petroleum well for producing petroleum products that incorporates a system adapted to controllably route communications and / or electrical power having a time-varying current through a piping structure in the well, and methods of producing petroleum products use such a well, are provided by the present invention. The system comprises a first induction choke, a second induction choke, and a controllable switch. The first induction choke is located about a portion of a first branch of the piping structure. The second induction choke is located about a portion of a second branch of the piping structure. The controllable switch having two switch terminals. A first of the switch terminals I is electrically connected to the piping structure on a junction side of the induction chokes. The first and second branches of the piping structure intersect on the junction side of the induction chokes. A second of the switch terminals is electrically connected to the piping structure on another side of at least one of the induction chokes.

Owner:SHELL OIL CO

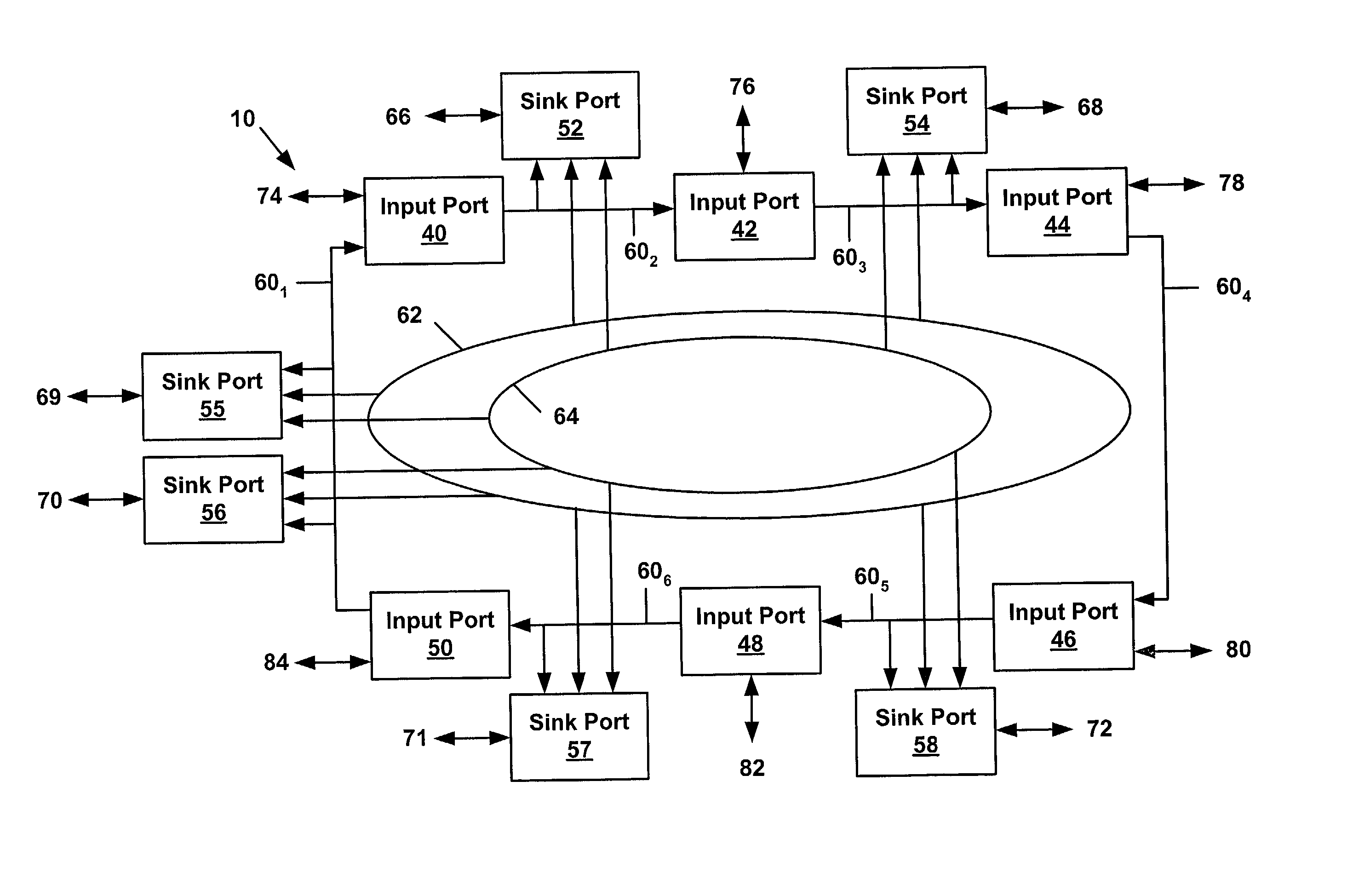

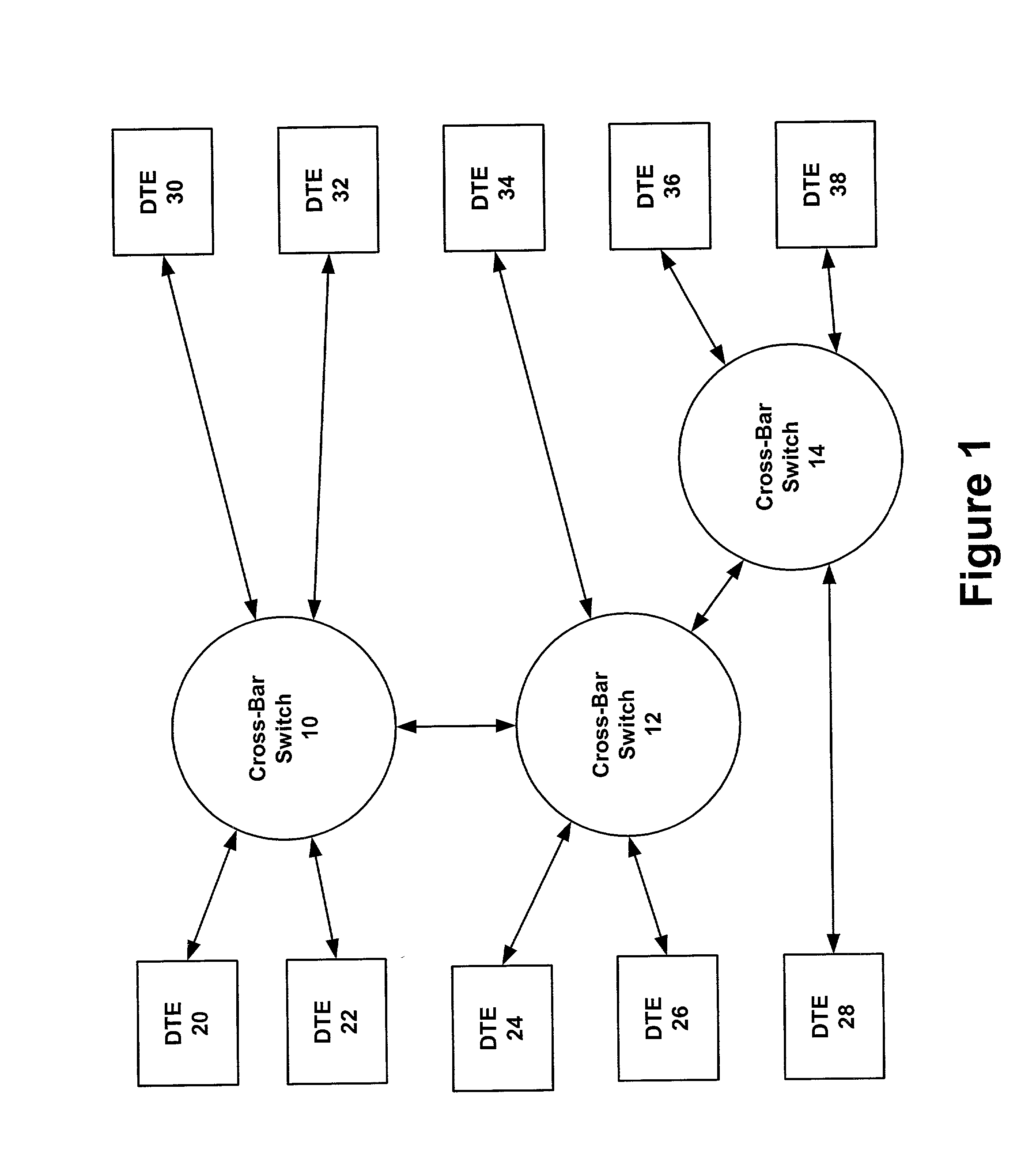

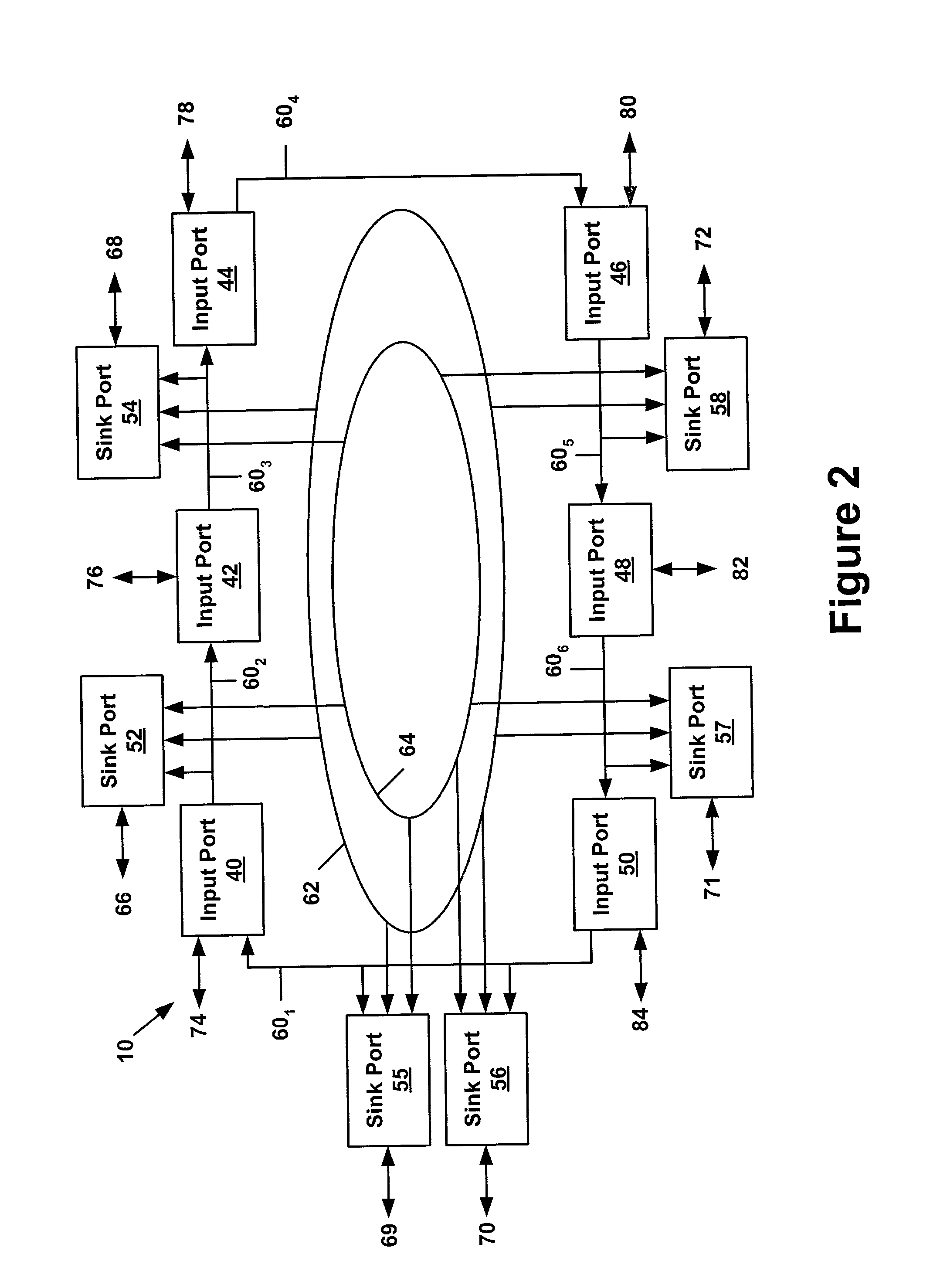

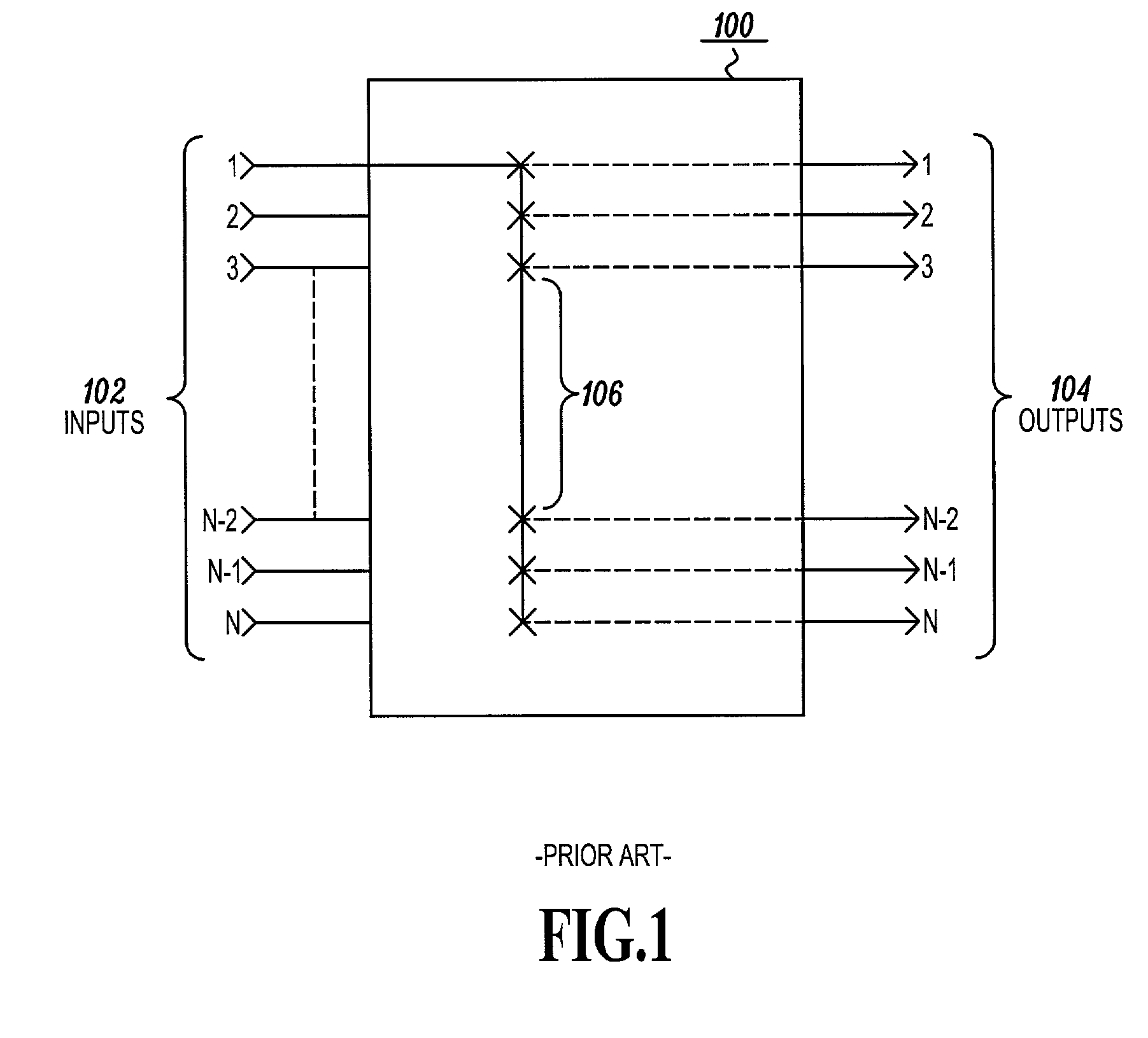

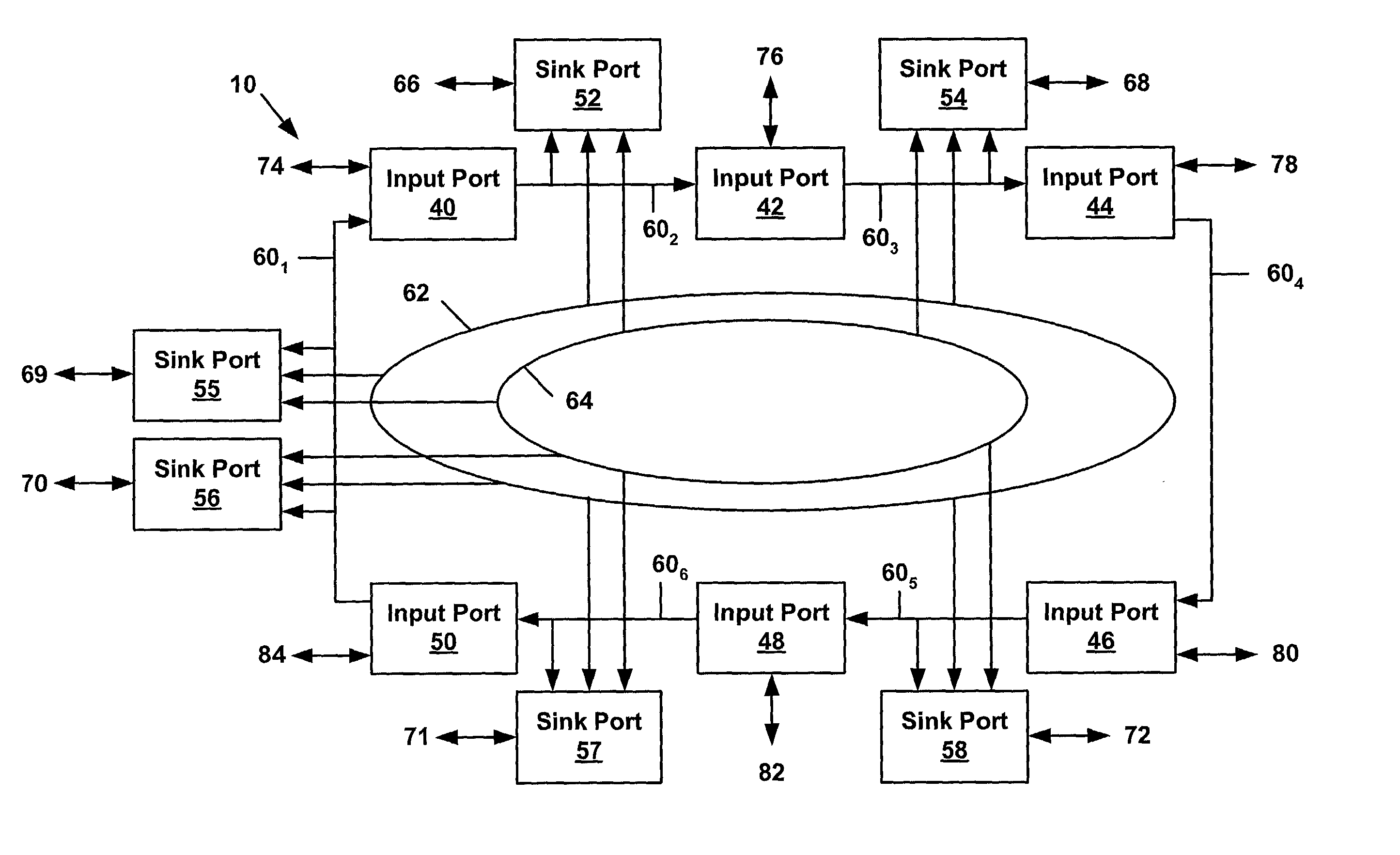

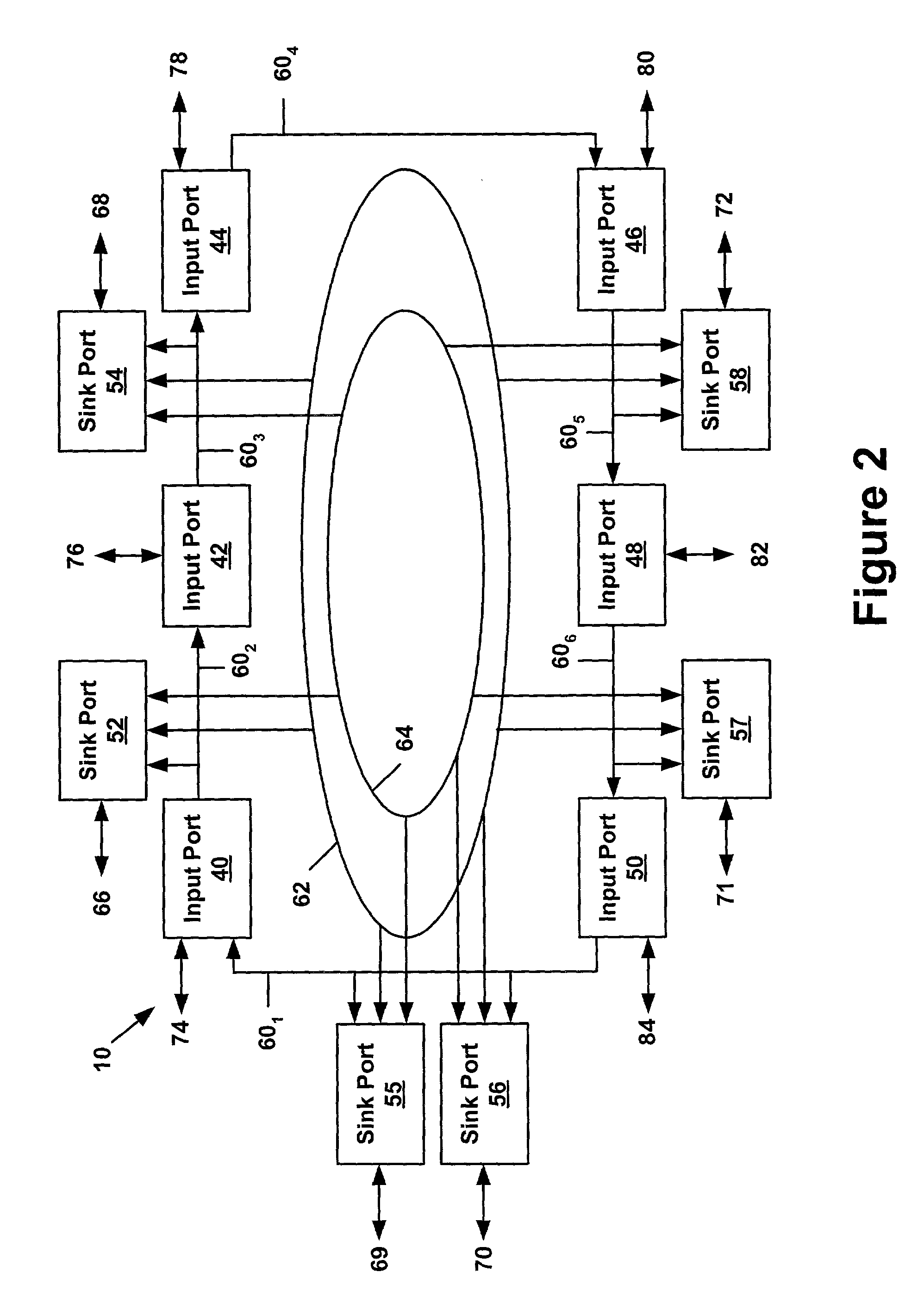

Cross-bar switch

InactiveUS7068603B2Less powerLess spaceFrequency-division multiplex detailsError preventionCrossbar switchNetwork packet

A cross-bar switch includes a set of input ports for receiving data packets and a set of sink ports for transmitting the received packets to identified targets. A set of data rings couples the input ports to the sink ports. Each sink port utilizes the set of data rings to simultaneously accept multiple data packets targeted to the same destination—creating a non-blocking cross-bar switch. Sink ports are also each capable of supporting multiple targets—providing the cross-bar switch with implicit multicast capability.

Owner:NEXSI SYSTEMS CORP

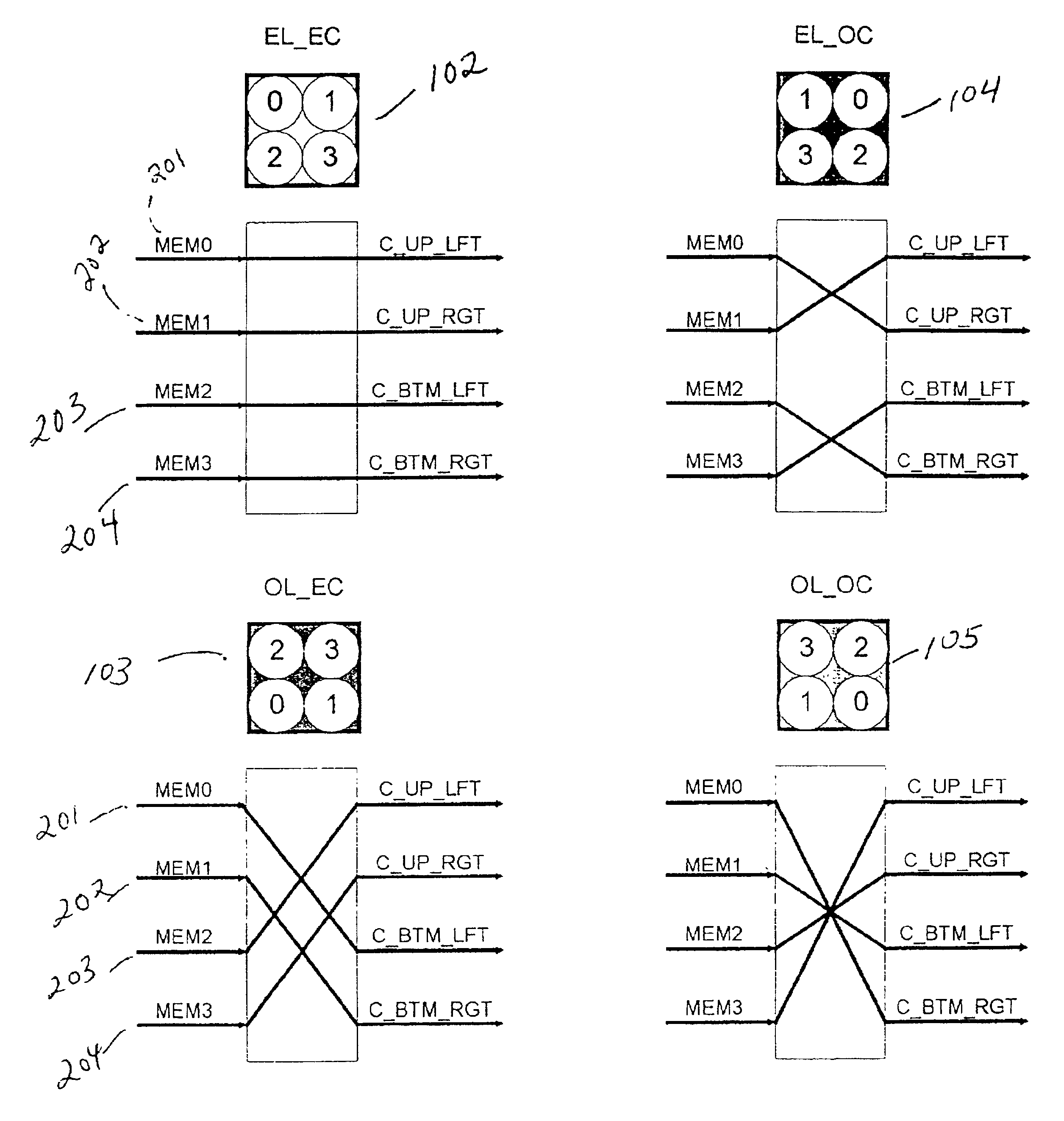

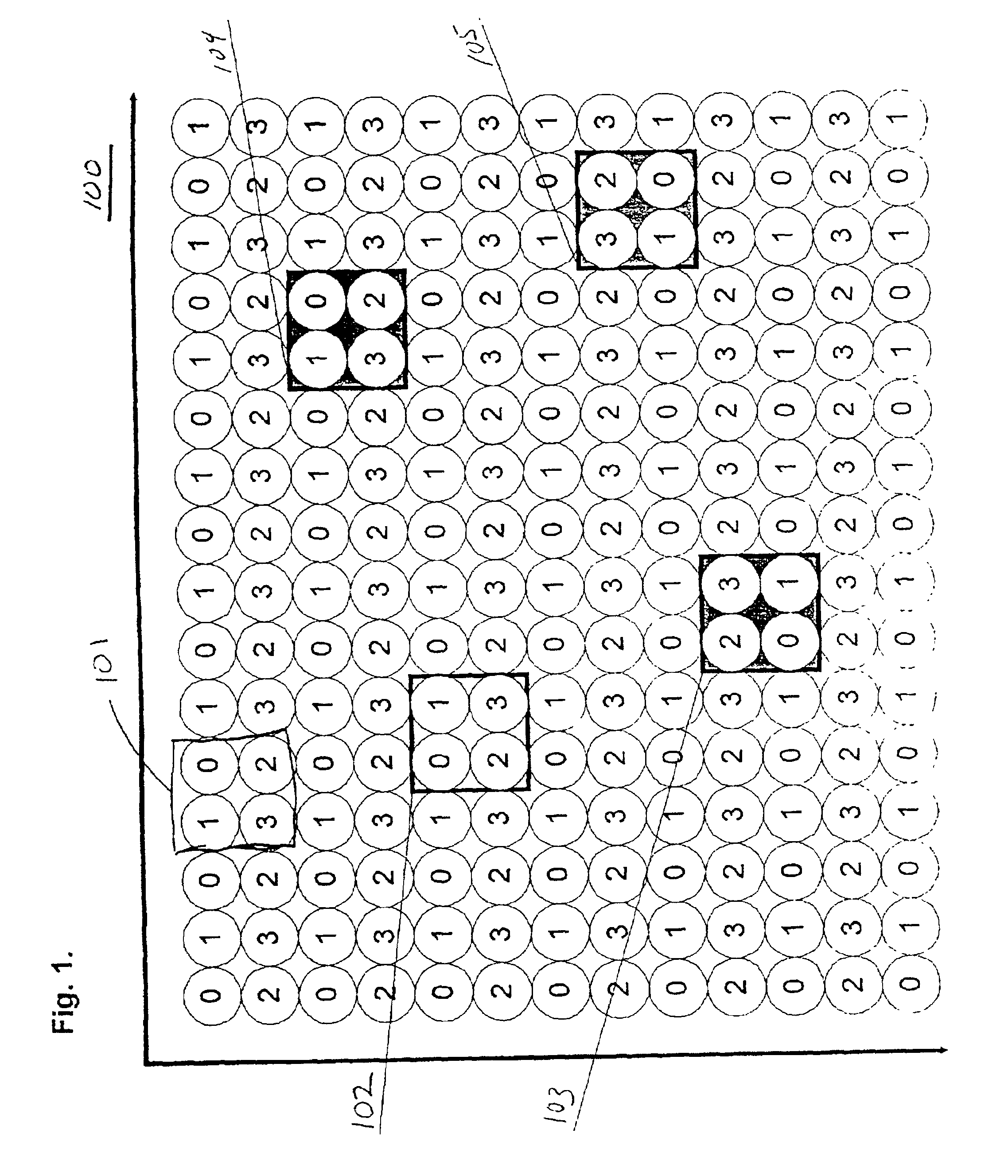

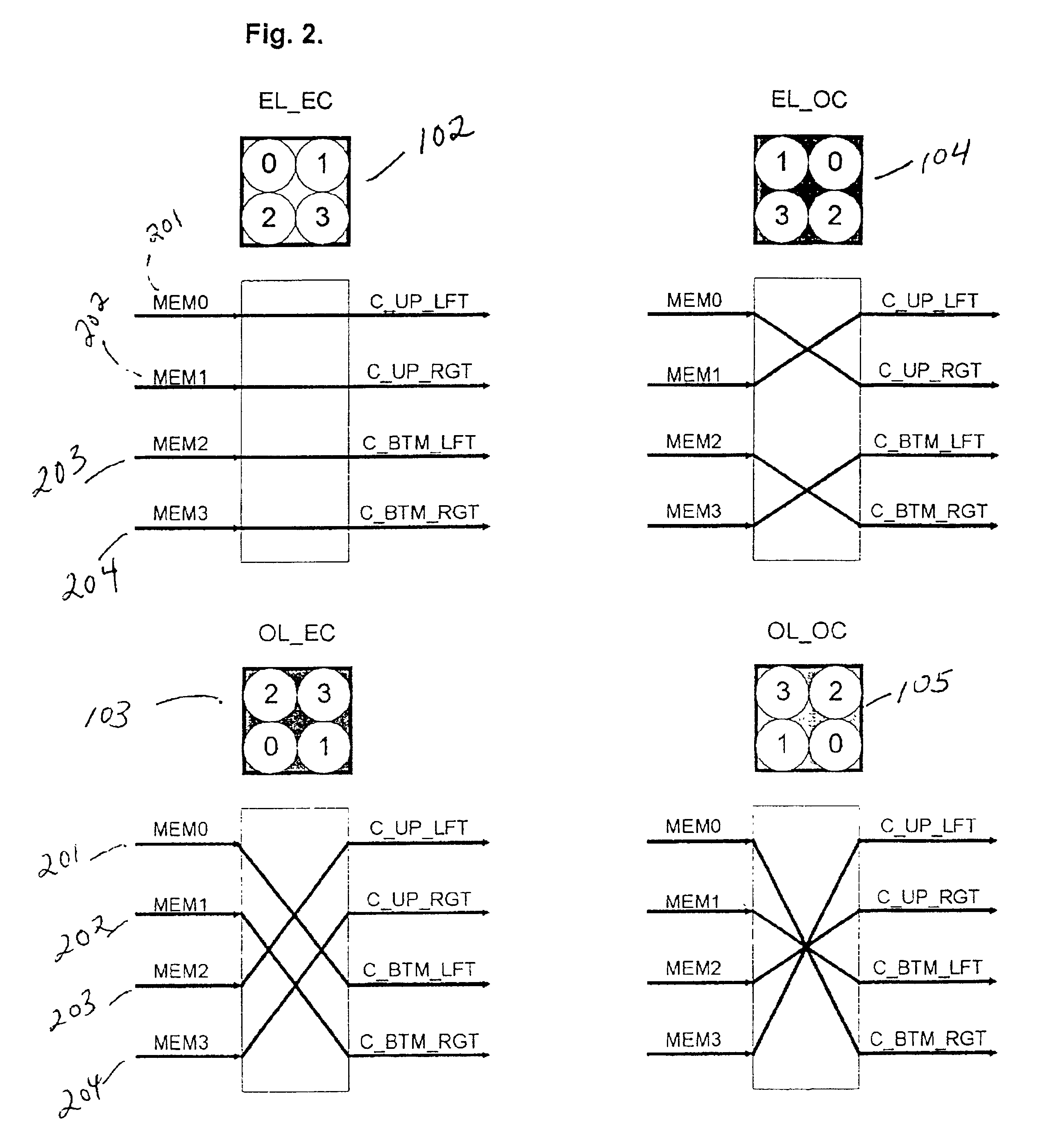

Color non-uniformity correction method and apparatus

InactiveUS6844883B2Increase the number of colorsIncrease the number ofTelevision system detailsColor signal processing circuitsAlgorithmCorrection method

A method of correcting a video signal includes retrieving a correction data from a respective one multiple memory devices; reordering the correction data to a predetermined order for a particular segment; and interpolating multiple correction data so that all pixels in the particular segment have a corresponding one of the correction data. An apparatus for correcting video comprises multiple memory devices, each having multiple correction data; a cross-bar switch that reorders at least some of the data to a predetermined order for a particular segment; and an interpolator that calculates multiple interpolated correction data. One of the correction data corresponds to one of multiple pixels in the segment.

Owner:FUNAI ELECTRIC CO LTD

Memory module and method having on-board data search capabilities and processor-based system using such memory modules

InactiveUS20050146944A1Faster rateDigital data information retrievalDigital storageCrossbar switchWrite buffer

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory interfaces coupled to respective memory devices, and a cross-bar switch coupling any of the link interfaces to any of the memory interfaces. Each memory interface includes a memory controller, a write buffer, a read cache, and a data mining module. The data mining module includes a search data memory that is coupled to the link interface to receive and store at least one item of search data. A comparator receives both the read data from the memory device and the search data. The comparator then compares the read data to the respective item of search data and provides a hit indication in the event of a match.

Owner:JEDDELOH JOSEPH M

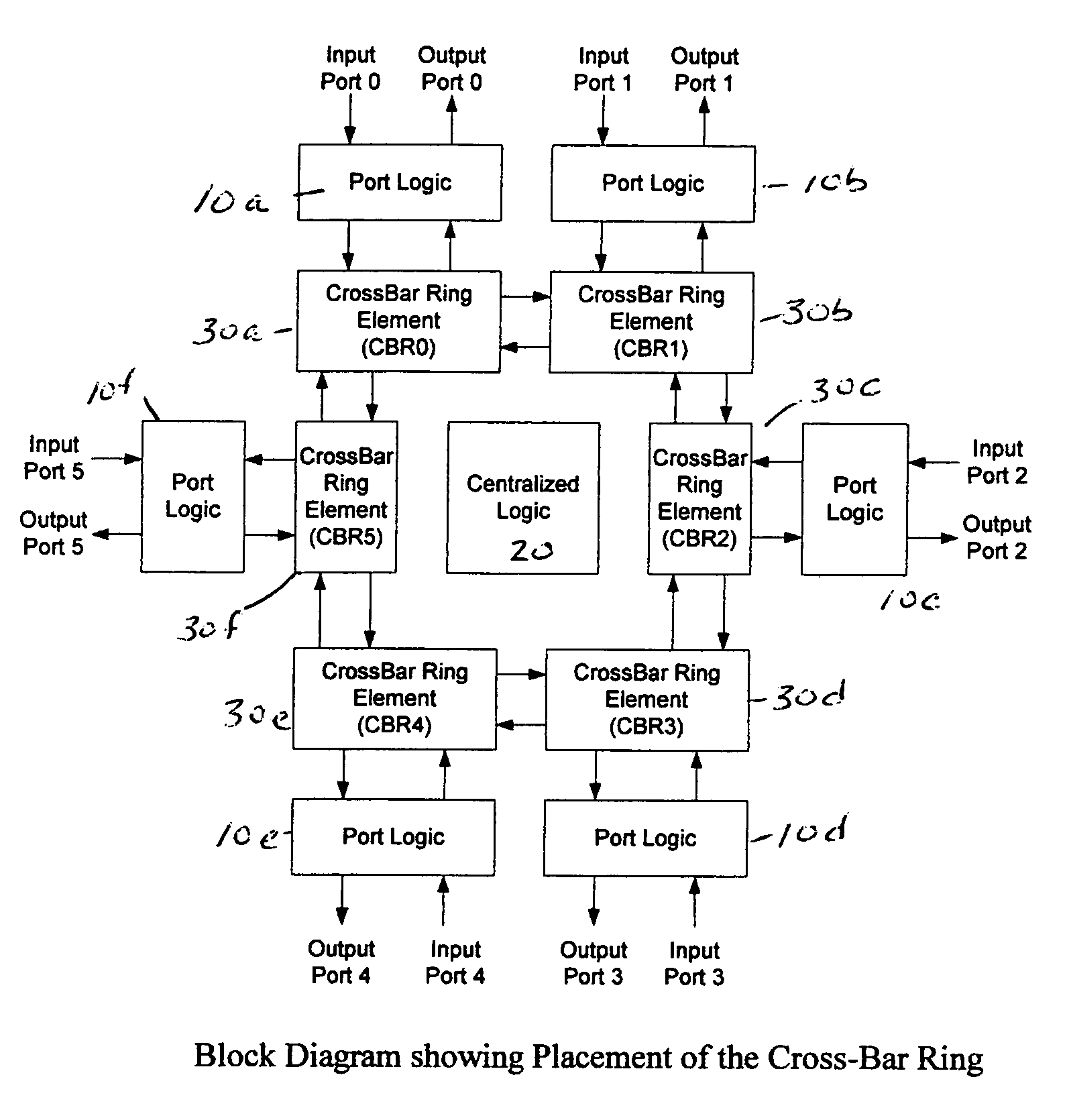

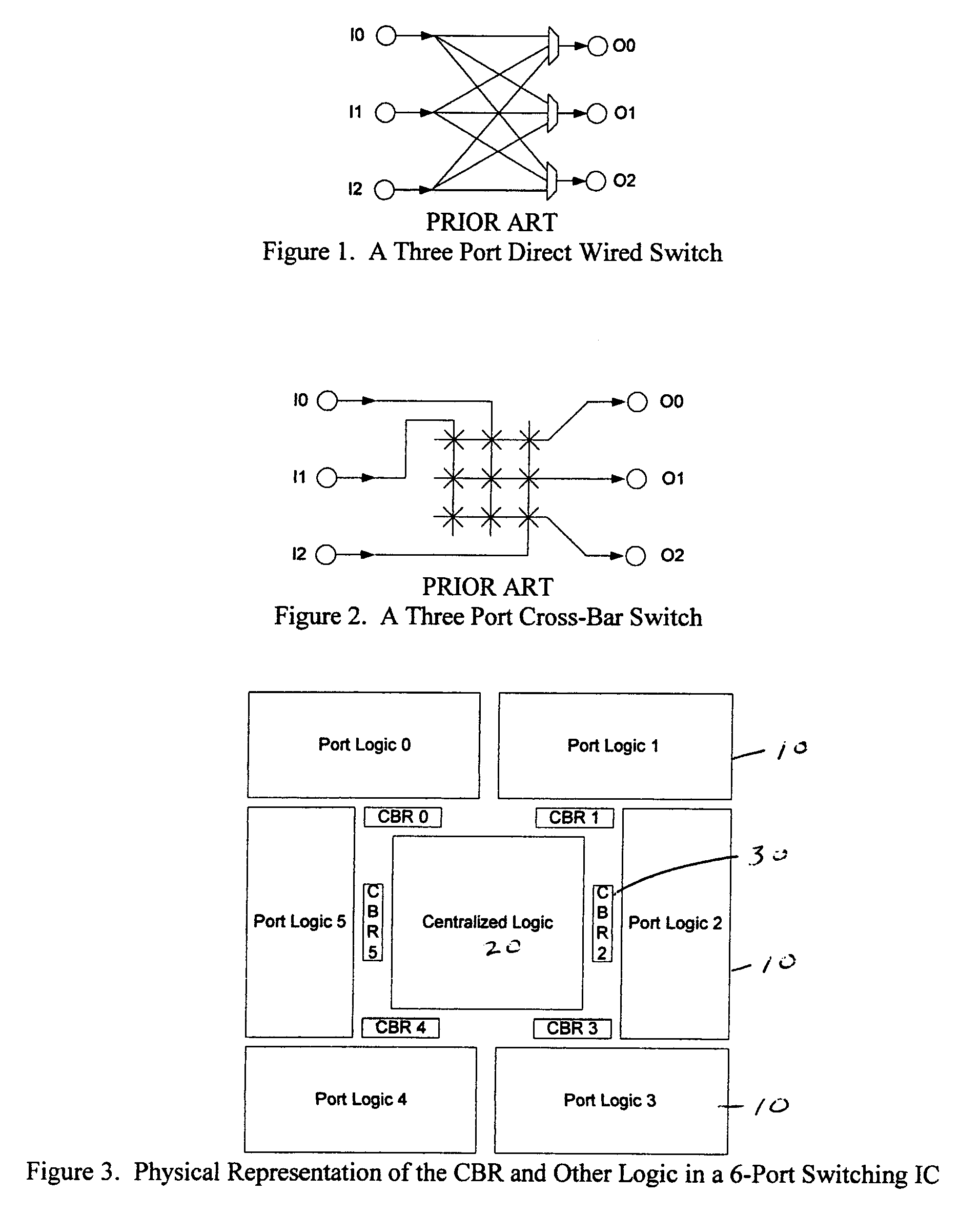

Communication mechanism

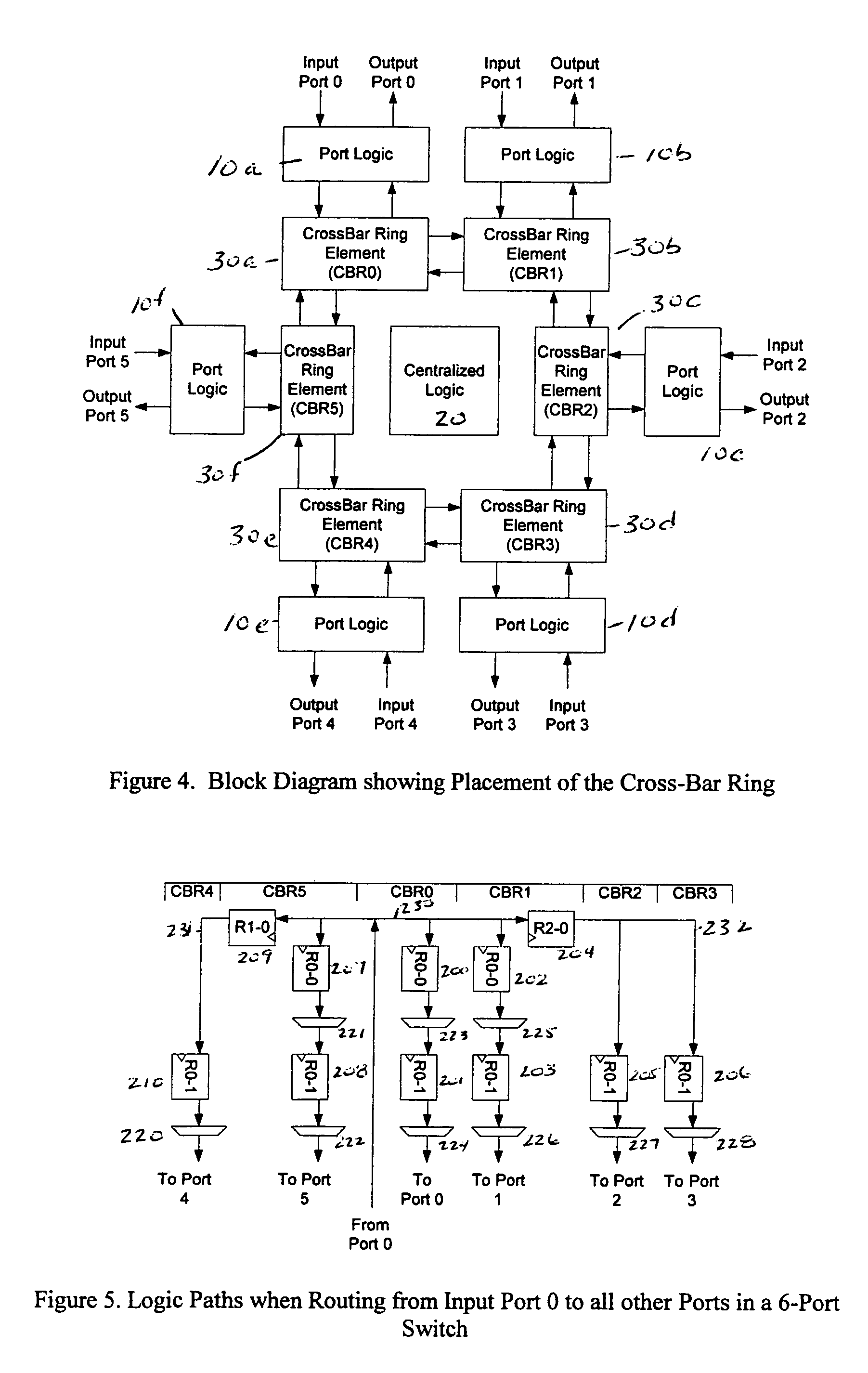

ActiveUS7155557B2Improve distributionAid in placement and routingTransmissionMemory systemsEngineeringSemiconductor

The invention provides an interconnection architecture for semiconductor devices. Cross bar switches are traditionally placed in the center of the IC. However, this location may also be the preferred location for the centralized logic in the IC. This invention, known as a cross bar ring or CBR, provides cross bar switch functionality in a manner that can be easily distributed around the chip. Typically, it can fit in the routing channels between other functional blocks, thereby allowing other centralized functions to be placed in the center of the IC. The CBR is defined so that it can be partitioned into separate modules, which greatly aids in the placement and routing of wires. Furthermore, the architecture is defined such that the CBR can use storage elements, allowing it to be pipelined so that the wire distances can be increased while still maintaining a high internal clock speed. The use of storage elements also allows the CBR to provide a deterministic delay between any two locations on the IC, and can, if desired, insure a constant delay regardless of source and destination.

Owner:CALLAHAN CELLULAR L L C

Superconductive crossbar switch

InactiveUS7459927B2Lower latencyDetects and resolve conflictMultiplex system selection arrangementsElectronic switchingCrossbar switchNanosecond

A superconductor crossbar switch for connecting a plurality of inputs with a plurality of outputs, including a switching cell having an input, an output and a circuit for connecting the input with the output for bidirectionally transmitting data therebetween. The connection of the retaining and releasing circuitry of a plurality of cells enables the switch to simultaneously retain a selected cell or cells of a group of cells and disable the remaining cells of that group, whereby a subsequent query on a disabled cell is inoperative until the selected cell or cells is released. The crossbar switch is characterized by latency on the order of nanoseconds, a data rate per channel on the order of gigabits per second, essentially zero crosstalk, and detection of contention in nanoseconds or less and resolution of contention in nanoseconds or less.

Owner:BEDARD FERNAND D

Cross-bar switch

A cross-bar switch includes a set of input ports for receiving data packets and a set of sink ports for transmitting the received packets to identified targets. A set of data rings couples the input ports to the sink ports. Each sink port utilizes the set of data rings to simultaneously accept multiple data packets targeted to the same destination-creating a non-blocking cross-bar switch. Sink ports are also each capable of supporting multiple targets-providing the cross-bar switch with implicit multicast capability.

Owner:NEXSI SYST

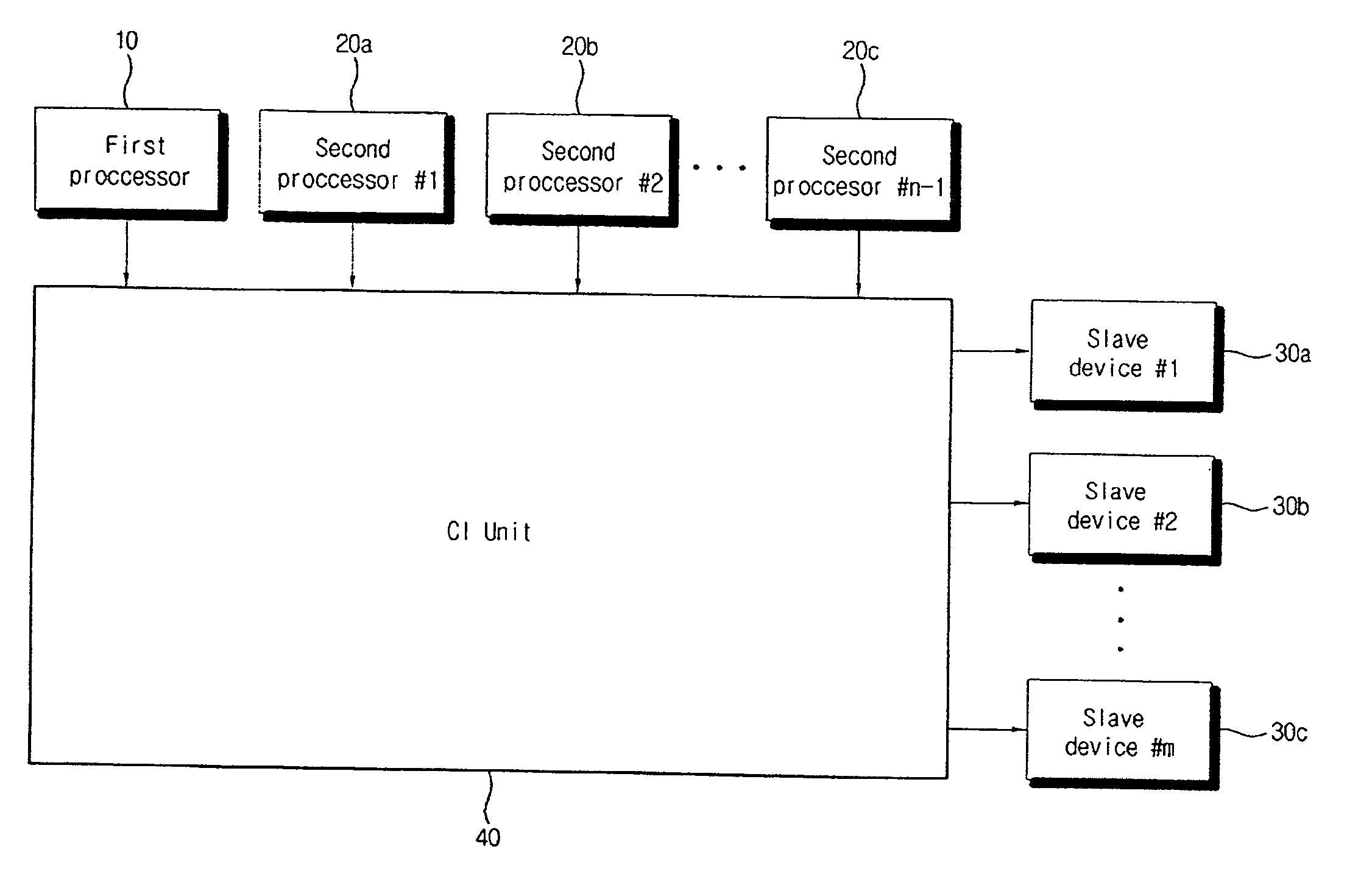

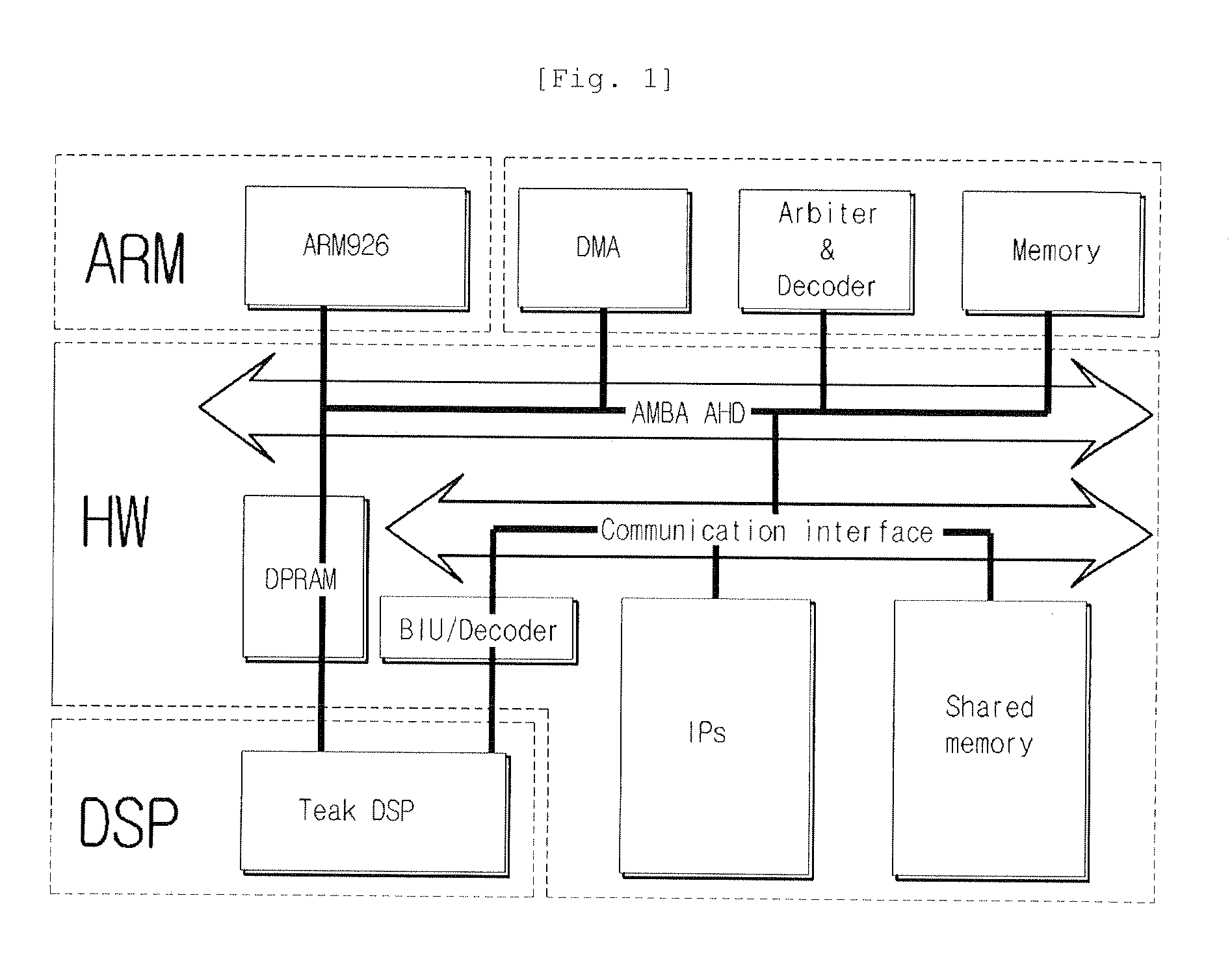

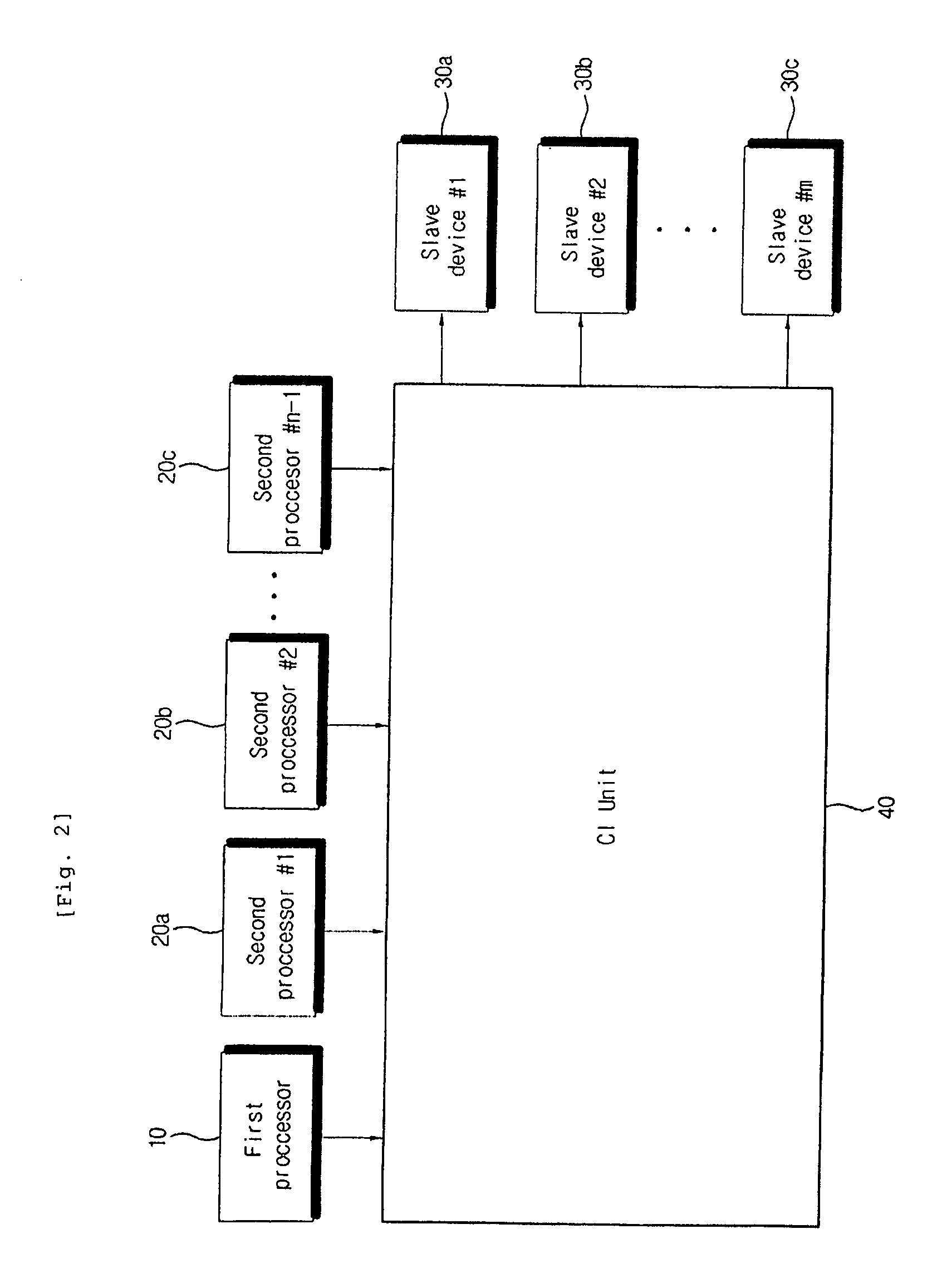

Multi-processor system on chip platform and dvb-t baseband receiver using the same

InactiveUS20090144480A1Speed up the calculation processIncrease speedDigital computer detailsElectric digital data processingCommunication interfaceBaseband receiver

A multi-processor system on chip (SoC) platform and a DVB-T baseband receiver using the same are disclosed. The multi-processor SoC platform includes a first processor, at least one second processor, at least one slave device communicating with the first processor and the second processor and a communication interface (CI) unit connecting the slave device to the first processor and the second processor according to a cross-bar switching method to allow the slave device to be communicated with the first processor and the second processor. Therefore, the multi-processor SoC platform having flexibility with being adapted for high speed calculation by using a cross-bar switch is provided.

Owner:CHO JUN DONG +5

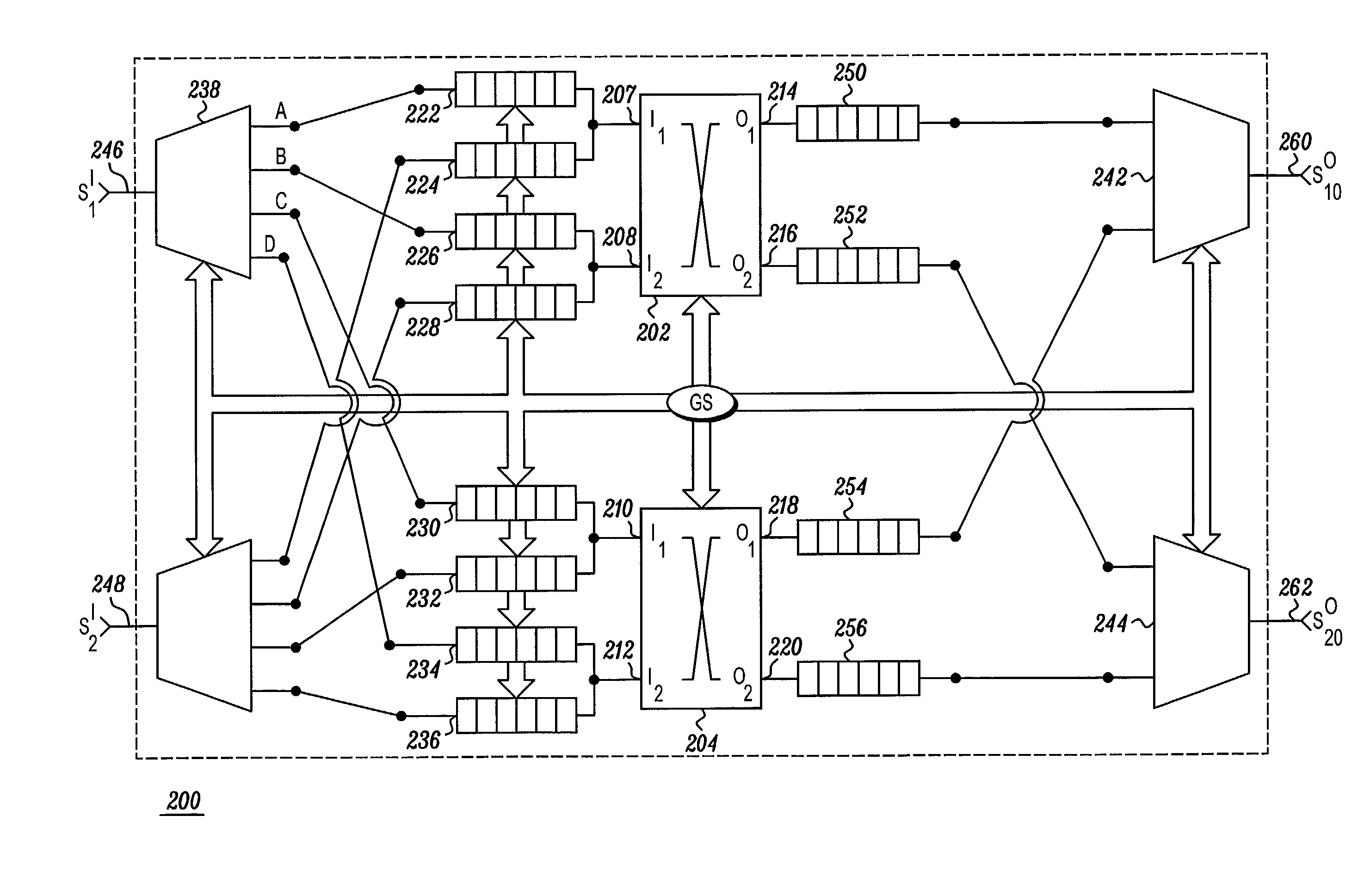

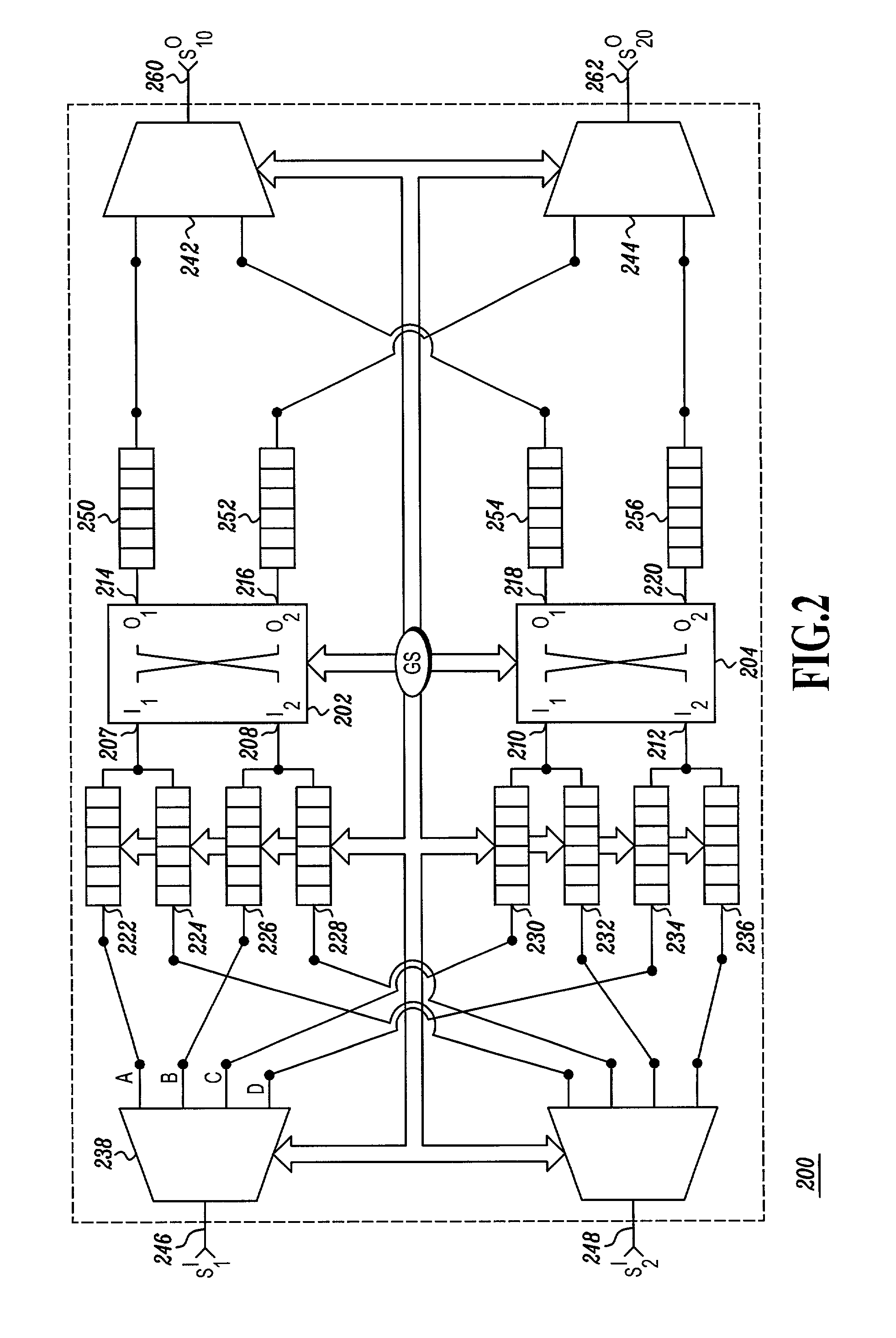

High-speed parallel cross bar switch

InactiveUS7123623B2Multiplex system selection arrangementsData switching by path configurationLow speedComputer science

Low speed switches operated under the common control of a global scheduler can be used to switch high speed data while preserving packet ordering if the incoming packets are queued in a temporal order. By operating several low speed switches in parallel, a high-speed switching capacity can be realized.

Owner:TELLABS OPERATIONS

Cross-bar switch supporting implicit multicast addressing

InactiveUS7065090B2Less powerLess spaceDigital computer detailsManual exchangesCrossbar switchNetwork packet

A cross-bar switch includes a set of input ports and a set of sink ports in communication with the input ports. The input ports receive packets, which are snooped by the sink ports. The cross-bar switch also includes a set of port address tables. Each port address table is adapted to store data identifying a plurality of destinations supported by a sink port. For example, a first port address table is adapted to identify a plurality of destinations supported by a first sink port in the set of sink ports. When determining whether to accept a packet, a sink port considers whether the packet's destination is identified in the sink port's port address table. By supporting multiple destinations, a port address table implicitly facilitates a sink port's multicast operation.

Owner:NEXSI SYST +1

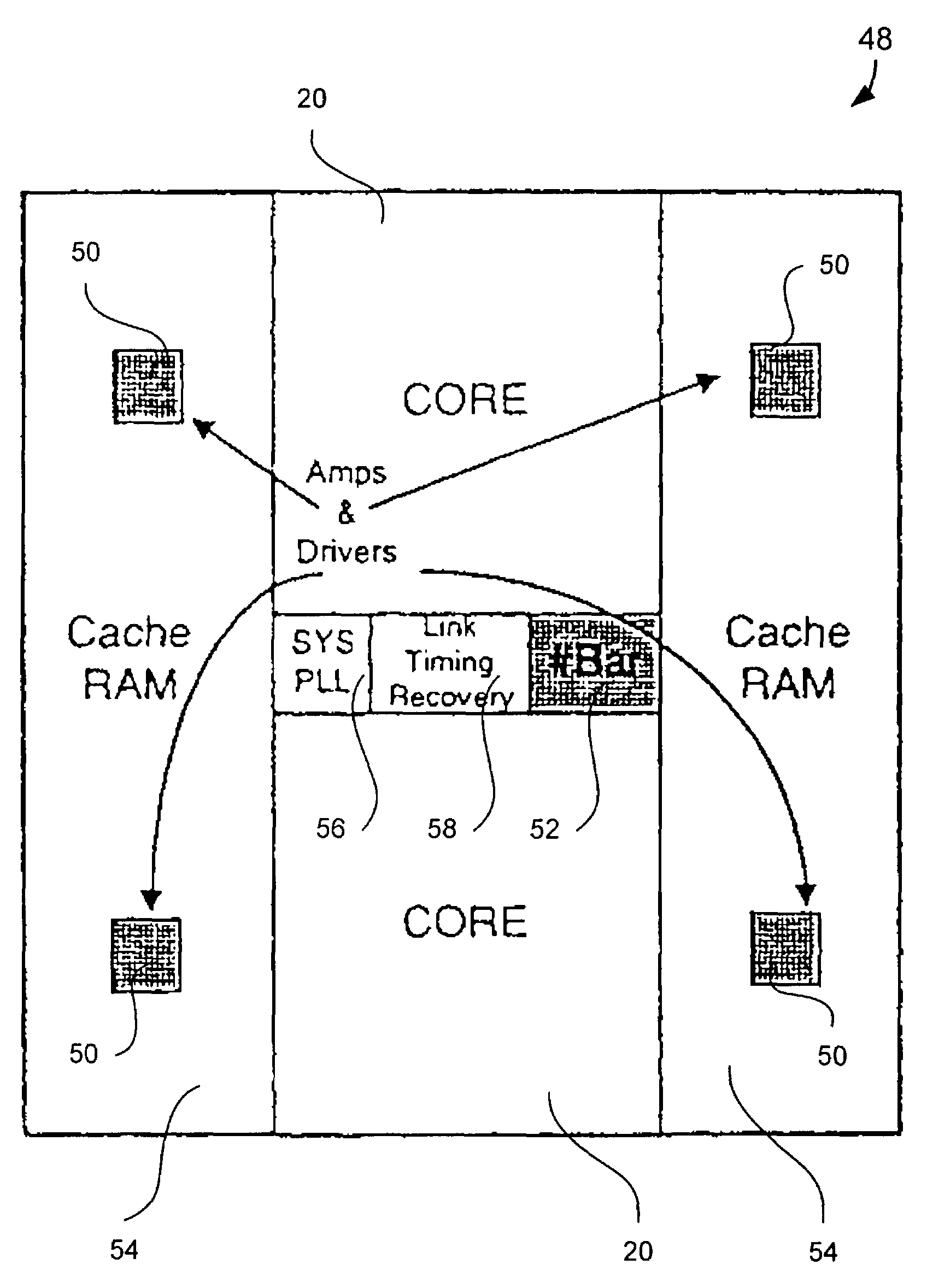

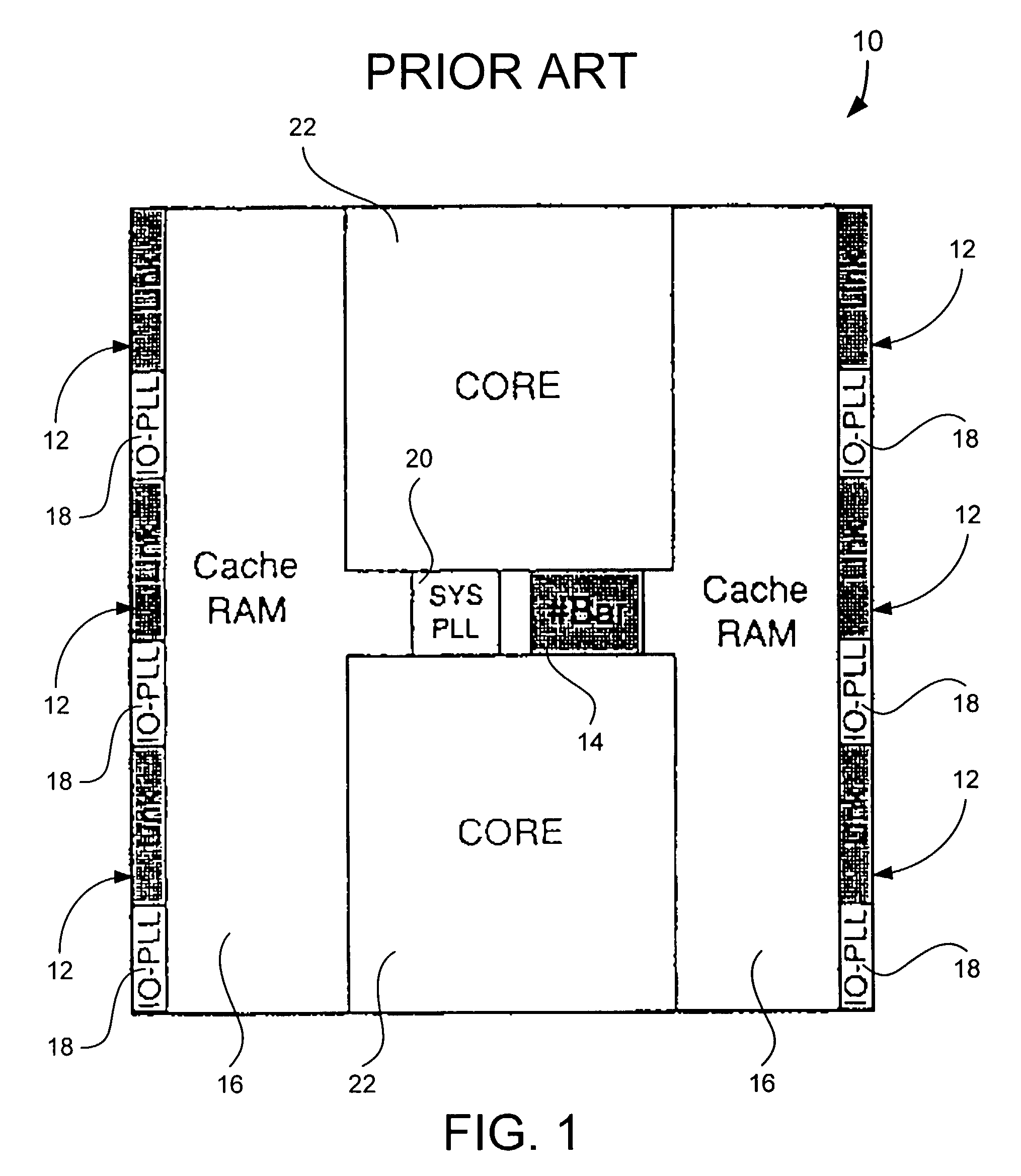

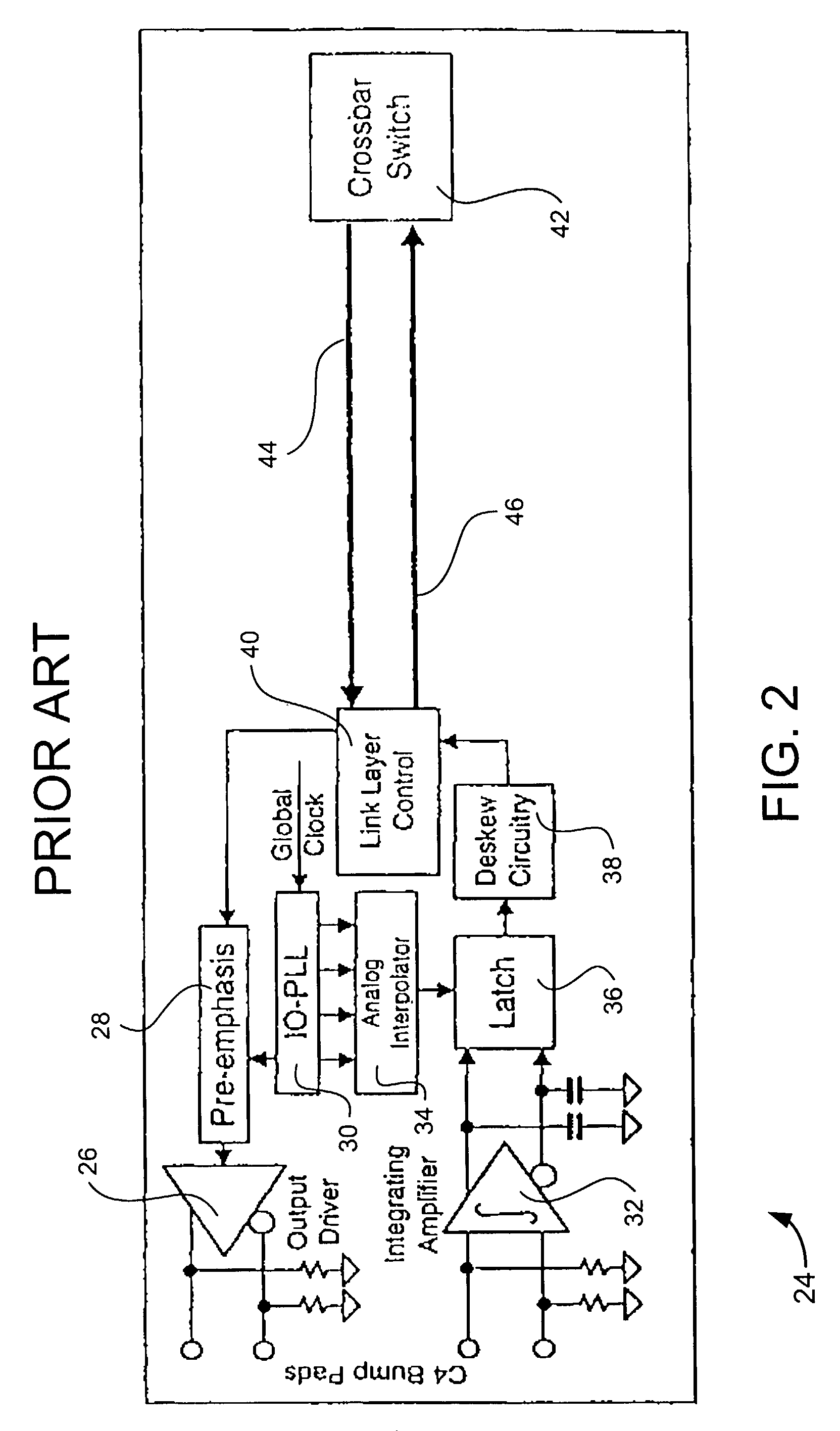

Distributed link module architecture

A link module architecture is disclosed for use with a multi-core central processing unit having a cross bar switch. The link module comprises timing recovery circuitry operably coupled to the central processing unit, wherein the timing recovery circuitry is positioned proximate to the cross bar switch. The link module further comprises a bit receiver operably coupled to the central processing unit, and a bit output driver operably coupled to the central processing unit. The bit receiver, preferably comprising a wide bandwidth amplifier, and the bit driver are preferably integrated with a sea of on-chip RAM.

Owner:HEWLETT PACKARD DEV CO LP