Reform buffer for vector data streams

A buffer and data stream technology, applied in electrical digital data processing, instruments, etc., to achieve the effect of reducing disturbance, convenient and flexible control interface, and improving access efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

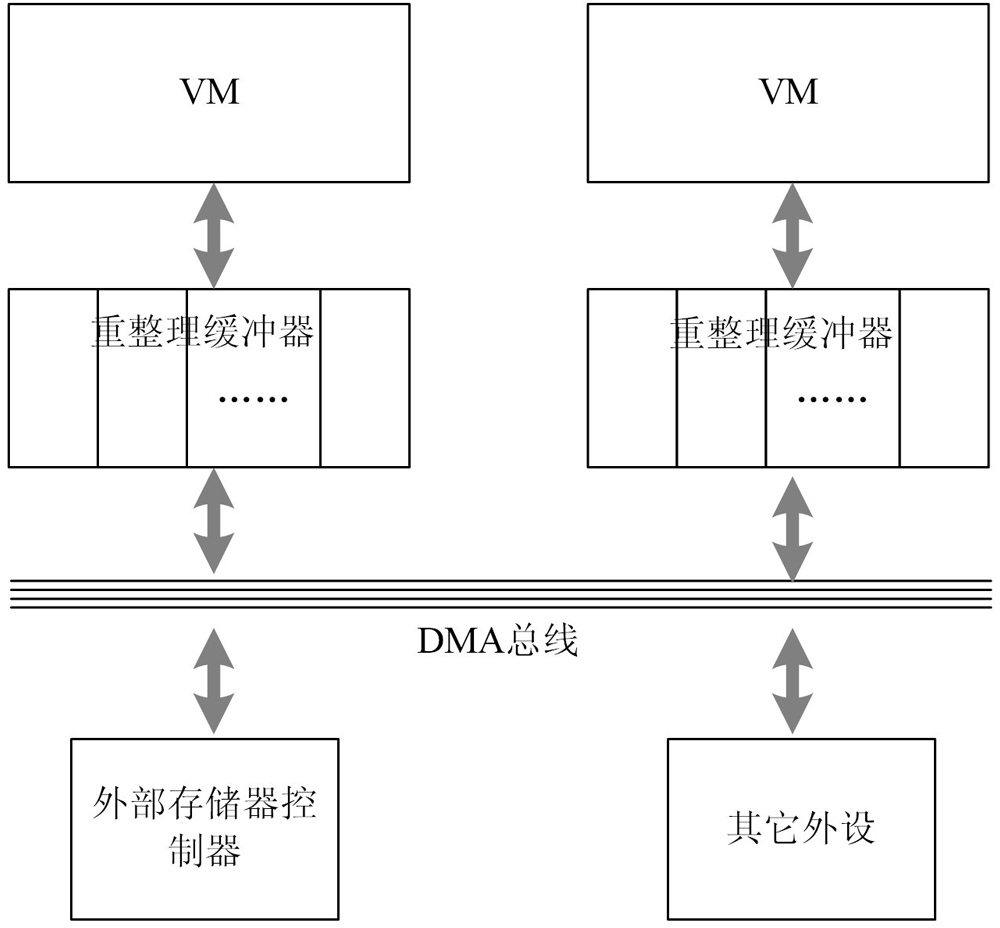

[0032] figure 1 It is a structural schematic diagram of a rearrangement buffer, a vector memory VM, and a DMA bus used for vector data streams in the present invention. The reorganization buffer of the present invention is located between the DMA bus and the VM. Multiple vector memories VM share the DMA bus with other storage units or peripherals, and there is a rearrangement buffer between each vector memory VM and the DMA bus. The read and write requests from DMA are first processed in the rearrangement buffer. When the read buffer or write buffer is not full, the vector memory VM will only be accessed when the data line is allocated to the buffer or the write buffer line is replaced. In this way It can not only make full use of the high bandwidth characteristic of the vector memory VM, but also reduce the interruption of the DMA ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com