Petri net model based ASIP (application specific instruction set processor) behavior logic synthesis method

A logic synthesis and model technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as verification, debugging difficulty, design difficulty and cycle increase.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

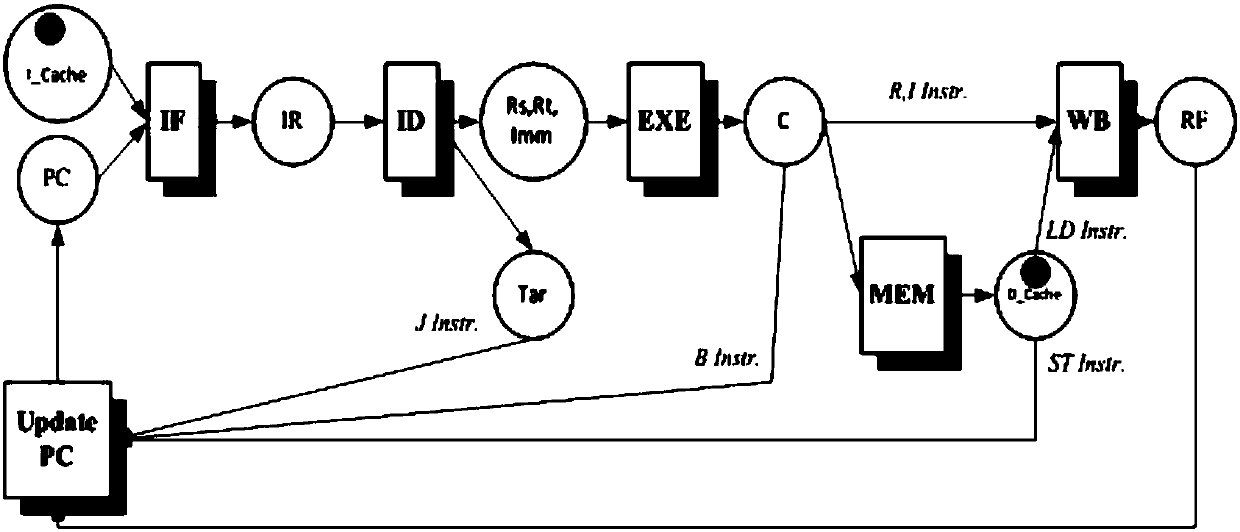

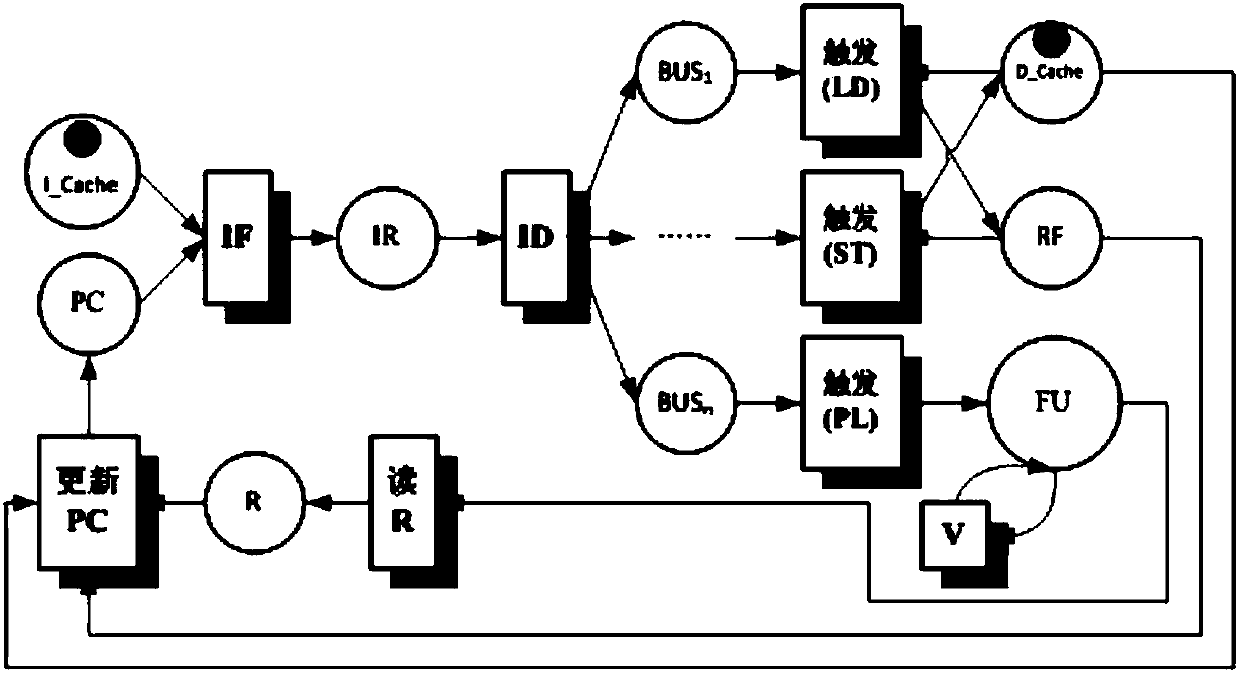

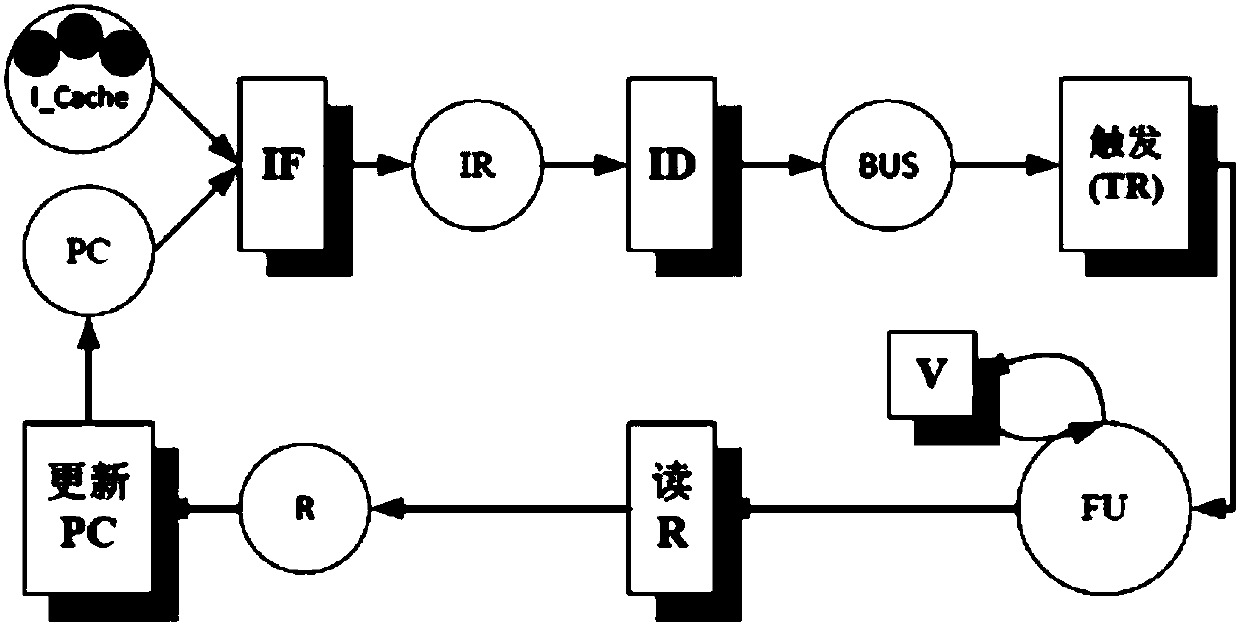

[0020] The pipeline behavior logic and its ADL description model are one of the key issues in processor design. The pipeline ADL description based on the Petri net model, namely PNML, is further obtained. After verification by third-party tools, it is synthesized into HDL and carried out in EDA and SoC environments. Architecture exploration and optimization.

[0021] In computer architecture, the position in the Petri net can be used to represent the local state of the system, such as queues, buffers, resources, etc.; transitions are used to describe events that cause system state changes, such as information processing, memory reading and writing, data processing, etc. Operations such as sending and receiving; arcs indicate the relationship between states and events, and the quantitative attributes can also be expressed by means of position capacity and arc weights, thus giving the pipeline behavior based on the Petri net model. The essence of a pipeline is a collection of co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More