Patents

Literature

79 results about "Processor model" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

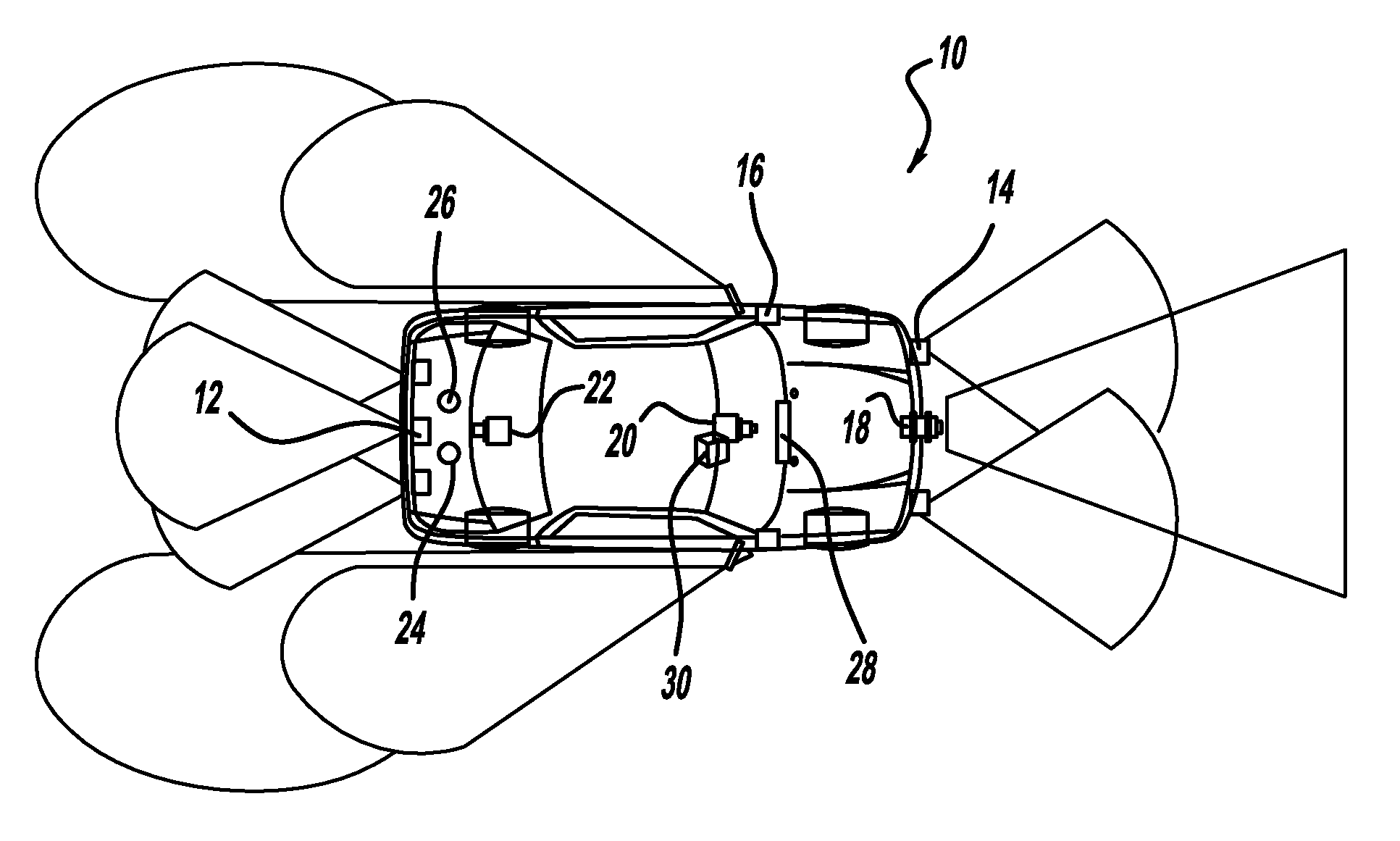

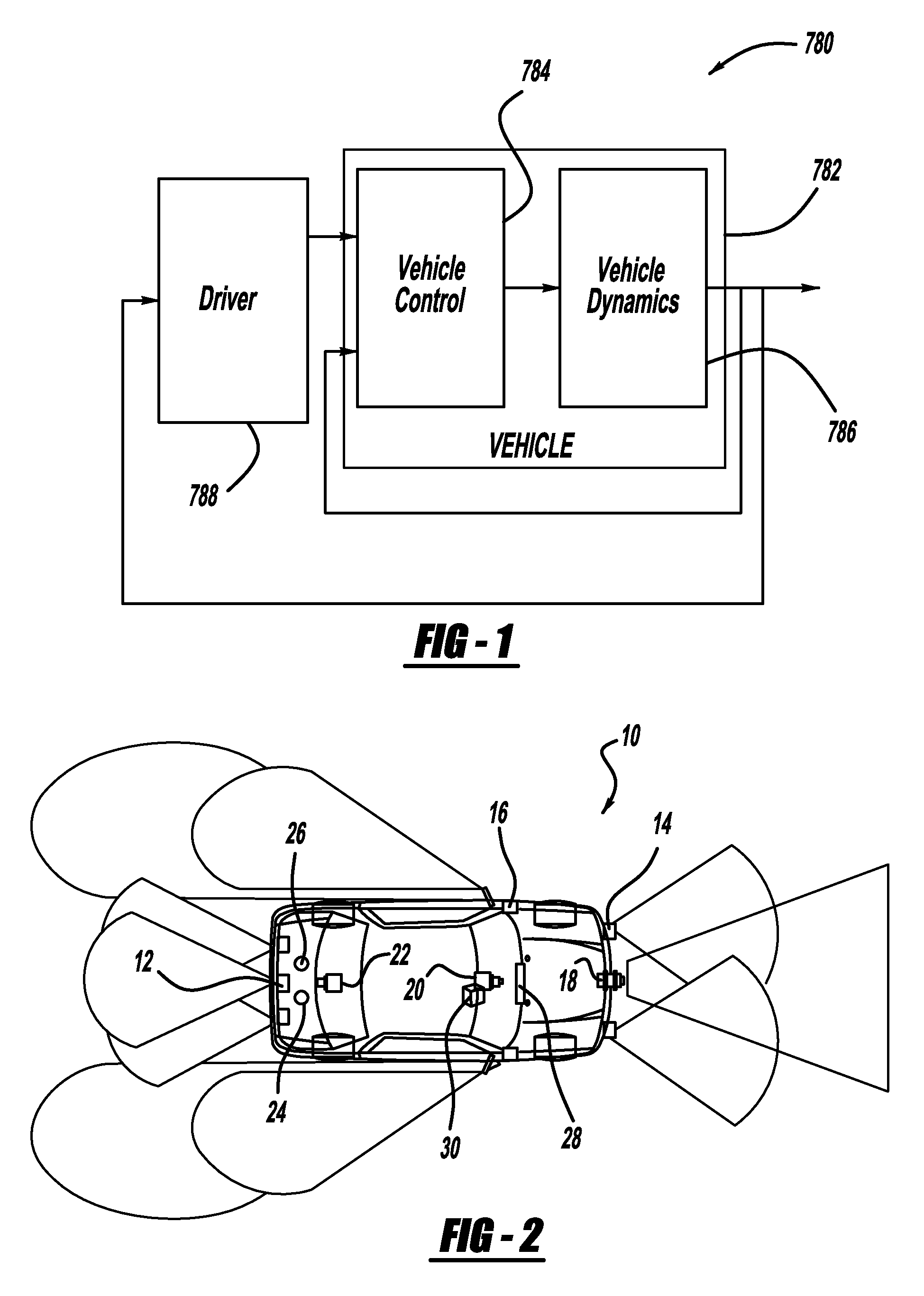

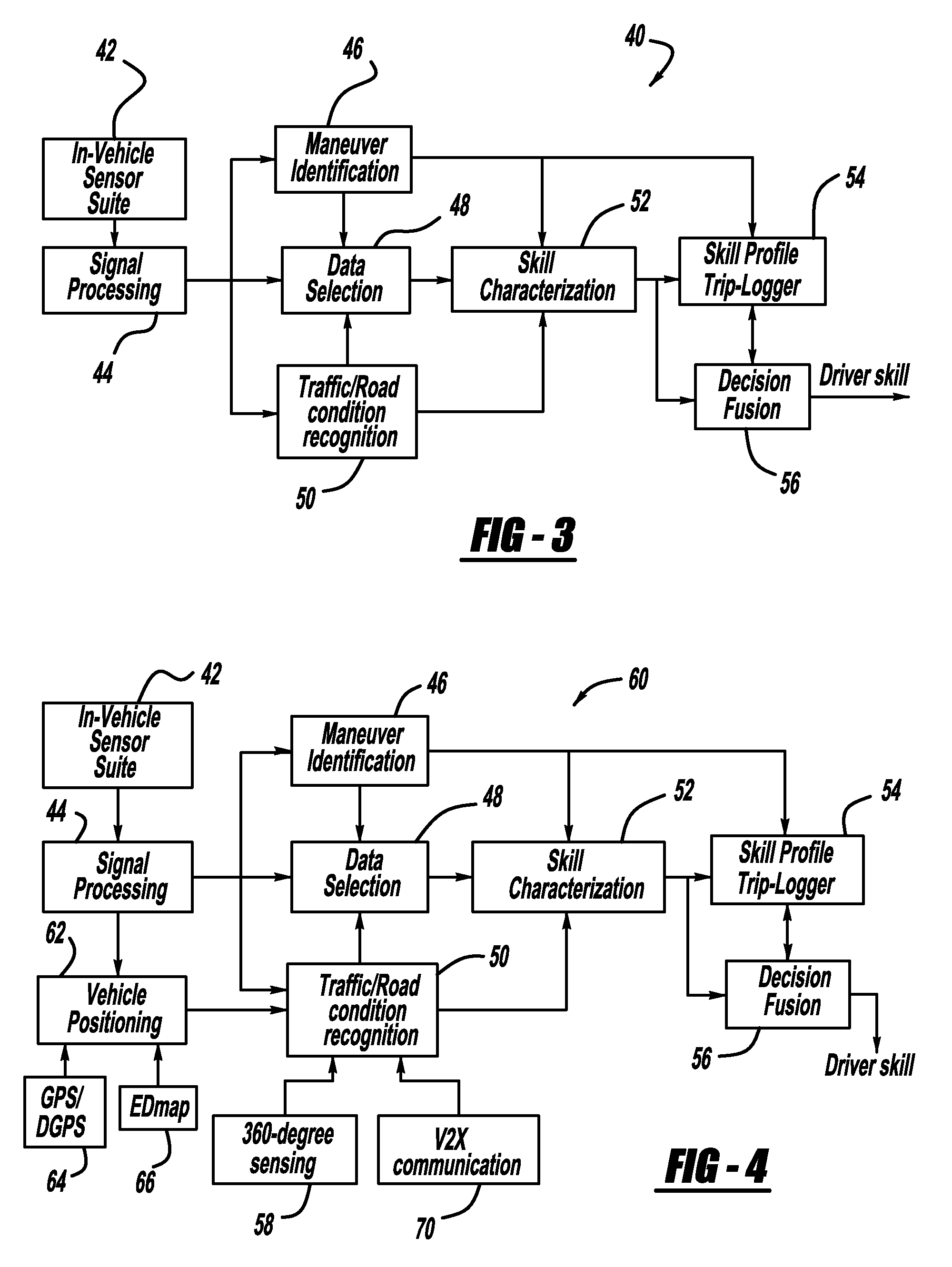

Driving skill recognition based on behavioral diagnosis

A system for classifying a driver's driving skill of a vehicle based on behavioral diagnosis. A plurality of vehicle sensors providing vehicle measurement signals. A maneuver qualification and identification processor qualifies and identifies characteristic maneuver identifying signals and a maneuver index and parameter processor creates a maneuver index and identifies relevant vehicle parameters. A path reconstruction processor reproduces an intended vehicle path for each characteristic maneuver identified by the maneuver characteristic processor. A maneuver model processor models the characteristic maneuvers and a driving skill diagnosis processor provides driving skill signals based on the maneuver model and driver input data. The driving skill diagnosis processor converts the maneuver model signals and the driver command input signal to the frequency domain to provide frequency content discrepancy analysis.

Owner:GM GLOBAL TECH OPERATIONS LLC

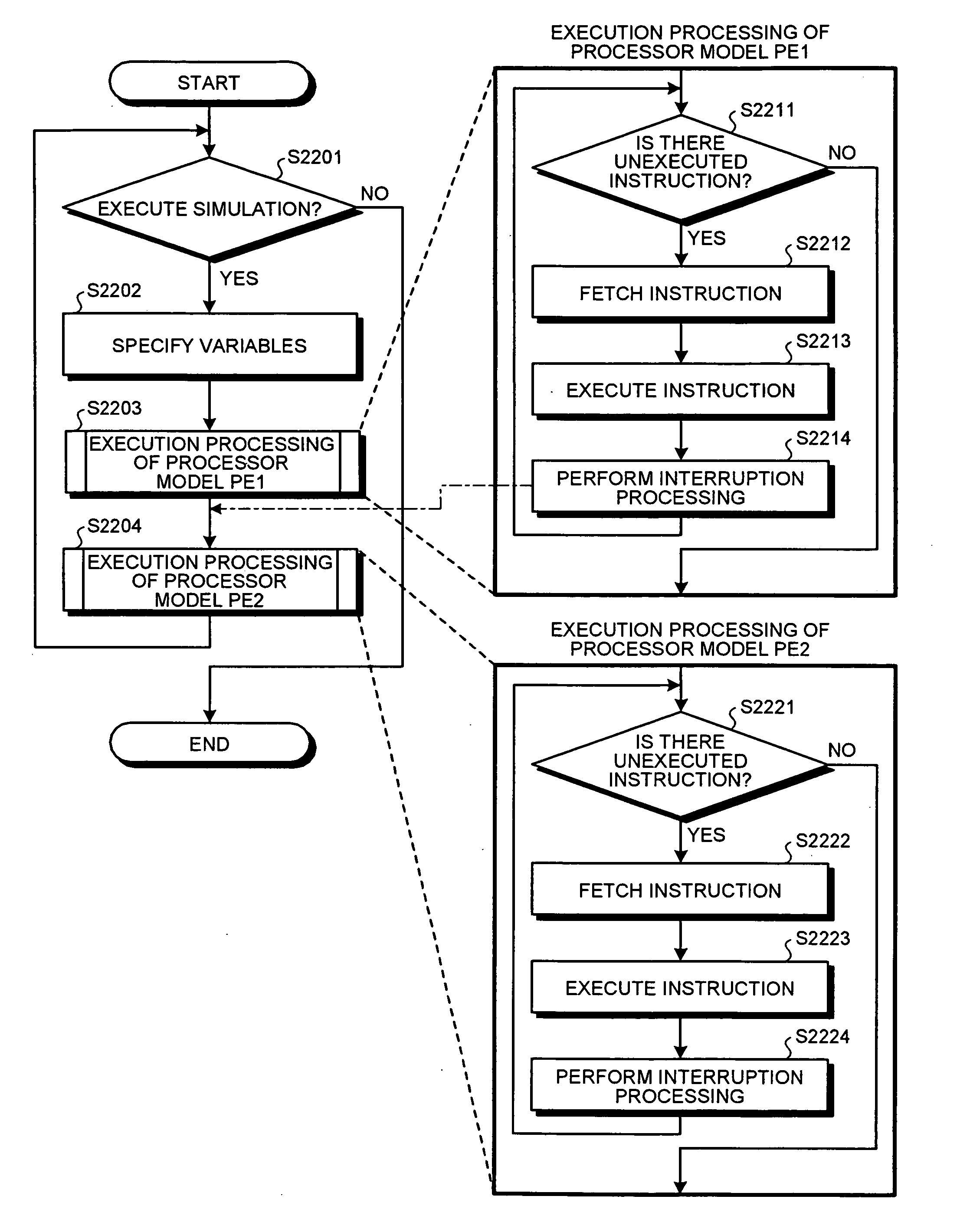

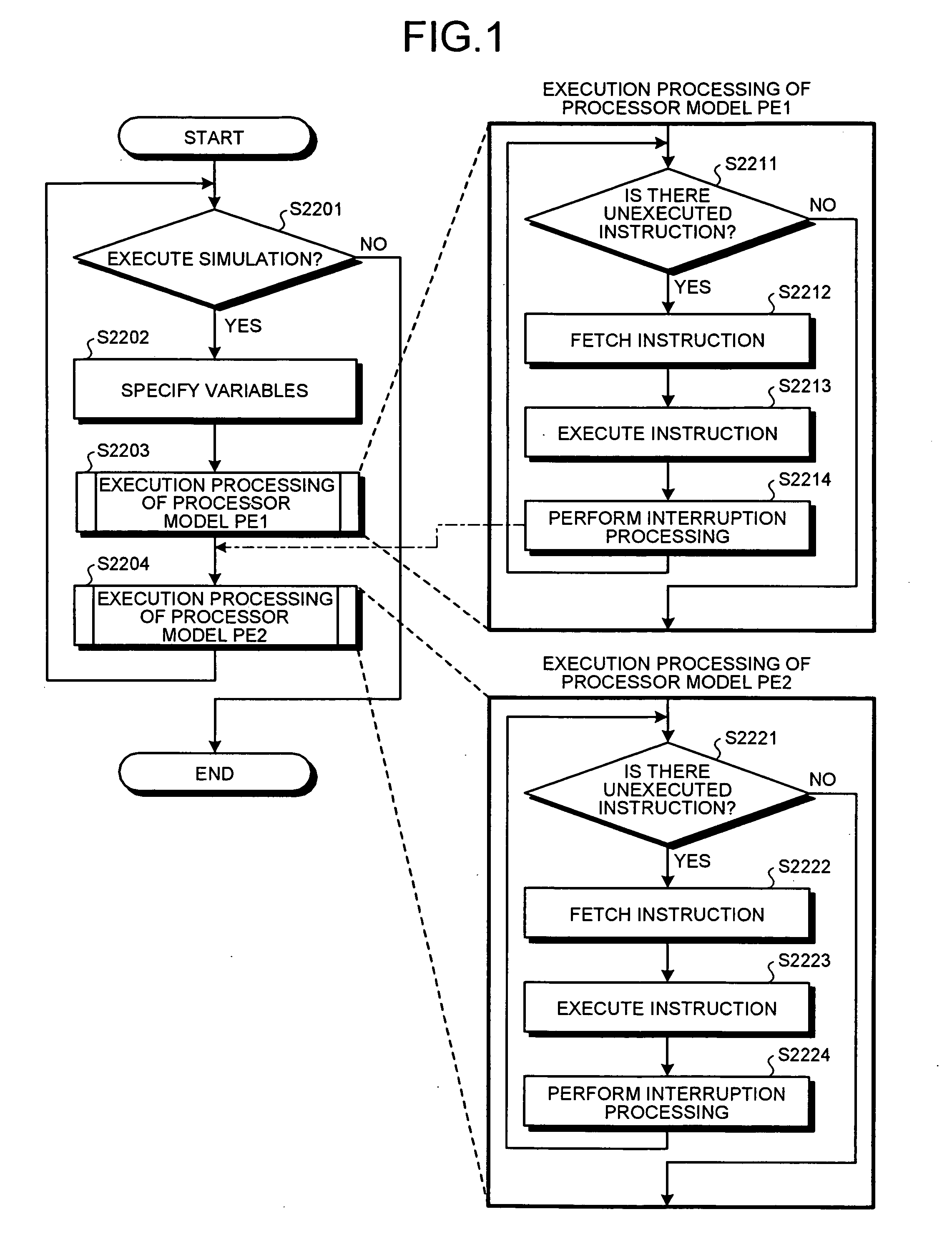

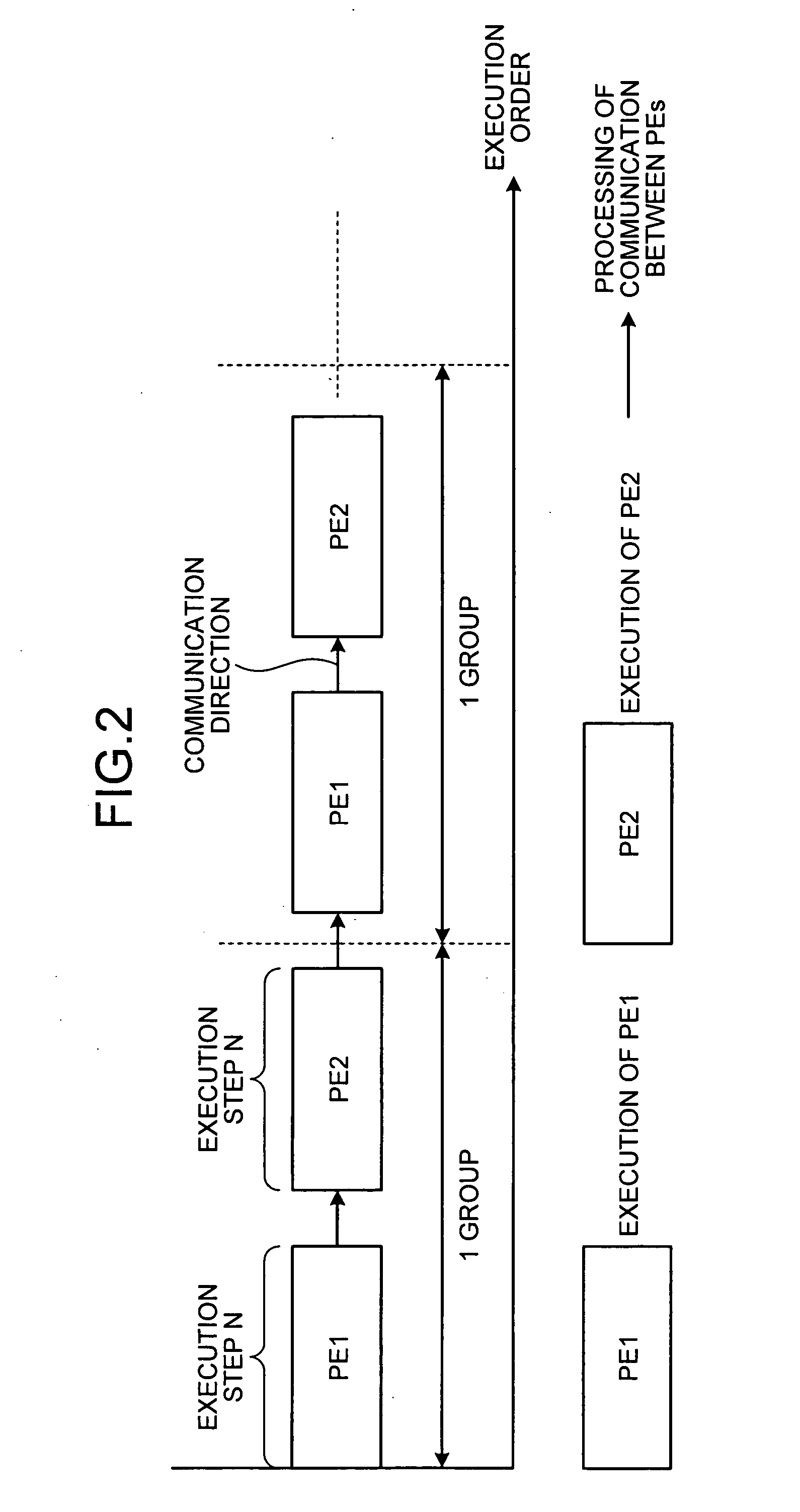

Multi-core-model simulation method, multi-core model simulator, and computer product

InactiveUS20070101318A1Electronic circuit testingProgram synchronisationProcessor modelMulti processor

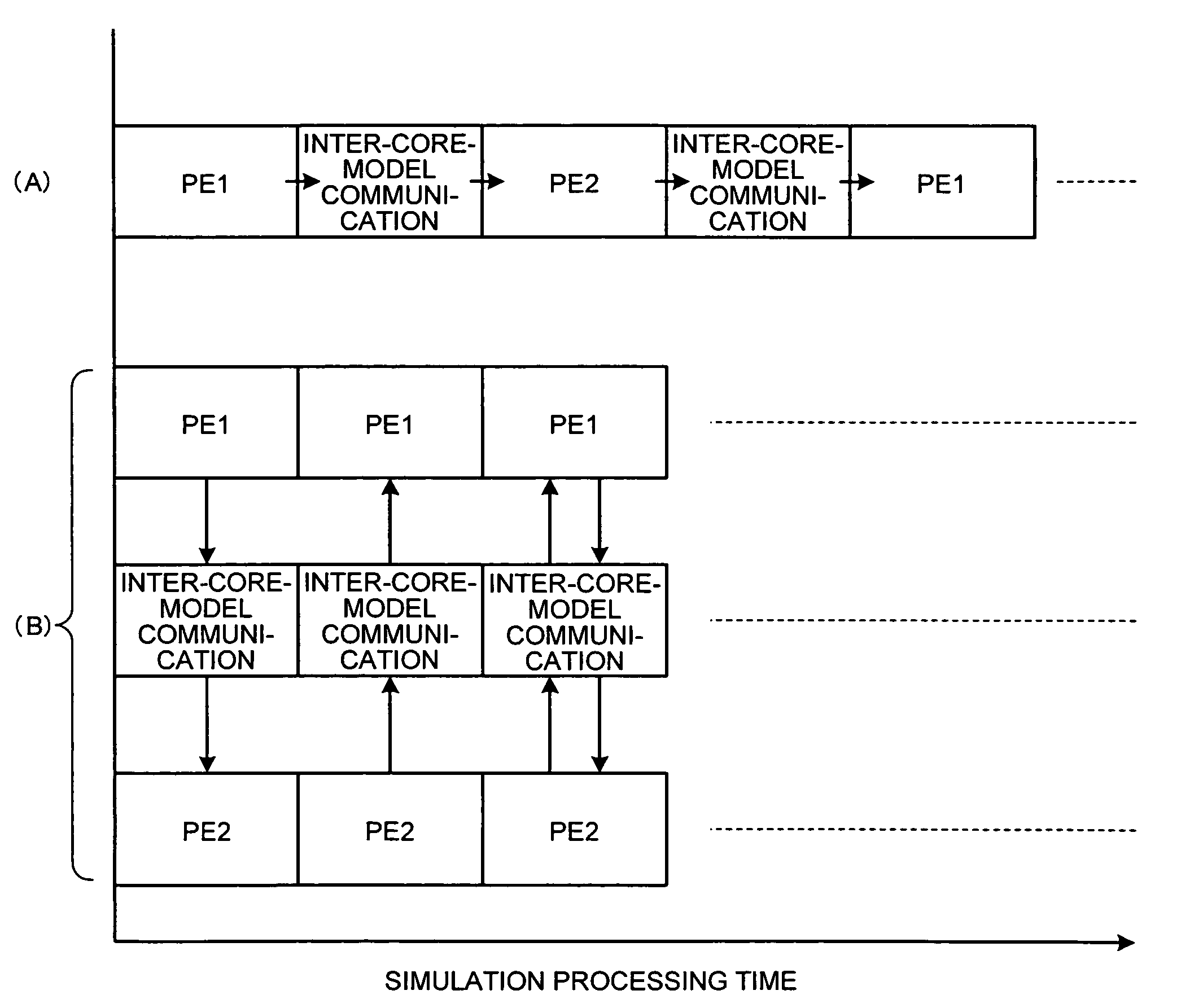

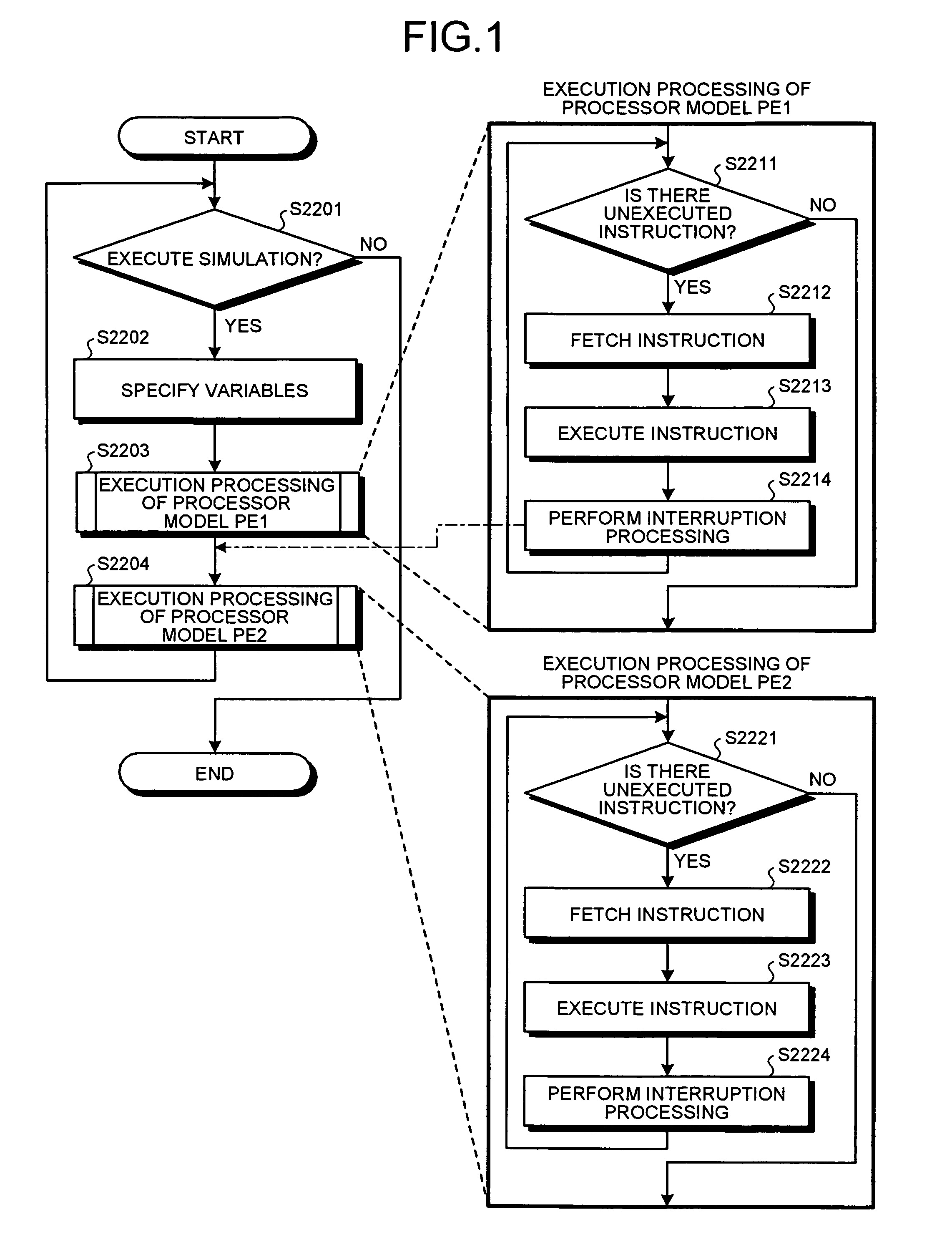

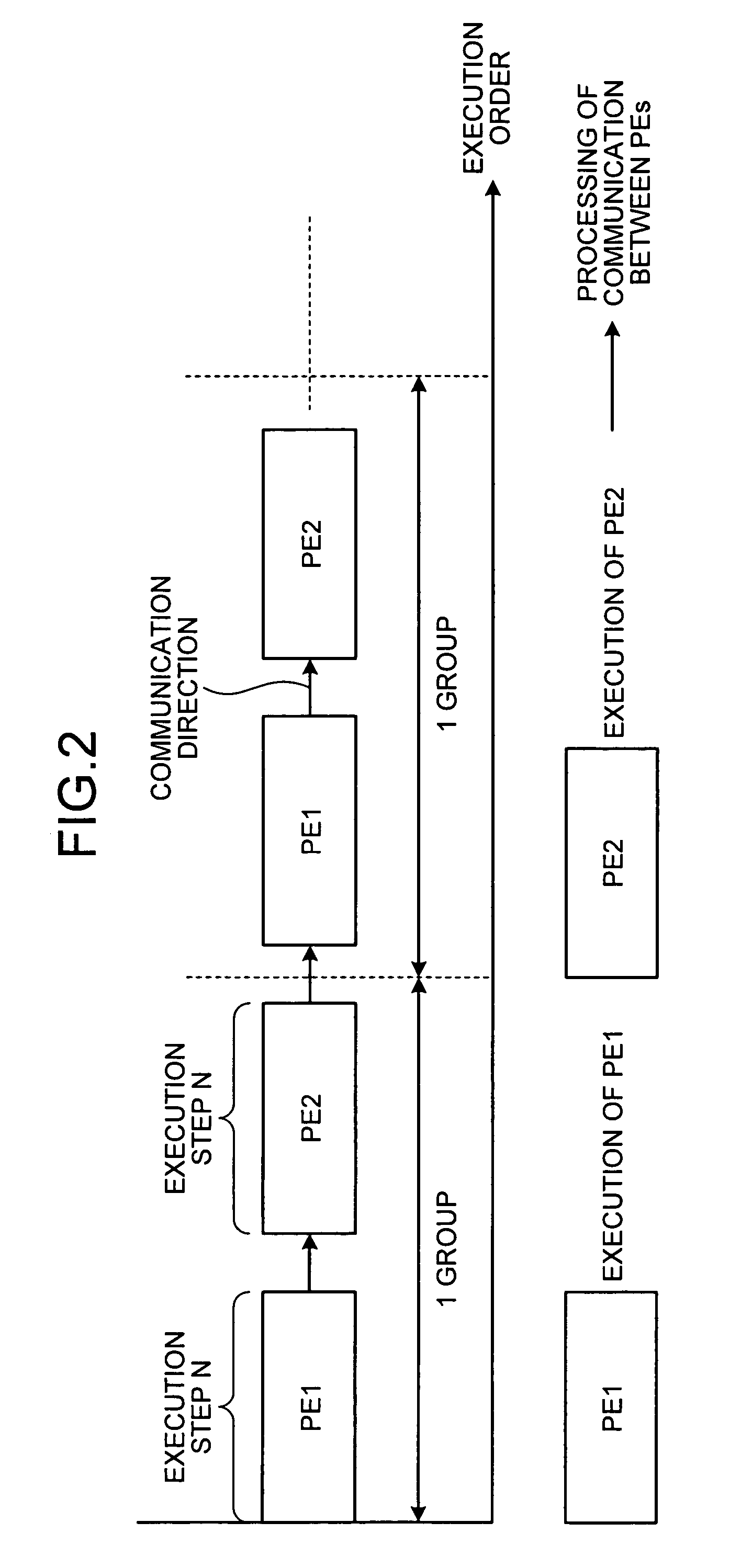

Core model processing of a processor model PE1 and a processor model PE2 is serialized. Therefore, processing time for the inter-core-model communication is required between the core model processing of a first processor model and the core model processing of a second processor model. The inter-core-model communication processing is performed such that the inter-core-model communication required for the simulation processing of a multi-processor model is performed in parallel with the core model processing.

Owner:SOCIONEXT INC

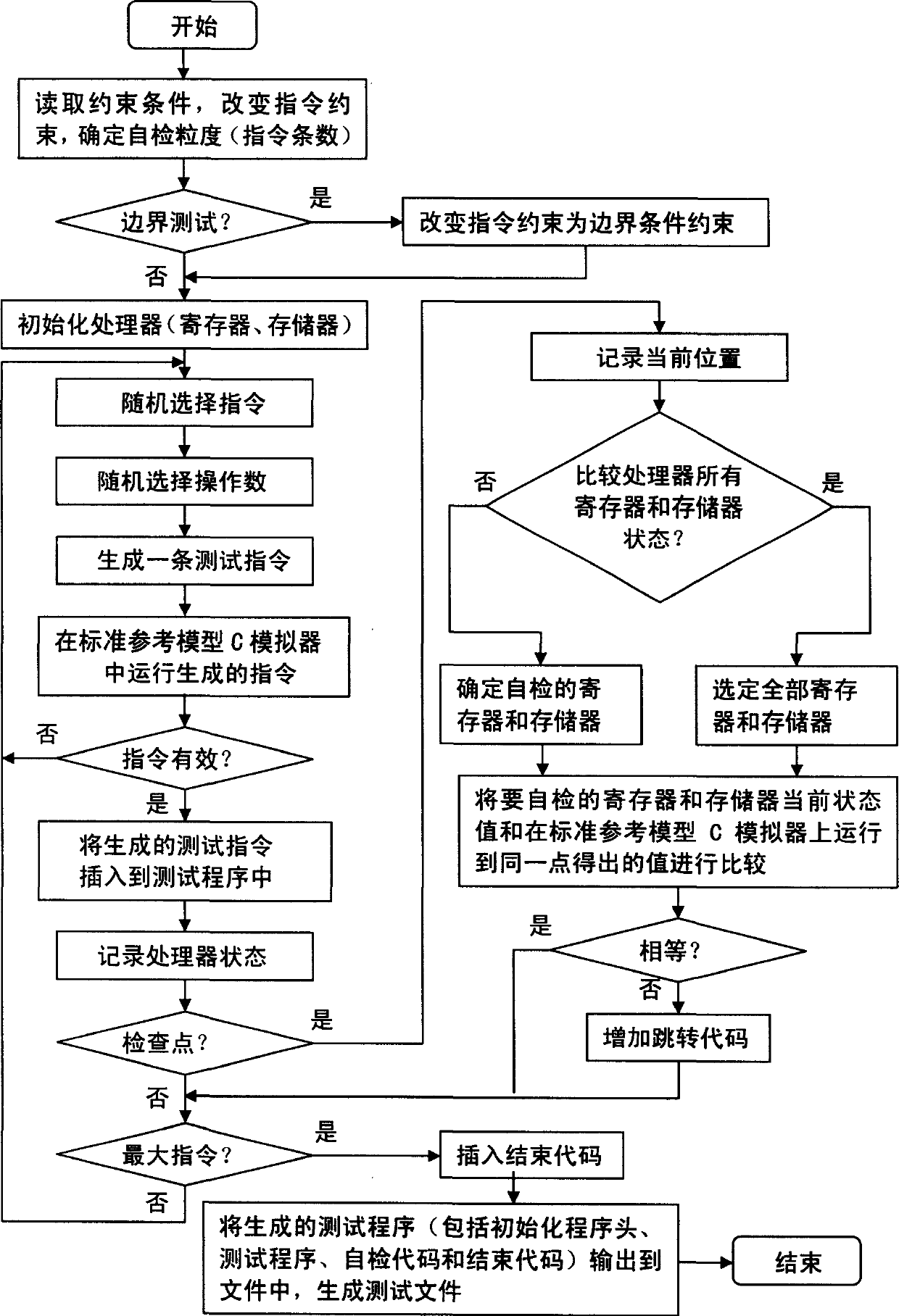

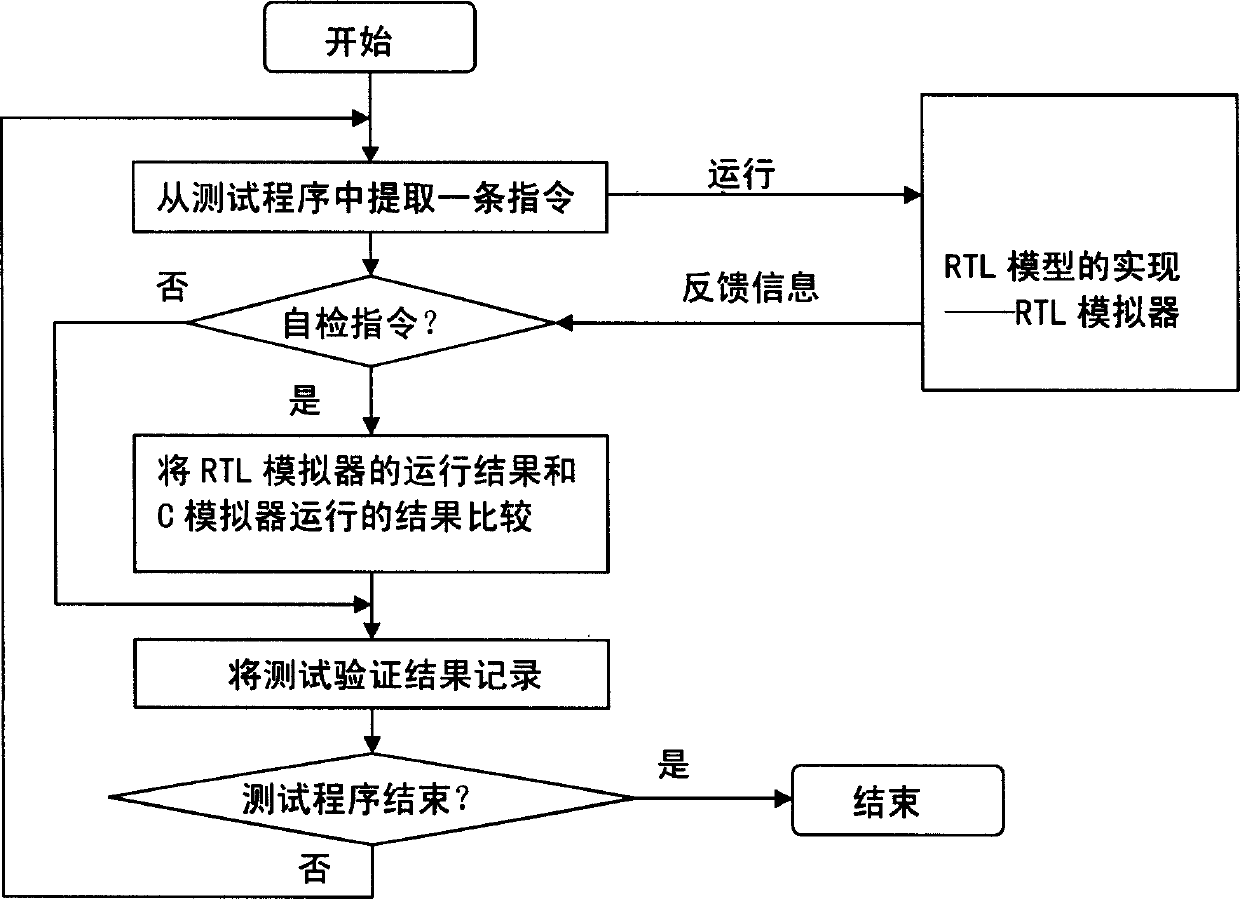

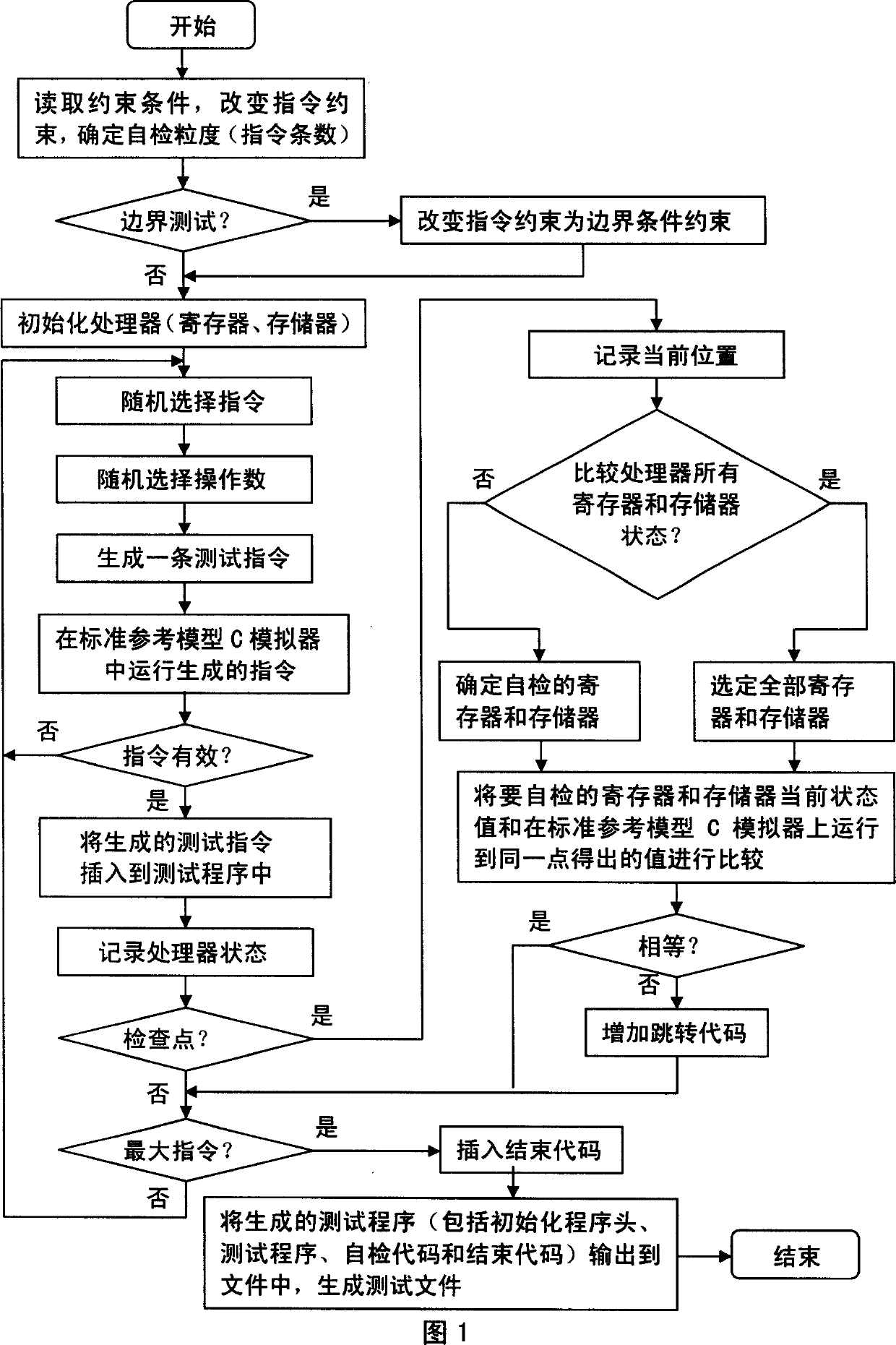

CPU restraint forming and verifying method based on boundary condition and self detection random test

InactiveCN1684047AQuality improvementSpeed up the verification processSoftware testing/debuggingReference modelProcessor model

The present invention belongs to the field of automatic computer verifying technology, and is the CPU restraint creating and verifying method based on boundary condition and random self test. The specific mode is one random test environment including system structure model and RTL model. The system structure model is expected processor model realized with C simulator and used as the standard reference model. The RTL model is one to be tested and verified, and the random test and verification aims at testing the consistency of the RTL model to the system structure model. Both the RTL model and the system structure model can output separate processor state in each clock period, and comparing the processor state of these two model can judge the consistency. The present invention has independent system structure, and can constitute new verifying platform easily to raise the verification speed and quality greatly.

Owner:TSINGHUA UNIV

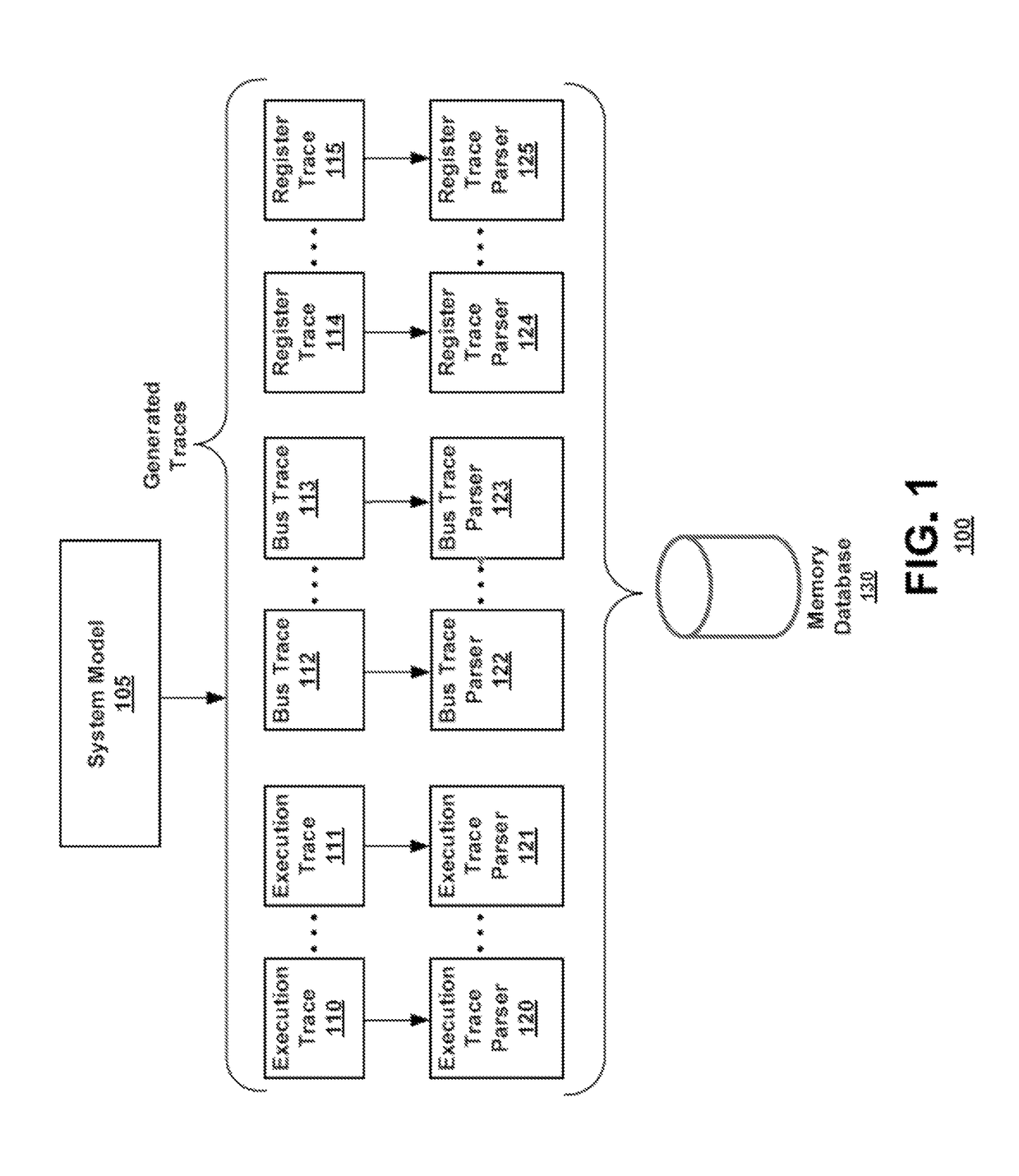

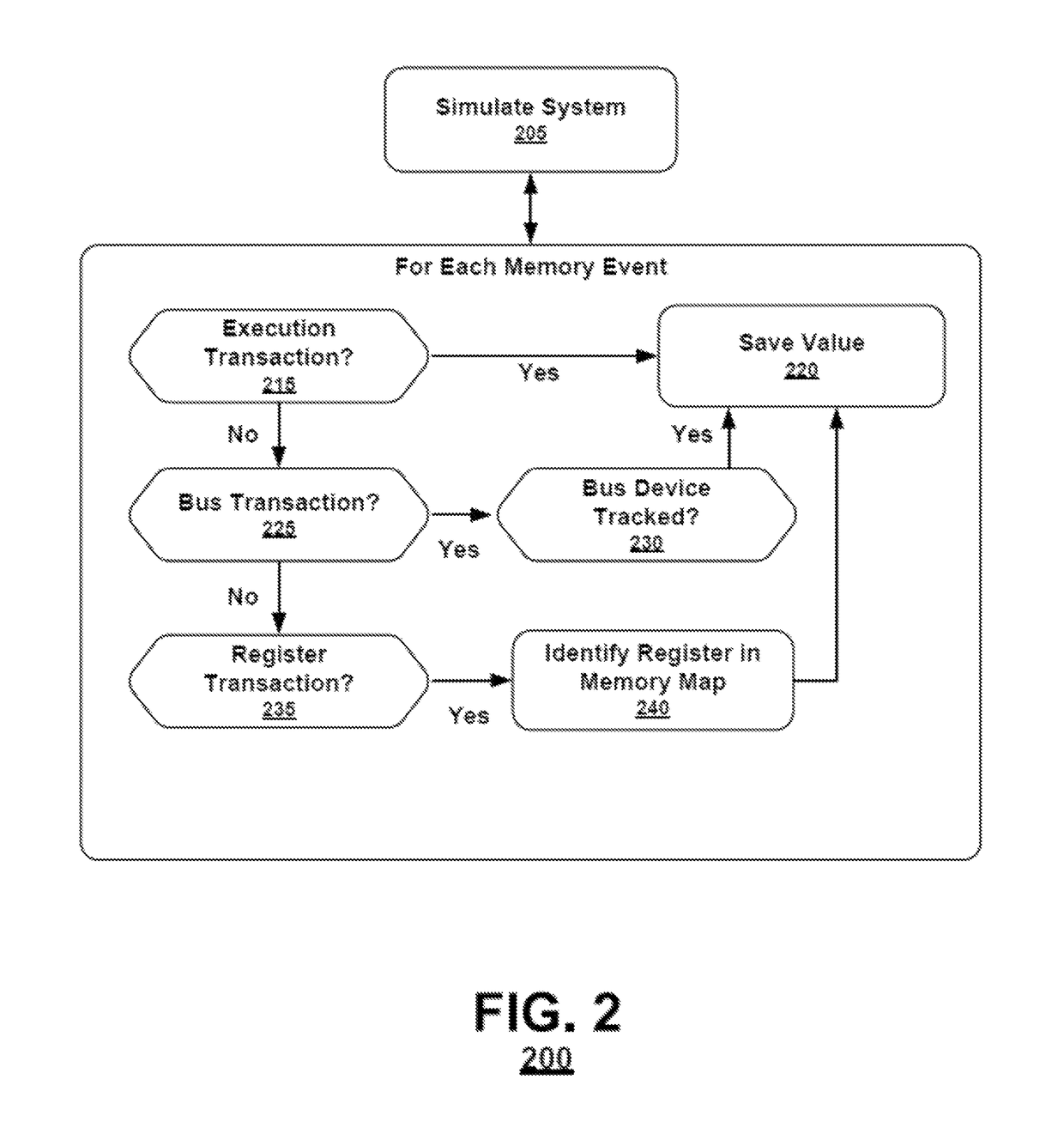

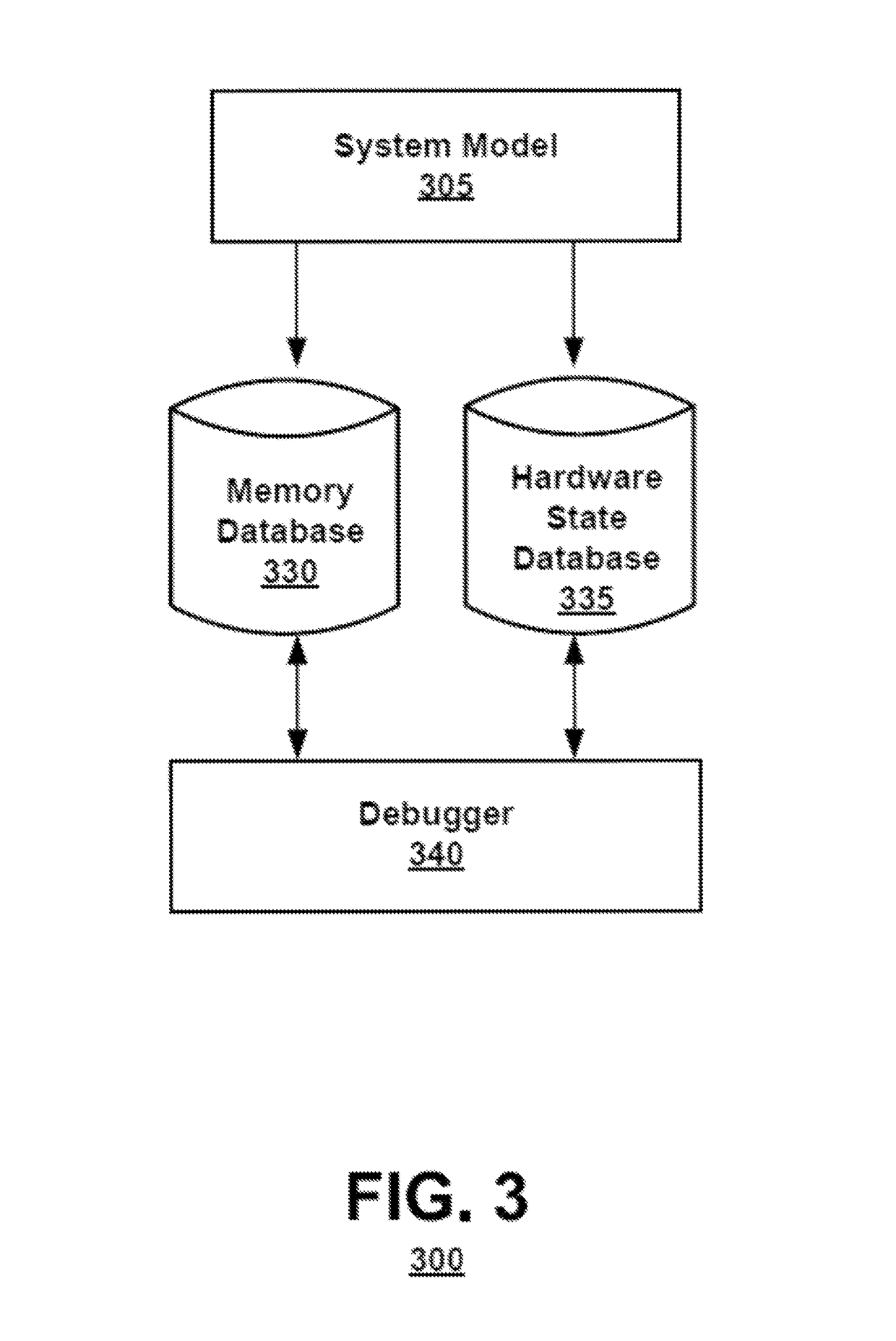

Debugging process

ActiveUS10176078B1Hardware monitoringSoftware maintainance/managementProcessor modelElectronic design

The present disclosure relates to a system and method for capturing log messages in a post-processing debugging environment. Embodiments may include receiving a processor model associated with an electronic design and generating, using one or more processors and the processor model, a complete view of the state of the memory. Embodiments may further include writing, using one or more processors and the processor model, a log message whenever a designated message logging function is reached within the complete view of the state of the memory.

Owner:CADENCE DESIGN SYST INC

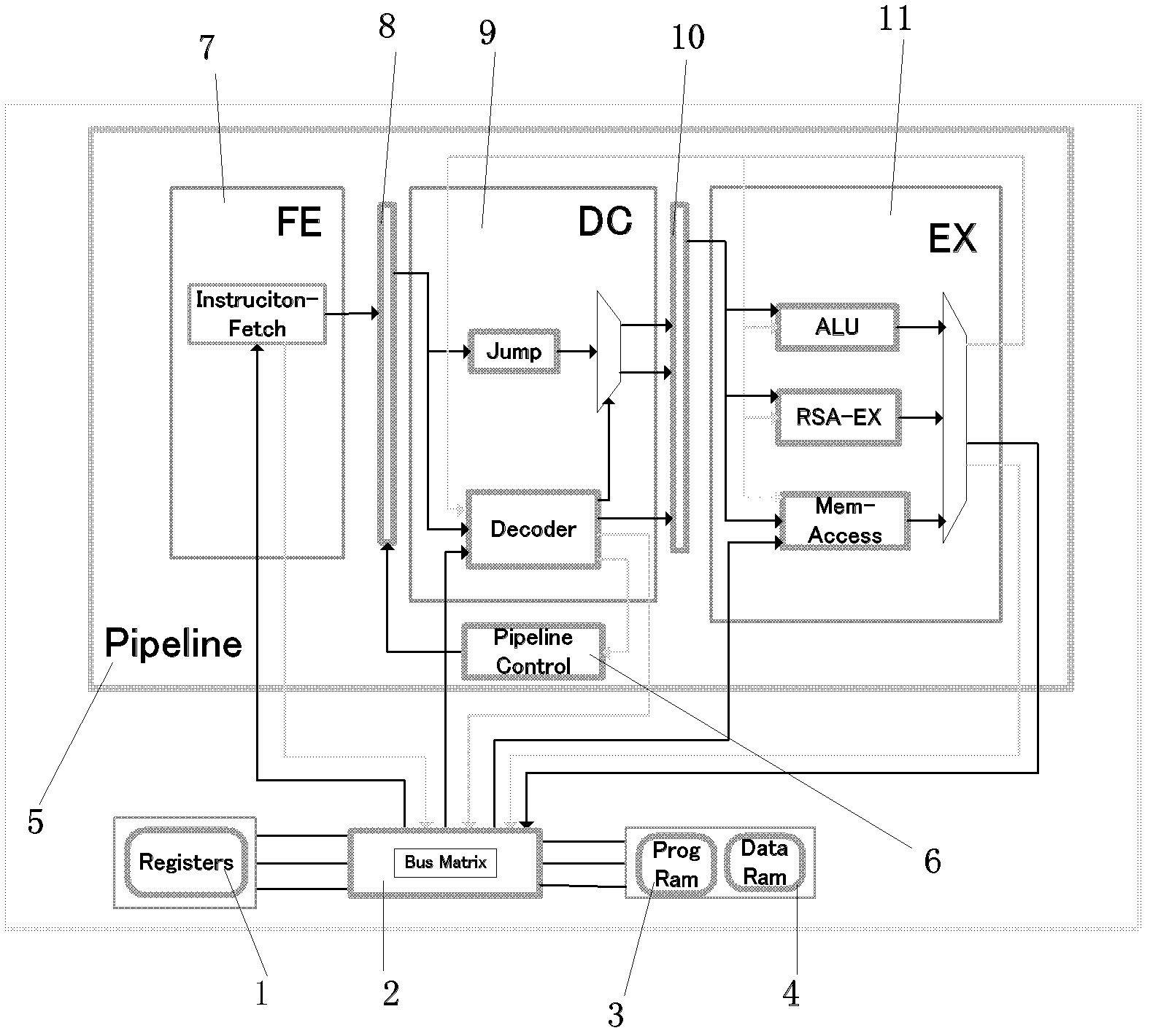

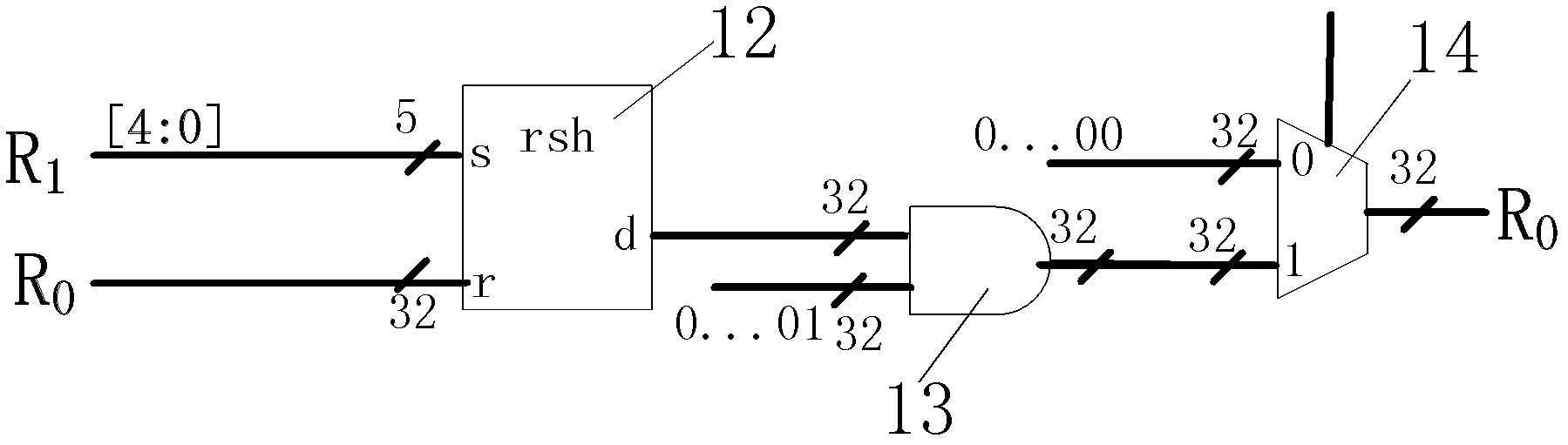

Instruction optimization processor for RSA encryption algorithm

InactiveCN102662628AEasy to implementSpeed up executionConcurrent instruction executionMemory systemsProcessor modelExtensibility

The invention relates to an instruction optimization processor for RSA encryption algorithm. The instruction optimization processor for RSA encryption algorithm adopts five extension instructions specially used for accelerating optimization on RSA encryption algorithm, and designs a special instruction processor model-RSA_ASIP corresponding to a new instruction set. The five extension instructions specially used for accelerating optimization on RSA encryption algorithm include getbit, shift_l, shift_r, muladd and muladd2 instructions, and the special instruction processor model-RSA_ASIP corresponding to the new instruction set consists substantially of a data memory, a code memory, a register file, a pipeline and a bus matrix. According to the RSA_ASIP processor designed by the invention, the execution of the RSA can be greatly optimized on the premise of ensuring flexibility and extensibility of software realization; through realization on RSA1024 and RSA2048, the instruction period is shortened by 64 percent on average compared with the realization on an ARM (Advanced RISC (Reduced Instruction-Set Computer) machines) processor, and the processor model after being subjected to instruction optimization can save resource consumption.

Owner:SHANDONG UNIV

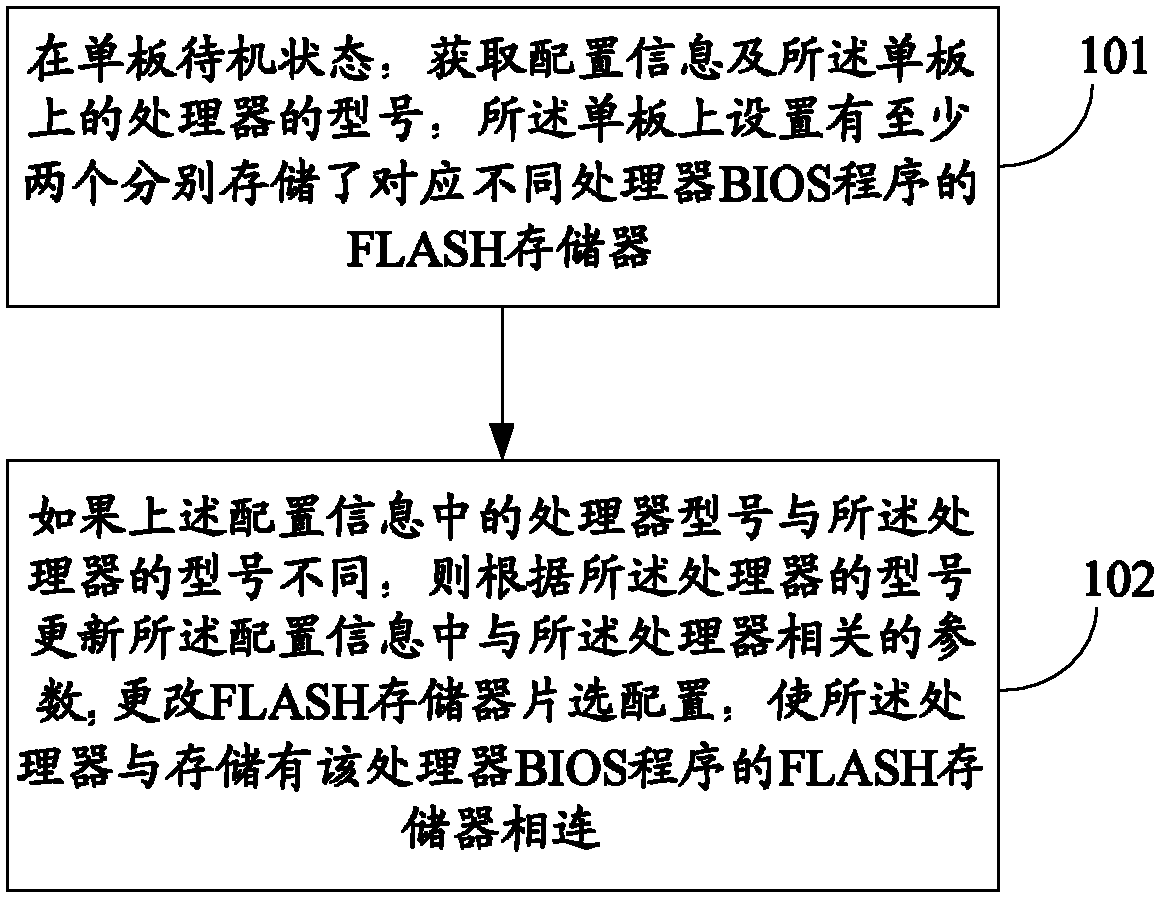

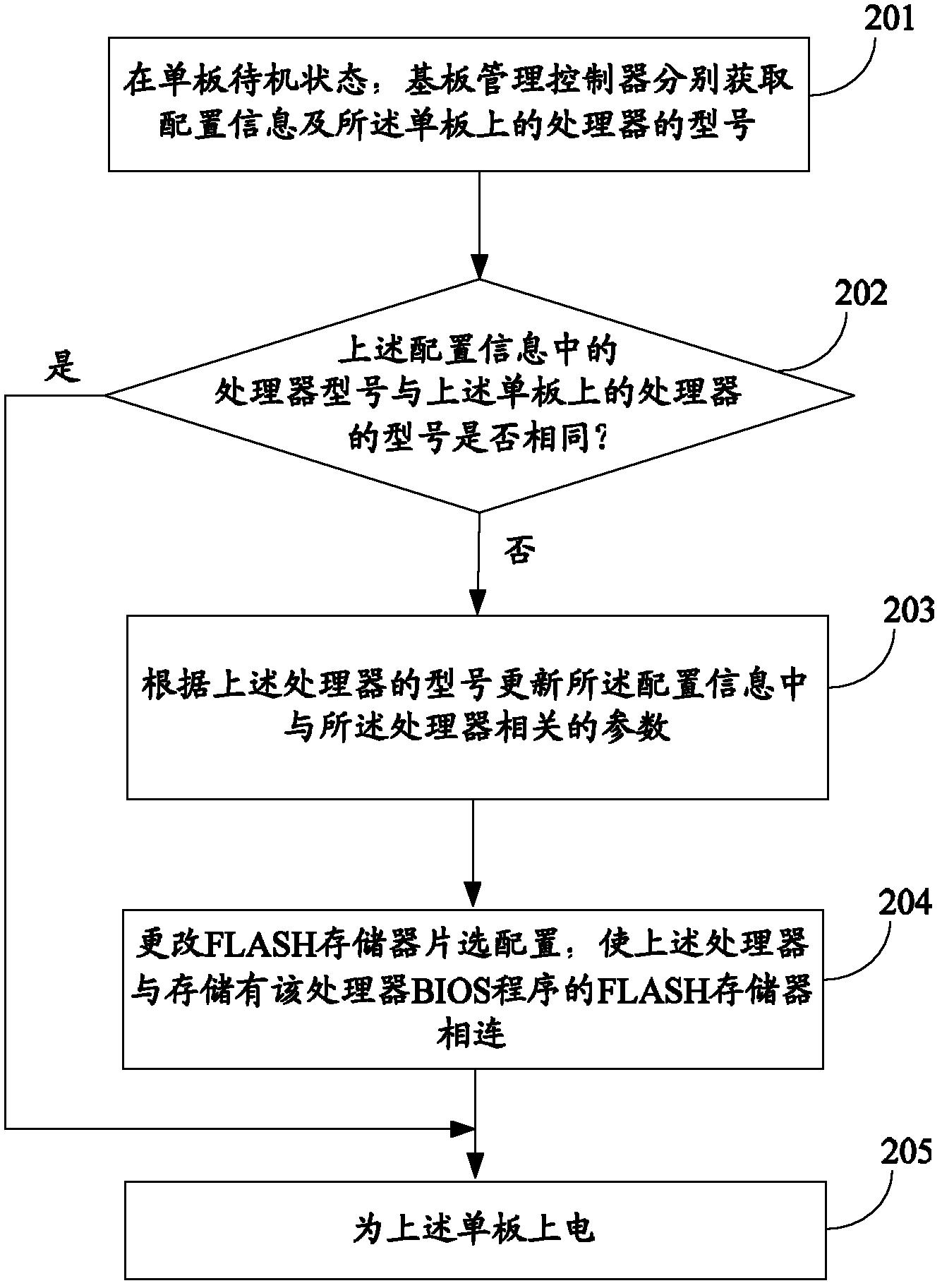

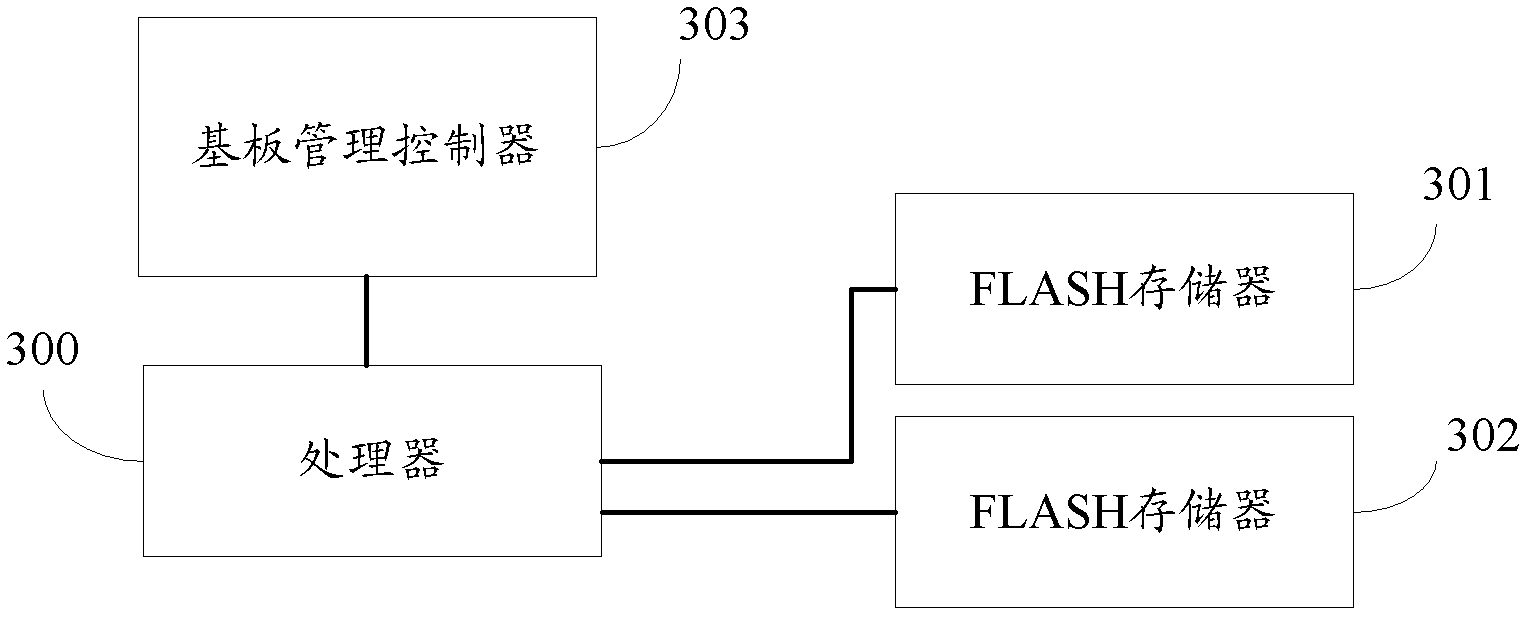

Method and device for realizing compatibility of different processors

ActiveCN102388366ASimple designEasy to updateProgram initiation/switchingBootstrappingProcessor modelBIOS

Disclosed are a method and a device for realizing compatibility of different processors. The method includes the steps of obtaining configuration information and processor model of a single board under a single board standby state, updating the parameters related to the processor in the configuration information according to the processor, if the processor model information in theconfiguration information is different from the processor model, and modifying configuration of a flash memory sheet, so that the processor is connected with the flash memory where the BIOS program of the process is stored.

Owner:HUAWEI TECH CO LTD

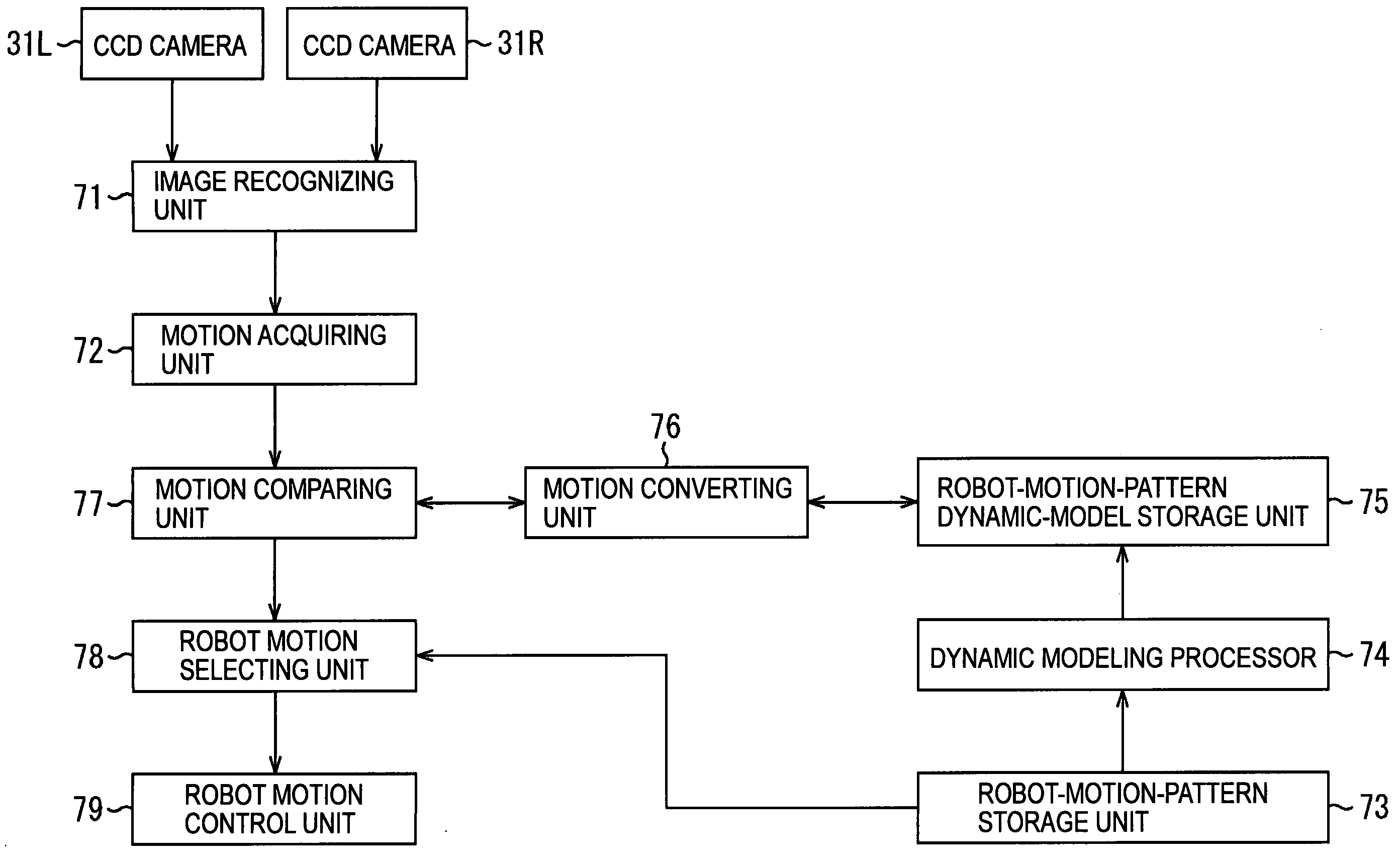

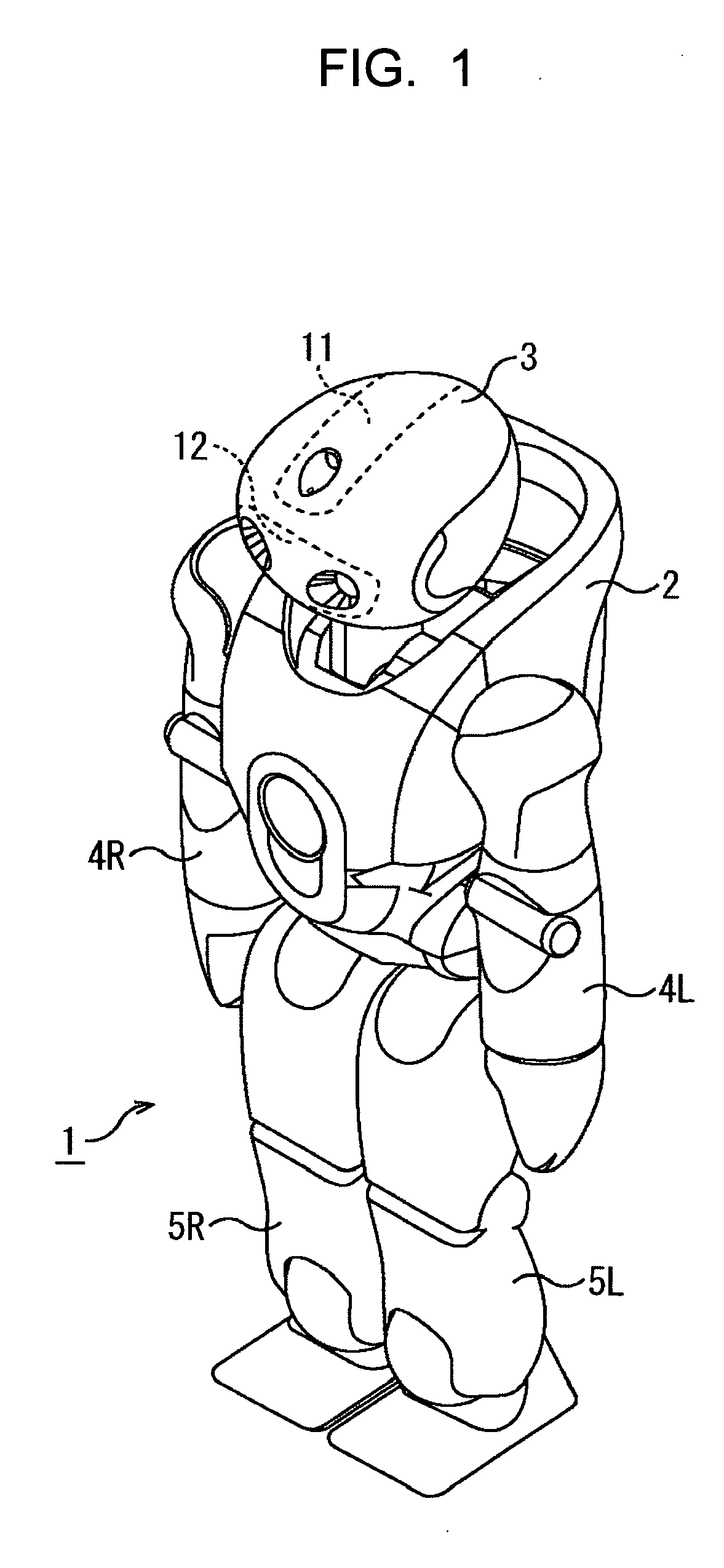

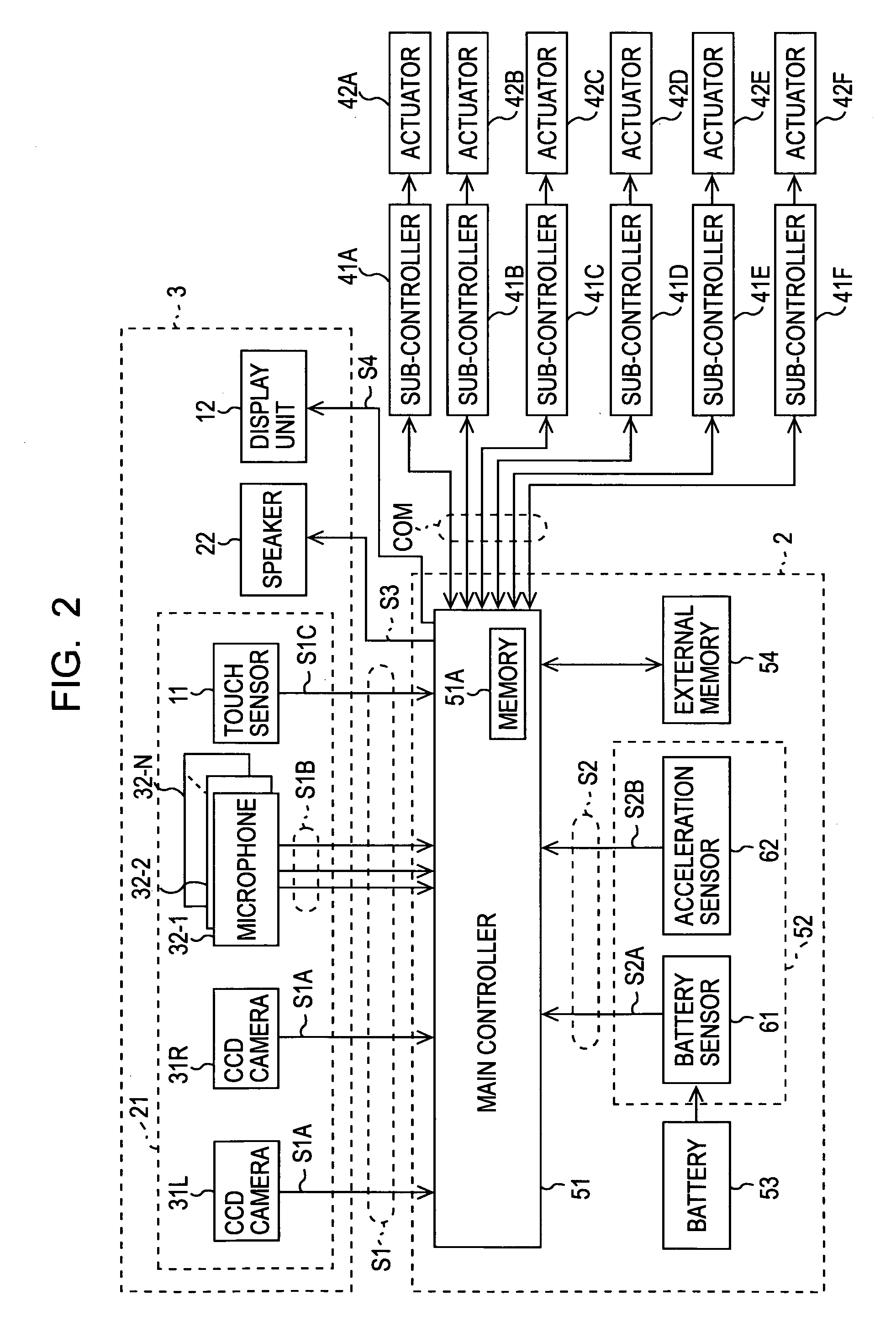

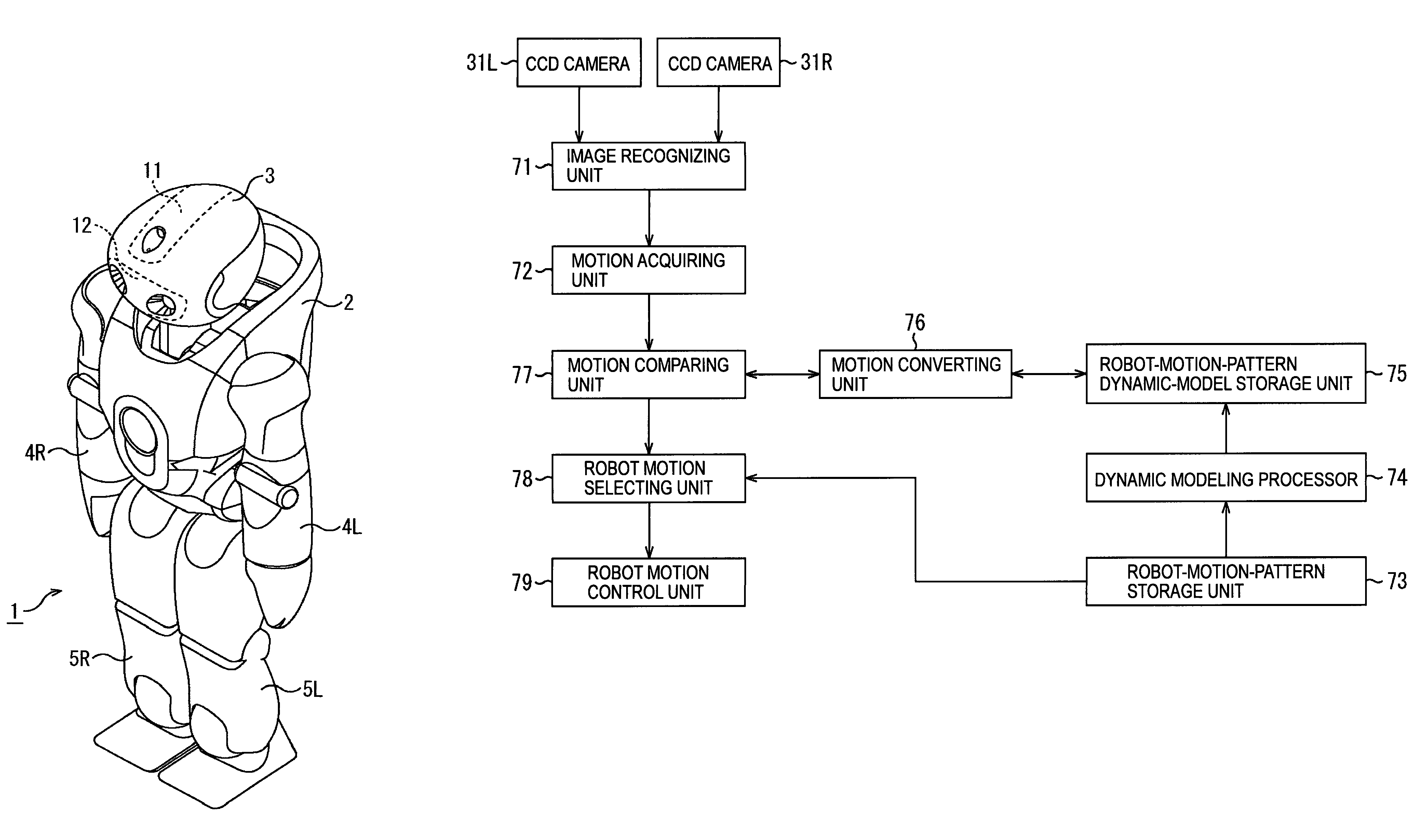

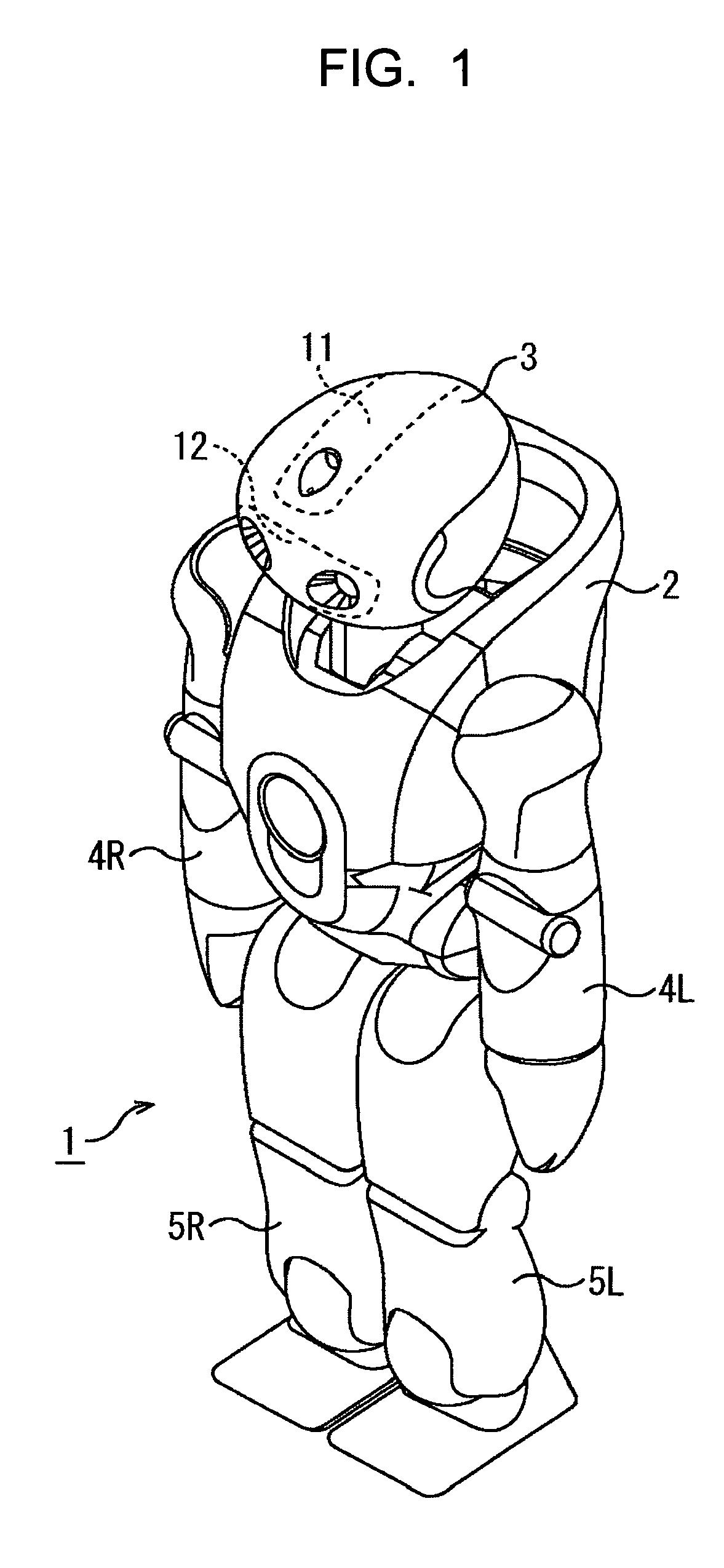

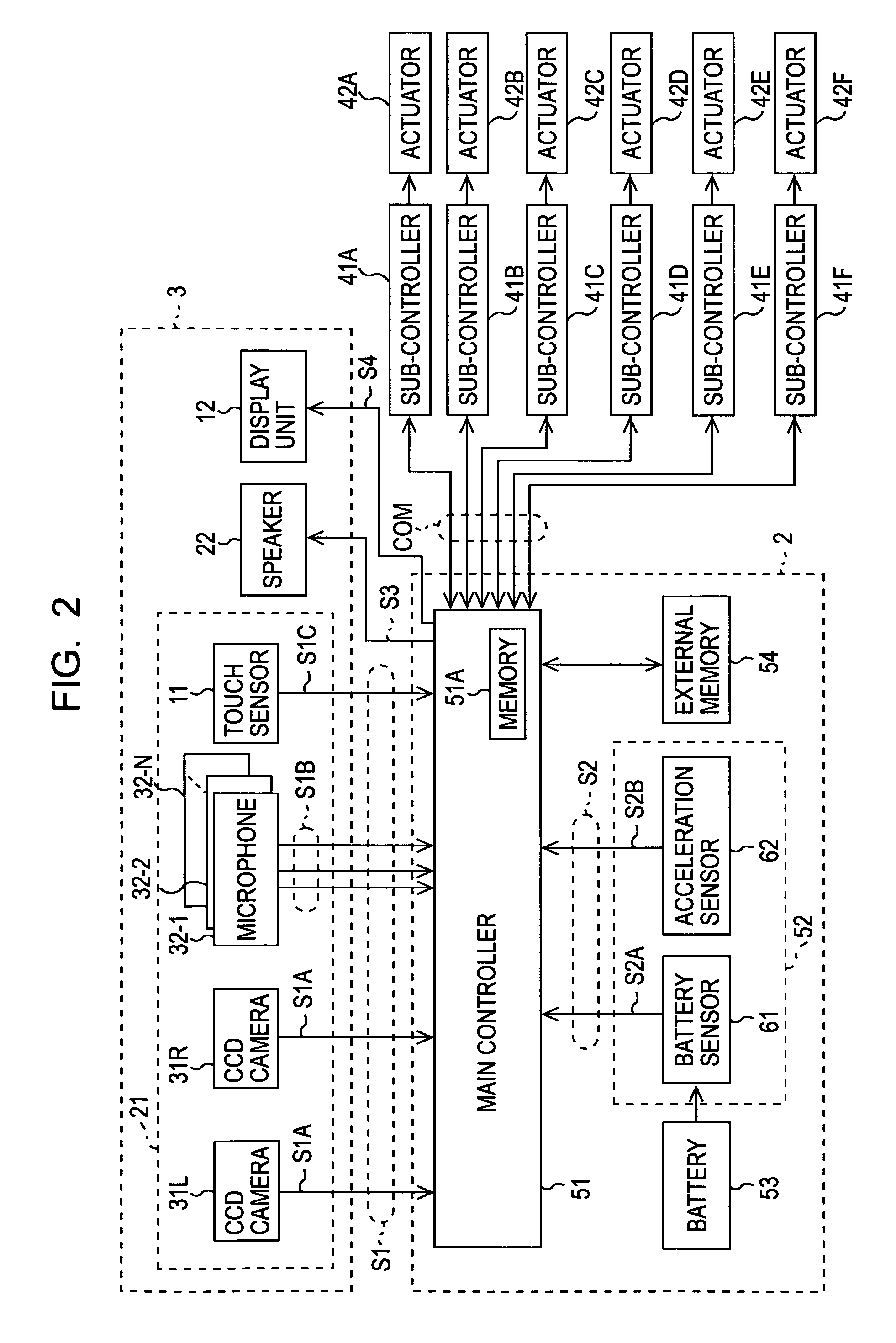

Information processing apparatus and method, program storage medium, and program

InactiveUS20050080513A1Reduce necessityPromote generationProgramme-controlled manipulatorComputer controlInformation processingProcessor model

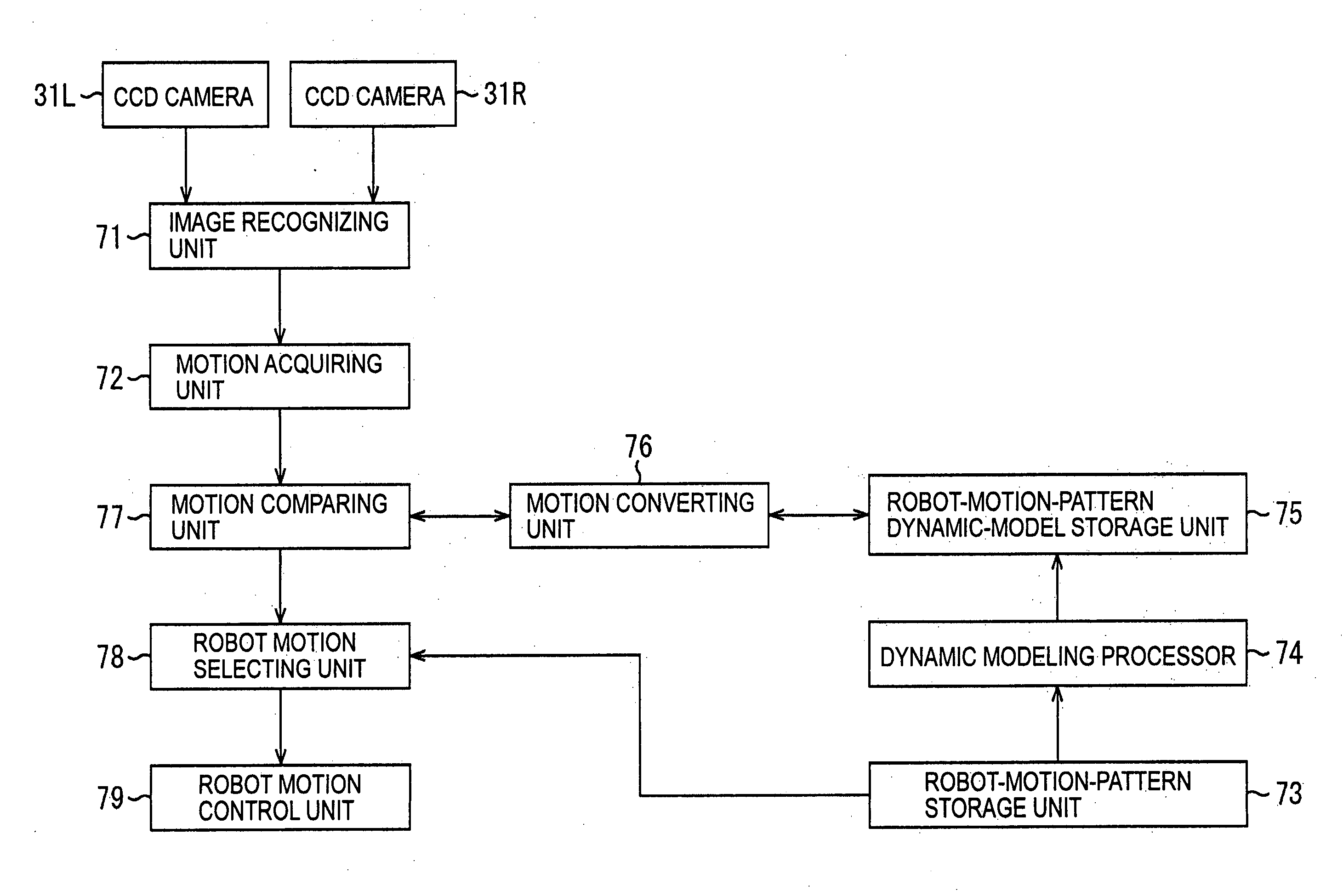

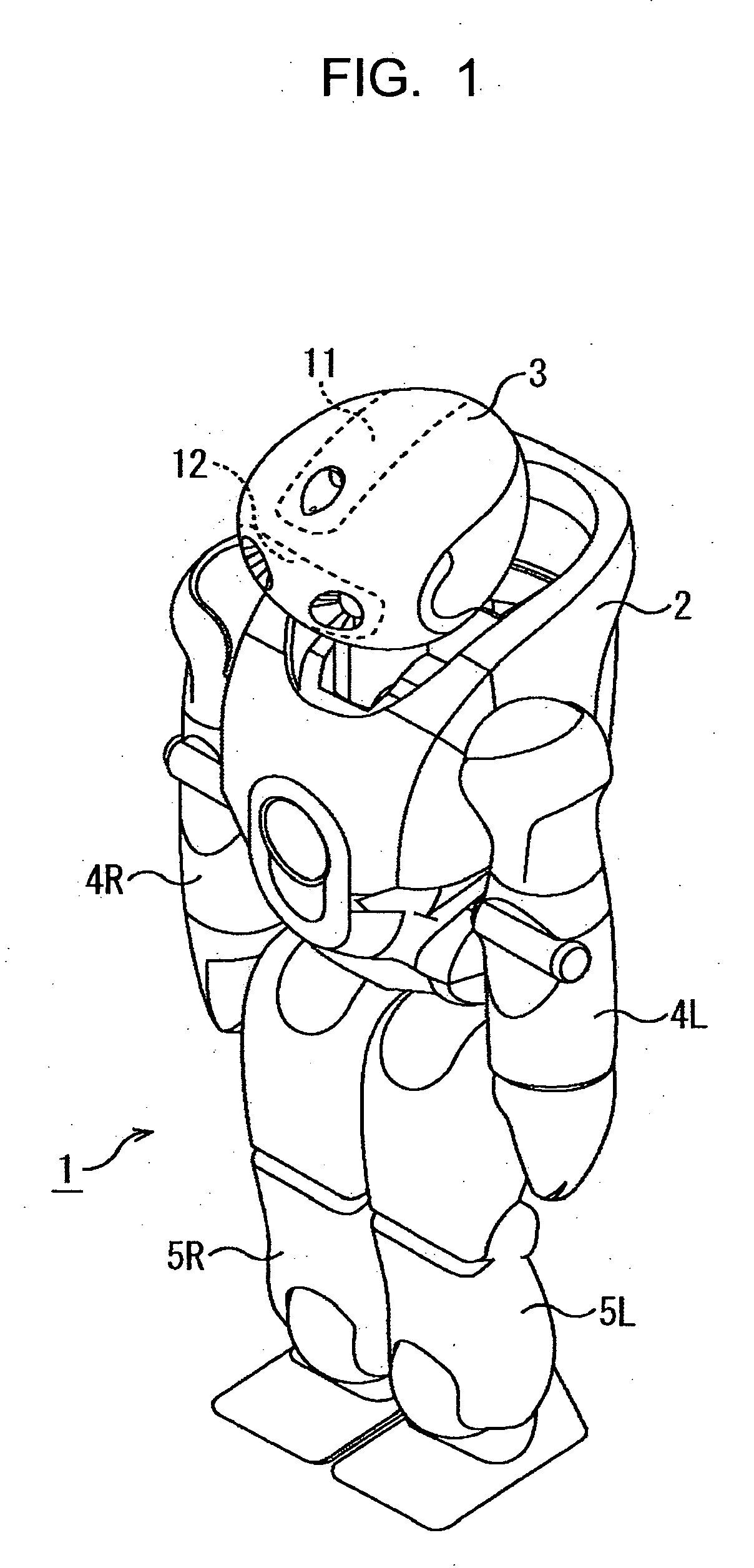

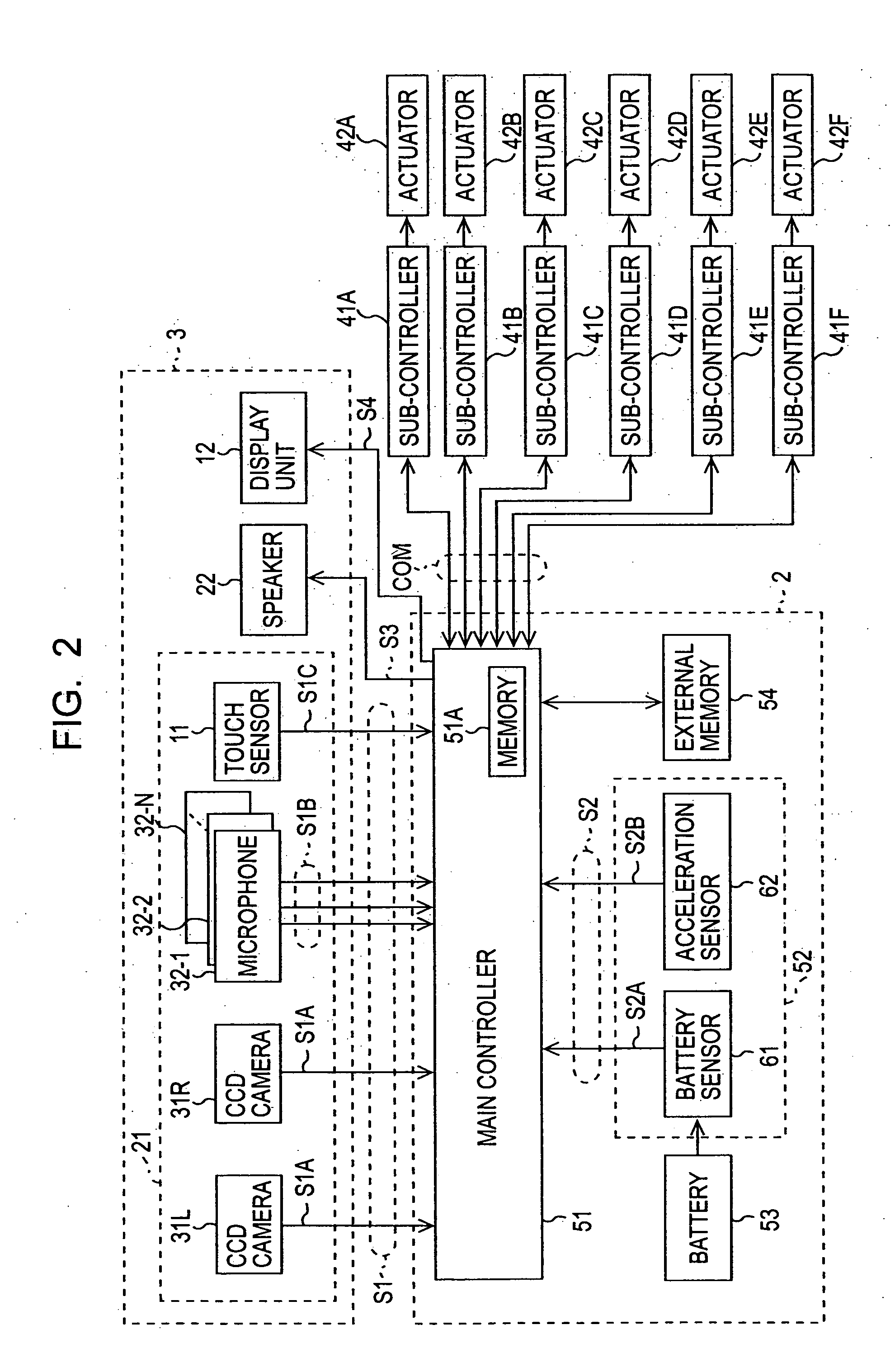

An input motion acquiring unit acquires a motion trajectory of an object from an image recognizing unit. A dynamic modeling processor models a plurality of robot motion patterns stored in a robot motion pattern storage unit in a dynamic system form, and stores the modeled robot motion patterns into a robot-motion-pattern-model storage unit. A motion converting unit linearly transforms the plurality of robot motion dynamic models stored in the robot-motion-pattern-model storage unit into prediction motion trajectories. A motion comparing unit compares the input motion trajectory acquired by the motion acquiring unit with the prediction motion trajectories transformed by the motion converting unit. A robot motion selecting unit selects a robot motion pattern having the highest similarity from the robot motion pattern storage unit. The present invention is applicable to a robot apparatus.

Owner:SONY CORP

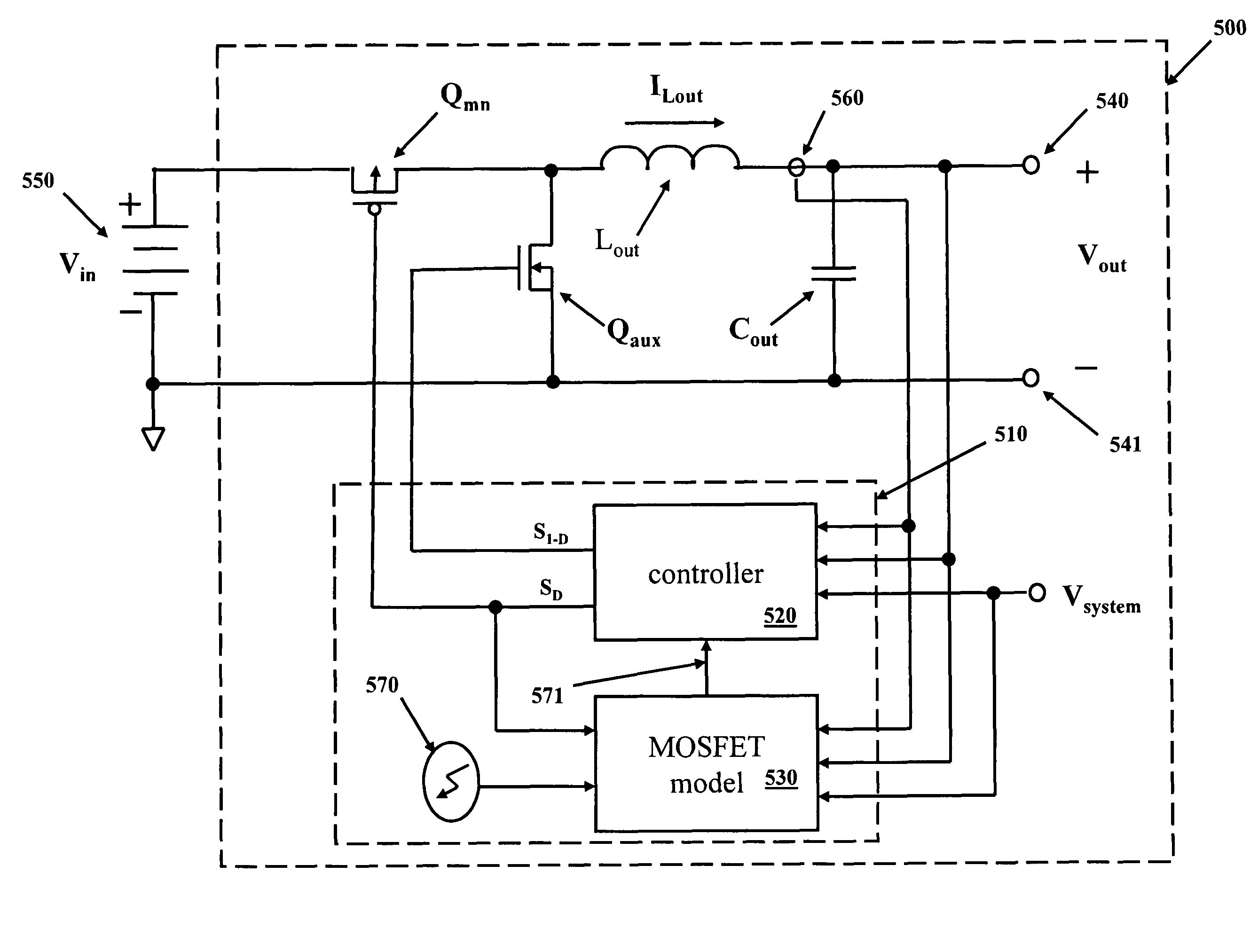

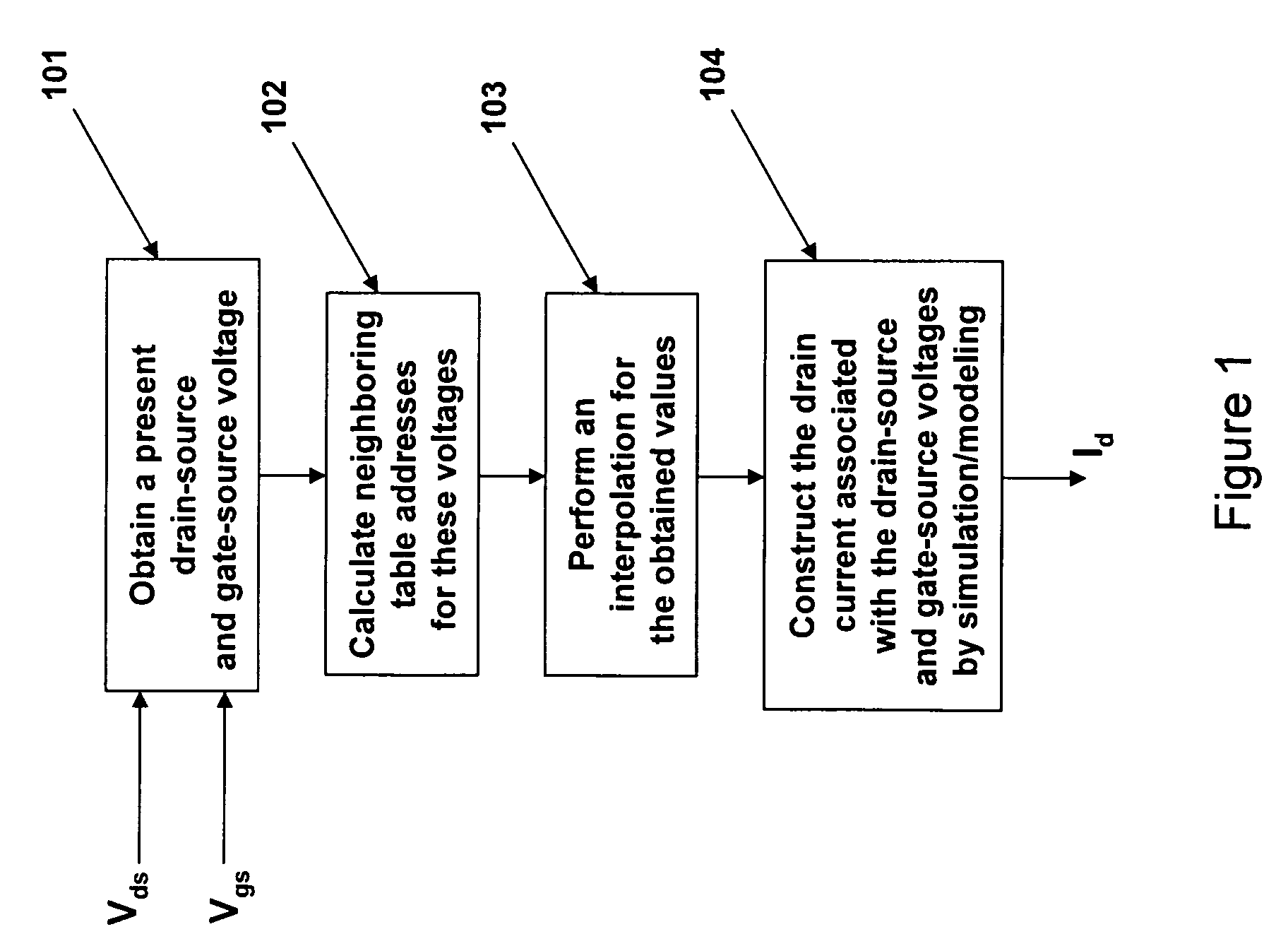

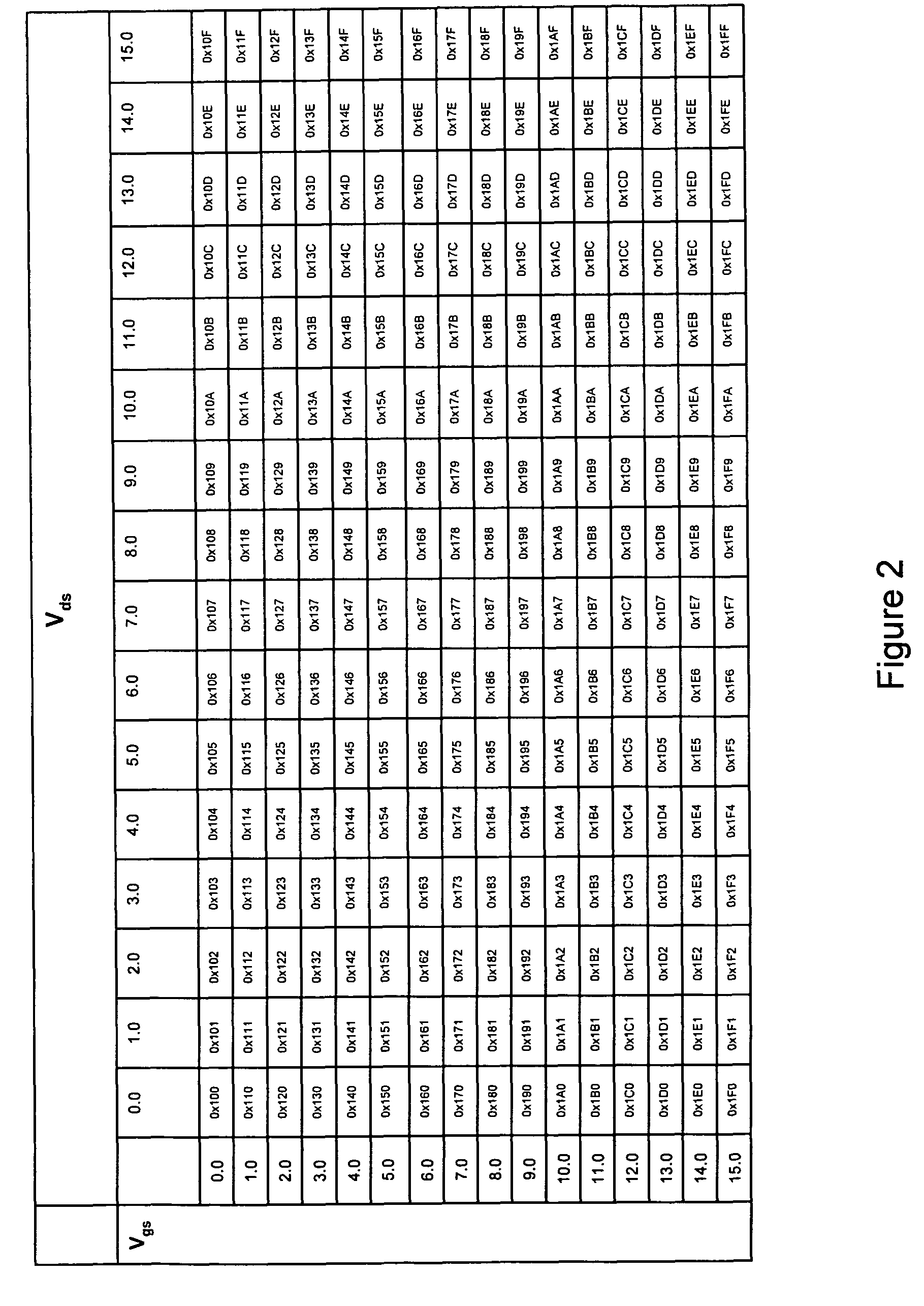

Apparatus for detecting a state of operation of a power semiconductor device

ActiveUS7940034B2TransistorElectronic switchingElectrical resistance and conductancePower semiconductor device

An embodiment of the invention relates to an apparatus including a power semiconductor device and a processor coupled thereto. The processor is configured to provide a control signal to the power semiconductor device to regulate an output characteristic of the apparatus. The processor models an internal characteristic of the power semiconductor device and alters the control signal if the modeled internal characteristic crosses a threshold value. In an exemplary embodiment, the internal characteristic is a channel temperature of a MOSFET. A sensor such as a thermistor is coupled to or included within the processor to sense a parameter separate from the power semiconductor device, such as a processor temperature, and the processor is configured to adapt the modeled internal characteristic to the sensed parameter.

Owner:INFINEON TECH AUSTRIA AG

Extensible embedded simulation test system

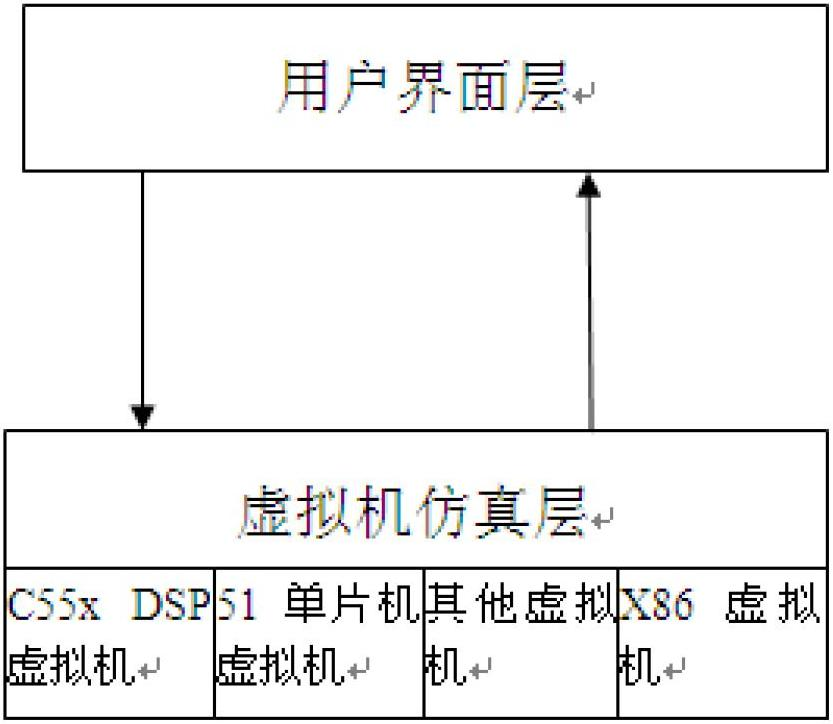

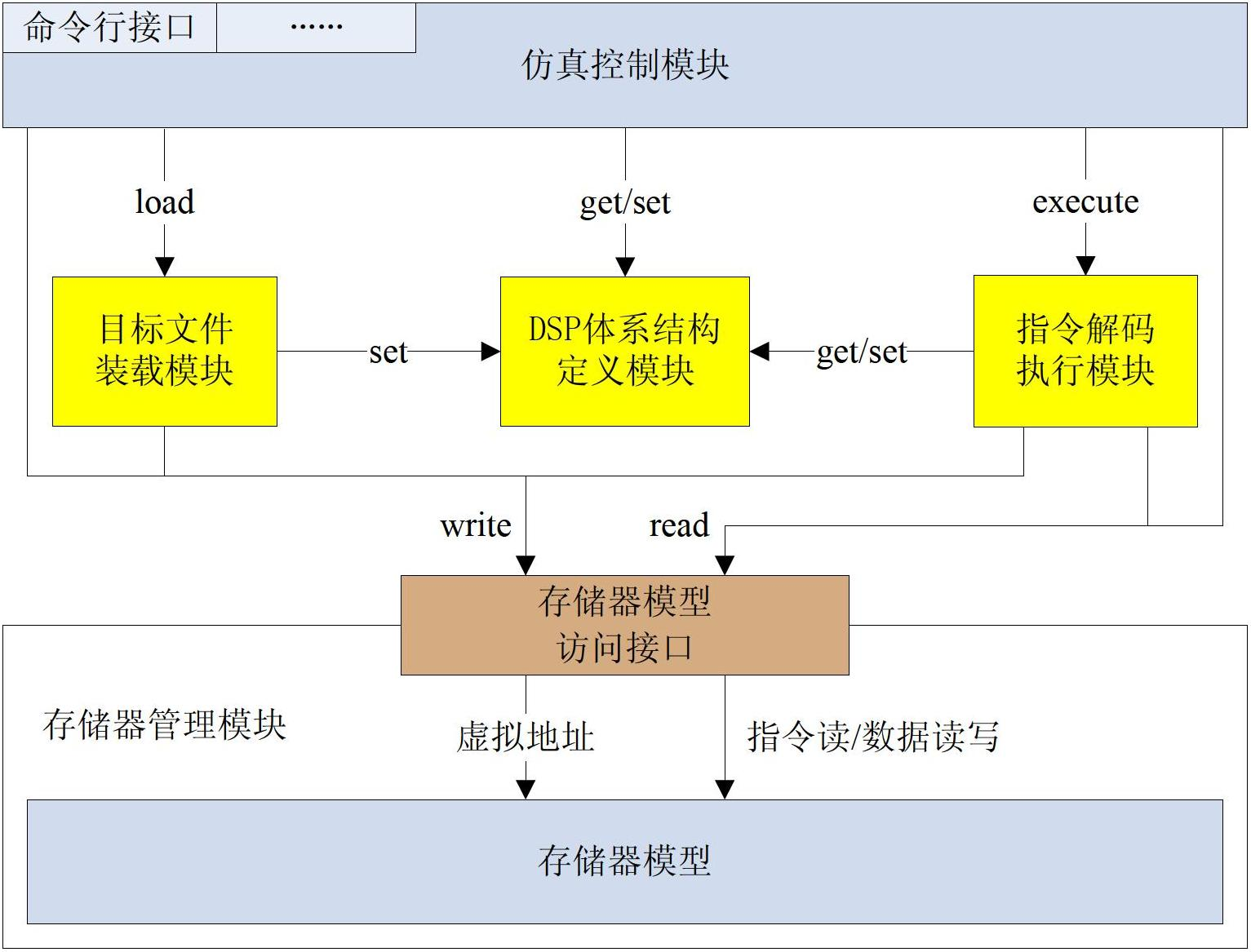

InactiveCN102681941AReduce couplingEasy to Modular DesignSoftware testing/debuggingProcessor modelInteraction layer

The invention provides an extensible embedded simulation test system which is formed through minimizing coupling degree between an operation interface and an underlying virtual machine and defining an excellent module design and is used for overcoming the disadvantage of insufficiency of embedded software testing caused by overdependence on target hardware in an embedded software testing process. The system comprises a user interface layer and a virtual machine simulation layer, wherein the user interface layer is a user interaction layer which is completely independent of other layers, and is called to interact with the underlying virtual machine only through command lines, and the virtual machine simulation layer is used for realizing the simulation of the target hardware. The system is applicable to virtual machine frameworks of a plurality of processors, establishes abstract embedded processor models, and provides an interface so as to integrate an upper software testing function.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

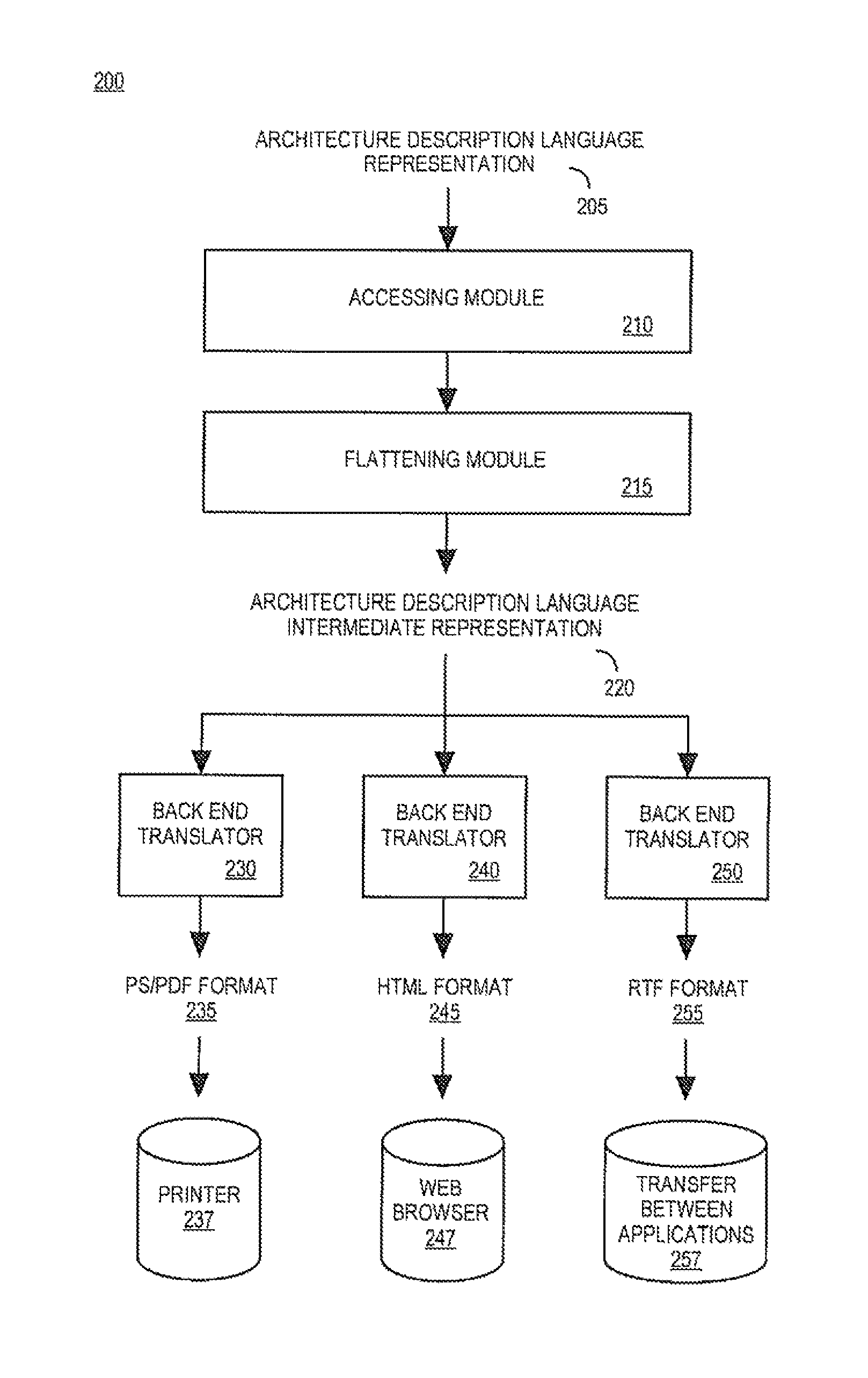

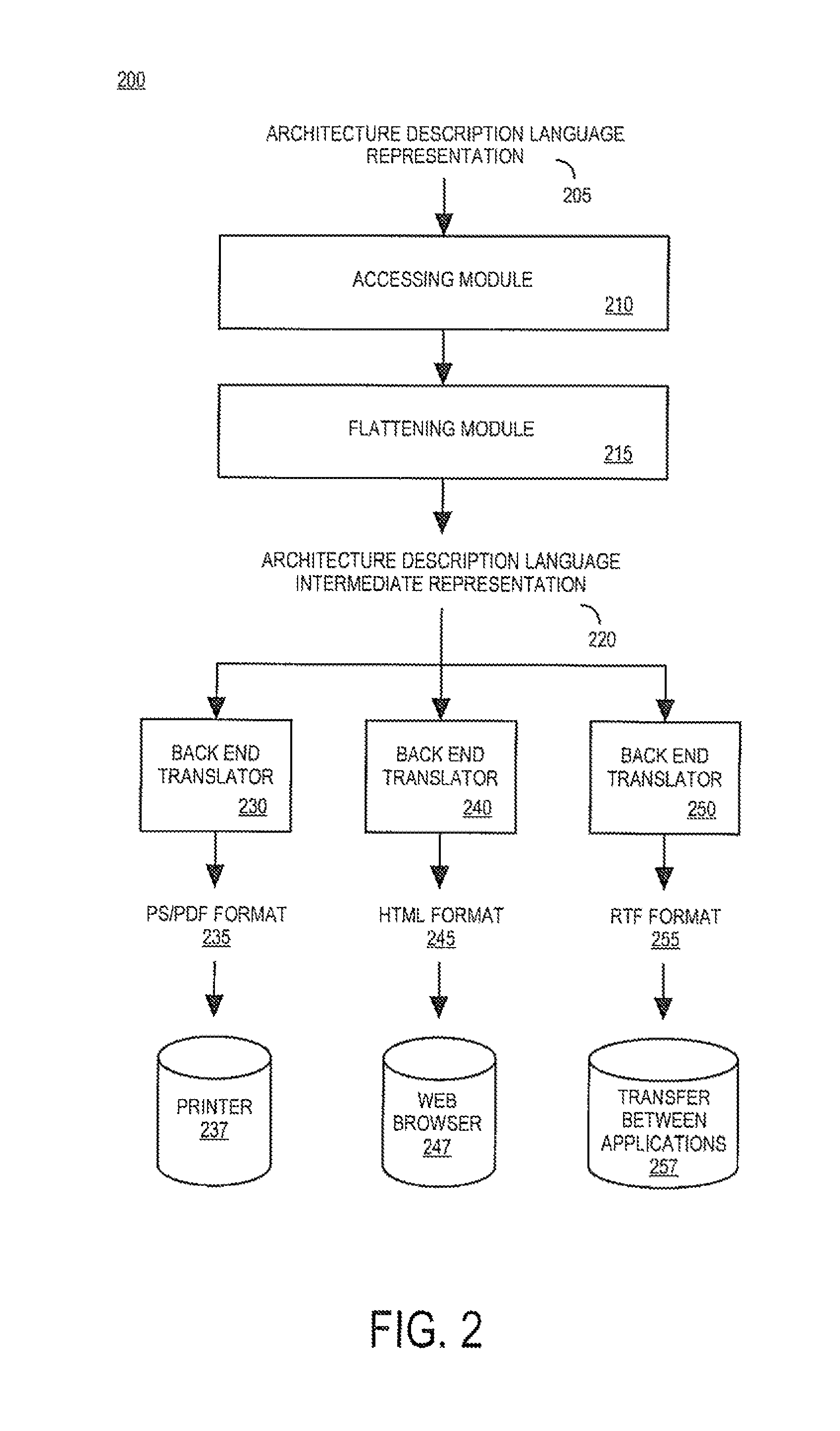

Techniques for automatic generation of instruction-set documentation

ActiveUS8522221B1Program documentationProgram controlArchitecture description languageProcessor model

A method and system for the automatic generation of user guides. Specifically, the method of the present invention includes accessing an abstract processor model of a processor, wherein said abstract processor model is represented using a hierarchical architecture description language (ADL). The abstract processor model includes a plurality of instructions arranged in a hierarchical structure. An internal representation of the abstract processor model is generated by flattening the abstract processor model. The flattening process generates a plurality of rules grouped by common convergent instructions. Each rule describes an instruction path through the hierarchical structure that converges at a corresponding convergent instruction. An instruction-set documentation is automatically generated from the plurality of rules, wherein the instruction-set documentation is arranged convergent instruction by convergent instruction.

Owner:SYNOPSYS INC

Information processing apparatus and method, program storage medium, and program

InactiveUS6980889B2Promote generationReduce necessityProgramme-controlled manipulatorComputer controlProcessor modelInformation processing

An input motion acquiring unit acquires a motion trajectory of an object from an image recognizing unit. A dynamic modeling processor models a plurality of robot motion patterns stored in a robot motion pattern storage unit in a dynamic system form, and stores the modeled robot motion patterns into a robot-motion-pattern-model storage unit. A motion converting unit linearly transforms the plurality of robot motion dynamic models stored in the robot-motion-pattern-model storage unit into prediction motion trajectories. A motion comparing unit compares the input motion trajectory acquired by the motion acquiring unit with the prediction motion trajectories transformed by the motion converting unit. A robot motion selecting unit selects a robot motion pattern having the highest similarity from the robot motion pattern storage unit. The present invention is applicable to a robot apparatus.

Owner:SONY CORP

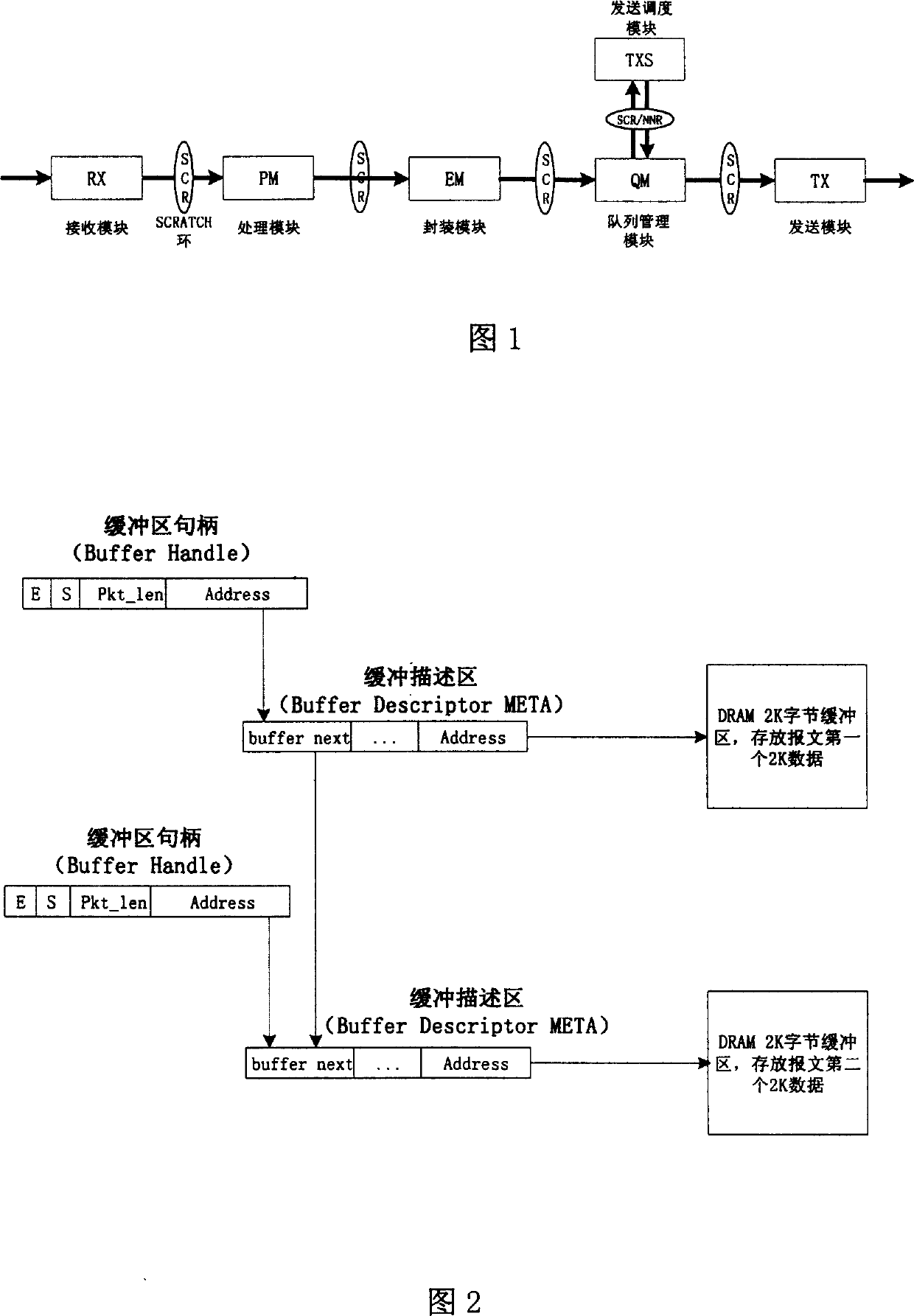

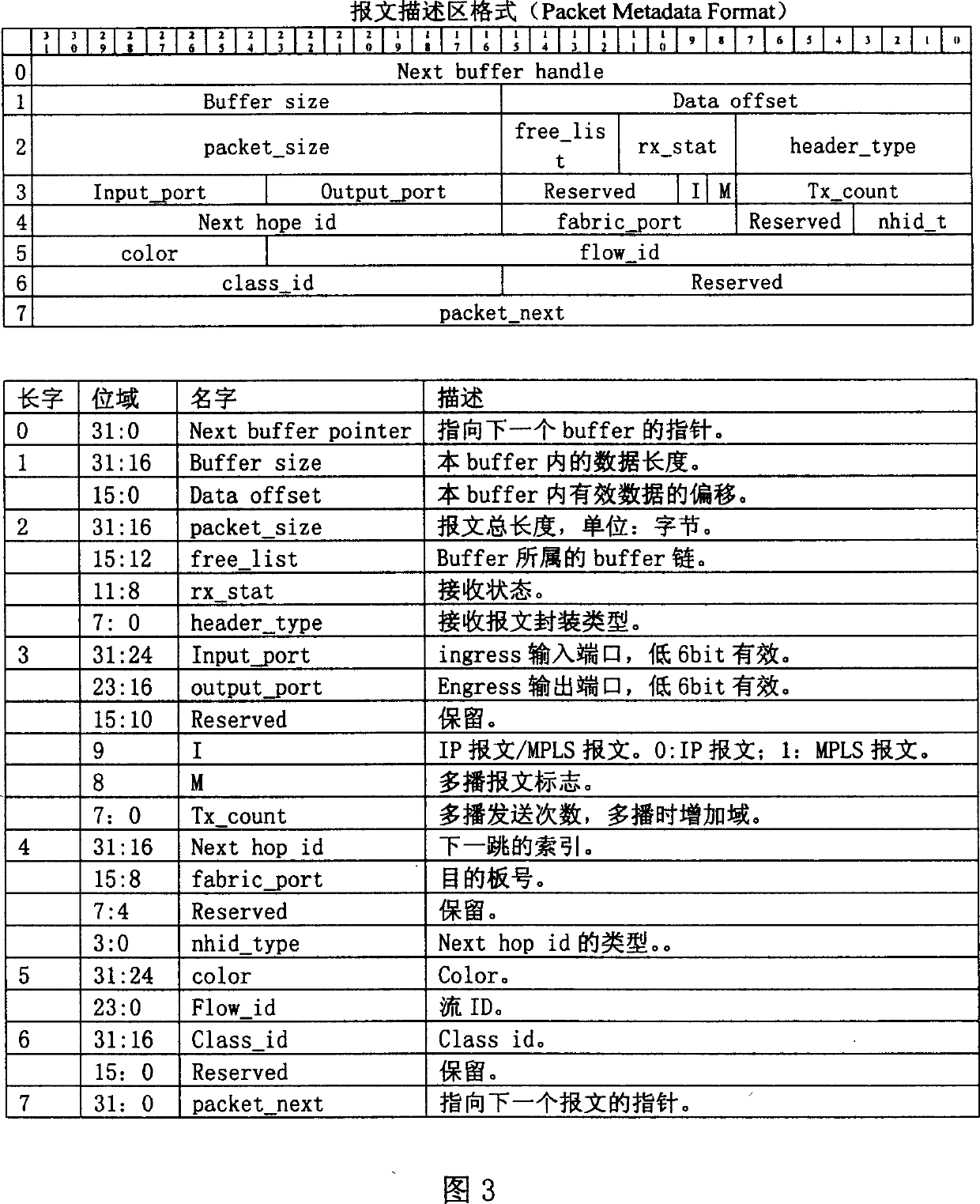

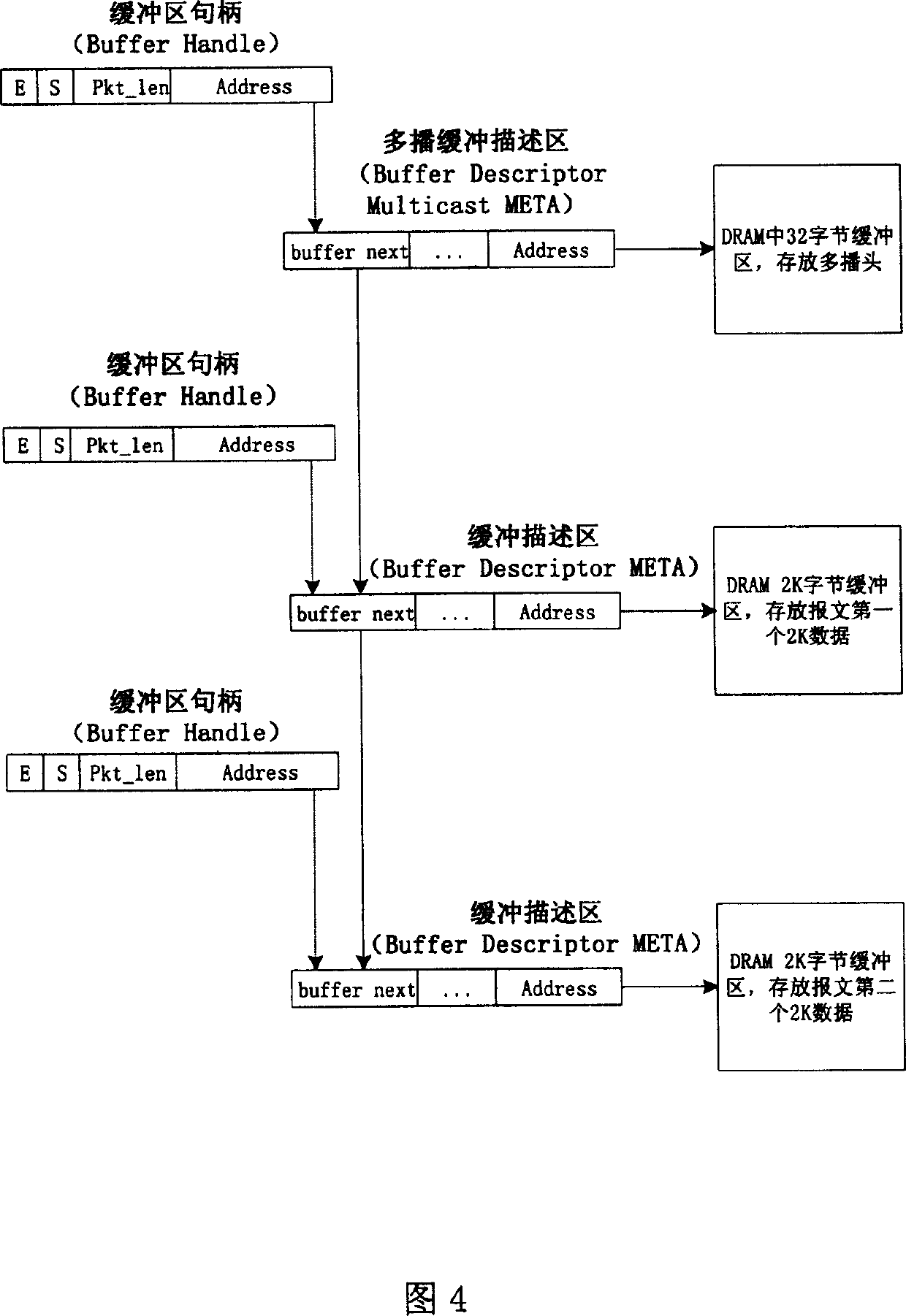

Method of realizing multitransmission

InactiveCN1556626AImprove forwarding efficiencyImprove performanceStore-and-forward switching systemsProcessor modelNetwork communication

The invention provides a method for multiple broadcasting and repeating on the Intel IXP2400 network processor, which belongs to computer network communication field, the method includes: the receiving model receives the message from the outer port, which is transmitted to the enclosing model (EM) after being processed by the processor model, the enclosing model (EM) searches the multi-broadcast adjoined enclosing table (DMAT) according to the index of multiple broadcast (MID), the table is a chain table, each item stores a export message enclosing format information, then sends a multi-broadcast message head buffer, the message head content is stored in the buffer, forms the multi-broadcast message head META, the META is looped at front of the message SOP META, forms a message chain table, the message is transmitted to the queue managing model (QM), the transmitting dispatching model (TXS) dispatches the package to the transmitting model (TX), then the message is transmitted by the transmitting model. The invention amends the message head only, the body is not duplicated, and the repeating efficiency is high.

Owner:HUAWEI TECH CO LTD

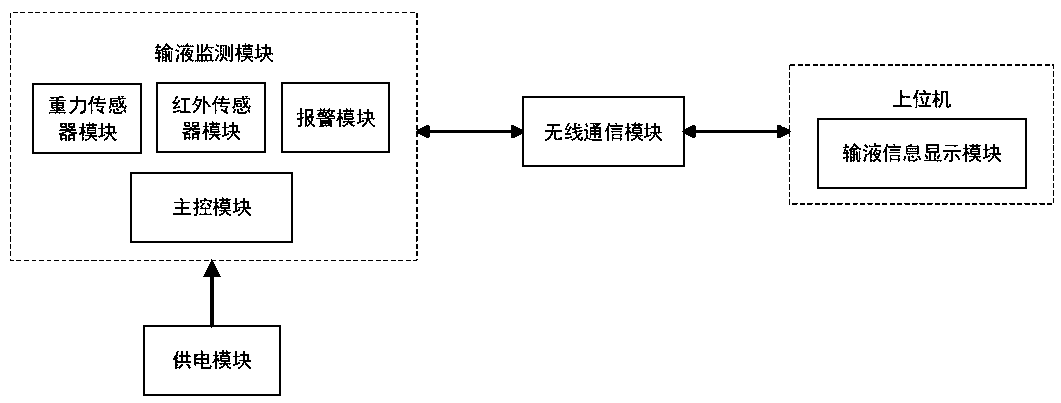

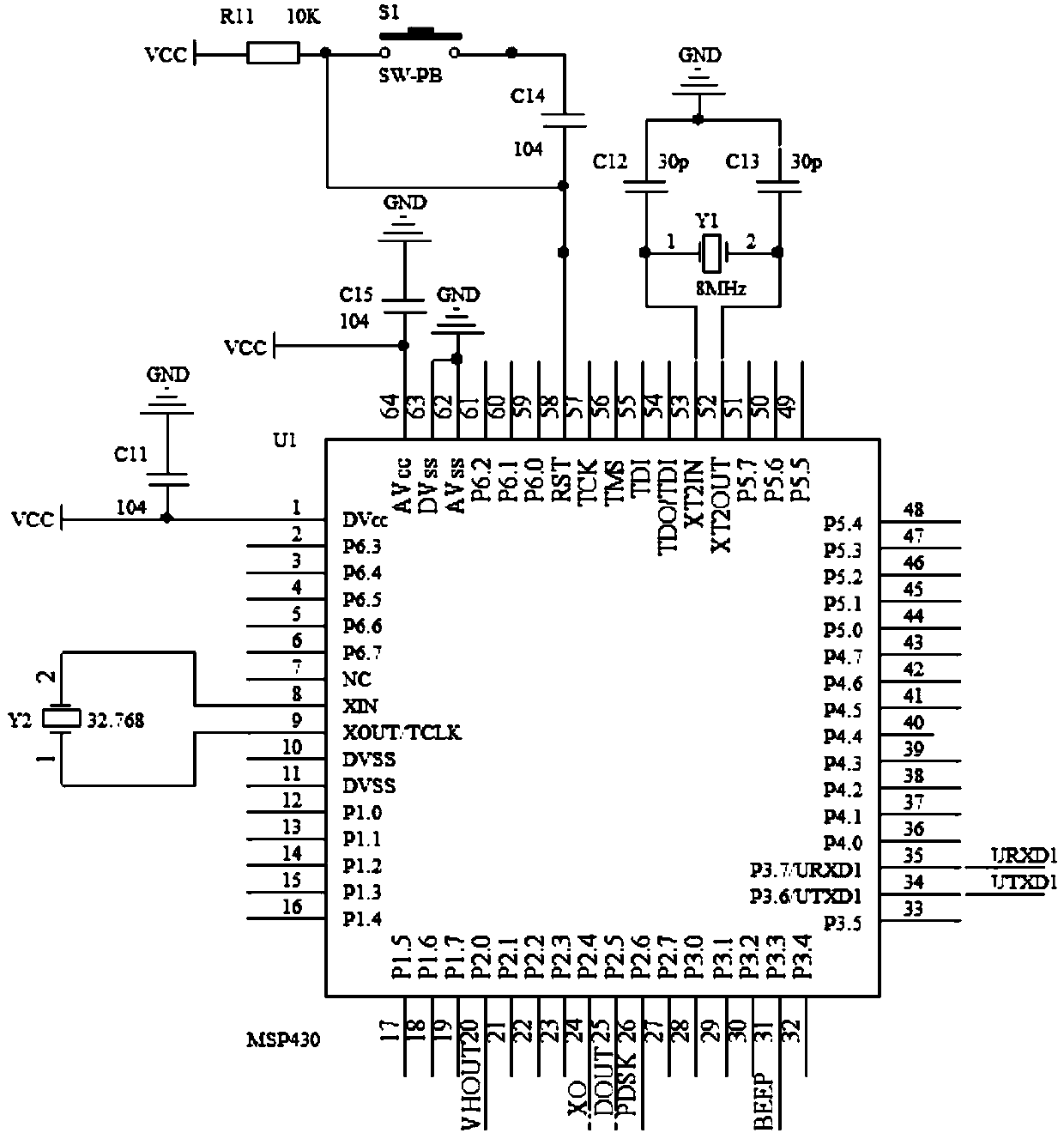

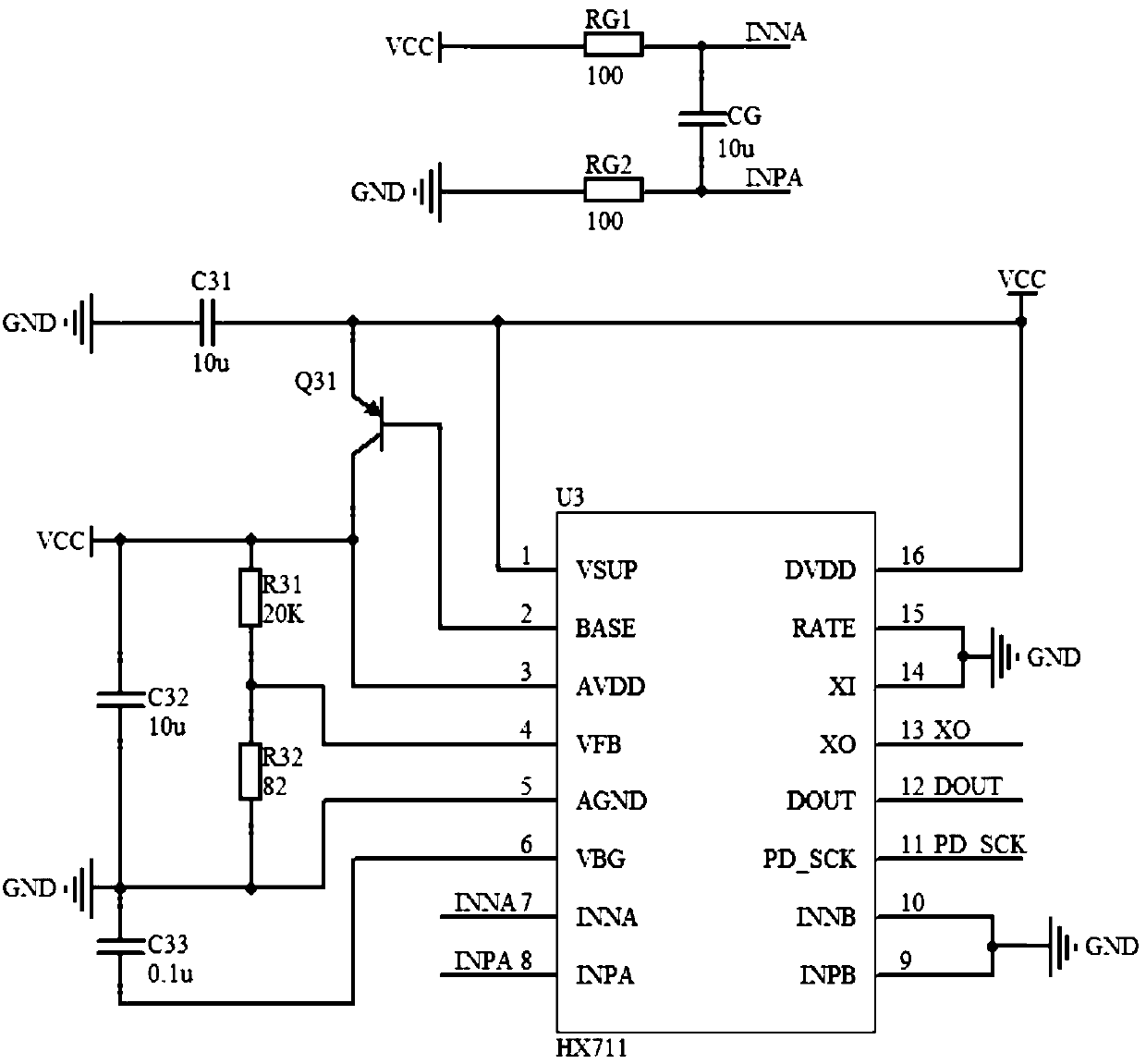

Remote combined unattended medical infusion monitoring system

InactiveCN110368552AShorten the development cycleReduce power consumptionMedical devicesFlow monitorsProcessor modelElectrical resistance and conductance

The invention provides a remote combined unattended medical infusion monitoring system, which comprises an infusion monitoring module, a wireless communication module, an information display module and a power supply module, wherein the infusion monitoring module comprises a main control module, a gravity sensor module, an infrared sensor module and an alarm module which are connected with the main control module; the central processor model of the main control module is MSP430F149REV; the gravity sensor module is mounted on a hook of an infusion frame; an infrared pipe sensor, which is U-shaped, is mounted on the outer wall above a Murphy dropper; the alarm module consists of a buzzer, a triode and a resistor; the wireless communication module is connected with the main control module andcarries out wireless transmission of information through a ZigBee technology; the wireless communication module comprises a chip with a model number of CC2530; and the information display module is connected with the wireless communication module. The situation that monitoring and alarming cannot be realized due to failure of a single sensor is solved, and the combined signal monitoring is reliable and has high accuracy.

Owner:JIANGSU OPEN UNIV

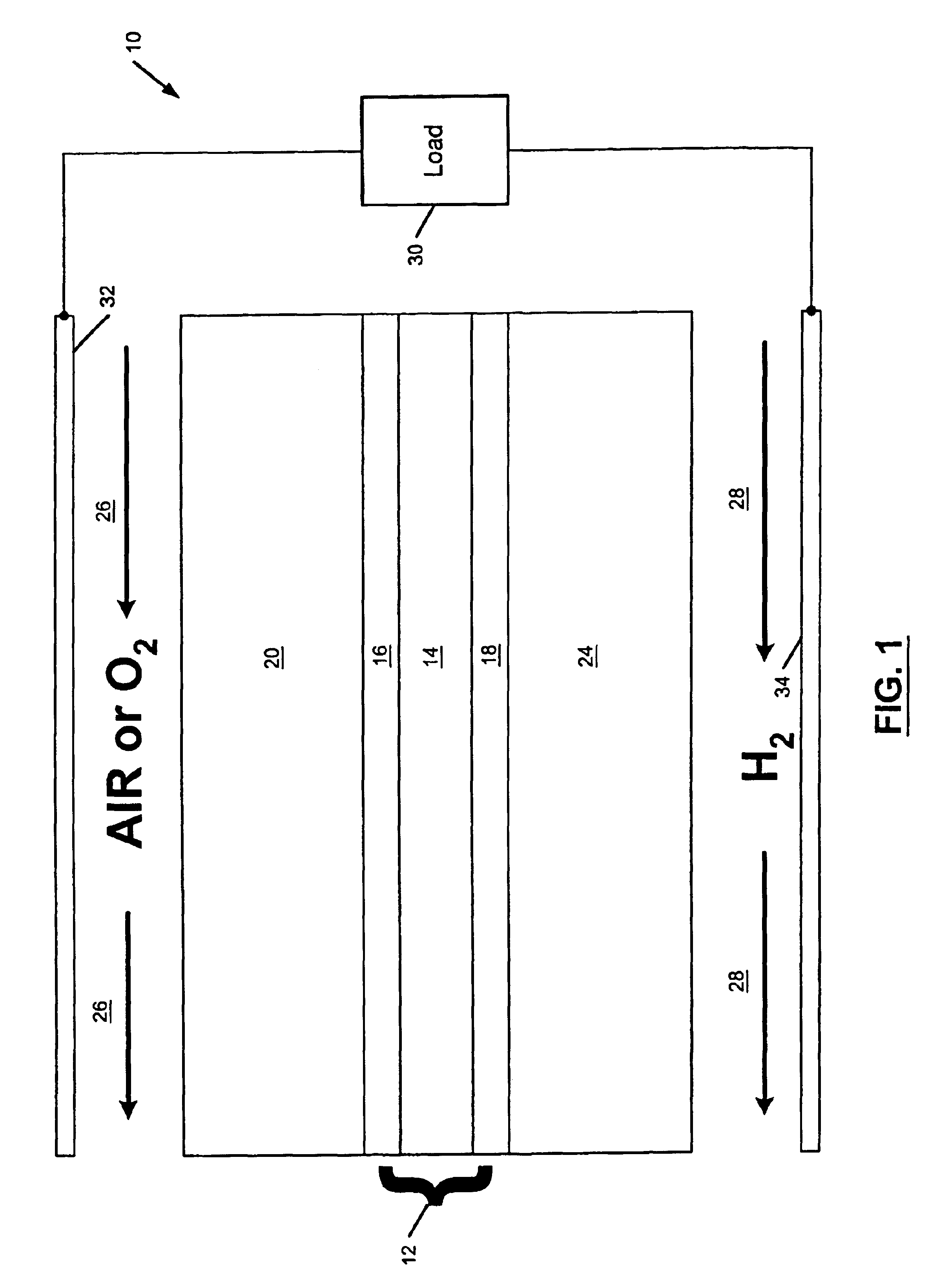

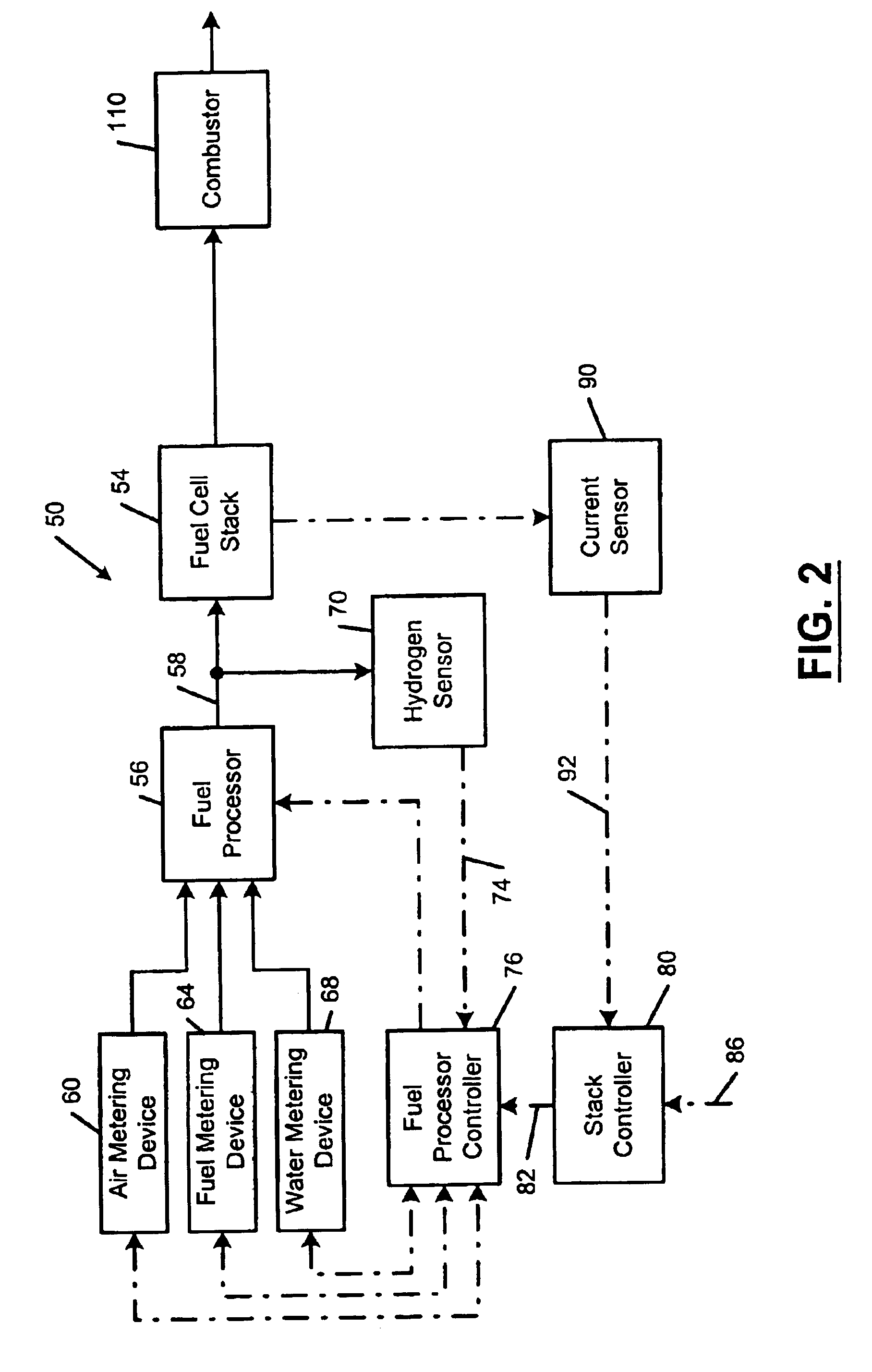

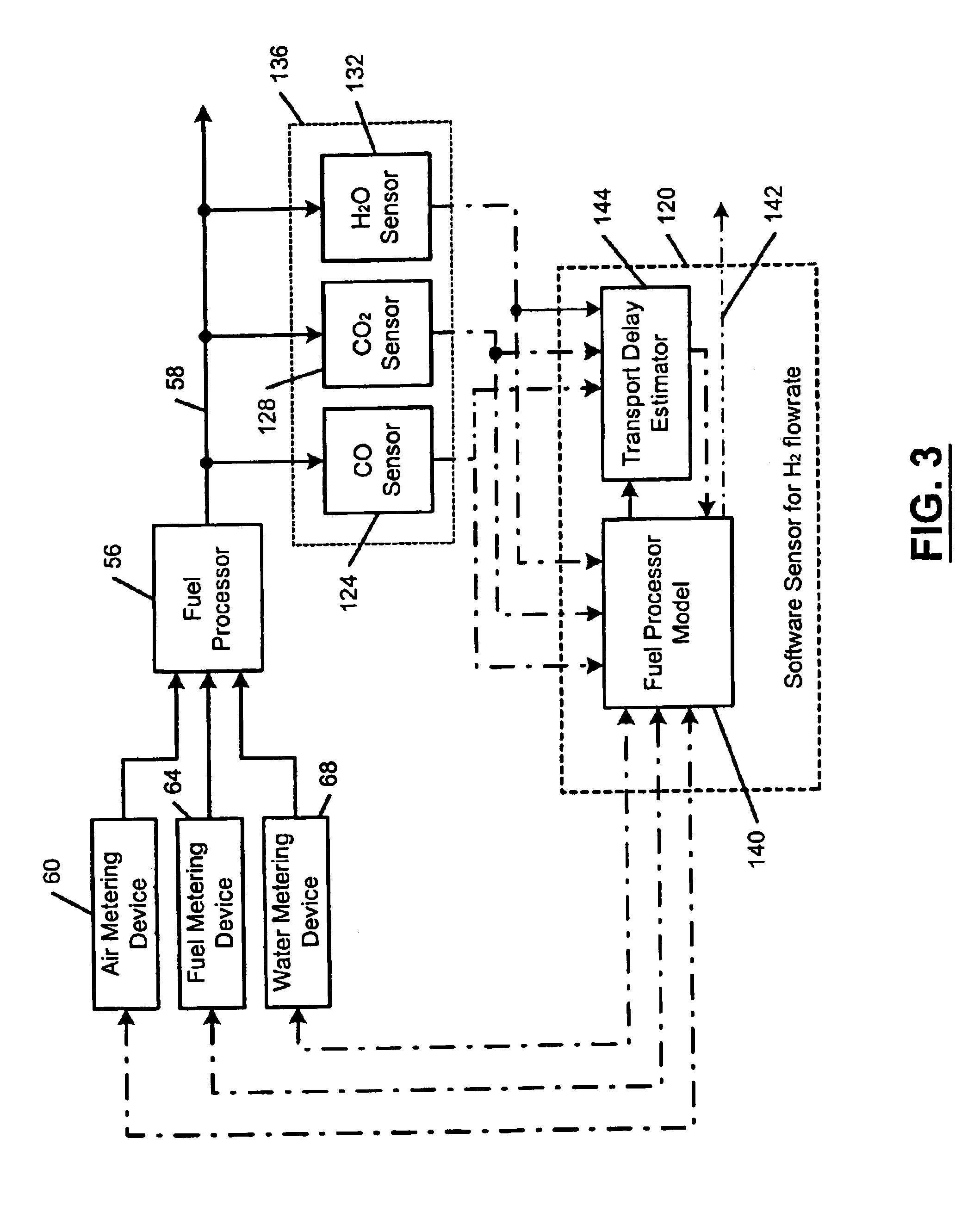

Hydrogen sensor for fuel processors of a fuel cell

InactiveUS6841292B2Photography auxillary processesElectrolysis componentsProcessor modelHydrogen concentration

A method and apparatus estimate hydrogen concentration in a reformate stream produced by a fuel processor of a fuel cell. A sensor measures carbon monoxide, carbon dioxide, and water in the reformate stream. A fuel meter controls fuel input to the fuel processor. An air meter controls air input to the fuel processor. A water meter controls water input to the fuel processor. A transport delay estimator recursively estimates transport delay of the fuel processor. A hydrogen estimator associated with the transport delay estimator, the air, water and fuel meters, and the sensor estimates hydrogen concentration in the reformate stream. The hydrogen estimator includes a fuel processor model that is adjusted using the estimated transport delay. The carbon monoxide, the carbon dioxide and the water are measured using a nondispersive infrared (NDIR) sensor.

Owner:GENERAL MOTORS COMPANY

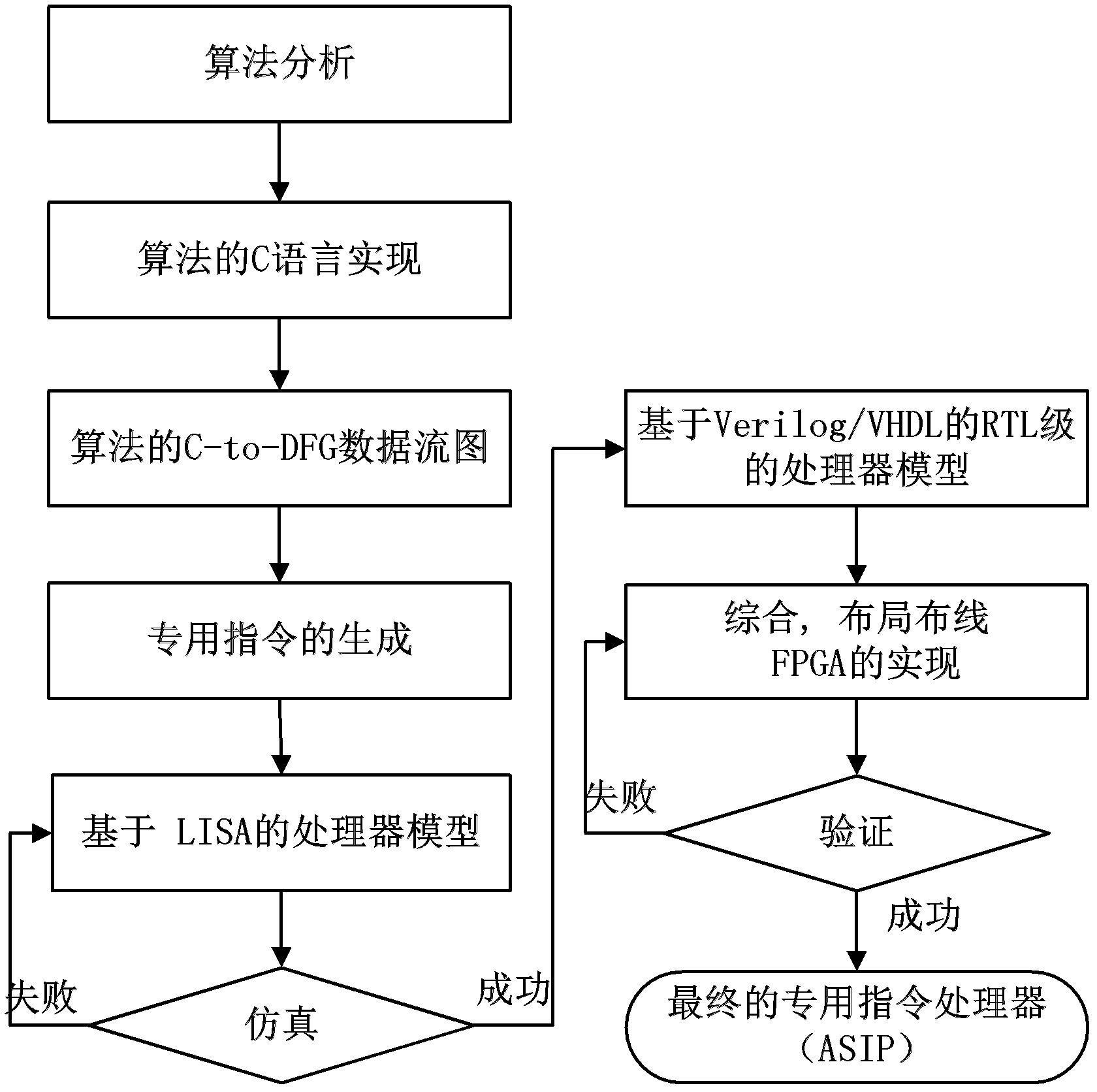

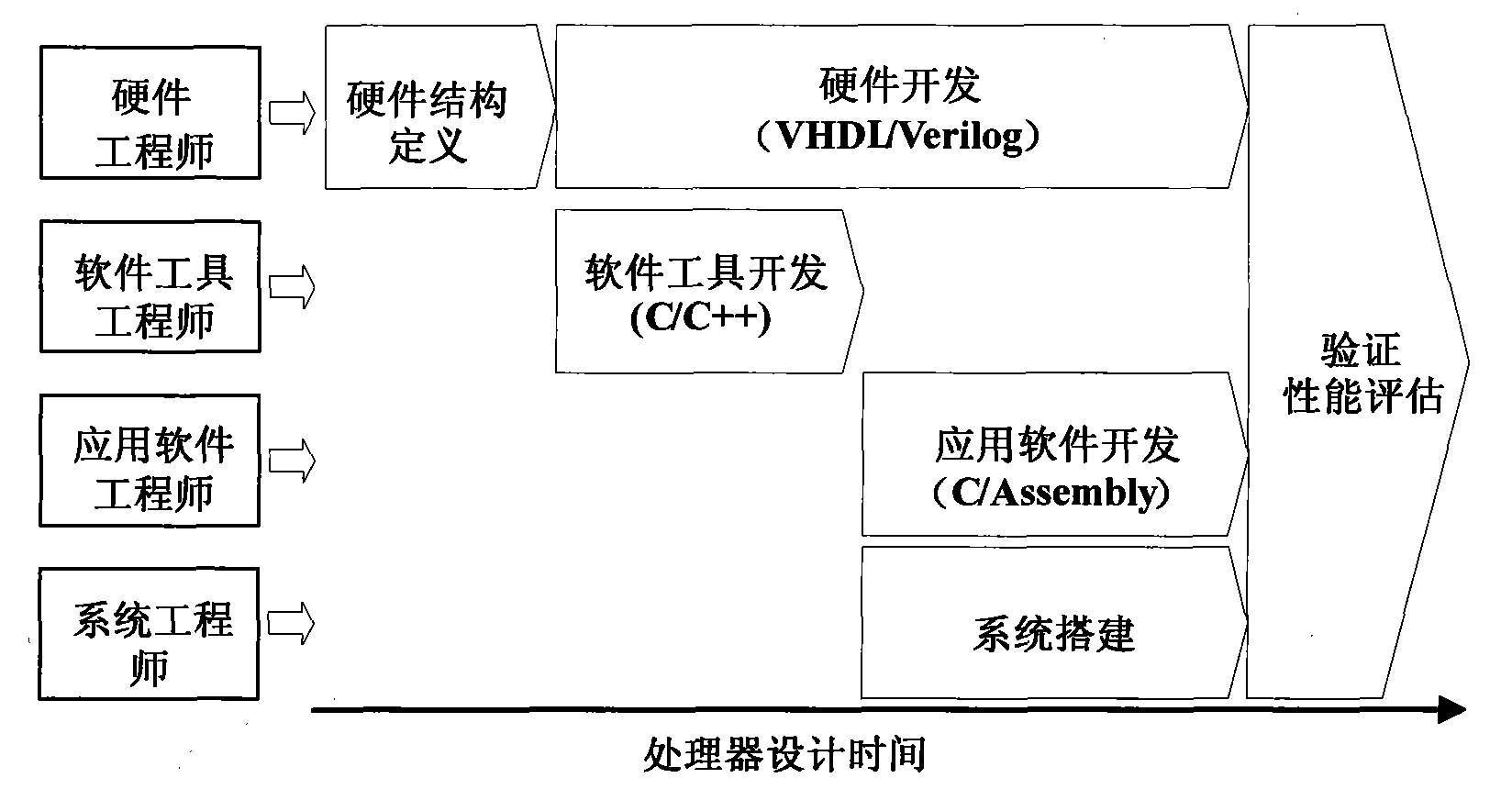

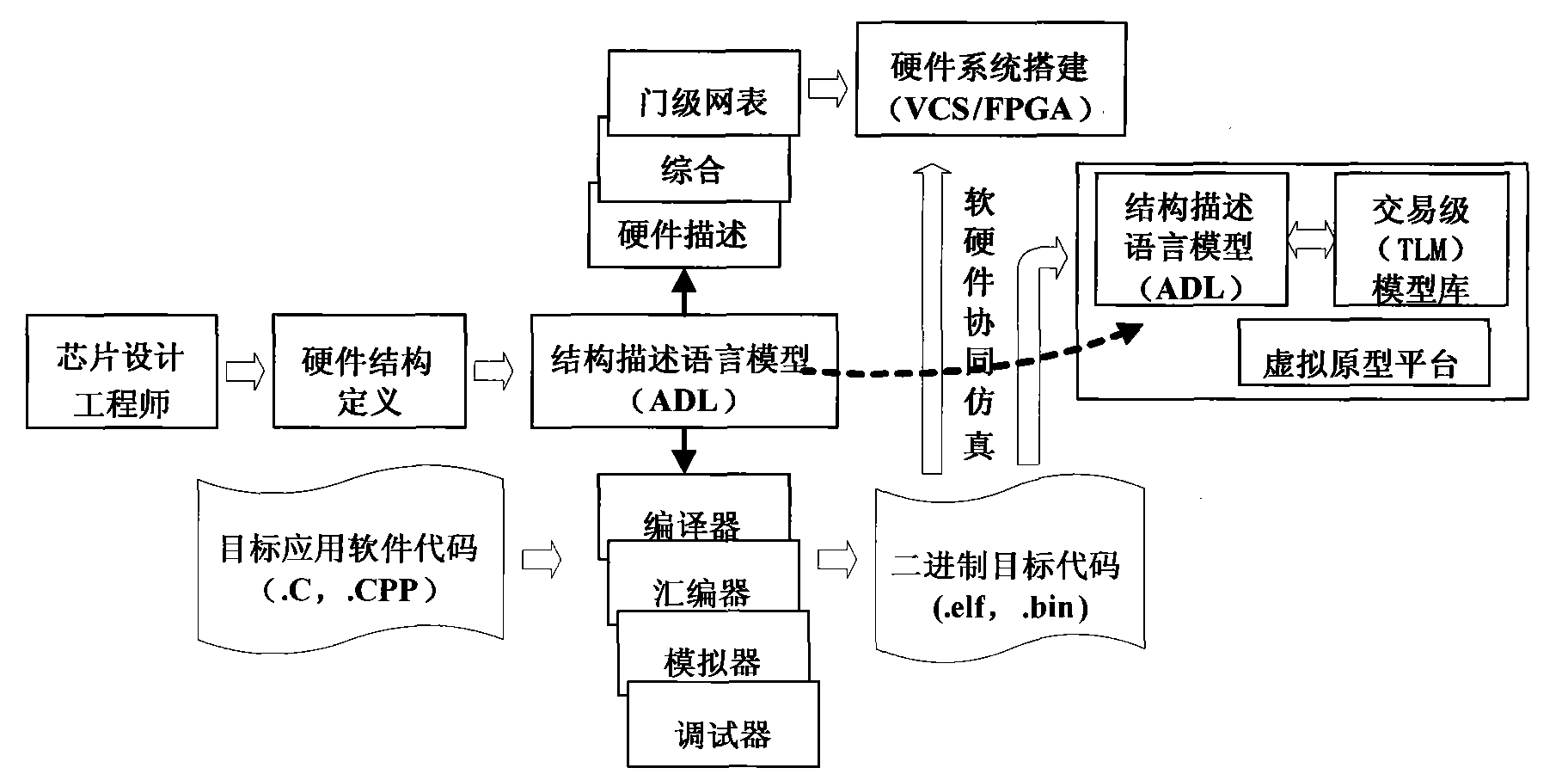

Method for designing specific instruction set processor

ActiveCN101561833AAccelerate Design CycleImprove performanceSpecial data processing applicationsProcessor modelComputer architecture

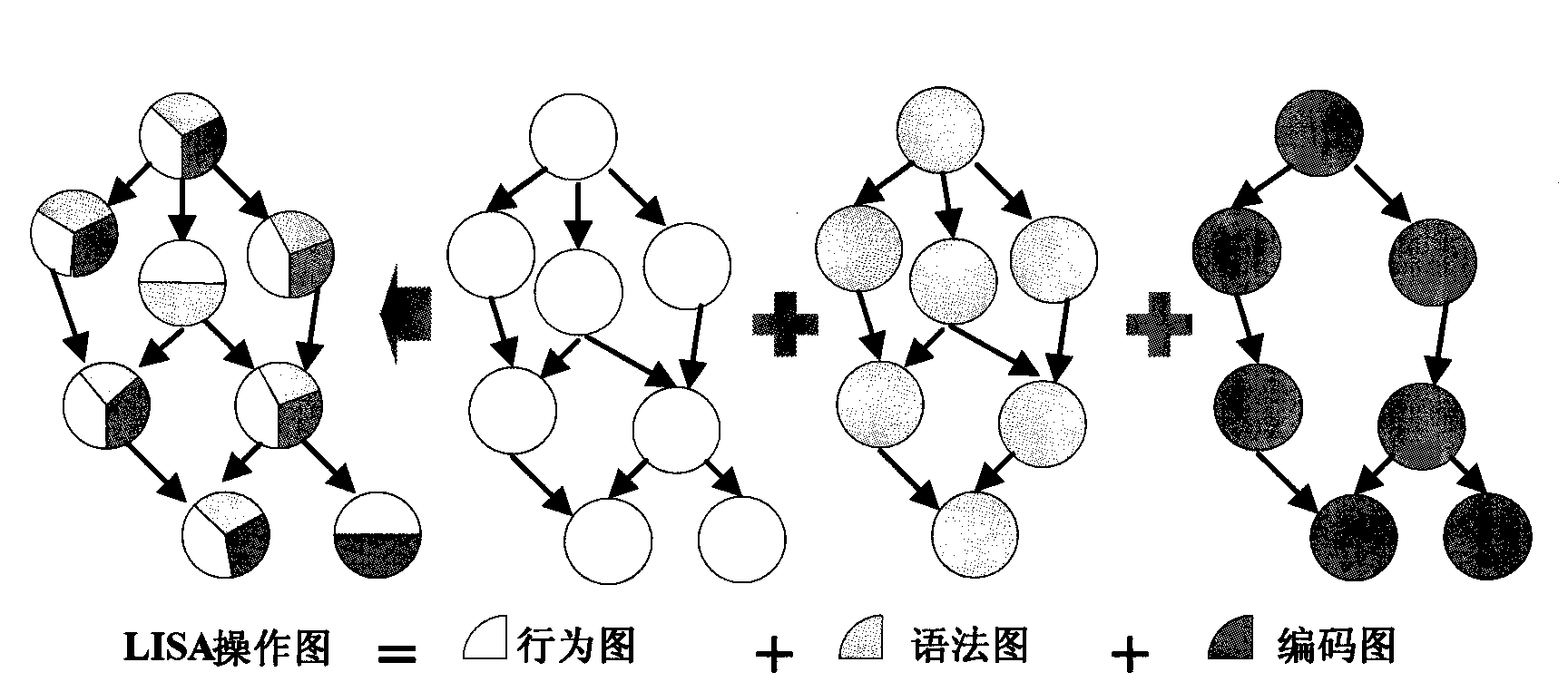

The invention relates to a method for designing a specific instruction set processor, and the method can make the accuracy performance evaluation at the beginning of designing a chip, advance the test of a specific application, speed up the design process and reduce the re-design possibility which is because the performances of the chip can not achieve the requirements. The method establishes an LISA processor model at the early stage of the design, generates a corresponding software tool by the LISA model, builds up a virtual prototyping platform which is similar to the performances of real hardware on an ARM ESL, including a AHB bus model with precise cycle, an EMI model and an SDRAM model which are needed for designing the platform, searches out the performances under the different situations by repairing the models of the processor, obtains an optical software / hardware dividing method, directly verifies on the models and speeds up the design cycle of the processor.

Owner:SOUTHEAST UNIV

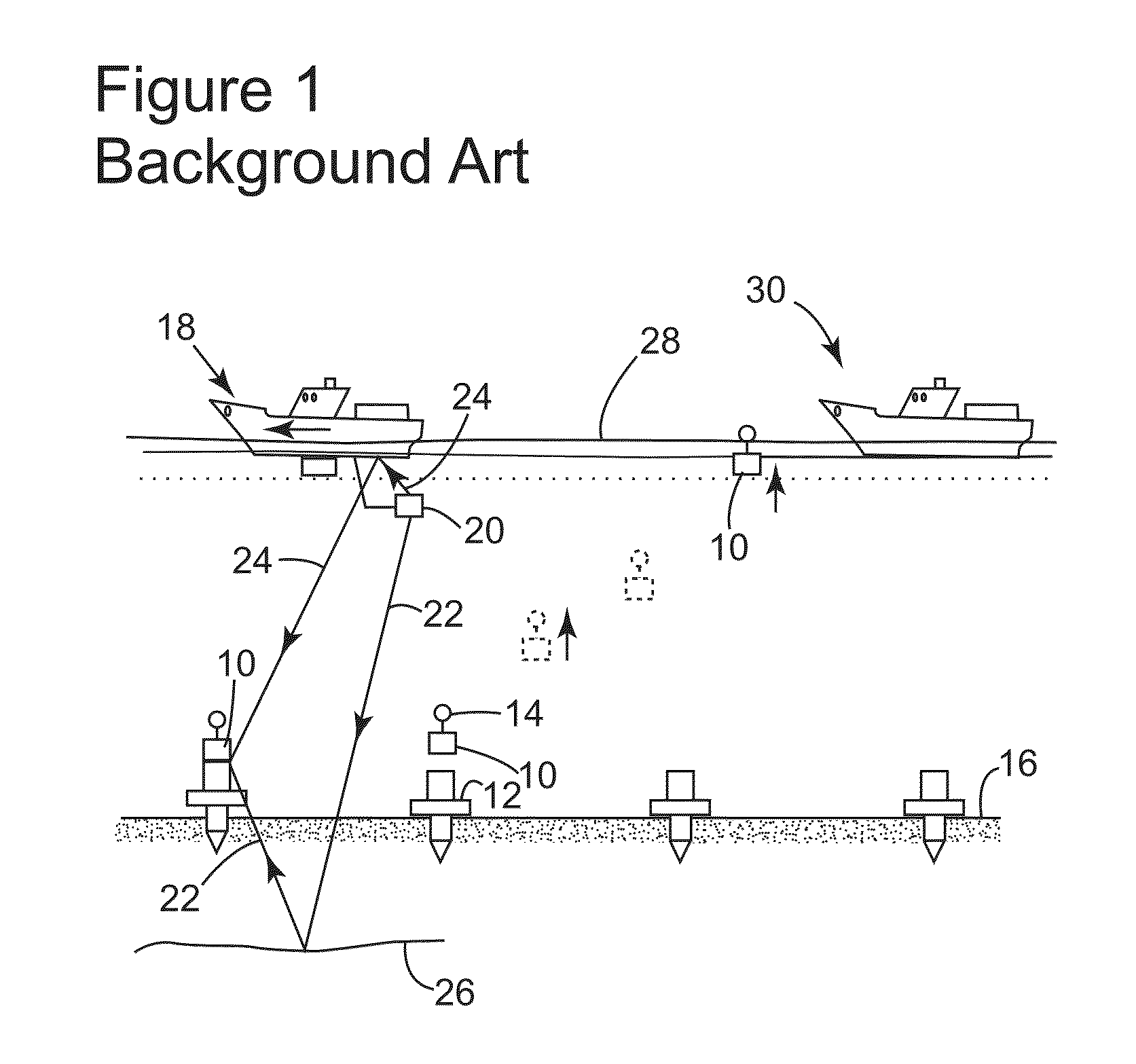

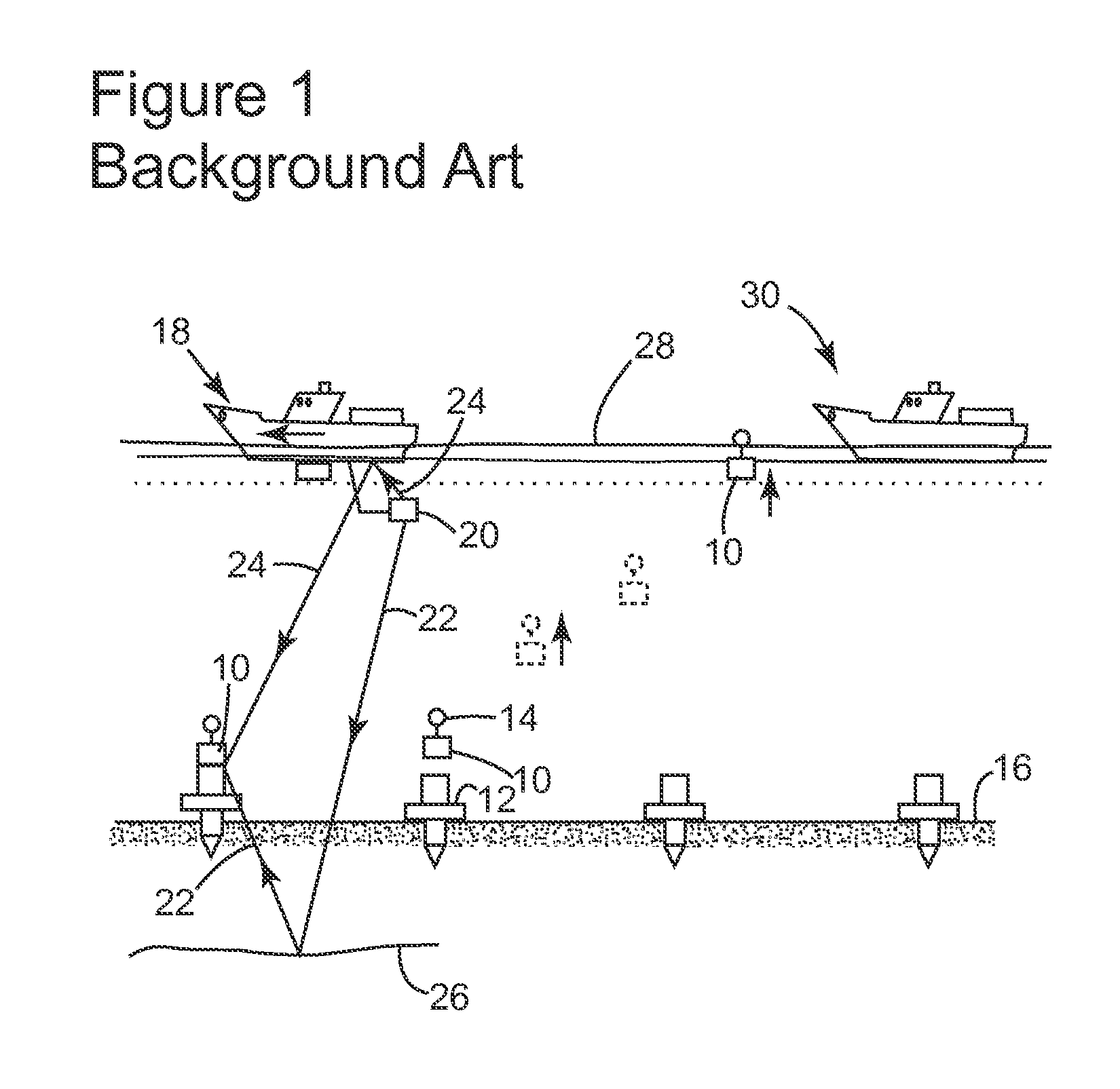

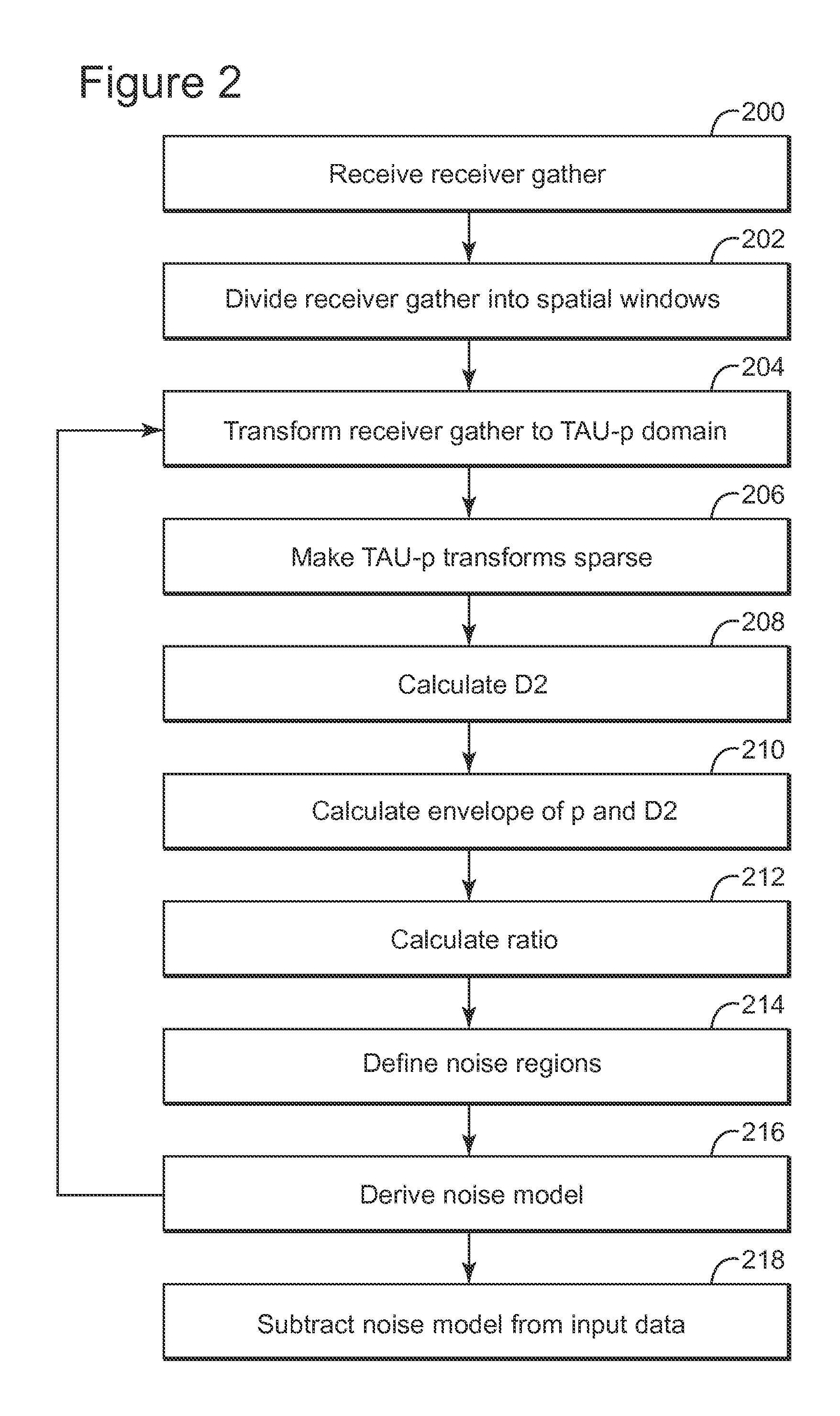

Device and method for denoising ocean bottom data

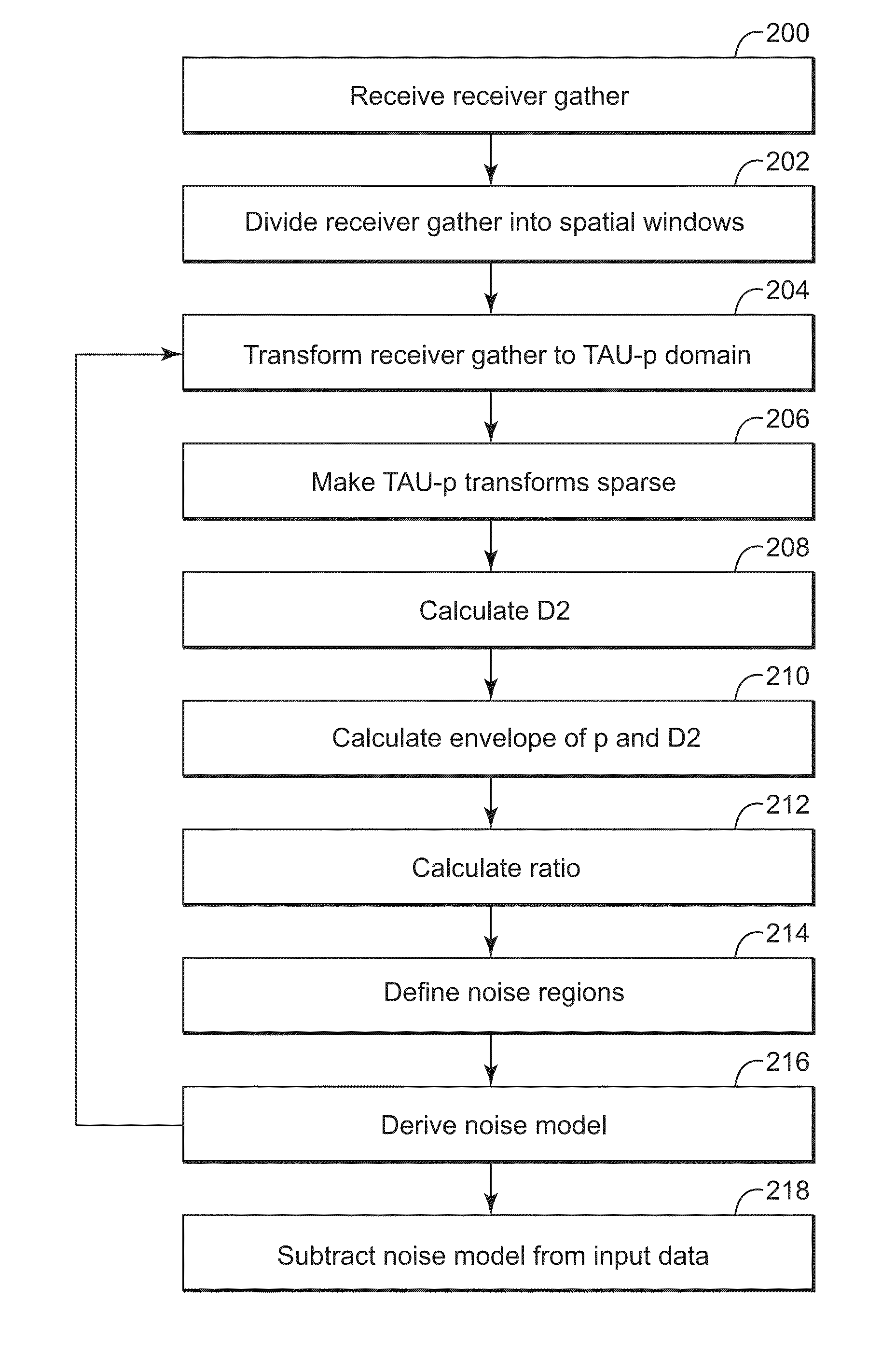

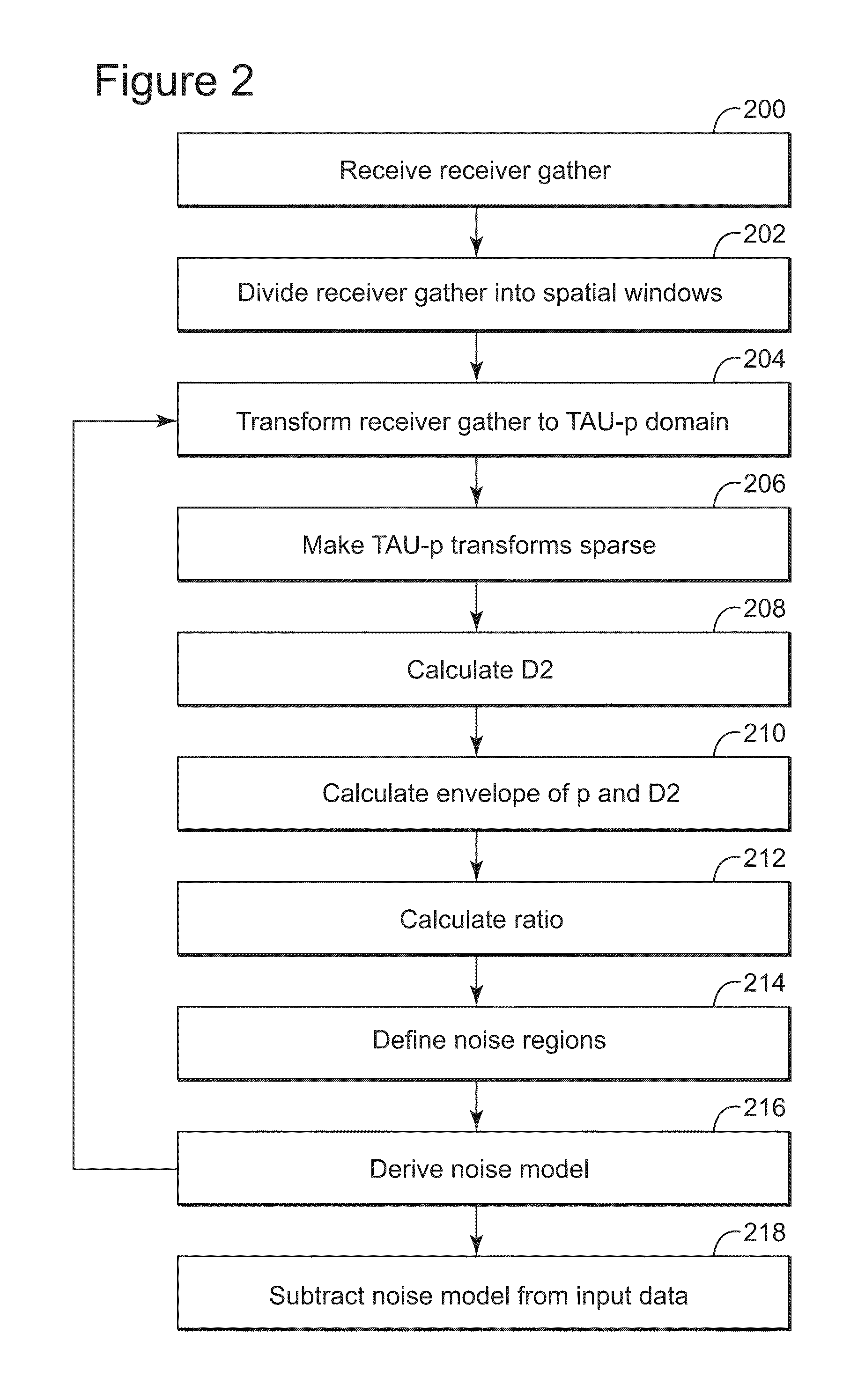

Computing device, computer instructions and method for denoising marine seismic data recorded with first and second seismic sensors. The method includes receiving first seismic data recorded with the first sensor in a time-space domain; receiving second seismic data recorded with the second sensor in the time-space domain, calculating with a processor models of the first and second seismic data in a transform domain that is different from the time-space domain; calculating in the transform domain an energy related to a down-going energy based on the models of the first and second seismic data; determining a noise in the transform domain corresponding to the second seismic data based on the calculated energy; reverse transforming the noise from the transform domain into the time-space domain; and denoising the second seismic data by subtracting the noise in the time-space domain from the second seismic data.

Owner:CGGVERITAS SERVICES

Multi-core-model simulation method, multi-core model simulator, and computer product

Core model processing of a processor model PE1 and a processor model PE2 is serialized. Therefore, processing time for the inter-core-model communication is required between the core model processing of a first processor model and the core model processing of a second processor model. The inter-core-model communication processing is performed such that the inter-core-model communication required for the simulation processing of a multi-processor model is performed in parallel with the core model processing.

Owner:SOCIONEXT INC

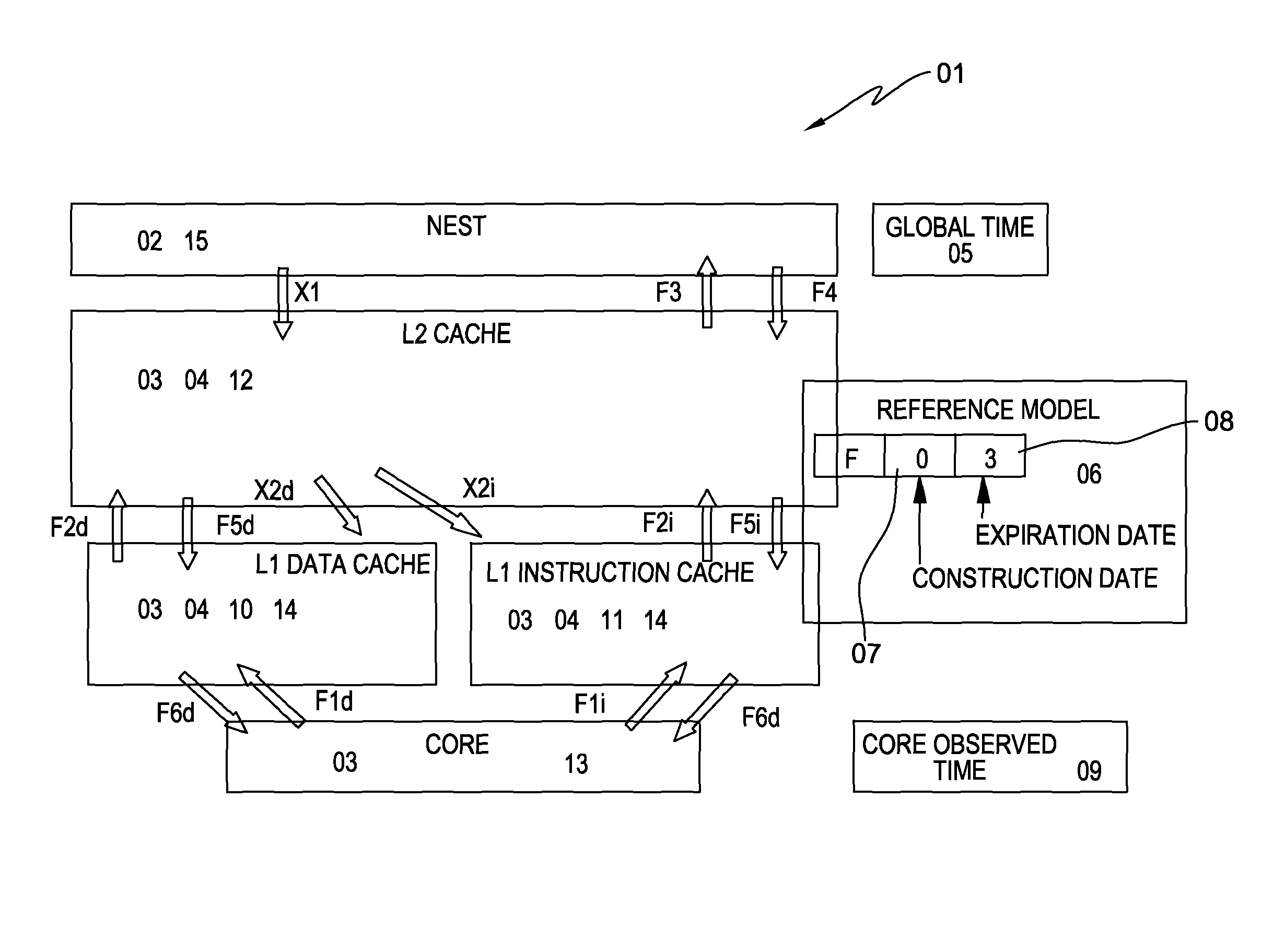

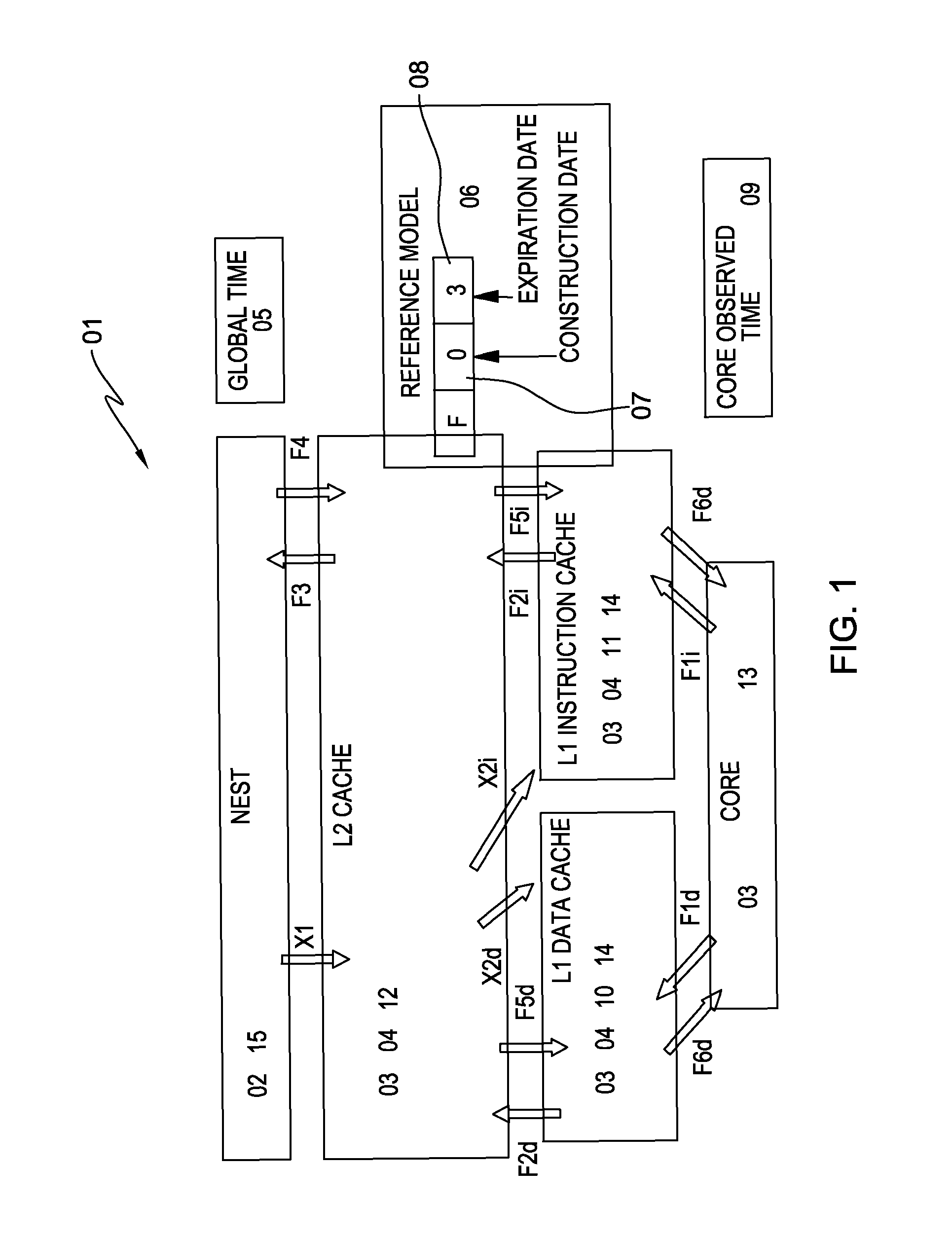

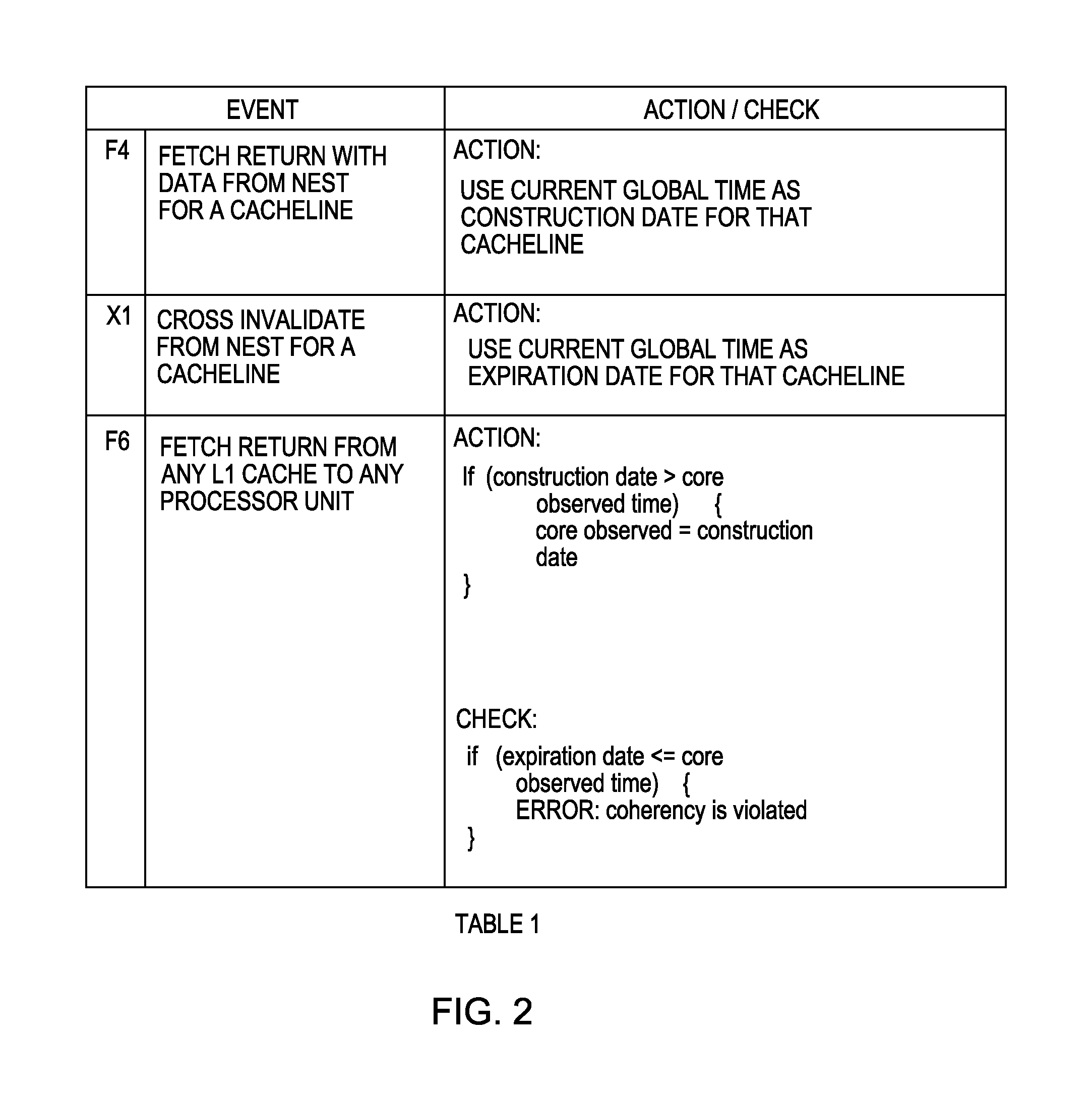

Method to verify an implemented coherency algorithm of a multi processor environment

InactiveUS8108197B2Easy to controlReduce complexitySpecific program execution arrangementsMemory systemsProcessor modelReference model

A coherency algorithm for a multi processor environment to run on a single processor model is verified by: generating a reference model reflecting a private cache hierarchy of a single processor within the multi processor environment, stimulating the private cache hierarchy with simulated requests and / or cross invalidations from a core side and / or from a nest side, and augmenting all data available in the private cache hierarchy with two construction dates and two expiration dates, which are set based on interface events. Multi processor coherency is not observed if the cache hierarchy ever returns data to the processor with an expiration date that is older than the latest construction date of all data used before. Further, a single processor model and a computer program product can be employed to execute the method.

Owner:IBM CORP

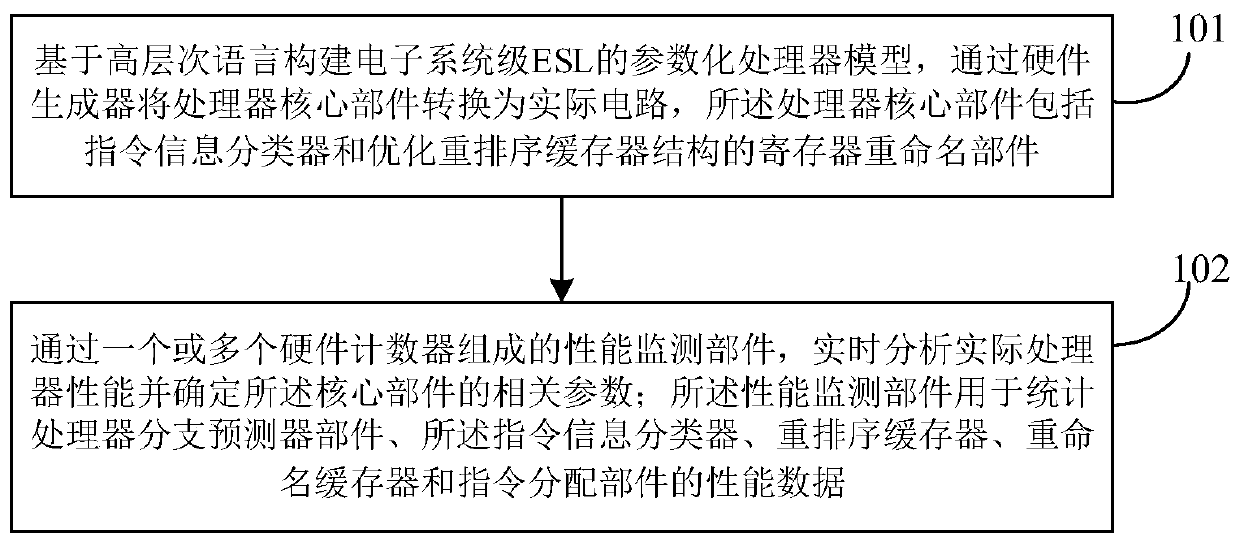

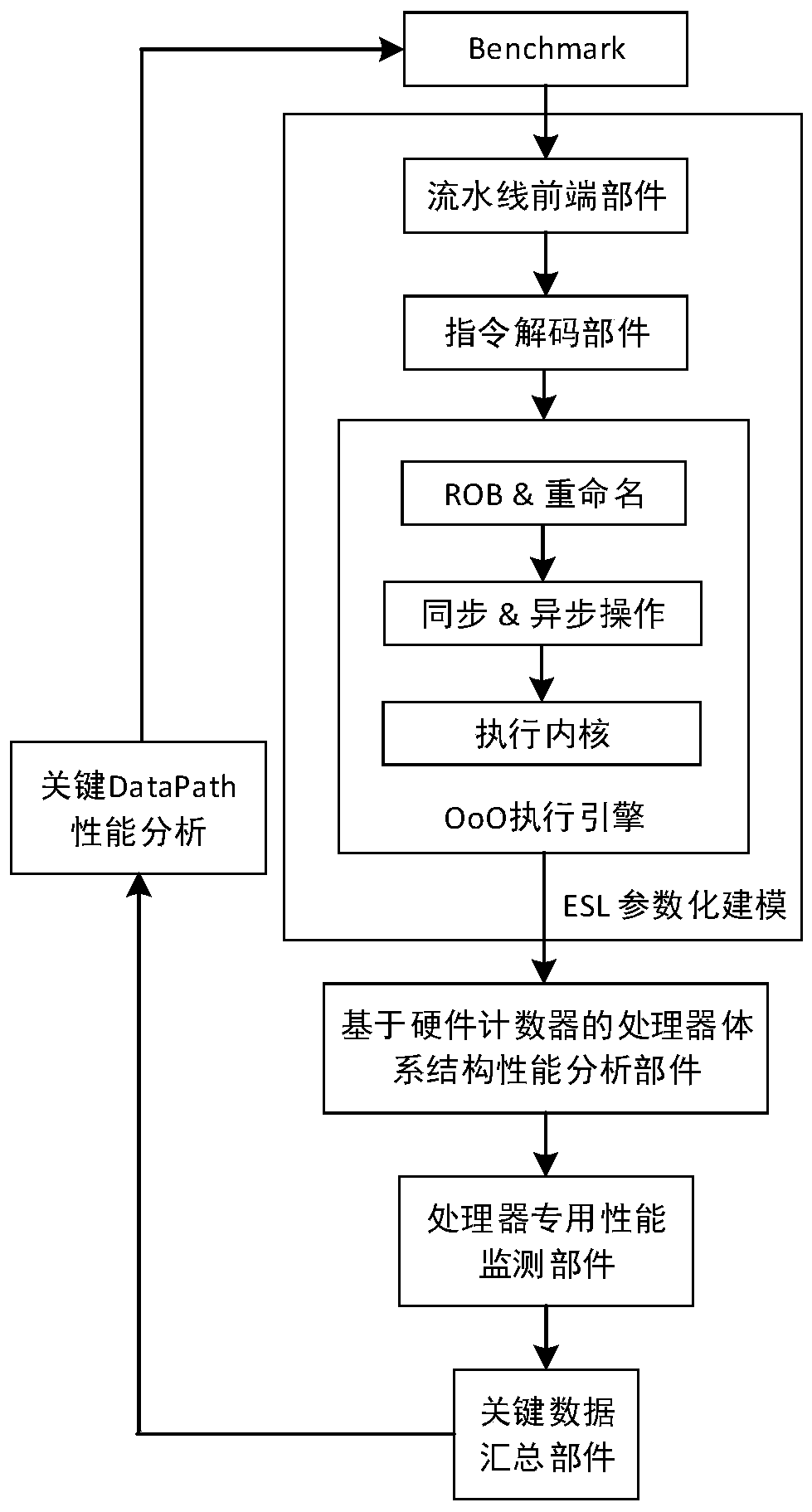

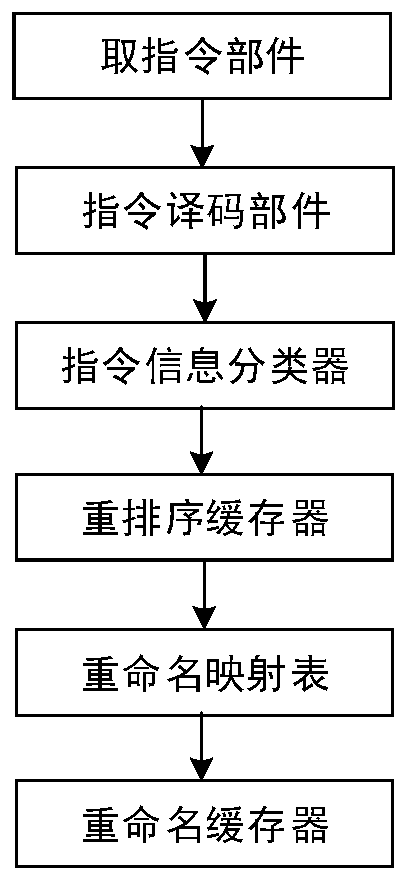

Register renaming method and system for out-of-order high-performance processor

InactiveCN111221575AImprove performanceRealize early retirement mechanismRegister arrangementsConcurrent instruction executionProcessor modelComputer architecture

The invention discloses a register renaming method and a system for an out-of-order high-performance processor. The method comprises the steps of constructing a parameterized processor model of an electronic system level ESL based on a high-level language, converting processor core components into an actual circuit through a hardware generator, and the core components comprise an instruction information classifier and a register renaming component for optimizing the structure of a reordering buffer; analyzing actual processor performance in real time and determining related parameters of the core component through a performance monitoring component composed of one or more hardware counters; and the performance monitoring component is used for counting performance data of the branch predictor component, the instruction information classifier, the reordering buffer, the renaming buffer and the instruction distribution component of the processor. In addition, based on the optimized register renaming structure, a fine-granularity instruction in-advance retirement mechanism is realized, and the performance of the processor can be further improved.

Owner:核芯互联科技(青岛)有限公司

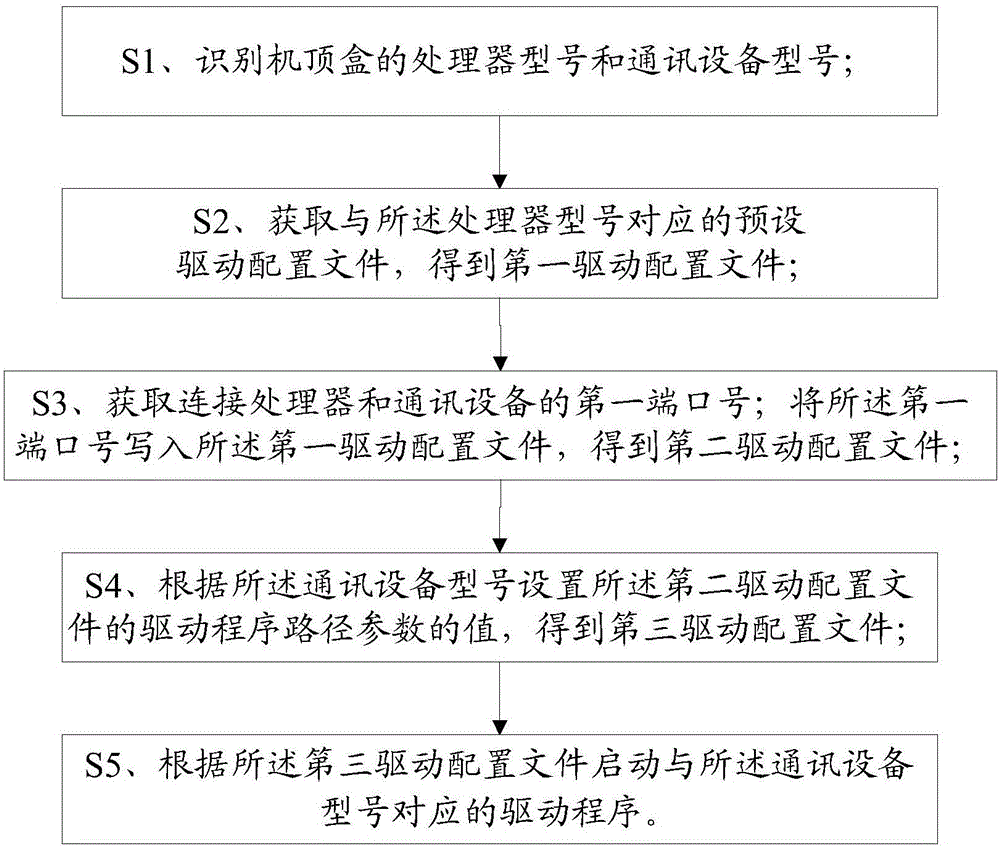

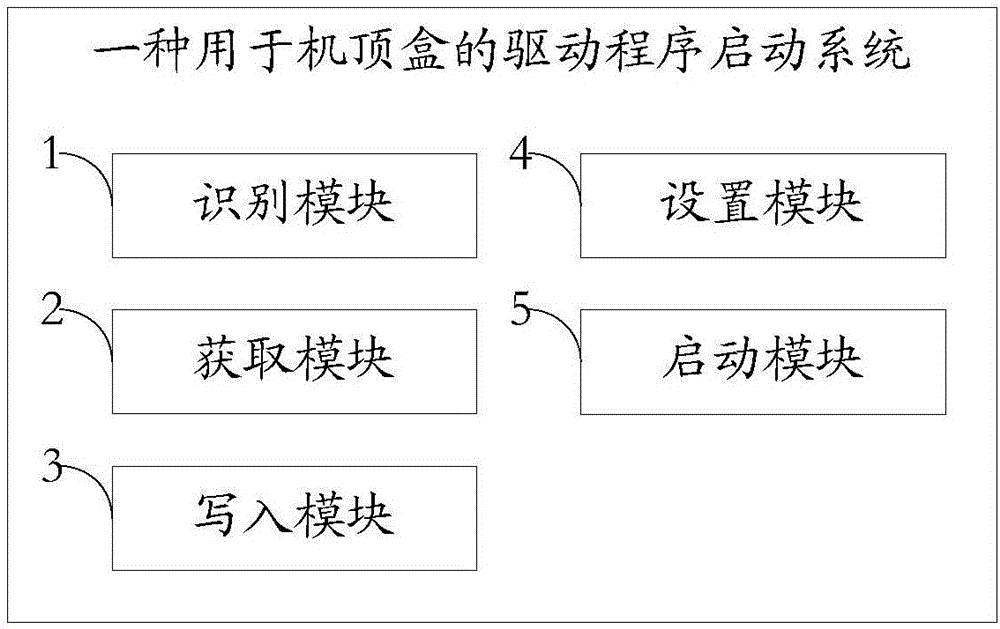

Drive program starting method and drive program starting system for set top box

InactiveCN106775897AImprove efficiencyImprove convenienceProgram loading/initiatingProcessor modelModel Number

The invention relates to the field of set top boxes, in particular to a drive program starting method and a drive program starting system for a set top box. The method includes steps: S1, recognizing a processor model and a communication device model of the set top box; S2, acquiring a preset drive configuration file corresponding to the processor model to obtain a first drive configuration file; S3, acquiring a number of a first port for connection of a processor and a communication device, and writing the number of the first port into the first drive configuration file to obtain a second drive configuration file; S4, setting values of drive program path parameters of the second drive configuration file according to the communication device model to obtain a third drive configuration file; S5, starting a drive program corresponding to the communication device model according to the third drive configuration file. The universal method for automatically loading drive programs of different models of communication devices is provided for the set top boxes with different models of processers.

Owner:FUZHOU FUDA HISI MICROELECTRONICS

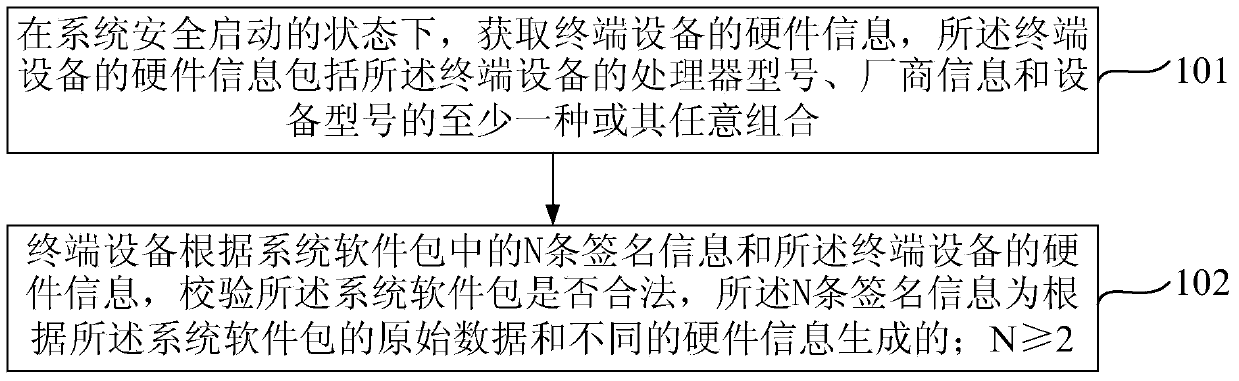

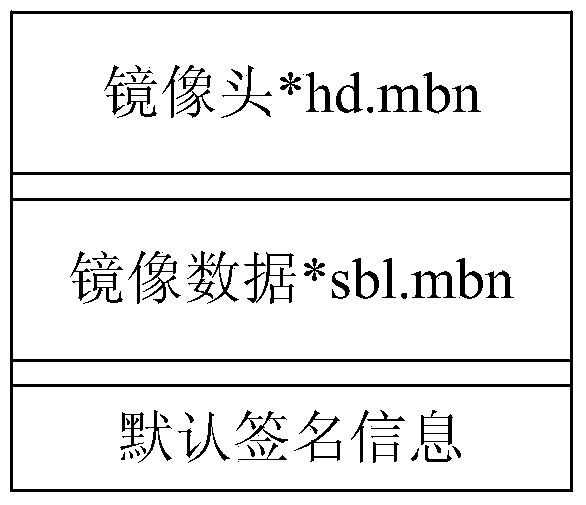

Signature calibration method and terminal device

ActiveCN103425932APerformance is not affectedNormal use is not affectedPlatform integrity maintainanceProcessor modelOriginal data

The invention discloses a signature calibration method and a terminal device. The signature calibration method includes the steps of obtaining hardware information of the terminal device in the state that a system is safely started, and conducting calibration to find out whether a system software package is legal or not through the terminal device according to N pieces of signature information in the system software package and the hardware information of the terminal device, wherein the hardware information of the terminal device includes at least one of the type of a processor of the terminal device, information of a manufacturer and the type of the device or any combination of the type of the processor of the terminal device, information of the manufacturer and the type of the device, the N pieces of signature information is generated according to original data of the system software package and different types of hardware information, and N is larger than or equal to 2. Due to the fact that the N pieces of signature information is generated according to the original data of the system software package and the different types of hardware information, the signature calibration method and the terminal device can adapt to safe starting of various types of hardware, and when the hardware information such as the type of the processor, the information of the manufacturer and the type of the device changes, normal use such as starting of the device, updating of the device and maintaining of the device can not be influenced.

Owner:HONOR DEVICE CO LTD

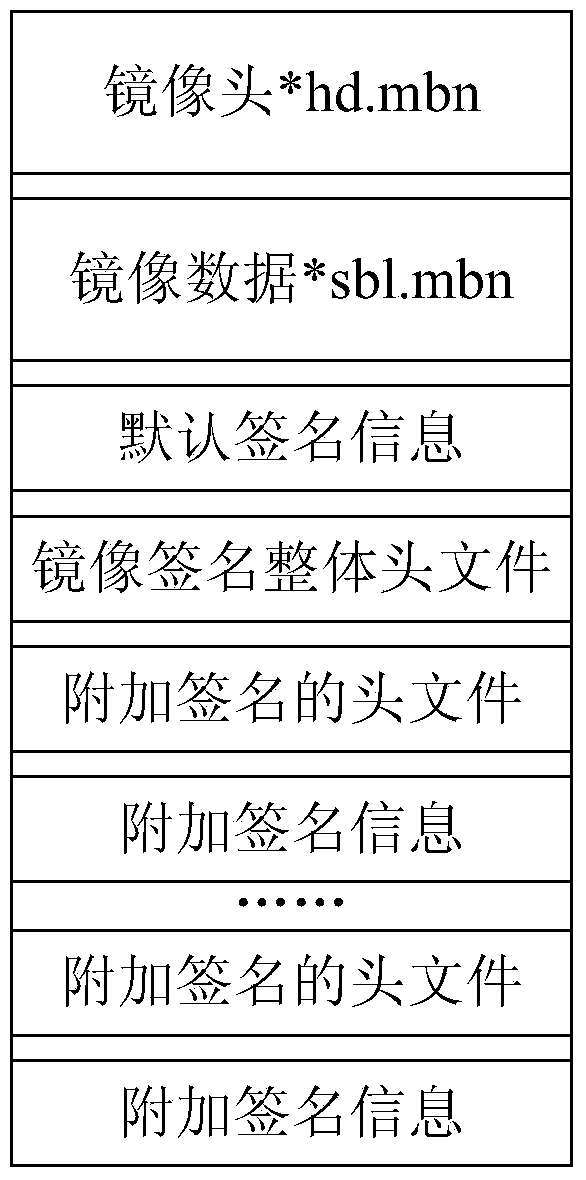

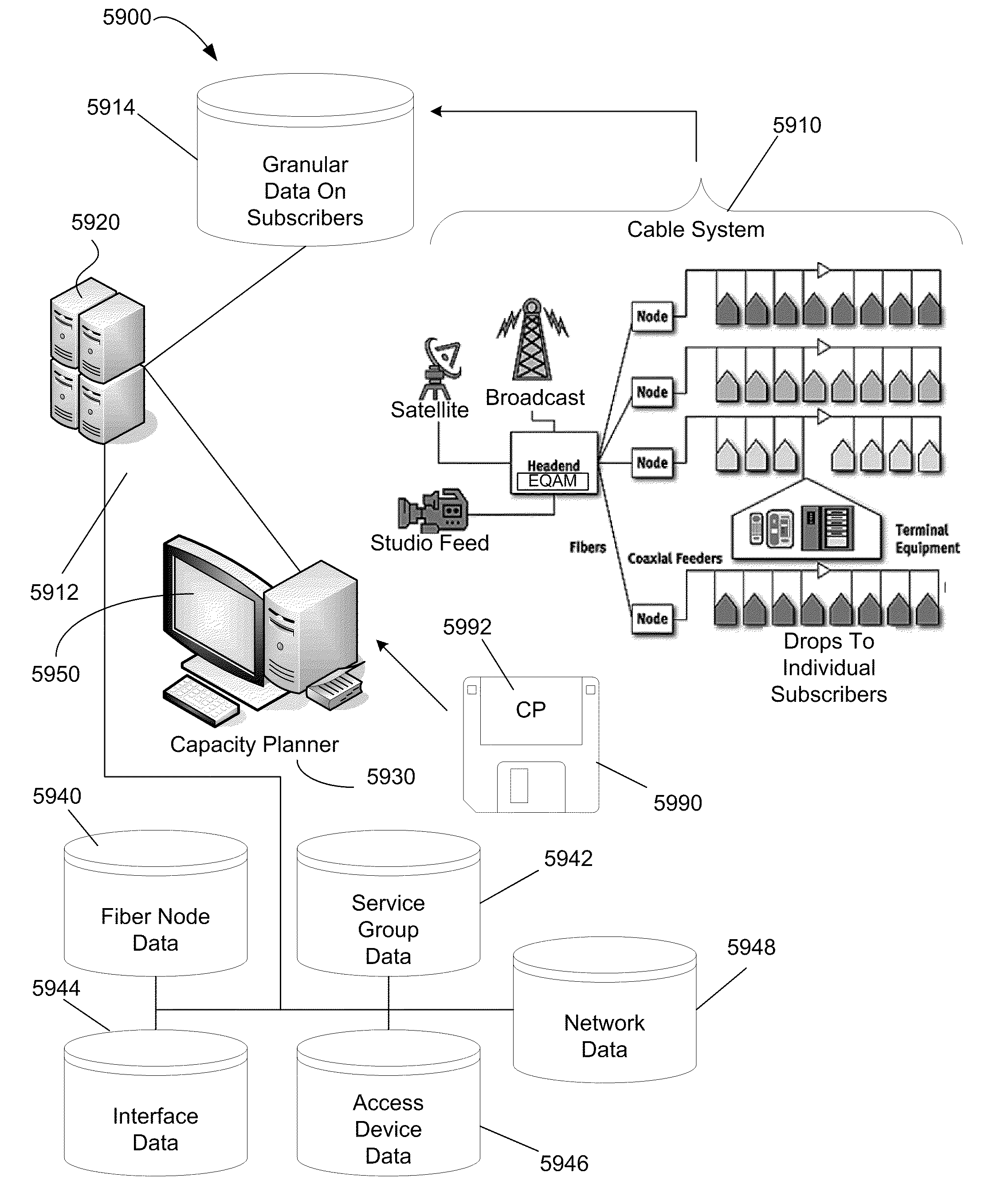

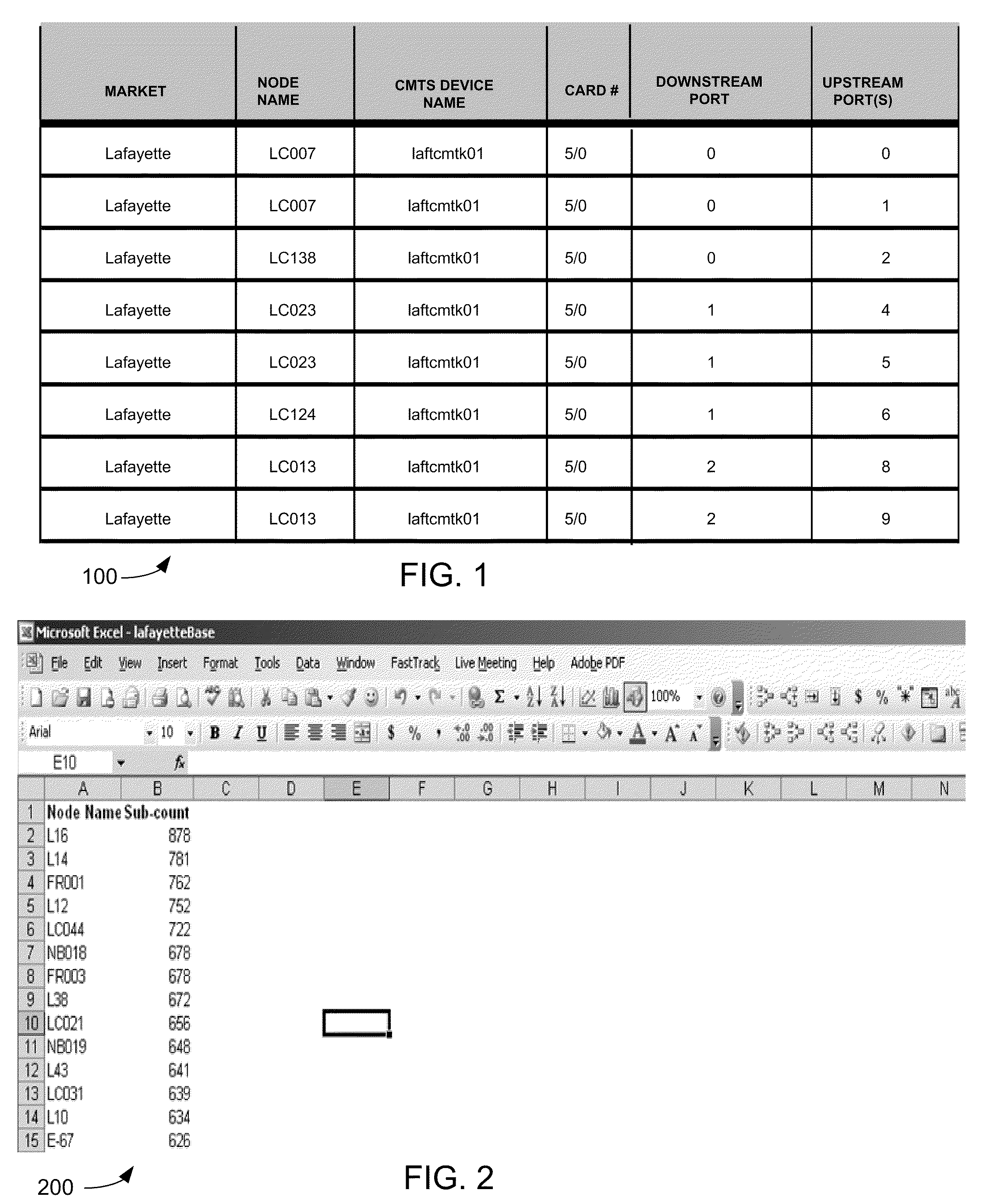

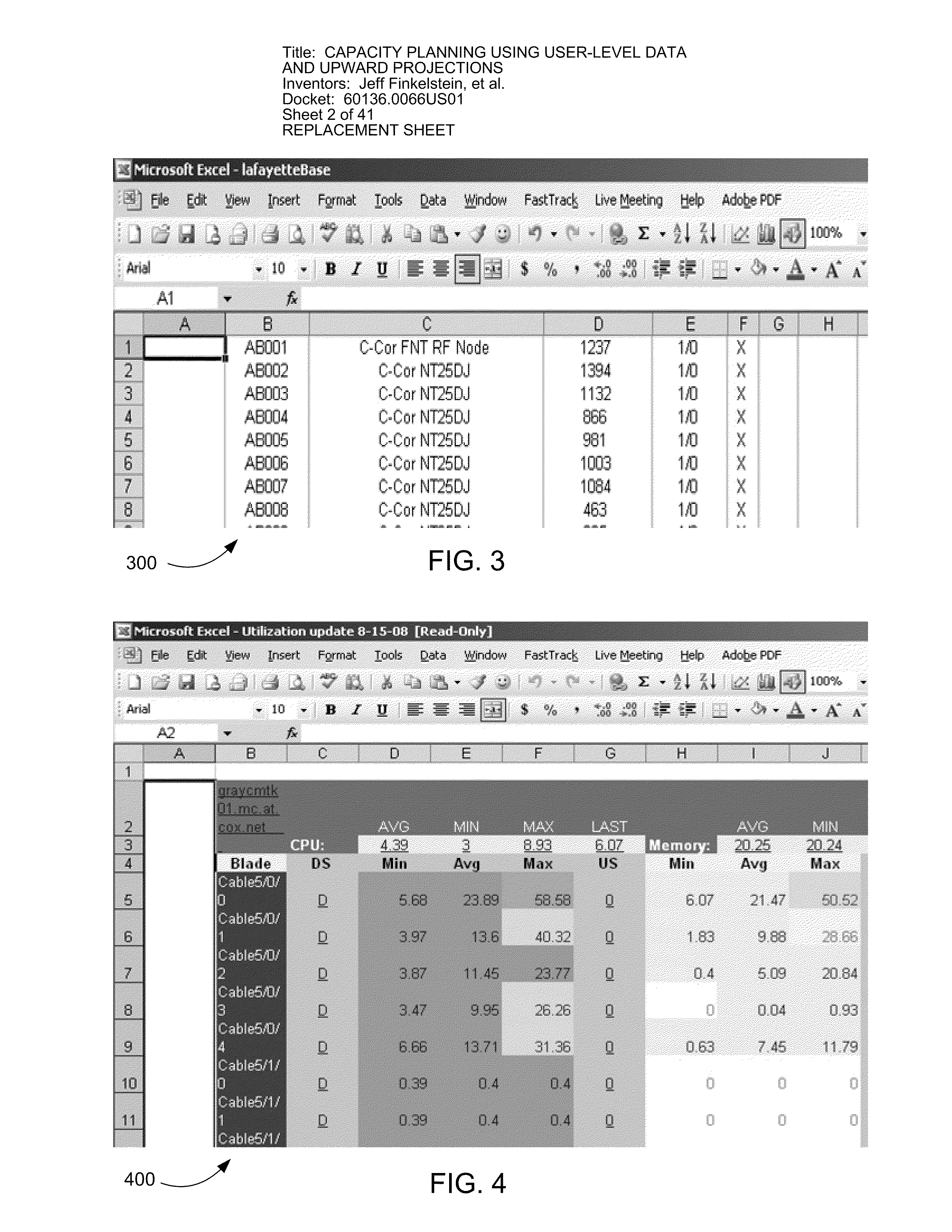

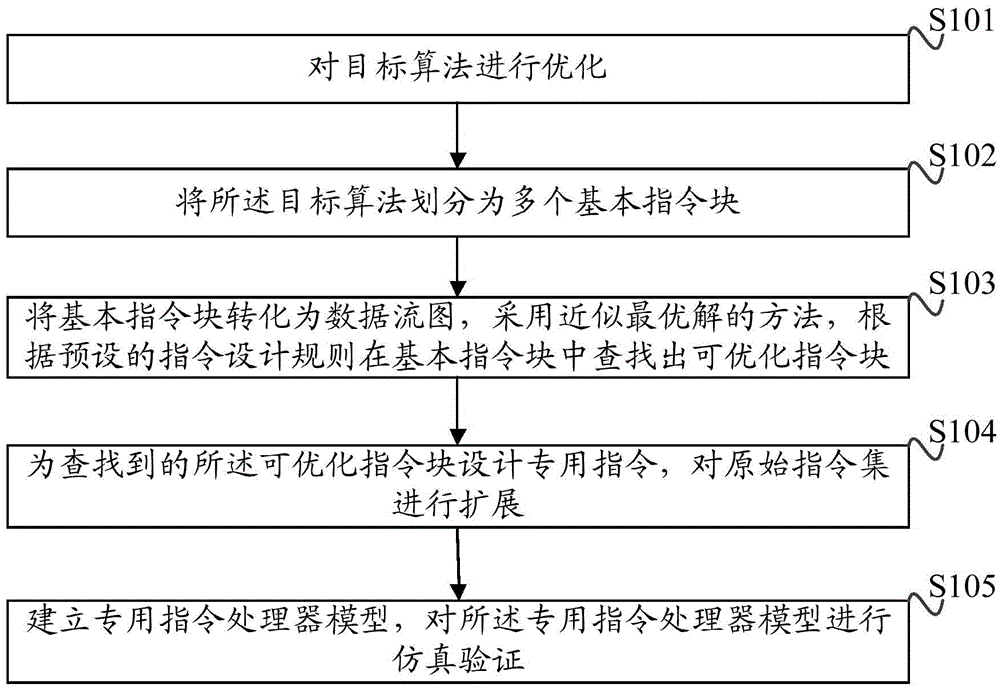

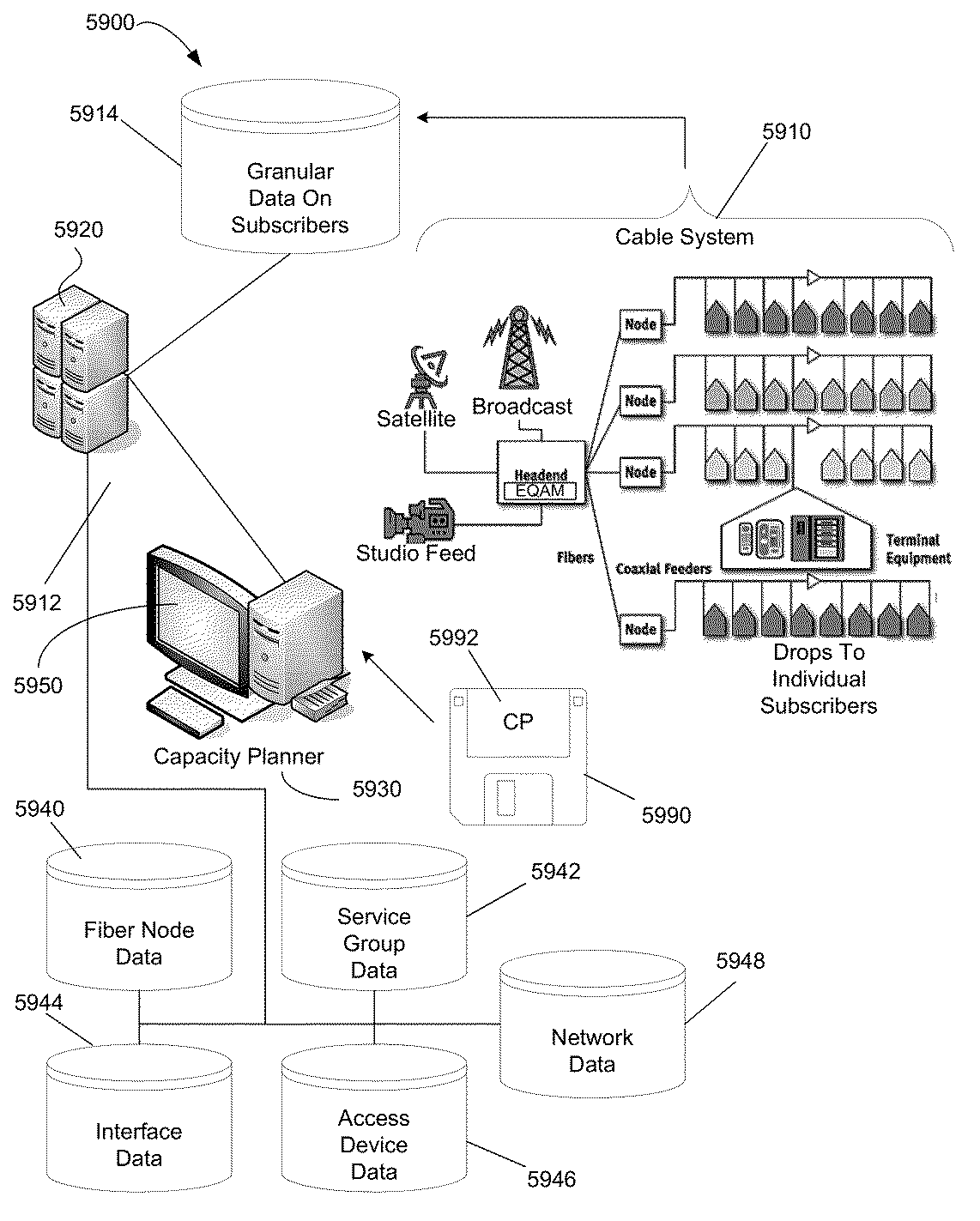

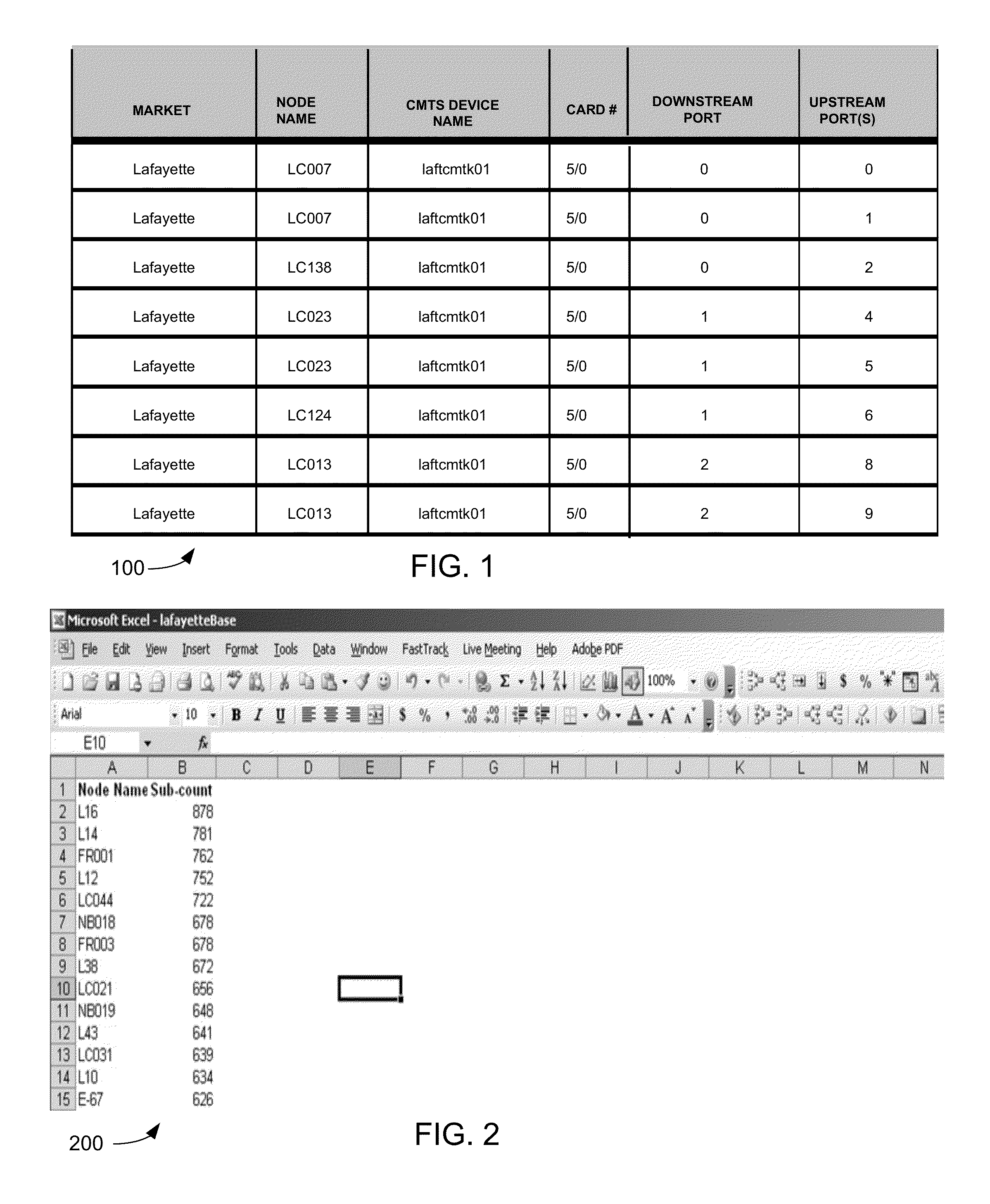

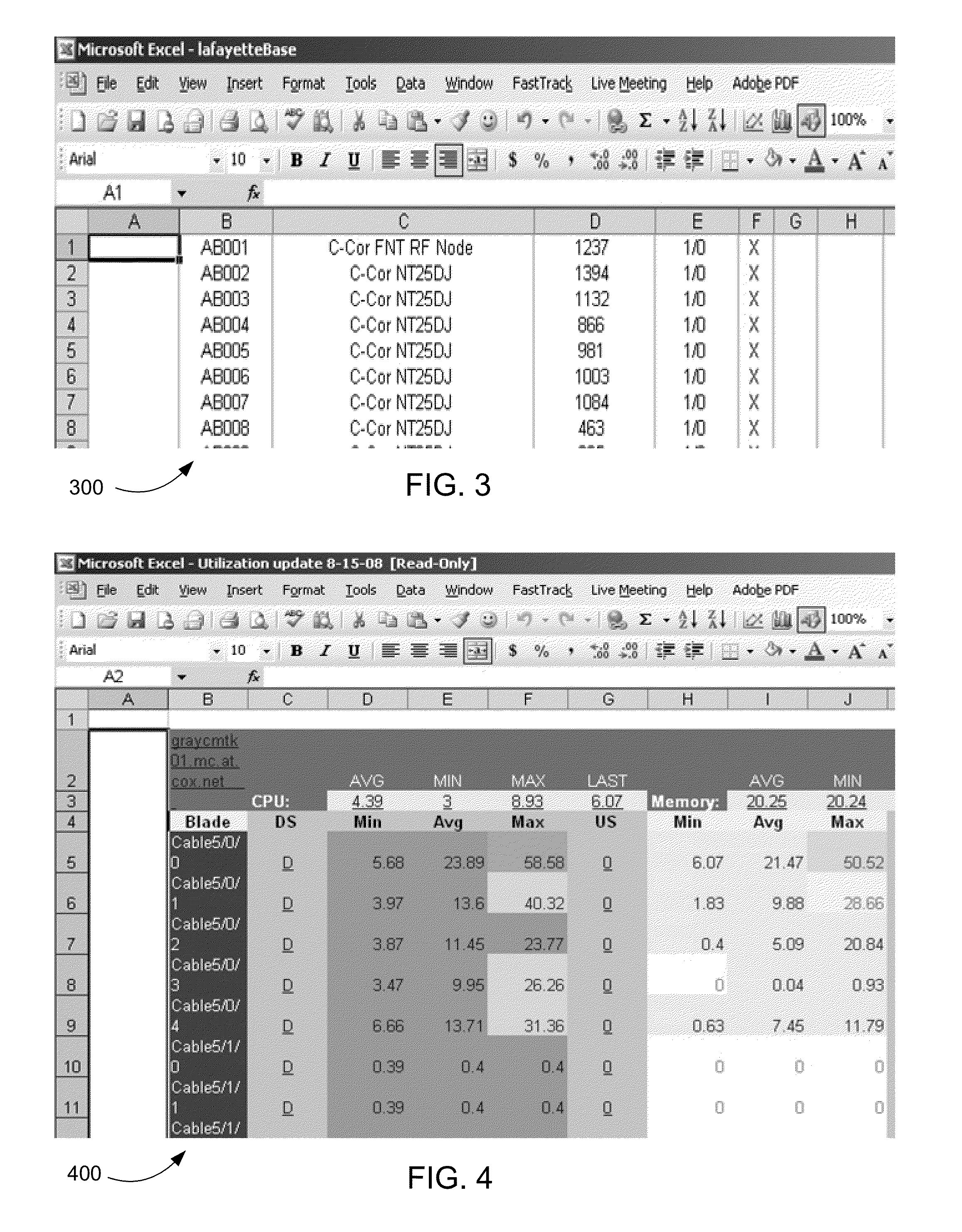

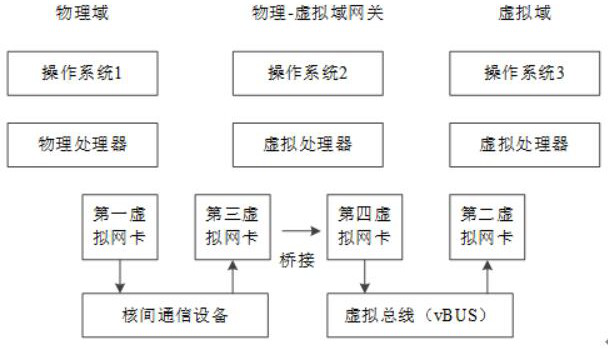

Capacity Planning Using User-Level Data and Upward Projections

ActiveUS20100290350A1Error preventionFrequency-division multiplex detailsProcessor modelTelecommunications network

A telecommunications network capacity planning system. The telecommunications network capacity planning system includes a telecommunications network including a telecommunications services provider, subscribers and a network coupling the telecommunications services provider and the subscribers for provisioning of the telecommunications services. A database system is used for collecting and storing data at the user-level associated with provisioning of telecommunication services over the telecommunications network. A processor is coupled to the database system. The processor models the telecommunications network by generating upward projections from the stored user-level data and transforms the modeling of the network to a visual display of capacity information and network parameters for manipulation to evaluate capacity planning scenarios.

Owner:COX COMMUNICATIONS

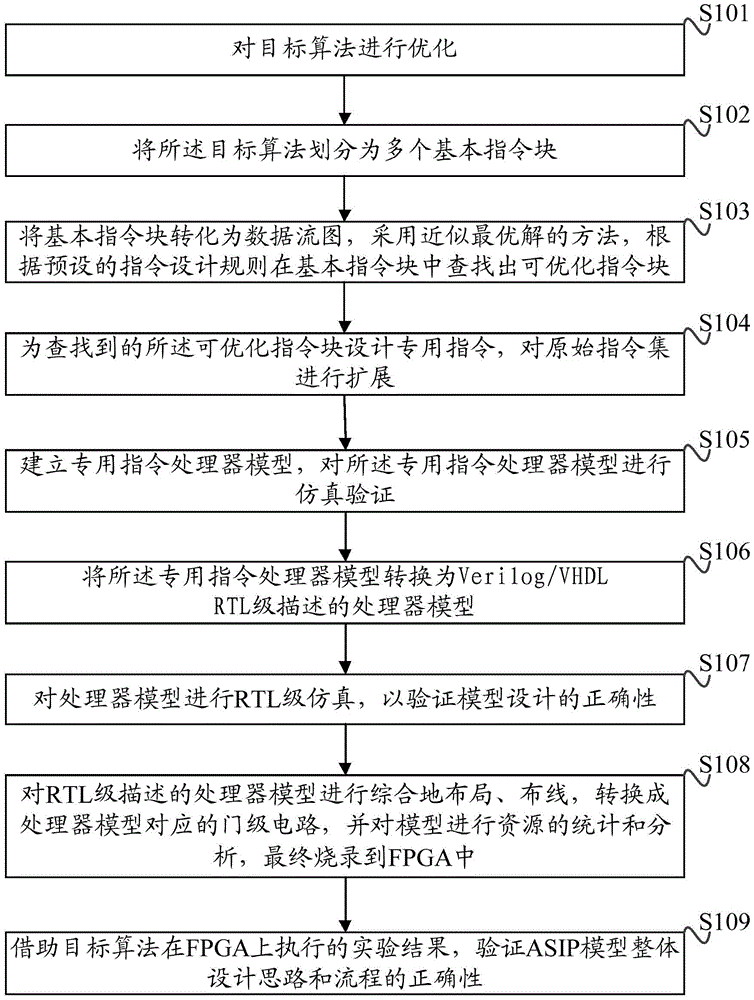

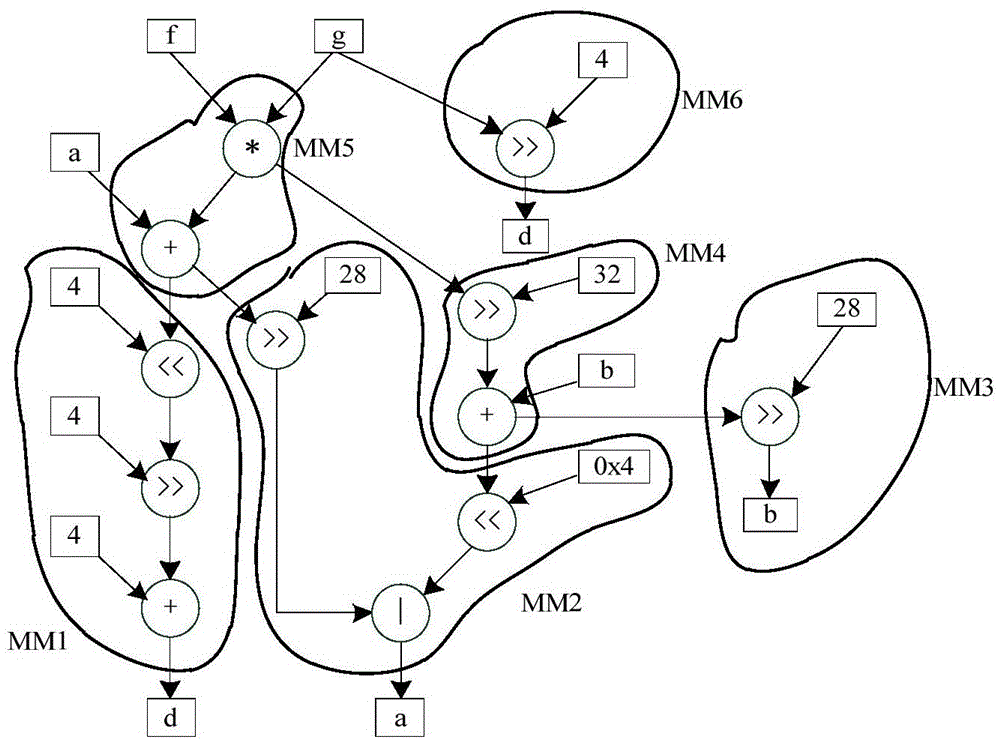

Design verification method of special instruction processor

InactiveCN105574269AImprove execution efficiencyFast operationCAD circuit designSpecial data processing applicationsProcessor modelRound complexity

The invention discloses a design verification method of a special instruction processor. The method comprises the following steps: optimizing a target algorithm; dividing the target algorithm into a plurality of basic instruction blocks; converting the basic instruction blocks into a data flow diagram, and searching optimizable instruction blocks from the basic instruction blocks according to a preset instruction design rule by adopting a method of approximate optimal solution; designing special instructions of the searched optimizable instruction blocks and extending an original instruction set; and establishing a special instruction processor model and carrying out simulation verification on the special instruction processor model. According to the design verification method of the special instruction processor, the operating speed of the target algorithm for executing the modules with relatively high complexity in the realization process is improved through an instruction set extension method, so that the execution efficiency of the algorithm is improved.

Owner:QINGDAO UNIV

Device and method for denoising ocean bottom data

ActiveUS20130163378A1Seismic signal processingSeismology for water-covered areasProcessor modelOcean bottom

Computing device, computer instructions and method for denoising marine seismic data recorded with first and second seismic sensors. The method includes receiving first seismic data recorded with the first sensor in a time-space domain; receiving second seismic data recorded with the second sensor in the time-space domain, wherein the first and second seismic data are recorded at the same locations underwater; calculating with a processor models of the first and second seismic data in a transform domain that is different from the time-space domain; performing a wavefield separation using the first and second datasets in the transform domain; determining a noise in the transform domain corresponding to the second seismic data based on the wavefield separation; reverse transforming the noise from the transform domain into the time-space domain; and denoising the second seismic data by subtracting the noise in the time-space domain from the second seismic data.

Owner:CGGVERITAS SERVICES

Capacity planning using user-level data and upward projections

A telecommunications network capacity planning system. The telecommunications network capacity planning system includes a telecommunications network including a telecommunications services provider, subscribers and a network coupling the telecommunications services provider and the subscribers for provisioning of the telecommunications services. A database system is used for collecting and storing data at the user-level associated with provisioning of telecommunication services over the telecommunications network. A processor is coupled to the database system. The processor models the telecommunications network by generating upward projections from the stored user-level data and transforms the modeling of the network to a visual display of capacity information and network parameters for manipulation to evaluate capacity planning scenarios.

Owner:COX COMMUNICATIONS

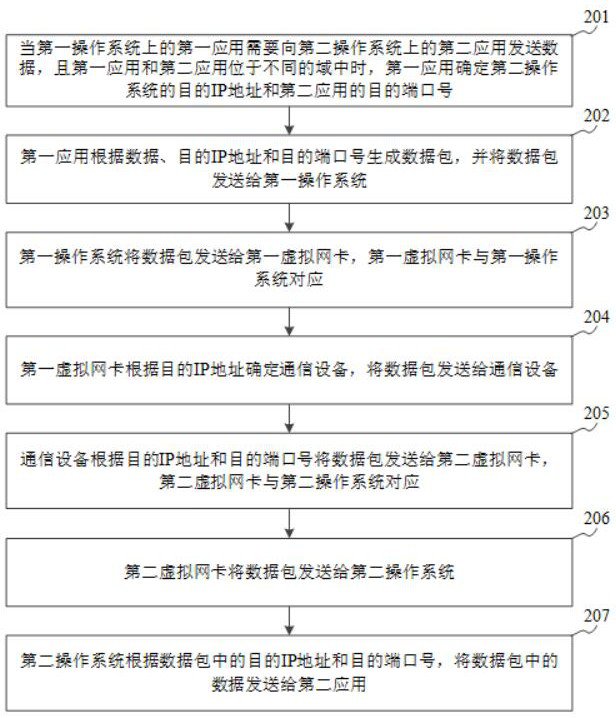

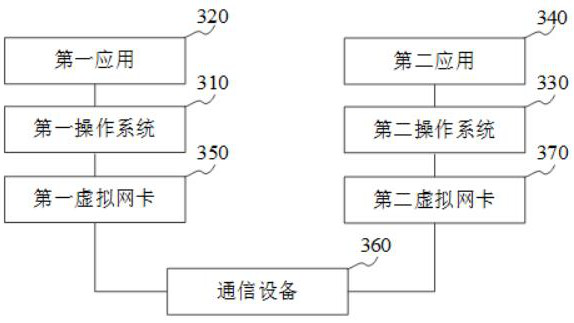

Hybrid heterogeneous virtualization communication method and chip

ActiveCN112433826ARealize communicationImprove cohesionSoftware simulation/interpretation/emulationProcessor modelVirtualization

The invention discloses a hybrid heterogeneous virtualization communication method and a chip, and belongs to the technical field of embedded chips on chips. The method comprises the following steps:allocating a virtual network card to each operating system existing in a chip, and setting a corresponding IP address, so that an application program can achieve cross-operating-system interconnectionand intercommunication in a unified manner (socket) through a routing process of virtual and real gateways. Due to the fact that the application programs can be interconnected and intercommunicated between the physical cores and can also be interconnected and intercommunicated between the physical cores and the virtual machine, the chip is changed into an on-chip distributed system based on network communication logically from an original heterogeneous multi-core processor model. In addition, the method disclosed by the invention can be conveniently expanded to a system-on-chip with more physical cores and virtual machines.

Owner:NANJING SEMIDRIVE TECH CO LTD

Information processing apparatus and method, program storage medium, and program

InactiveUS20060015216A1Promote generationReduce necessitySpecial data processing applicationsManipulatorProcessor modelInformation processing

An input motion acquiring unit acquires a motion trajectory of an object from an image recognizing unit. A dynamic modeling processor models a plurality of robot motion patterns stored in a robot motion pattern storage unit in a dynamic system form, and stores the modeled robot motion patterns into a robot-motion-pattern-model storage unit. A motion converting unit linearly transforms the plurality of robot motion dynamic models stored in the robot-motion-pattern-model storage unit into prediction motion trajectories. A motion comparing unit compares the input motion trajectory acquired by the motion acquiring unit with the prediction motion trajectories transformed by the motion converting unit. A robot motion selecting unit selects a robot motion pattern having the highest similarity from the robot motion pattern storage unit. The present invention is applicable to a robot apparatus.

Owner:SONY GRP CORP

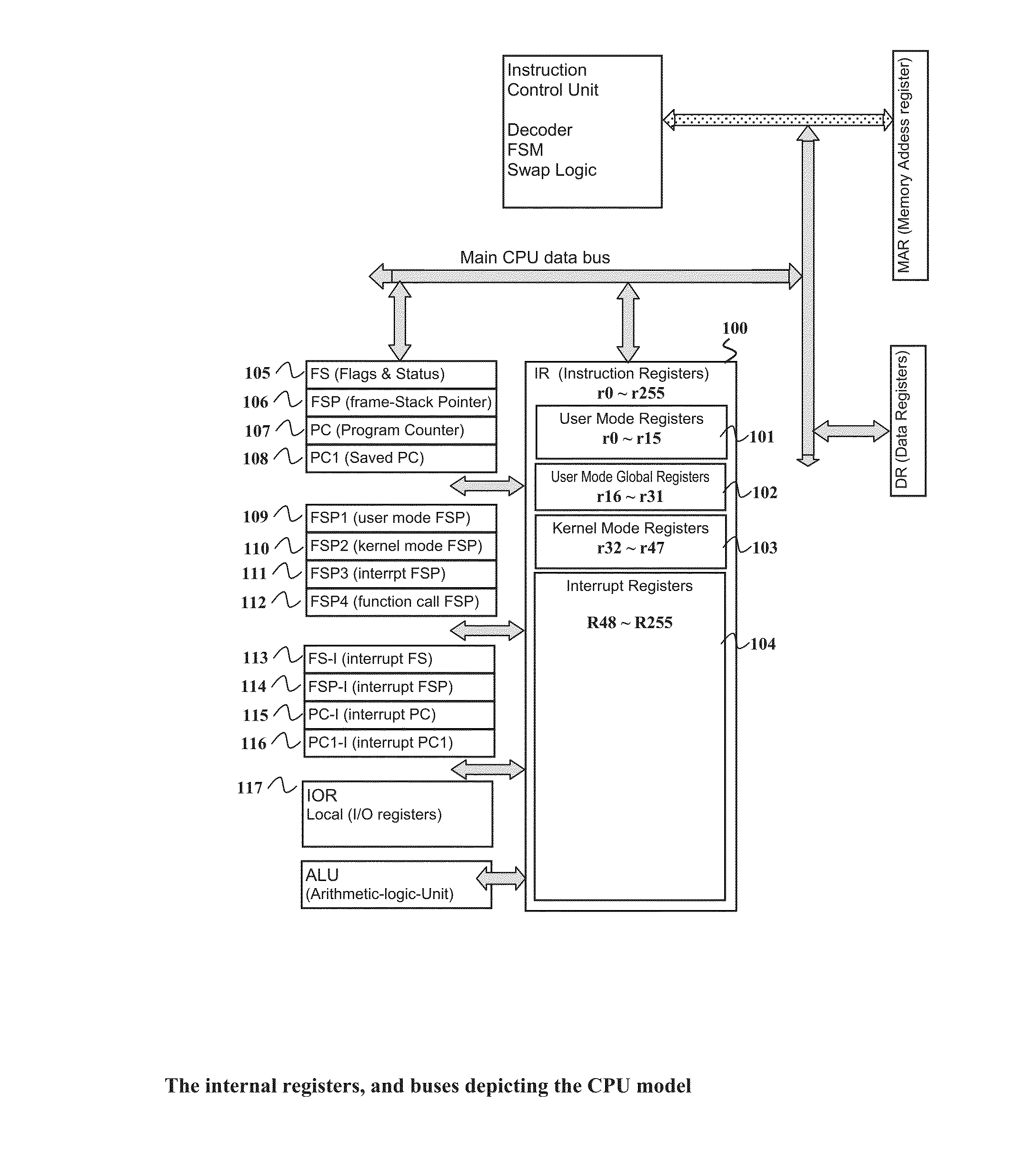

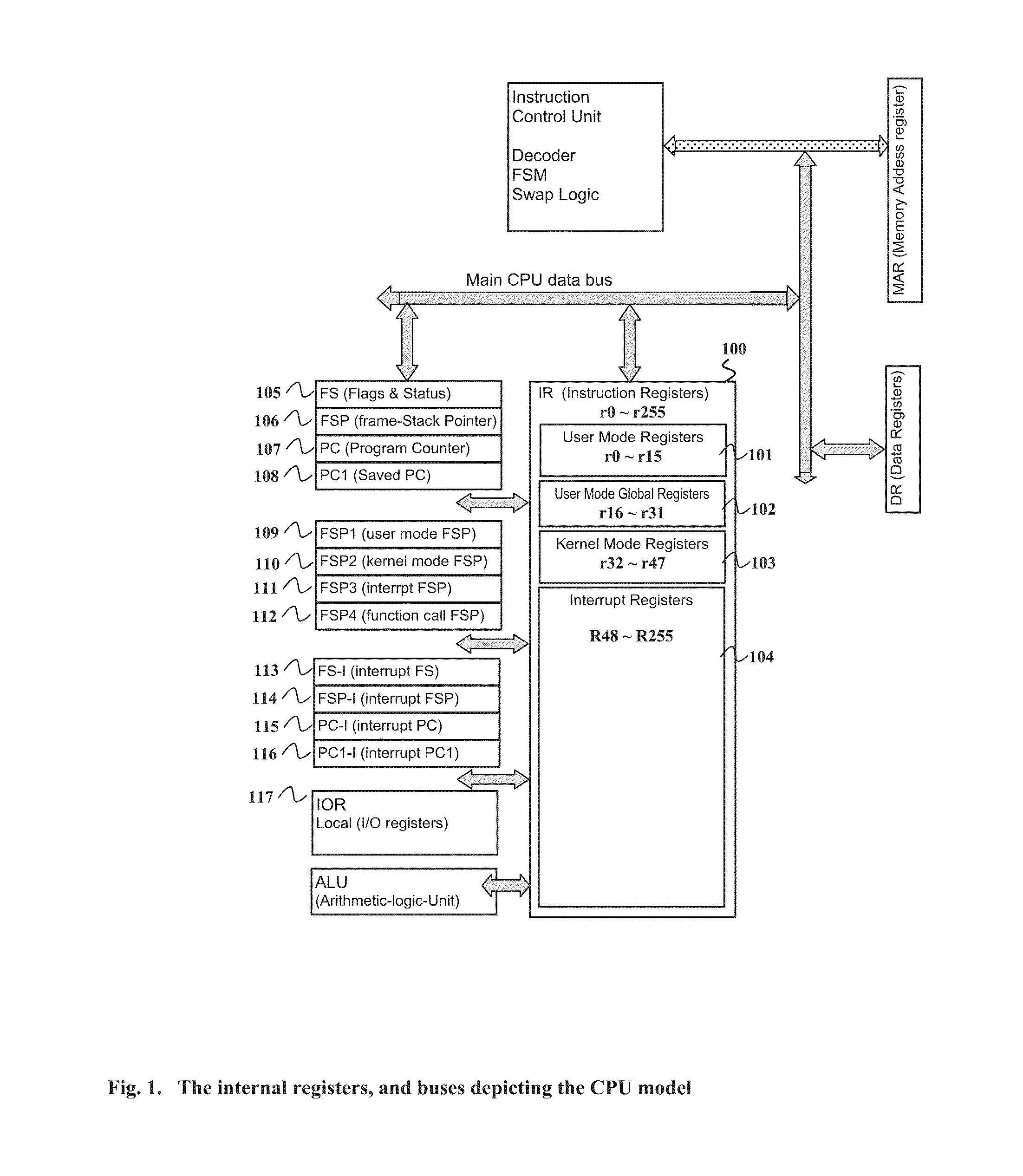

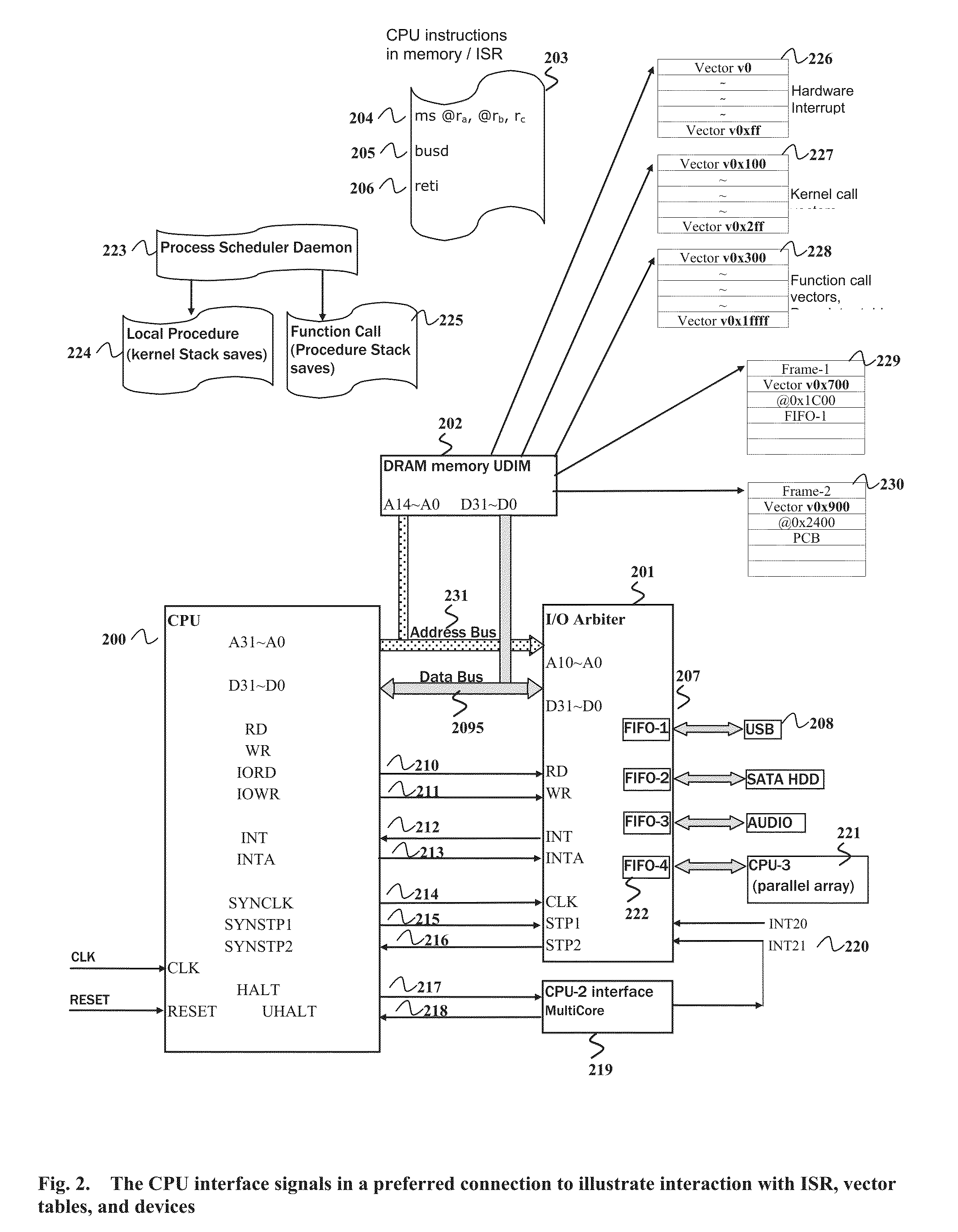

Processor model using a single large linear registers, with new interfacing signals supporting fifo-base I/O ports, and interrupt-driven burst transfers eliminating dma, bridges, and external I/O bus

InactiveUS20160224485A1Simple and powerful CPU architectureEfficient mappingElectric digital data processingProcessor modelSystems design

A processor or CPU architecture that implements many enabling technologies proven to enhance data through put supporting the synchronous burst data transfer. The Input-Output (I / O) is uniformly viewed and treated as an individual First-In-First-Out (FIFO) device. Pluralities of memory areas are implemented for user stack, kernel stack, interrupt stack and procedure call stack. Only one I / O arbiter is necessary for a CPU model that arbitrates between a plurality of FIFOs substituting data caches for on-chip implementation, thus eliminating traditional data transfer techniques using Direct-Memory-Access (DMA), bus control and lock signals leaving just the interrupt signals and the new synchronous signals for an easy and streamlined system design and CPU model. Supporting an interrupt-driven, FIFO-based I / O and synchronous burst data transfer the CPU employs a simple linear large register sets without bank switching.

Owner:UNIVERSITI TEKNOLOGI MALAYSIA +1

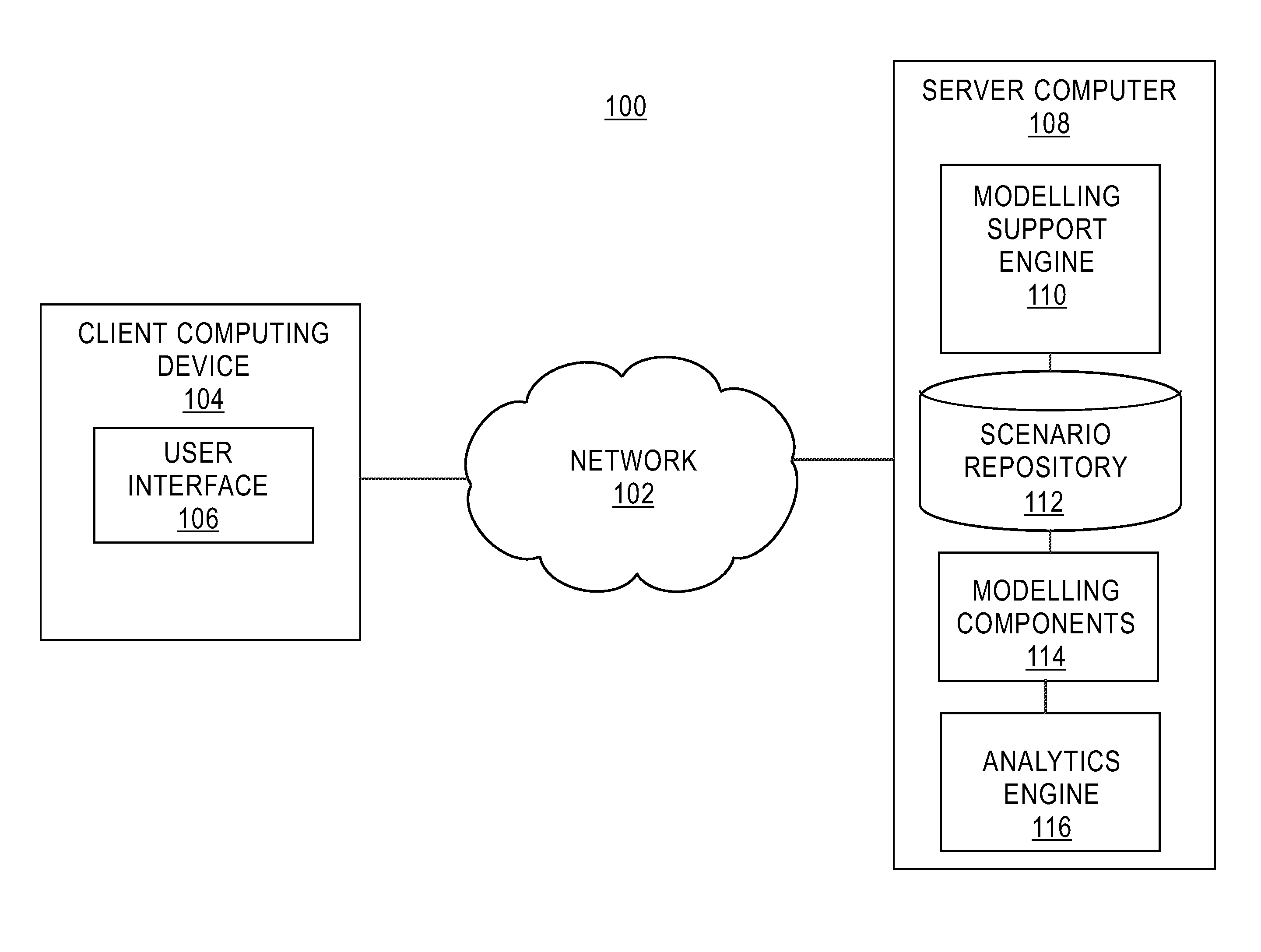

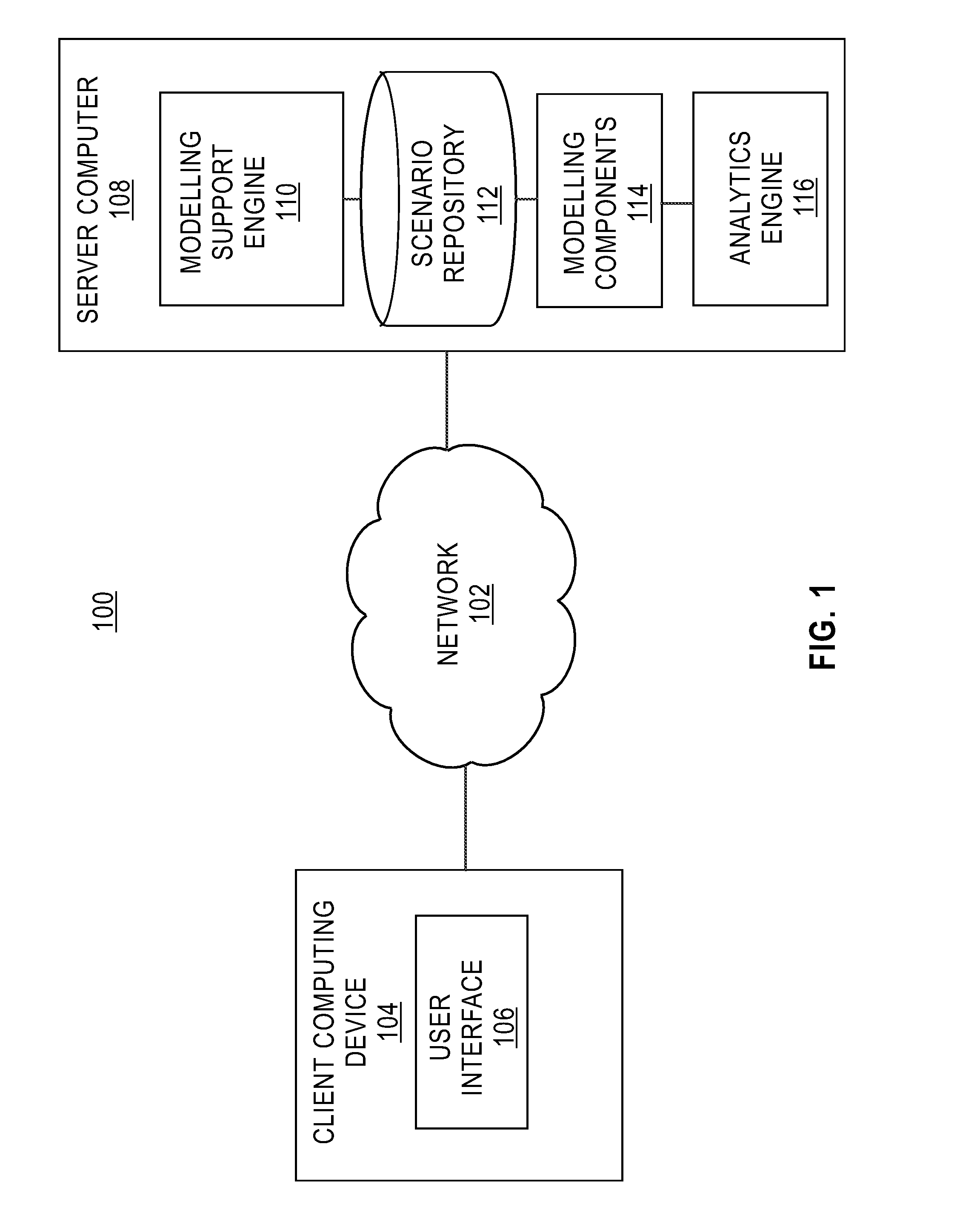

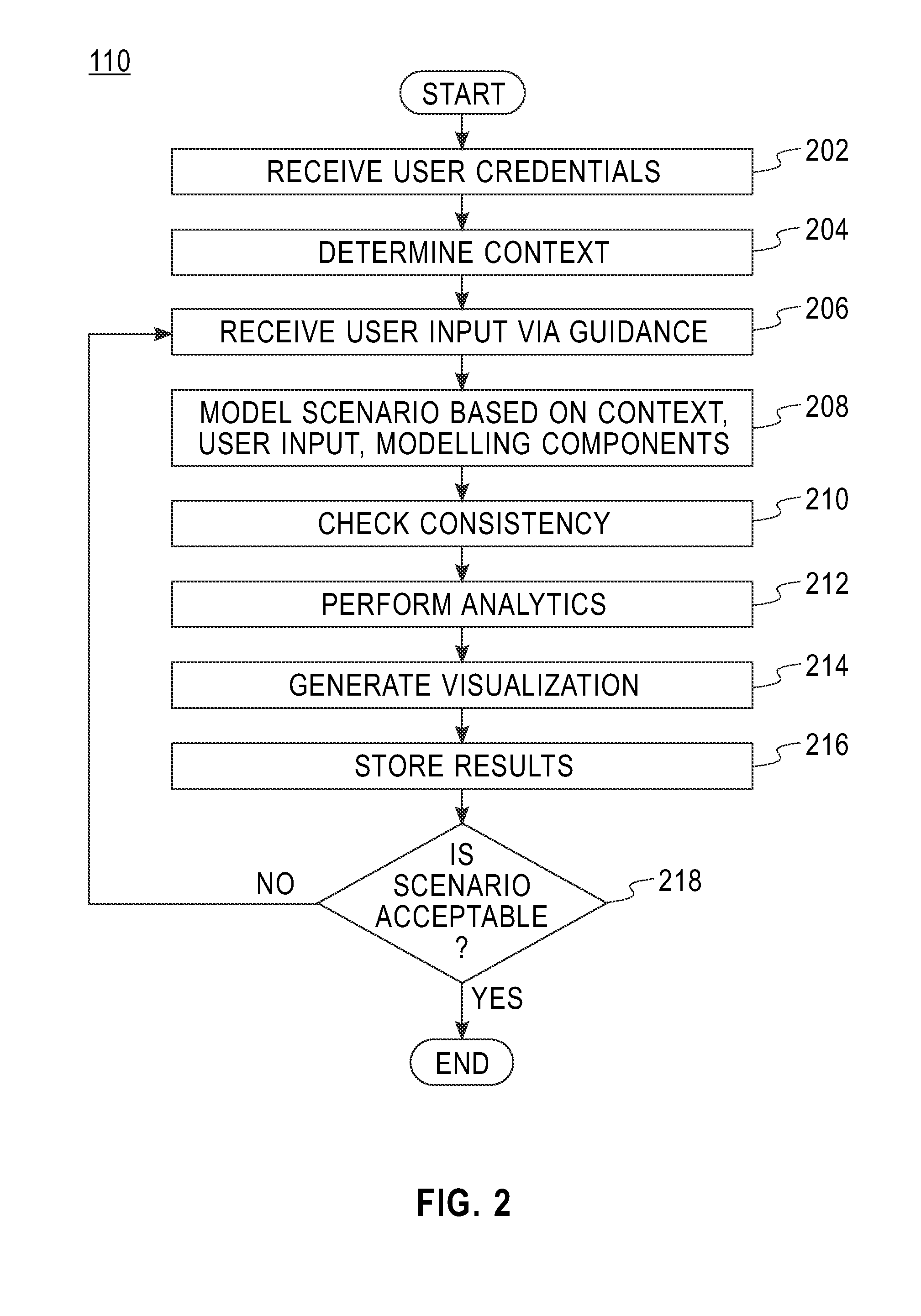

Modelling and planning population movement scenarios

InactiveUS20150379170A1Office automationSpecial data processing applicationsProcessor modelComputer science

In an approach to modelling population movement scenarios, one or more computer processors receive at least one credential of a user. The one or more computer processors determine, based, at least in part, on the received at least one credential, at least one context of a first population movement scenario, wherein the at least one context provides scenario-specific information for the first population movement scenario. The one or more computer processors receive a plurality of parameters associated with the first population movement scenario. The one or more computer processors model, based, at least in part, on the determined at least one context and the received plurality of parameters, the first population movement scenario. The one or more computer processors generate at least one visualization of the first population movement scenario model.

Owner:IBM CORP

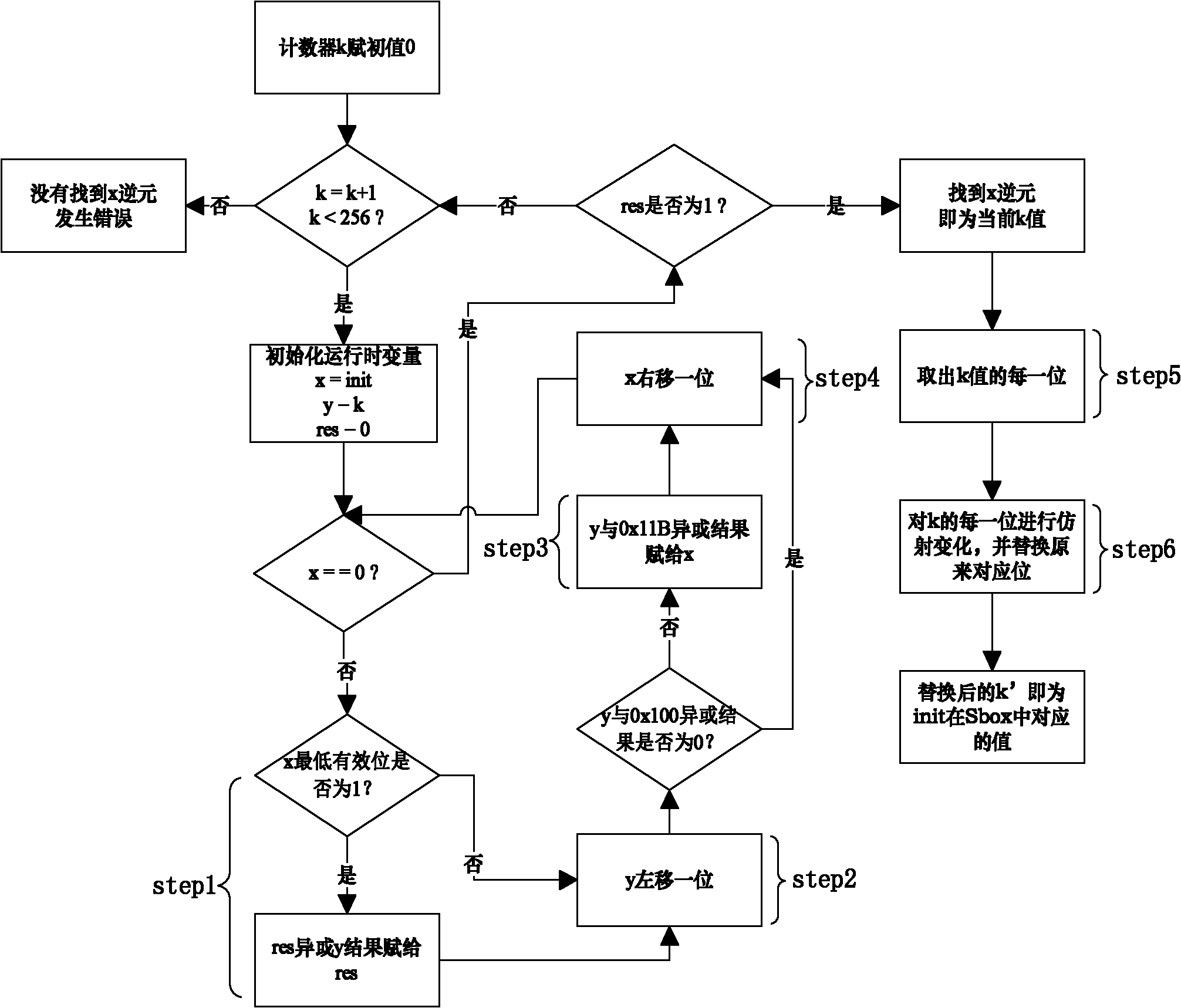

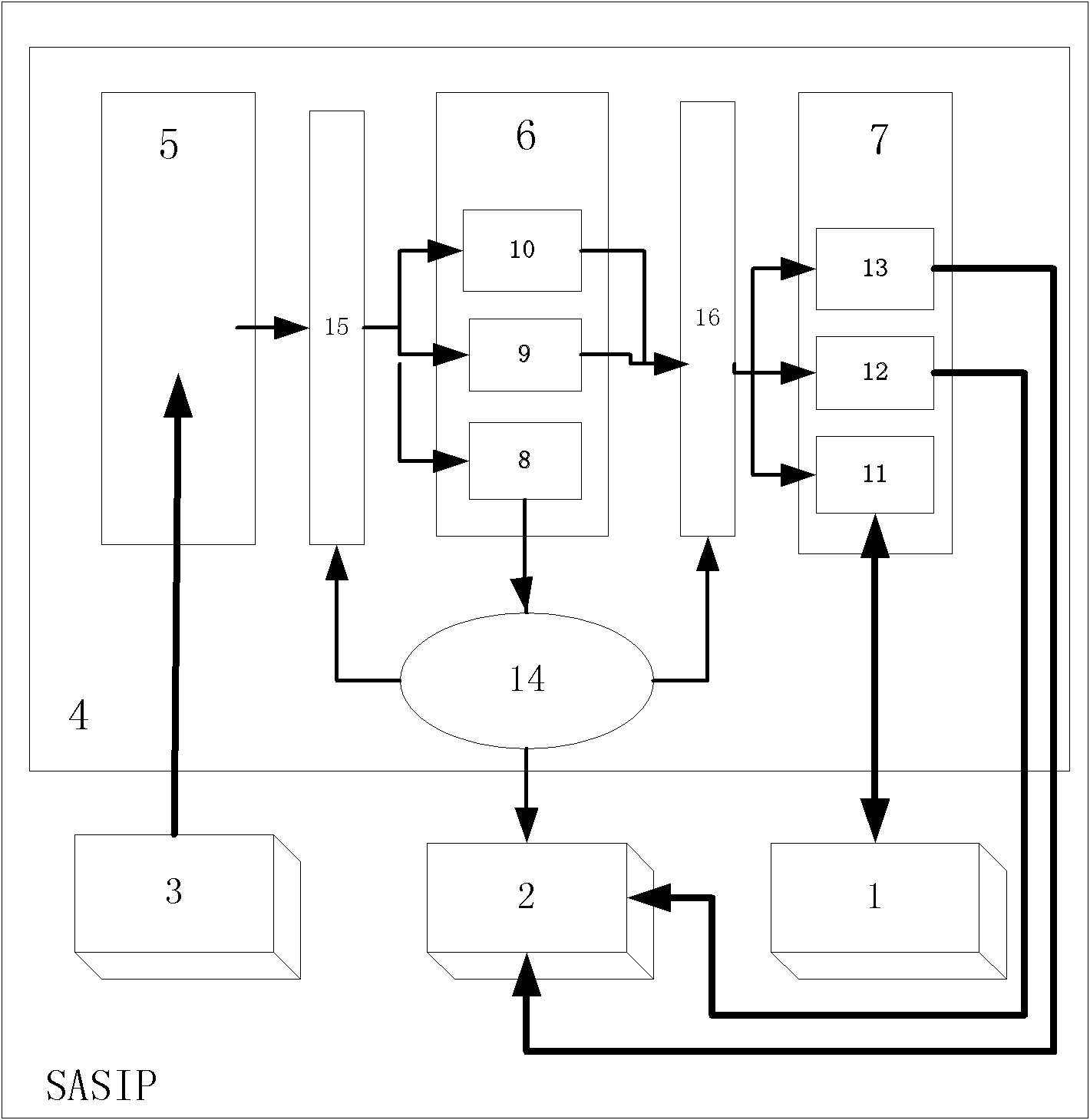

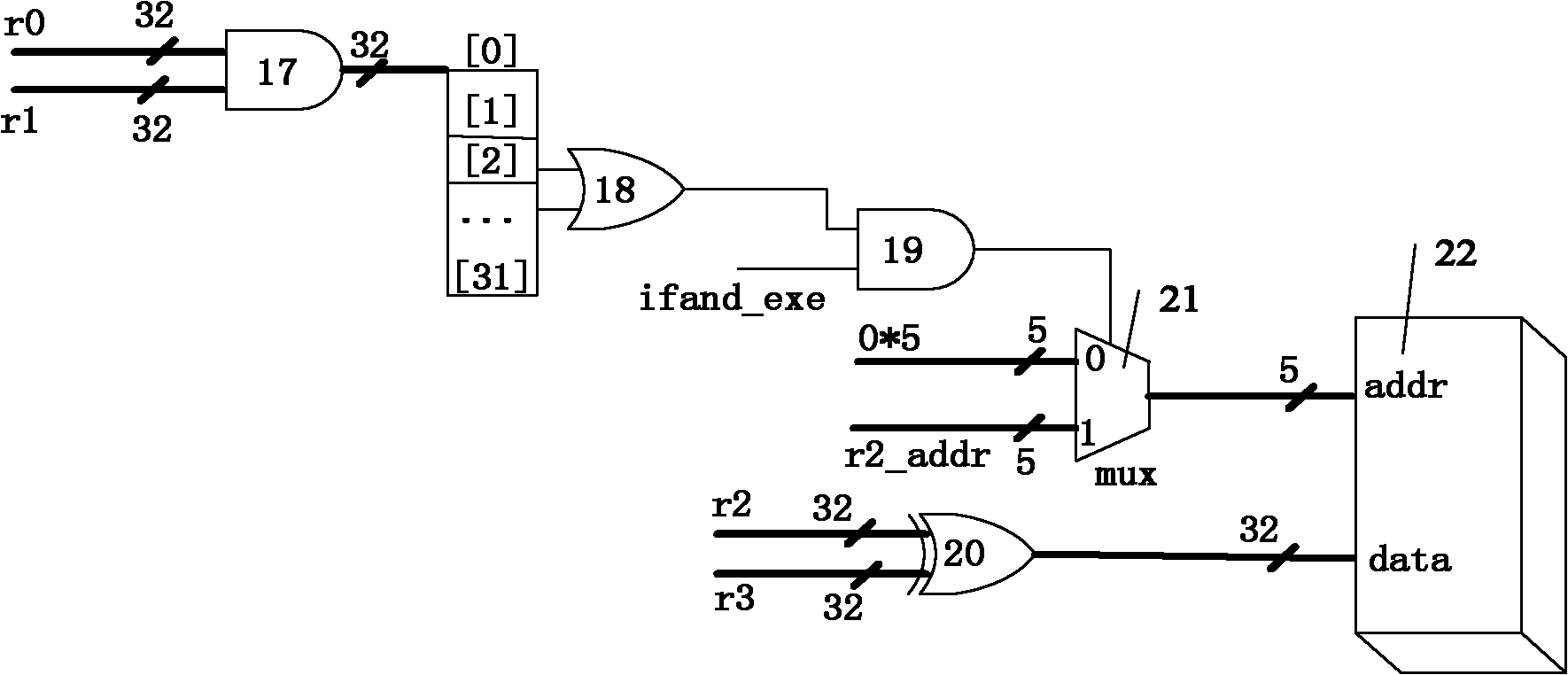

Sbox generation instruction optimization method in AES (Advanced Encryption Standard) encryption algorithm and instruction set processor thereof

InactiveCN102081514ASpeed up the build processReduce resource consumptionConcurrent instruction executionMemory systemsProcessor modelGeneration process

The invention relates to an instruction optimization method for an Sbox generation process in an AES (Advanced Encryption Standard) encryption algorithm and a design of an instruction set processor model thereof. In order to accelerate the Sbox generation process in the AES algorithm, the invention designs three new extended instructions: (1) ifand(src1),(src2),(xor_src1),(xor_src2), for accelerating in-domain multiplication operation in the Sbox generation process; (2) getbit(dest)=(src),(bitpos), for accelerating bit-getting operation in the affine transformation process; and (3) xor5(dest)=(src1),(src2),(src3),(src4),(src5), for accelerating quinary exclusive-or operation in the affine transformation process. The three instructions are completed within one clock cycle; but in the traditional ARM (Advanced RISC Machines) processor, the three instructions respectively need multiple clock cycles. Thus, the new instructions achieve the accelerating effect. The invention also designs a special instruction processor model (SASIP) corresponding to the new instruction set according to the new extended instructions. The processor model realizes the extended instructions on hardware logic, thereby being a processor model specializing in AES-Sbox acceleration.

Owner:SHANDONG UNIV