Sbox generation instruction optimization method in AES (Advanced Encryption Standard) encryption algorithm and instruction set processor thereof

An instruction optimization and encryption algorithm technology, applied in concurrent instruction execution, electrical digital data processing, instruments, etc., can solve problems such as the improvement effect is not very obvious, the space for algorithm optimization is limited, and the scalability is weak.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

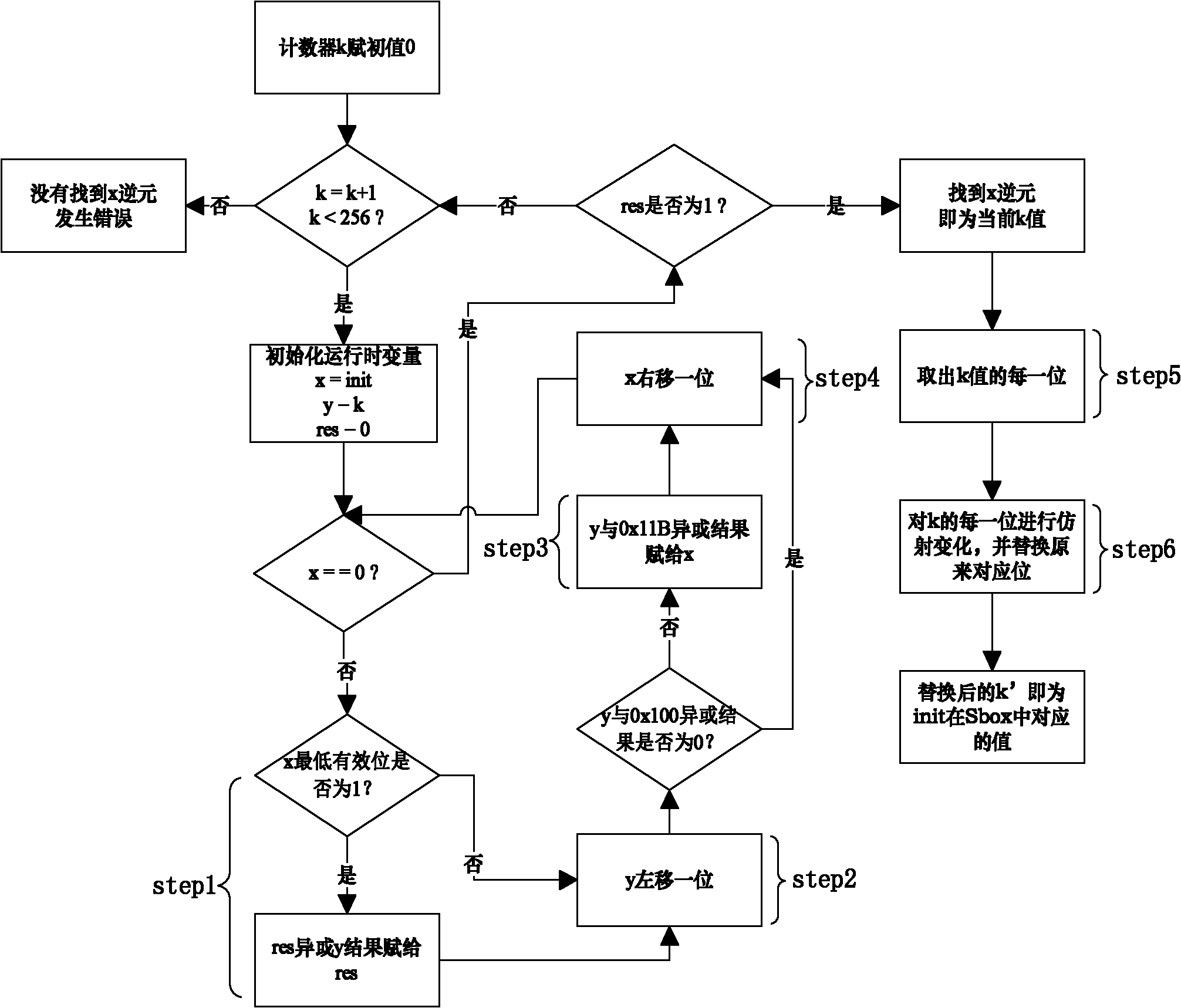

[0072] figure 1 It is a flowchart of the AES-Sbox generation algorithm, which mainly includes 6 execution steps. Under the premise of not changing the length of the instruction opcode, the number of instructions and not affecting the running speed of the processor, some steps of the Sbox generation process are accelerated. The specific process is as follows:

[0073] 1) In the process of Sbox generation, the inverse element needs to be solved, and the Galois field GF(2 8 ) within the multiplication operation. Analyzing the generation process of Sbox, it is found that in each cycle of multiplication in the domain, a post-judgment XOR process is required, which corresponds to figure 1 Step 1. In a traditional ARM processor, four assembly statements are required to complete this function, so four clock cycles are required. To speed up the pro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More