CPU restraint forming and verifying method based on boundary condition and self detection random test

A technology of random testing and boundary conditions, applied in software testing/debugging, etc., can solve problems such as time-consuming and large re-testing time consumption, and achieve the effect of independent architecture, accelerated verification progress, and rapid discovery

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

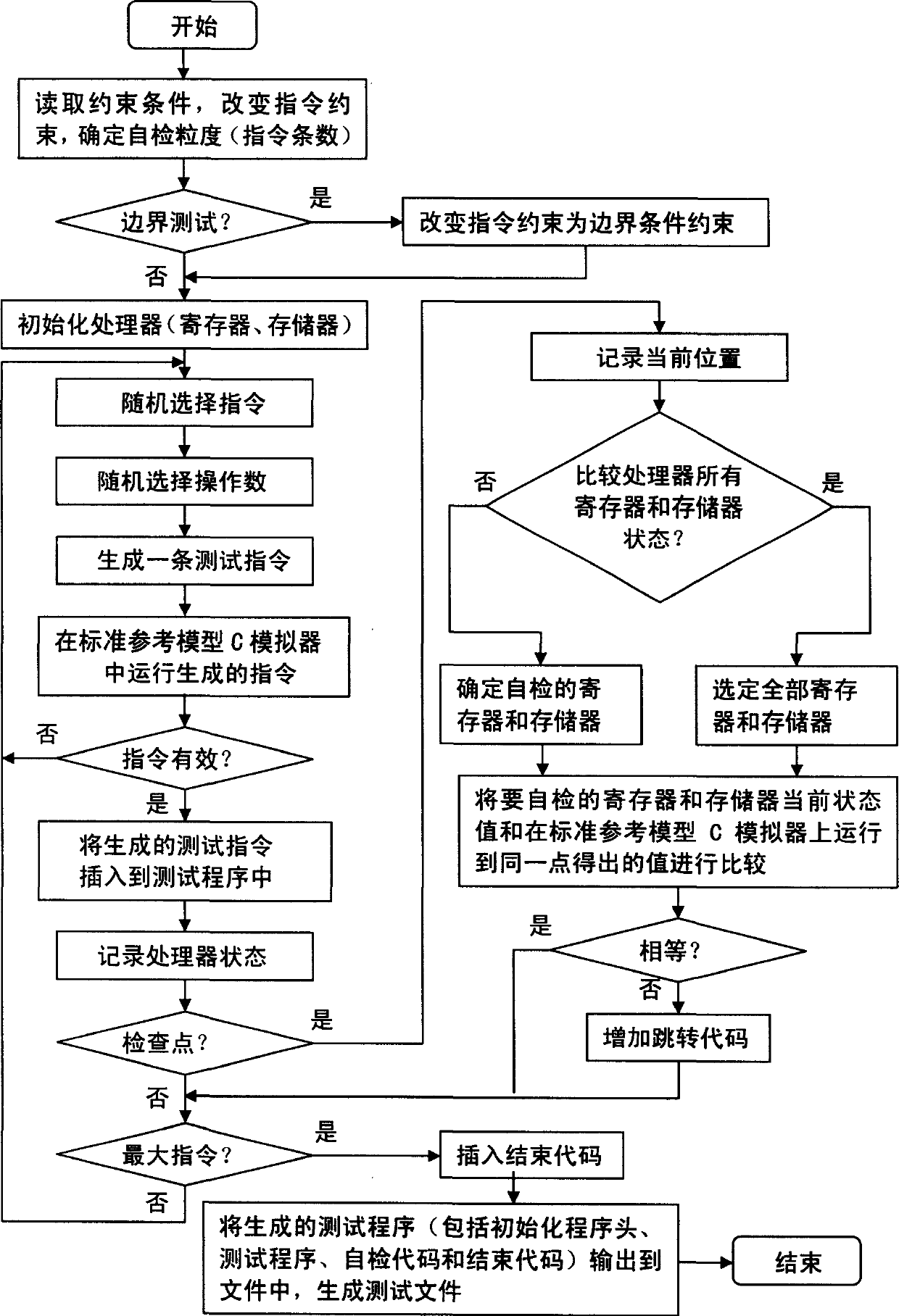

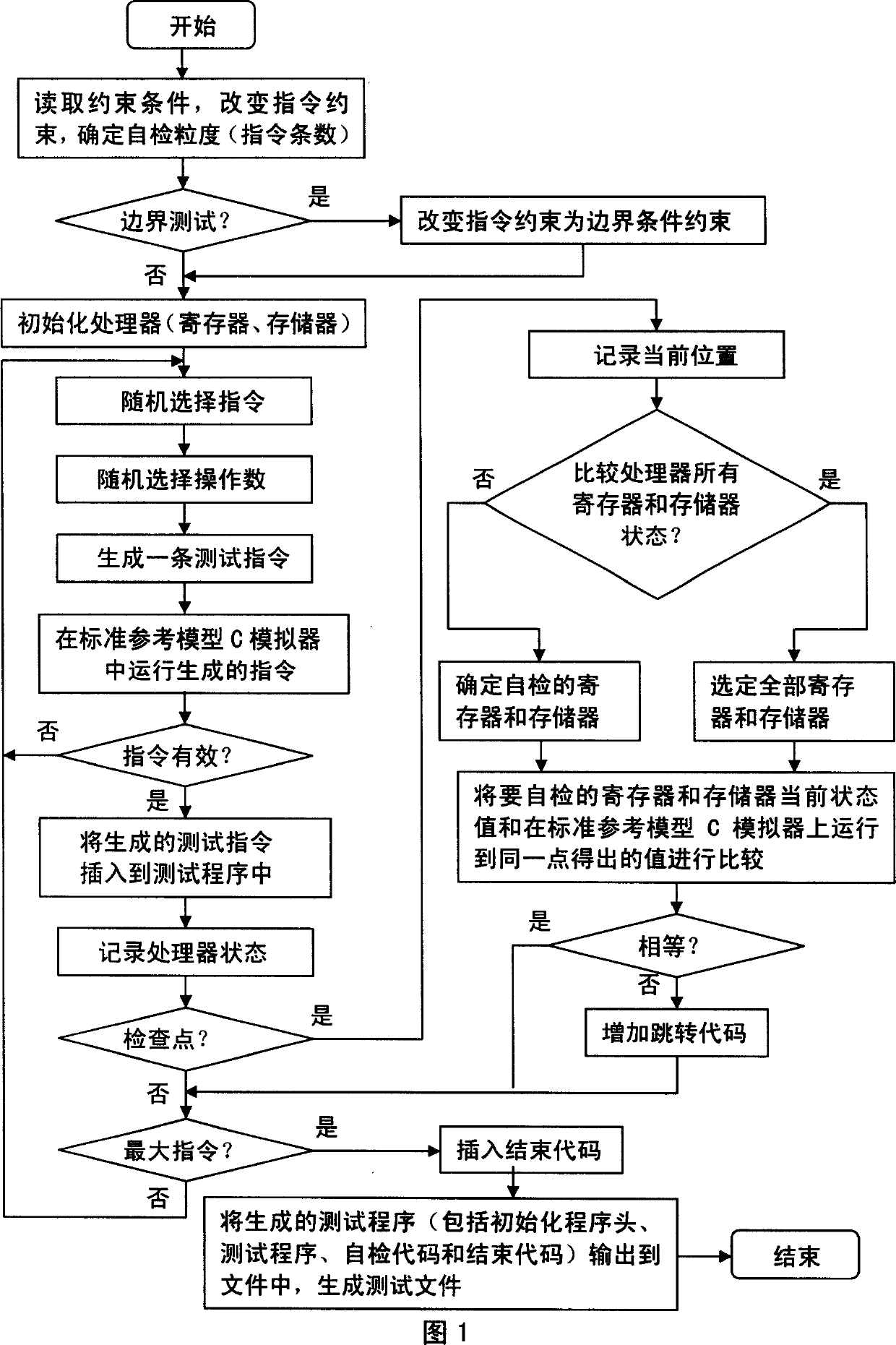

[0070] The specific implementation mode of the CPU constraint generation verification method based on boundary conditions and self-checking random testing is as follows:

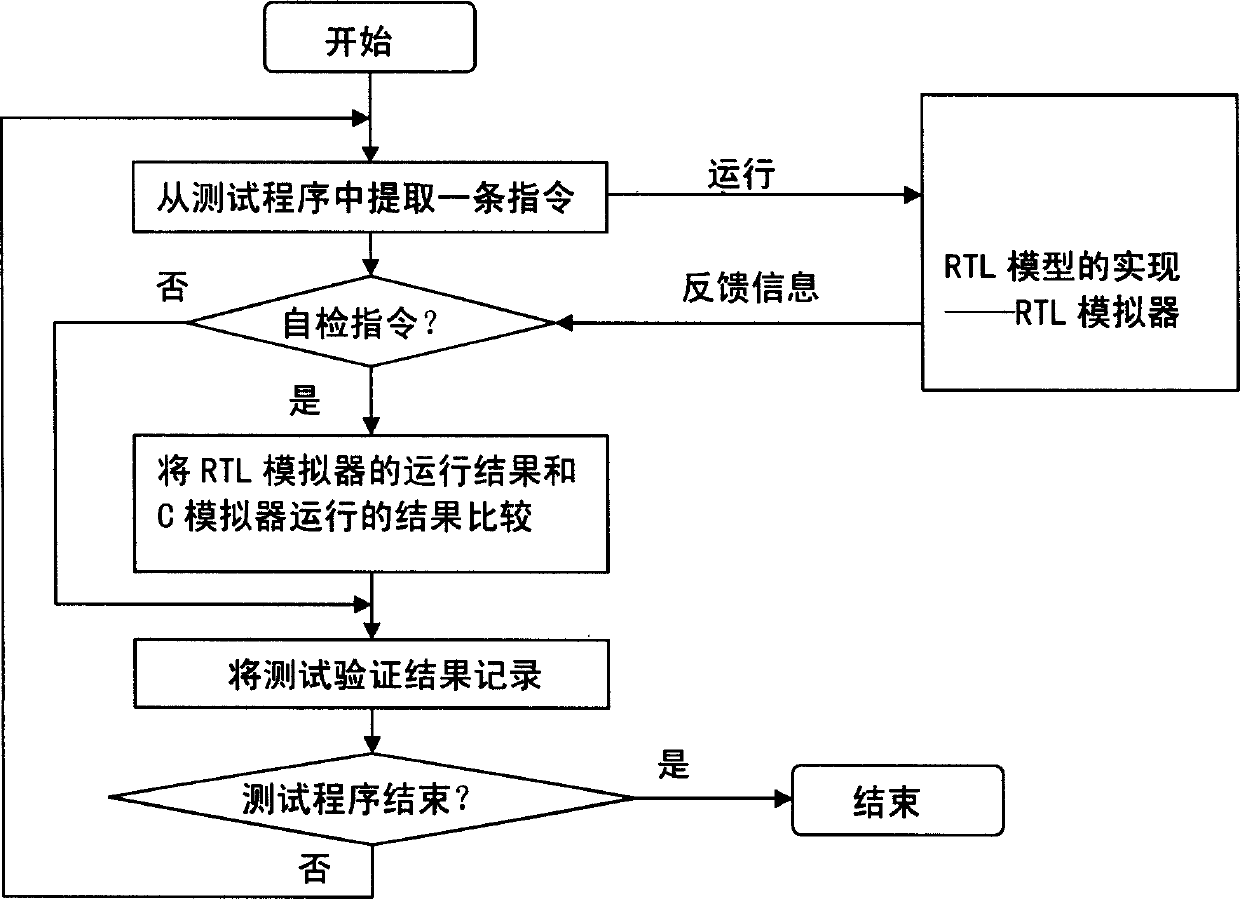

[0071] Two models are included in the random testing environment: architectural model and RTL model. The architecture model is the desired processor model, which is implemented using a C simulator and exists as a standard reference model. The RTL model is the model to be tested and verified. The purpose of random testing and verification is to test whether the RTL model is consistent with the architectural model.

[0072] Both the RTL model and the architecture model can output the processor state at each clock cycle, and by comparing the processor states of the two models, it is possible to judge whether the two models are consistent. If they are inconsistent, it means that there is an error in the RTL model. The goal of random testing is to achieve complete agreement between the RTL model and the archite...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More