An extensible asip structure platform and instruction processing method

An instruction and platform technology, applied in the field of ASIP structure platform and instruction processing, can solve problems such as limited register resources and inability to support dedicated extended instructions, and achieve the effects of increased software and hardware overhead, easy implementation, and simple principle.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

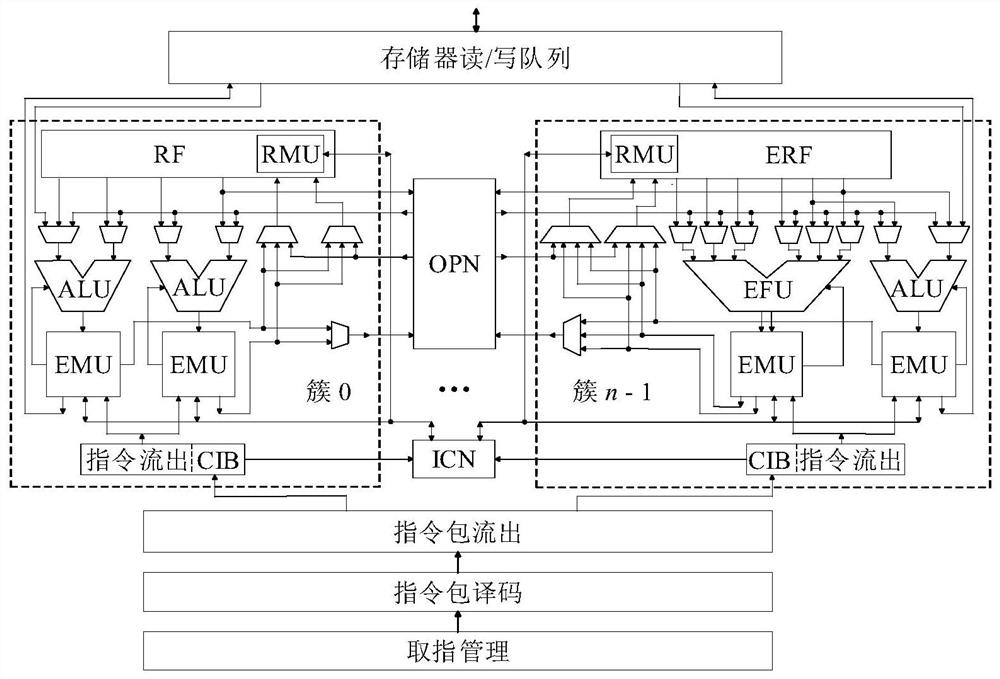

[0036]The scalable ASIP structure platform CASIP (Clustered Application Specific Instruction-set Processor) of the present invention, the CASIP structure is a clustered processor built on the basis of OR1200. Such as figure 1 As shown, a block diagram of the CASIP structure is shown. The CASIP of the present invention has a 6-stage integer pipeline, that is, an instruction fetch unit, a decoding unit, an outflow unit, a number fetch unit, an execution unit and a write-back unit. The parallelism of the instruction fetch unit depends on the bit width of the interface between the instruction fetch logic and the storage system. The degree of parallelism of the instruction decoding unit can be flexibly set according to the maximum length allowed by the instruction packet. Since the instruction outflow unit is performed in units of instr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More