Circuit switched to chip testing mode by utilizing negative voltage

A chip testing, negative voltage technology, applied in the direction of logic circuits, electrical components, pulse technology, etc., can solve the problems of increasing chip cost and design complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

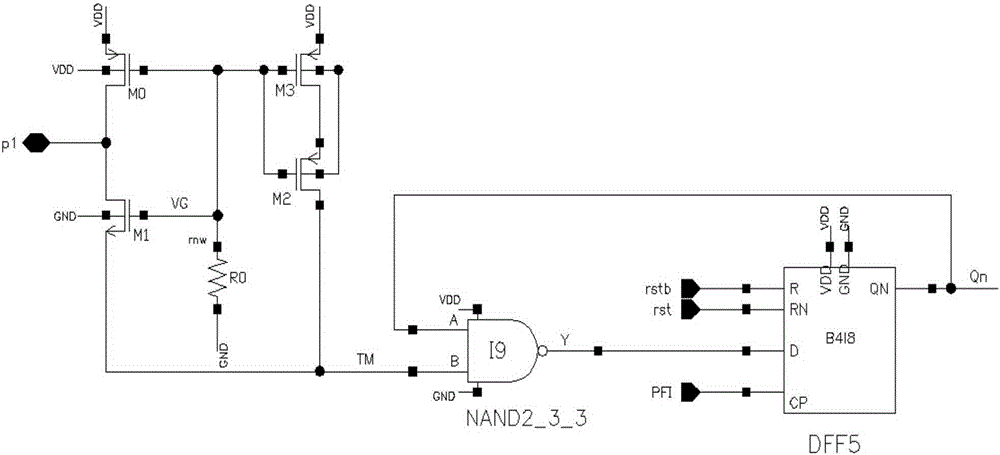

[0018] see figure 1 , a circuit that uses a negative voltage to enter a chip test mode, including a switch M0, a switch M1, a resistor R0, and an invertor I9, the source of the switch M0 is connected to the power supply VDD, and the drain of the switch M0 is connected to the chip tube The pin P1 and the drain of the switch tube M1, the gate of the switch tube M0 are connected to the resistor R0, the gate of the switch tube M1, the gate of the switch tube M2 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More