Digital logic circuit with stable reset control

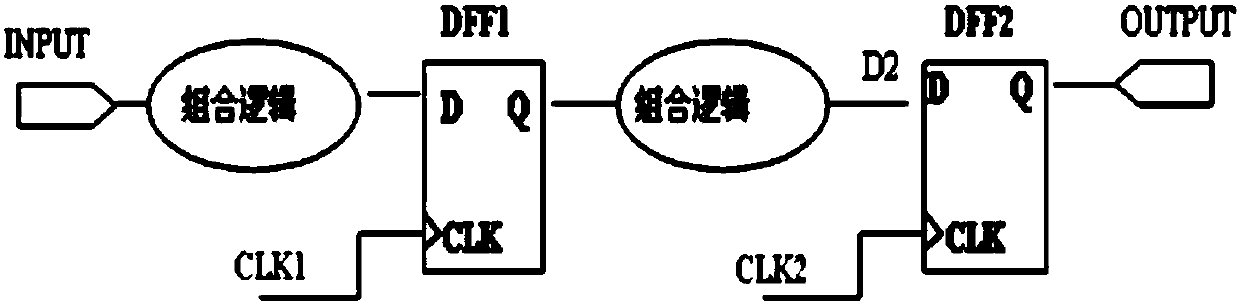

A digital logic circuit and reset control technology, applied in the field of digital logic circuits, can solve the problems of mutual deadlock of clock/reset functions and the inability of deburring circuits to meet requirements, and achieve the effect of reliable and stable reset control.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Attached below Figure 2-Figure 8 , the specific embodiment of the present invention will be further described in detail.

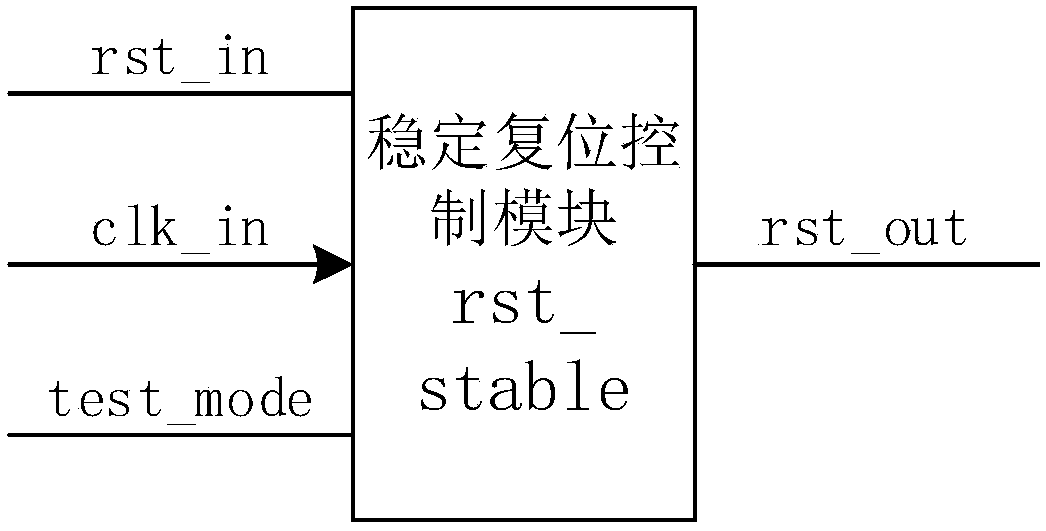

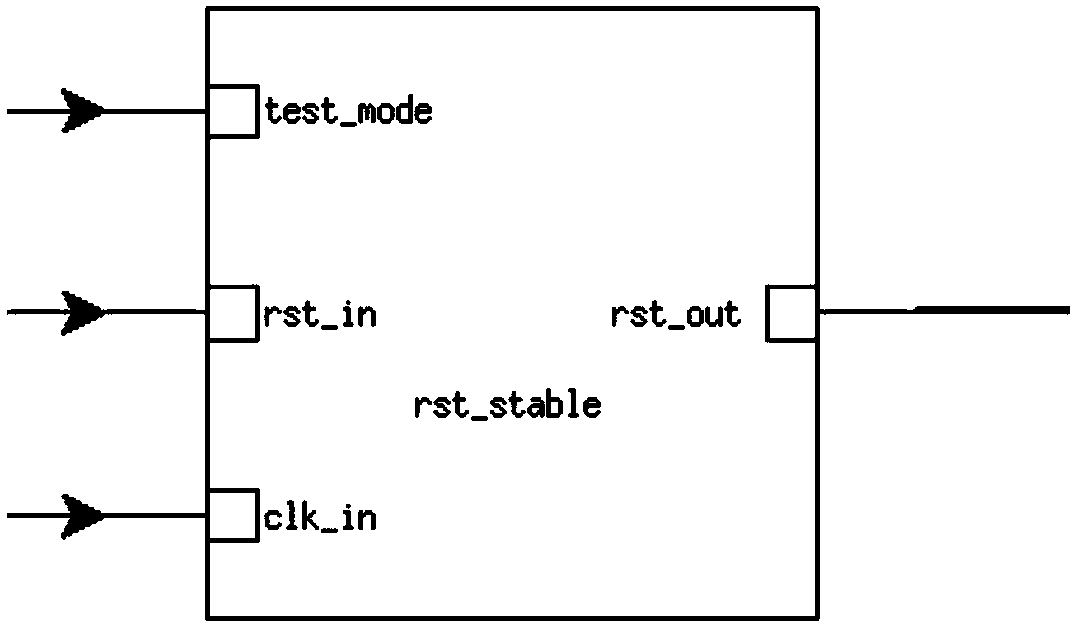

[0041] see figure 2 and image 3 , figure 2 Shown is the structural representation of the digital logic circuit with stable reset control of the present invention; image 3 Shown is a logic schematic diagram of a stable reset control module in the digital logic circuit of the present invention. As shown in the figure, the digital logic circuit with stable reset control includes an input terminal rst_in, an output terminal rst_out, a stable reset control module (not shown), a test mode control signal test_mode input terminal, and a synchronous clock signal clk_in input terminal.

[0042] It should be noted that the digital logic circuit with stable reset control of the present invention adopts a specific circuit design so that the internal D flip-flop is driven by the synchronous clock signal clk_in after the input clock is stabilized for a pe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More