Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as leakage current, failure to meet MOSFET device performance, short channel effect, etc., to improve device performance, Improve the inverse short channel effect, reduce the effect of junction capacitance and junction leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

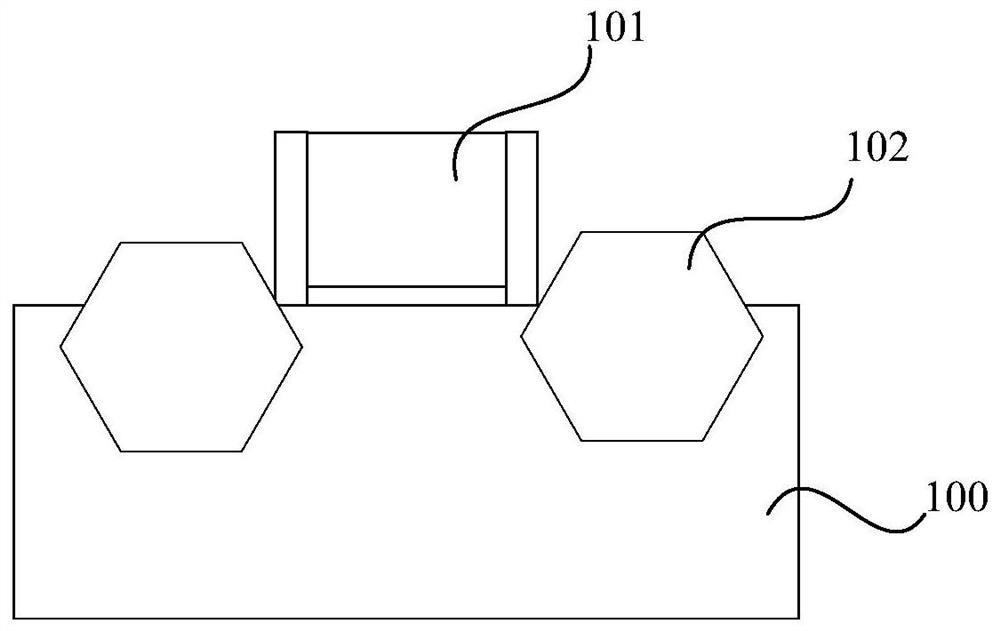

[0049] Please refer to figure 1 , a PMOS transistor comprising a semiconductor substrate 100, a gate stack structure 101 formed on the surface of the semiconductor substrate 100, and an embedded silicon germanium source and drain formed in the semiconductor substrate 100 on both sides of the gate stack structure 101 102, the formation process includes etching the semiconductor substrate 100 on both sides of the gate stack structure 101 to form a "Σ (Sigma)" shaped source-drain groove; The silicon germanium stress layer is epitaxially grown in the groove, or a stress seed layer is first grown, and then the silicon germanium stress layer is epitaxially grown to form the embedded silicon germanium source and drain 102 .

[0050] With the shrinking of the gate length of transistors, such as entering the 28nm technology node, the short channel effect (SCE) and short channel effect (RSCE) become the key restrictive factors for the performance improvement of the above-mentioned PMOS ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap