A method of transparently transmitting sdh bus data based on fpga

A technology of transparent transmission and bus, applied in the direction of bus network, data exchange through path configuration, electrical components, etc., can solve problems such as unfavorable signal integrity, PCB wiring business expansion, and many interconnected signal lines, and achieves a debug-friendly solution. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

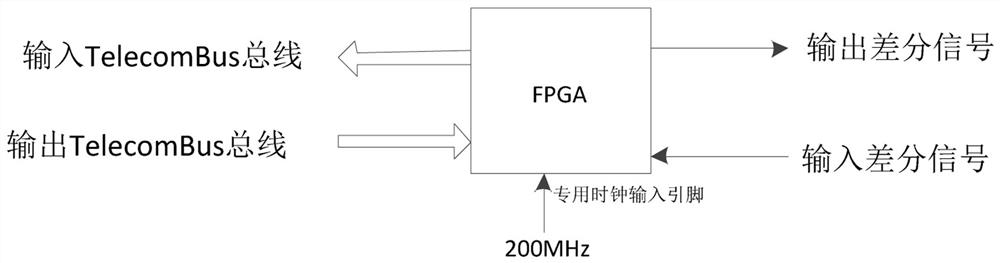

[0048] A method for transparently transmitting SDH bus data based on FPGA. This method uses 2 pairs of FPGA differential IO pins, such as image 3 As shown, the two-way transmission of bus data is realized by using SDR technology for 1 channel or using DDR technology for 2 channels. The programmable device FPGA is connected to the TelecomBus bus interface and 200MHz clock. The differential IO of the FPGA is connected to the other through the connector or directly The differential IO connection of FPGA includes the following steps, such as Figure 4 Shown:

[0049] 1) TelecomBus bus -> The processing steps of the differential IO direction are as follows:

[0050] 1-1) First, use the associated 19.44MHz clock of the TelecomBus bus to combine the 8bit data, 1bitJ0J1 signal and 1bit PL signal of the bus into 10bit data, and perform 5b / 6b encoding;

[0051] 1-2) Send the encoded data to the sending buffer;

[0052] 1-3) Read 6bit data from the cache, and use OSERDES to perform parallel / ser...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com