Three-dimensional vertical resistive random access memory array and operation method and device thereof, equipment and medium

A technology of resistive memory and operation method, applied in static memory, digital memory information, information storage and other directions, can solve the problems of high error programming operation of unselected cells, inability to read operations of a single or specific multiple devices, etc., to overcome errors. The effect of programming operations, avoiding misprogramming operations, and reducing the probability of misprogramming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

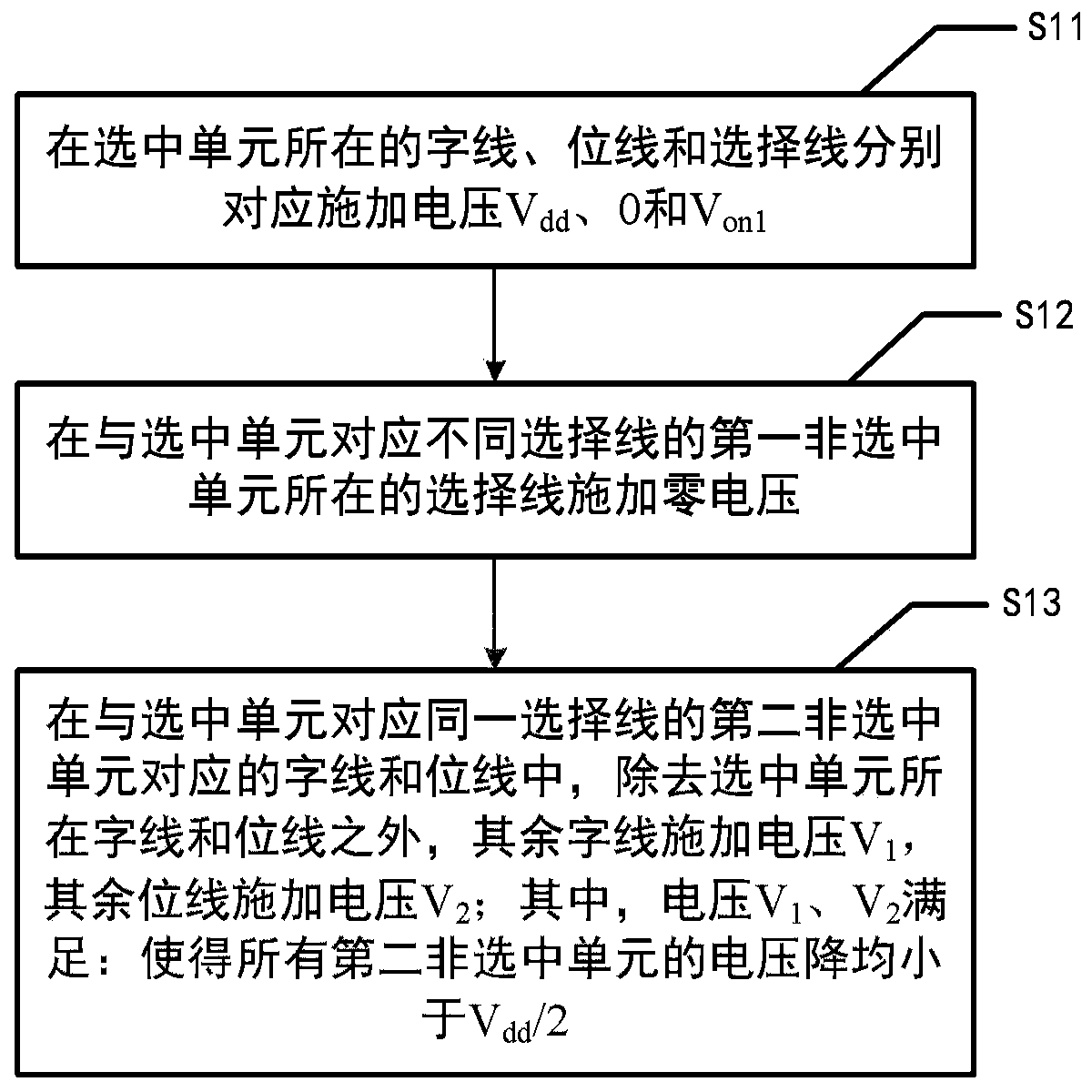

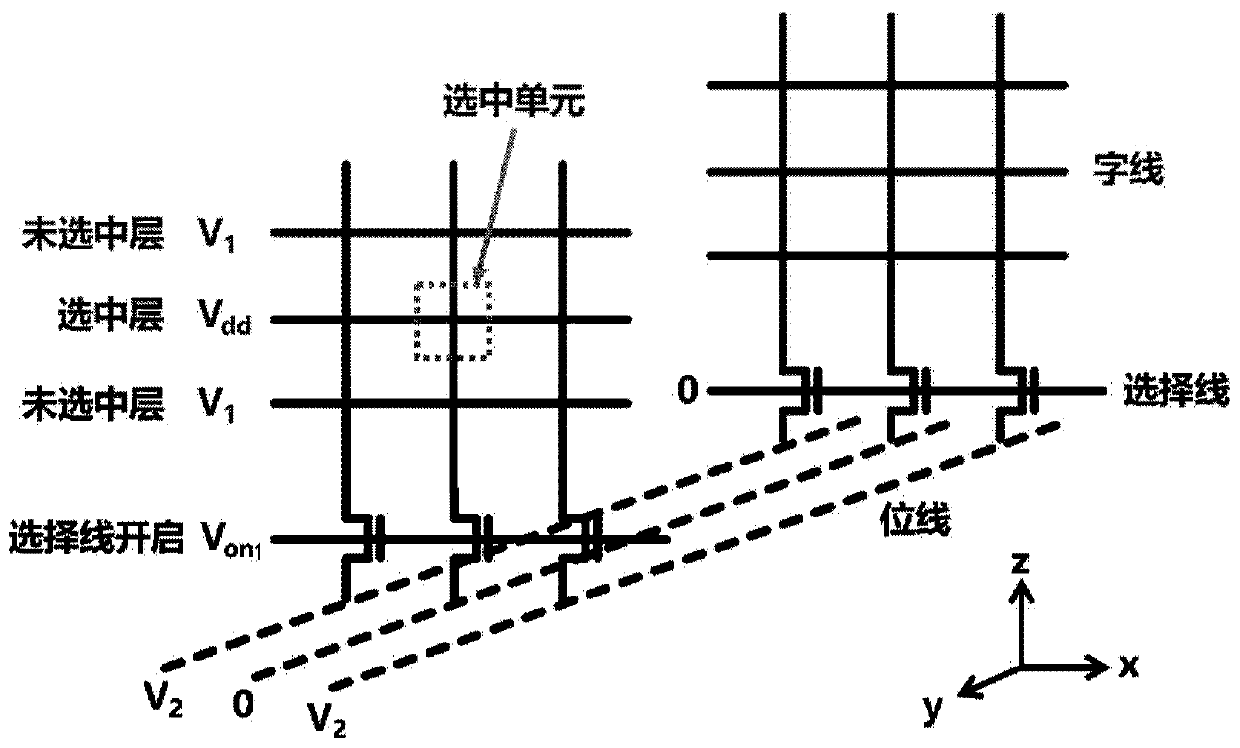

[0045] The first exemplary embodiment of the present disclosure provides a method for operating a three-dimensional vertical resistive memory array, in which a specific resistive memory in the three-dimensional vertical resistive memory array is selected as a selected cell for programming operation.

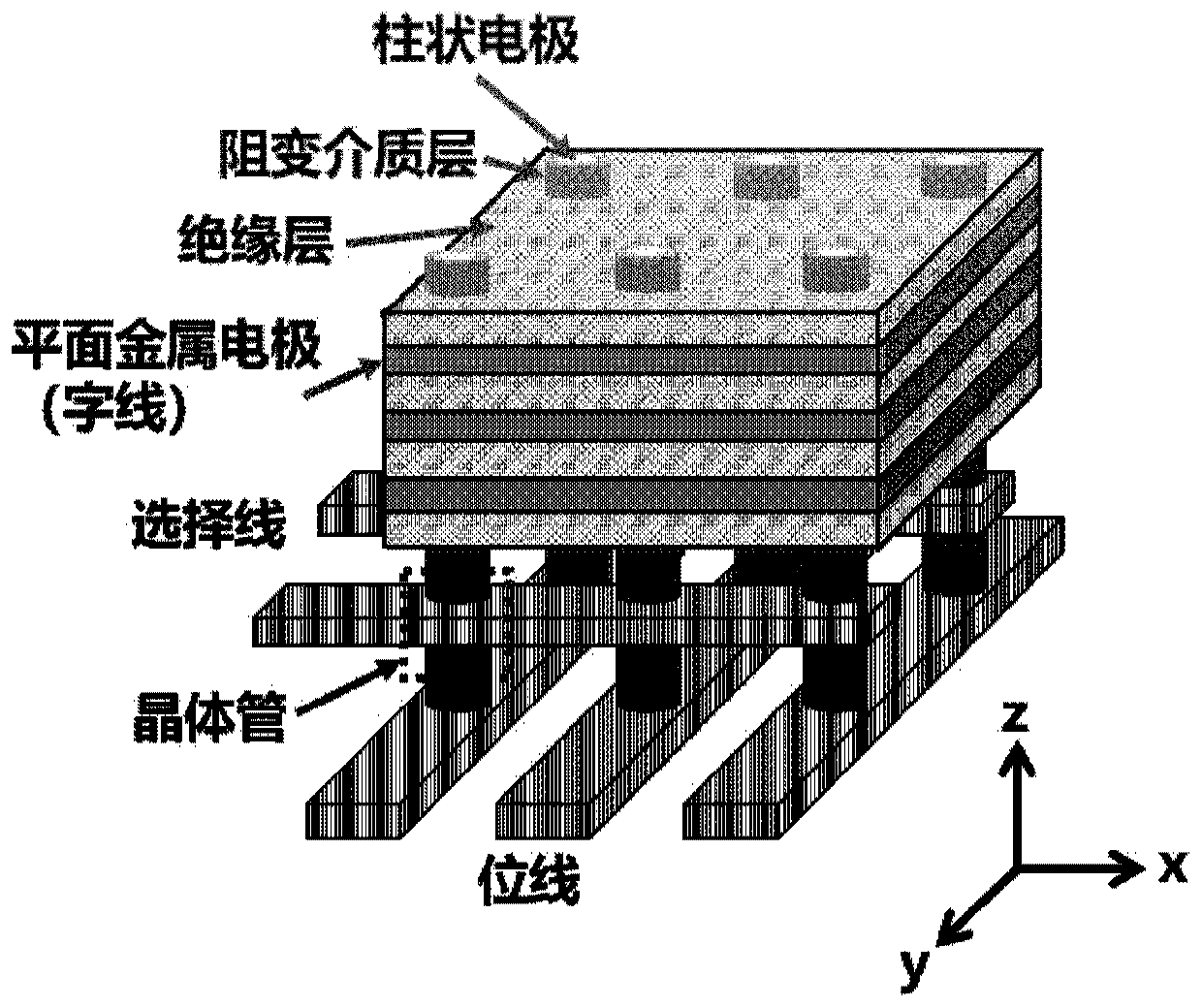

[0046] combine first figure 1 The structure of the three-dimensional vertical resistive memory array of this embodiment is introduced.

[0047] The operation method of the present disclosure is applicable to a three-dimensional vertical resistive memory array. The three-dimensional vertical resistive variable memory array includes: a stacked structure in which planar conductor layers and insulating layers are stacked in sequence; a columnar electrode vertically penetrating the stacked structure; a resistive dielectric layer surrounding the periphery of the columnar electrode; between the stacked structure and the columnar The intersection of the electrodes forms a resistive vari...

no. 2 example

[0072] In the second exemplary embodiment of the present disclosure, a method for operating a three-dimensional vertical resistive memory array is provided, in which a specific resistive memory in the three-dimensional vertical structure resistive memory array or on the same word line is selected A specific plurality of RRAMs on the / bit line are used as selected cells to perform a read operation. The read operation method in this embodiment can perform read and write operations on the same device as the programming operation in the first embodiment, or can be implemented separately from the method in the first embodiment, and the read operation illustrated in this embodiment is implemented separately (read operation) or the write operation (program operation) exemplified in the first embodiment is implemented separately.

[0073] Figure 6 It is a flowchart of a read operation method of a three-dimensional vertical resistive memory array according to an embodiment of the pre...

no. 3 example

[0095] In a third exemplary embodiment of the present disclosure, a three-dimensional vertical resistive memory array is provided for performing the above operation method.

[0096] For example, as shown in reference 1, the three-dimensional vertical resistive variable memory array of this embodiment includes: a laminated structure in which planar conductor layers and insulating layers are stacked in sequence; columnar electrodes vertically penetrating through the laminated structure; resistive variable memory arrays surrounding the columnar electrodes Dielectric layer; a resistive variable memory comprising a planar conductor layer, a resistive dielectric layer and a columnar electrode formed at the intersection of the stacked structure and the columnar electrode, wherein the planar conductor layer and the columnar electrode are respectively used as the resistive variable memory The two electrodes of the two electrodes; at the same time, the planar conductor layer is used as a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More