Complementary metal oxide semiconductor output circuit

A technology of oxide semiconductor and output circuit, which is applied in the direction of semiconductor devices, circuits, logic circuit connection/interface layout, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

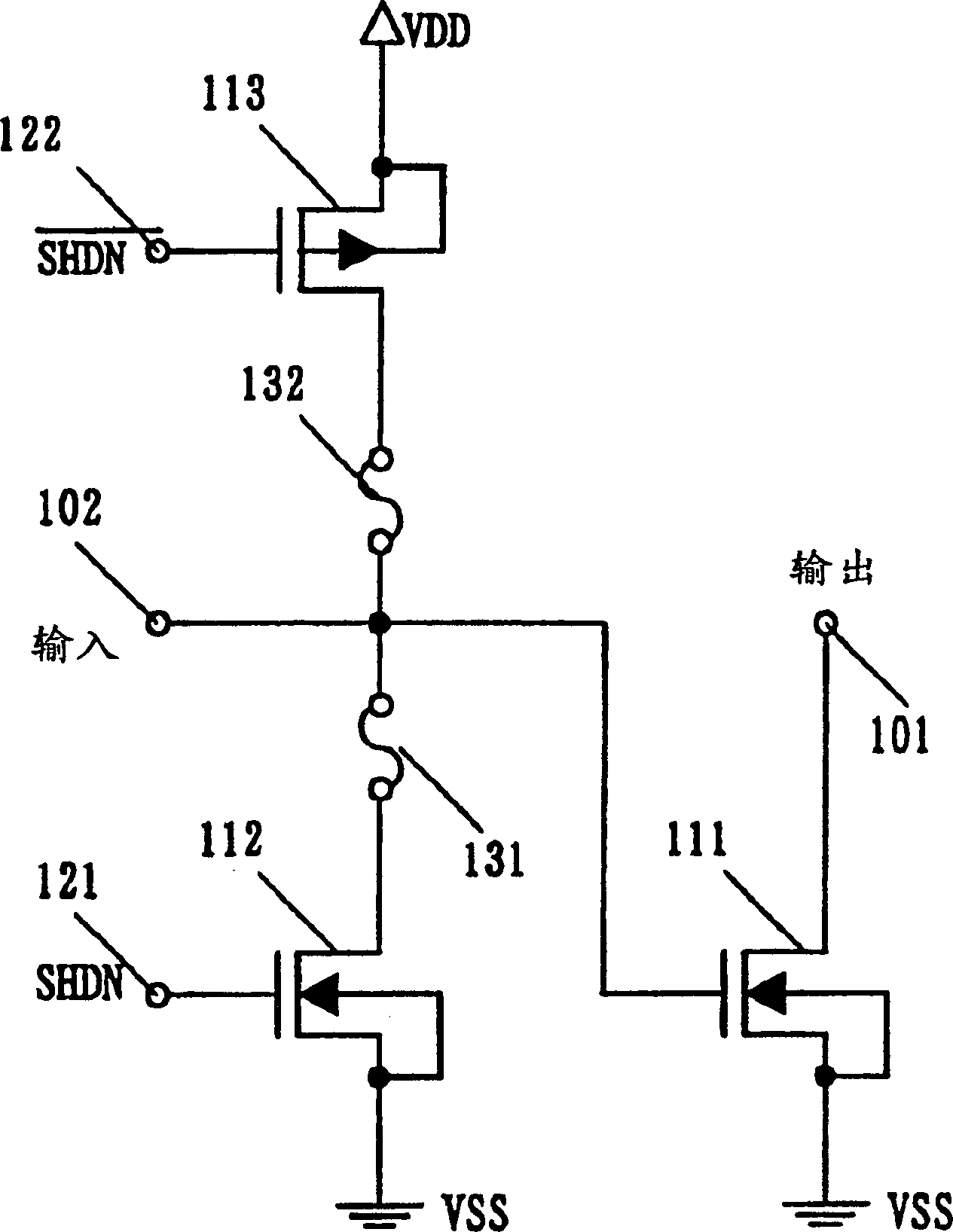

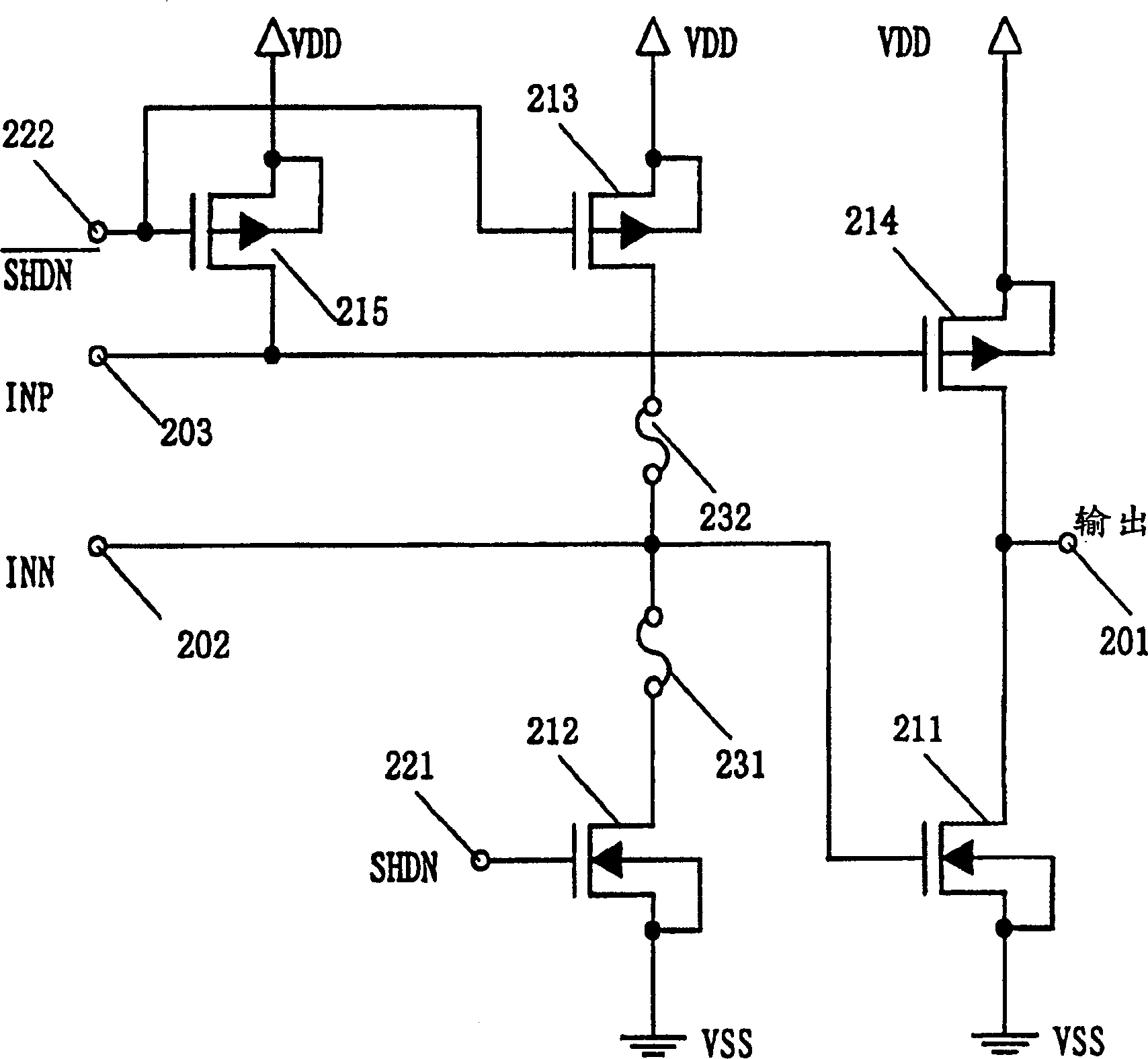

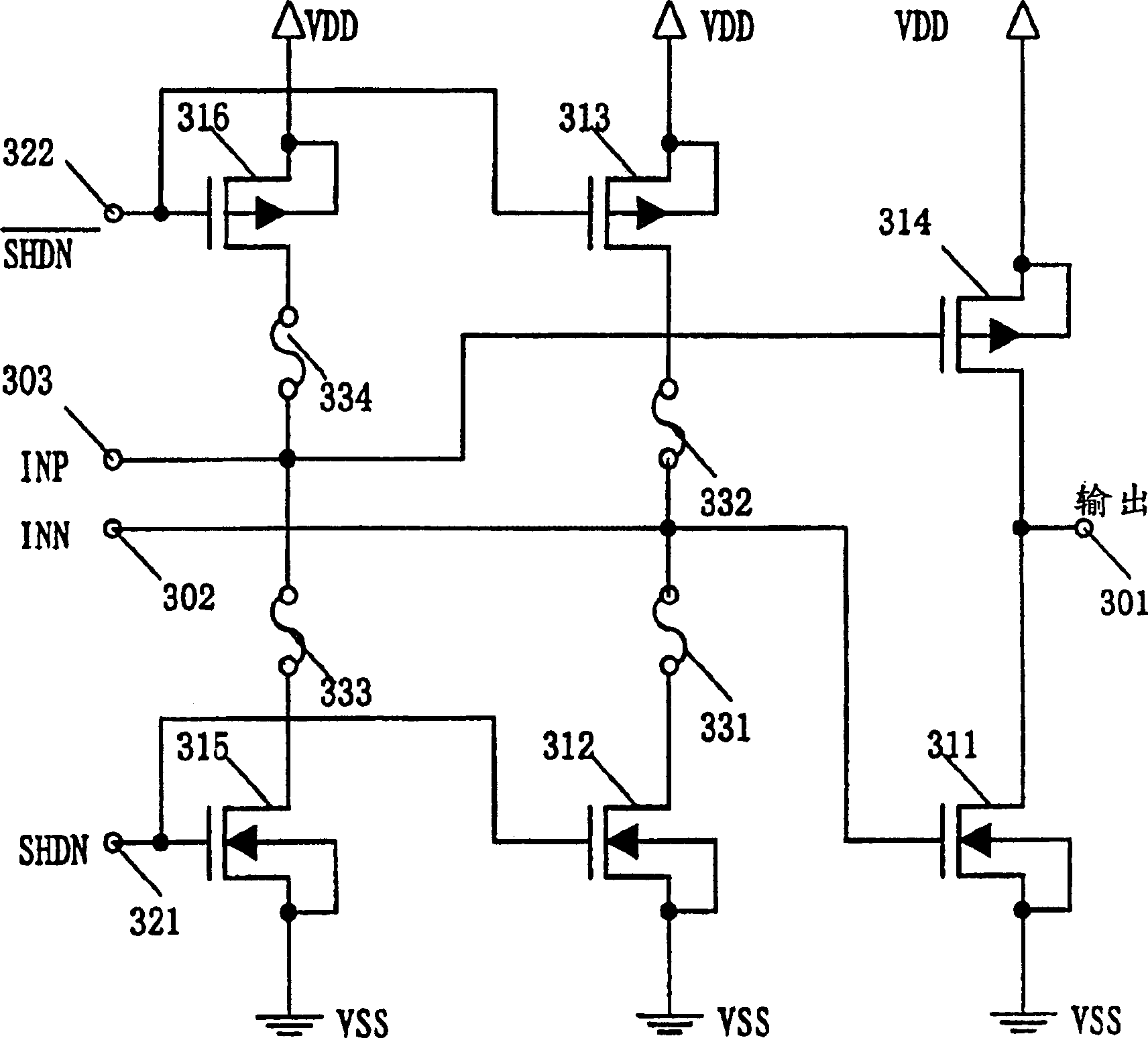

[0013] The embodiments of the present invention will now be described with reference to the drawings. figure 1 , 2 , 3, 5, and 6 are schematic diagrams showing examples of CMOS output circuits according to the present invention.

[0014] Refer to figure 1 , The input terminal 102 is connected to the gate of the NMOS transistor 111. The potential of the output terminal 101 is determined by the potential of the input terminal 102. When a signal is input to the off terminals 121 and 122, the NMOS transistor 112 and the PMOS transistor 113 are turned on. If the fuse 132 is disconnected and the fuse 131 is conductive at this time, the gate potential of the NMOS transistor 111 is pulled to VSS, so that the NMOS transistor 111 is turned off, thereby setting a high impedance at the output terminal 101. Conversely, if the fuse 131 is disconnected and the fuse 132 is conductive, the gate potential of the NMOS transistor 111 is pulled to VDD, the NMOS transistor 111 is turned on, and the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More