Method of manufacturing a semiconductor device

A technology of semiconductors and amorphous semiconductors, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve problems such as high leakage currents

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

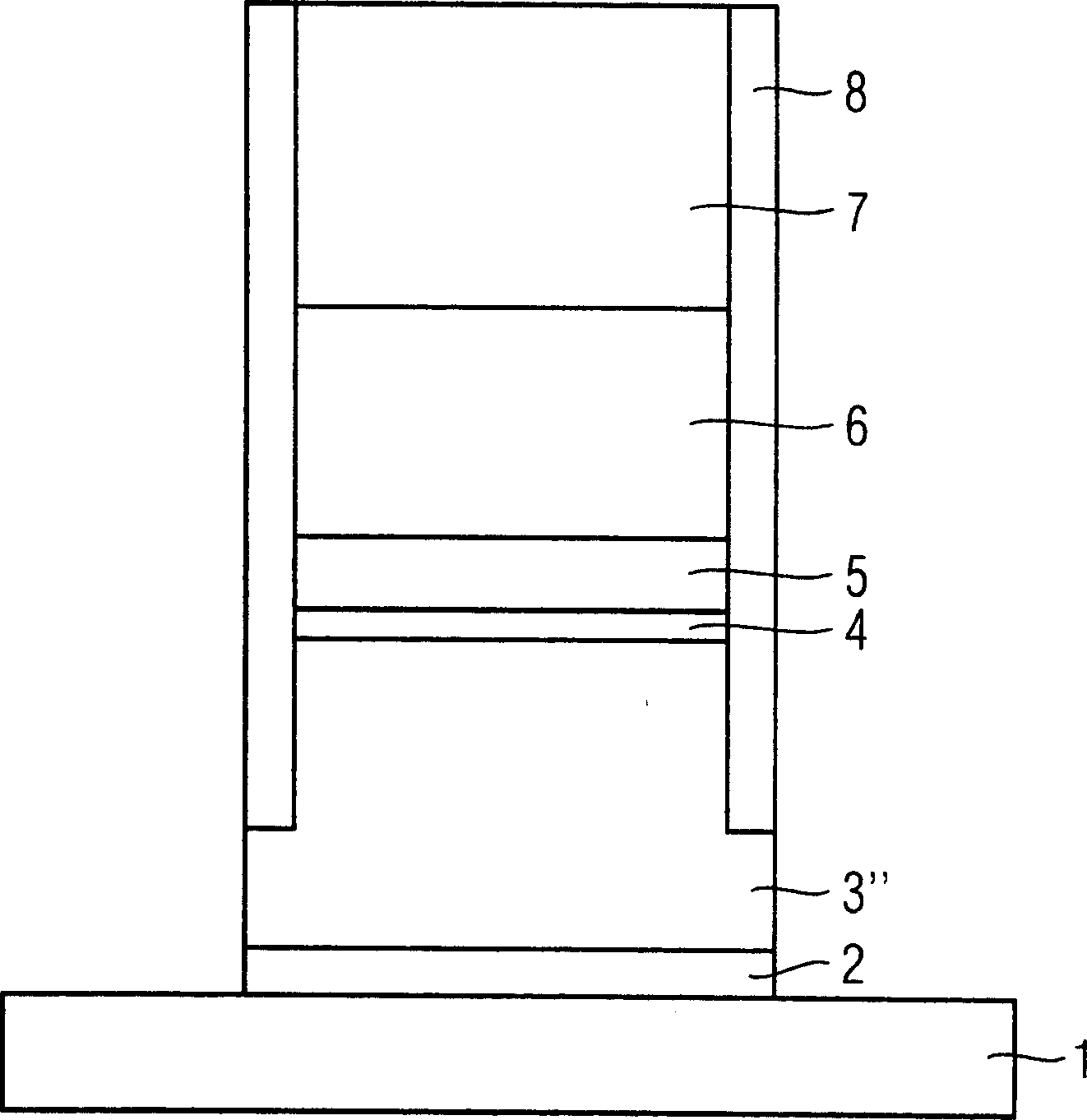

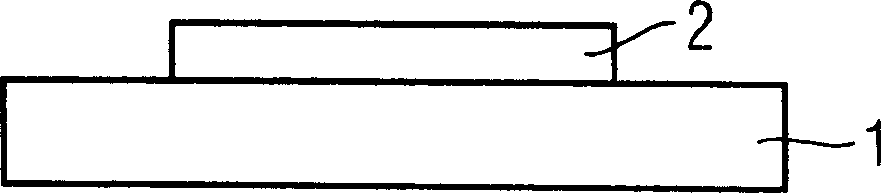

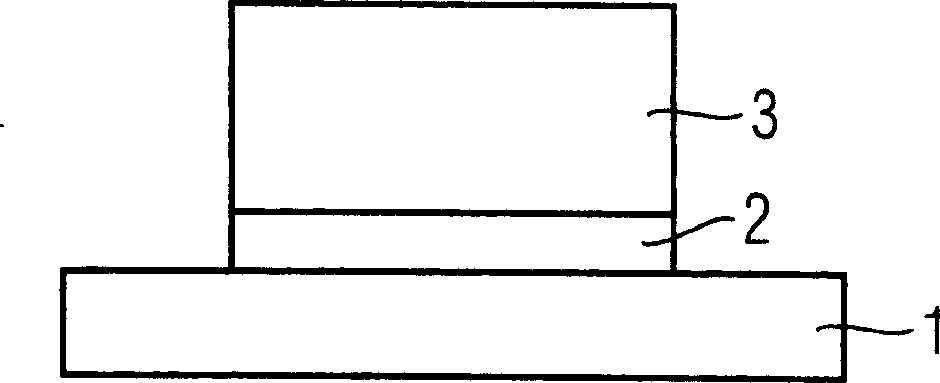

[0041] figure 1 A partial cross-sectional view of the gate stack is shown. On the substrate 1, a vertical gate stack is placed with the layers starting with the layer closest to the substrate 1 in the following order: gate dielectric layer 2, doped polycrystalline semiconductor layer 3", some intermediate layers 4, 5. Form the metal layer 6 of the contact or wire and the final cap layer nitride 7. The nitride or oxide spacer (spacer) 8 can be vertically arranged in the stack along all layers except the gate dielectric layer 2 at the side.

[0042] Substrate 1 contains a typical semiconductor structure, including drain and source regions arranged in different ways ( figure 1 not shown). Typically, the substrate 1 is positively (p-type) or negatively (n-type) doped.

[0043] A dielectric layer 2 is provided on the substrate above the gate region placed between the drain region and the source region. This dielectric layer 2 forms a gate dielectric layer isolating the subst...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap