Timer implementing method and apparatus

An implementation method and timer technology, applied in the direction of generating/distributing signals, etc., to achieve the effect of a reliable timer mechanism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

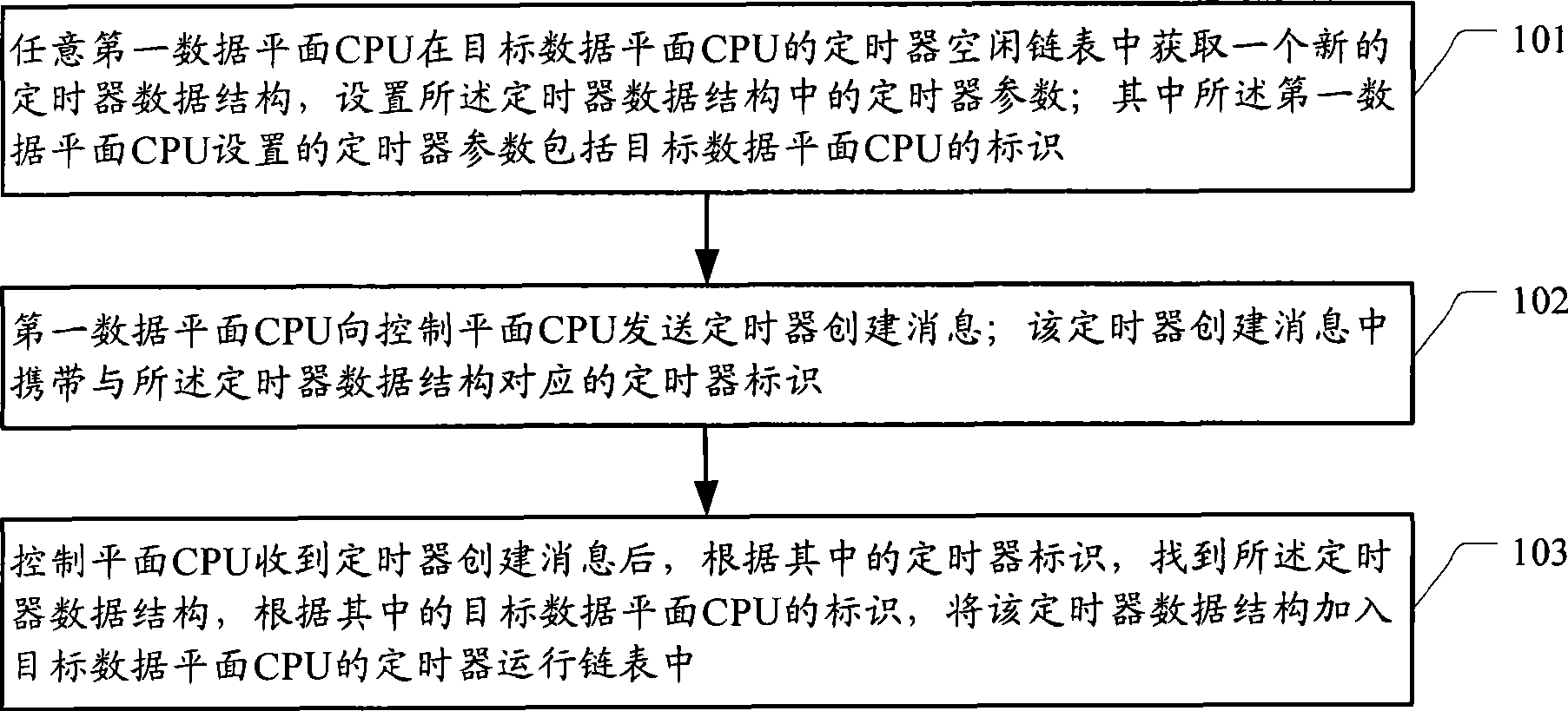

[0023] figure 1 It is a flowchart of a method for implementing a timer according to an embodiment of the present invention. Such as figure 1 As shown, the method includes the following steps:

[0024] Step 101, any first data plane CPU acquires a new timer data structure in the timer idle linked list of the target data plane CPU, and sets timer parameters in the timer data structure; wherein the first data plane CPU The set timer parameters include the identification of the target data plane CPU.

[0025] In this step, the first data plane CPU and the target data plane CPU may be the same CPU or different CPUs. This is because, in the business process, various business processes may be processed on different cores, and different stages of a message may also be performed on different cores. Therefore, different data plane CPUs need to process the same a business flow. For example, CPU A on the data plane classifies received packets, sends packets belonging to a certain ses...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com