High-robustness subthreshold memory cell circuit for limiting drain current

A memory cell circuit and threshold technology, which is applied in information storage, static memory, digital memory information and other directions, can solve the problem of process deviation of memory cells, and achieve the effect of reducing leakage current power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

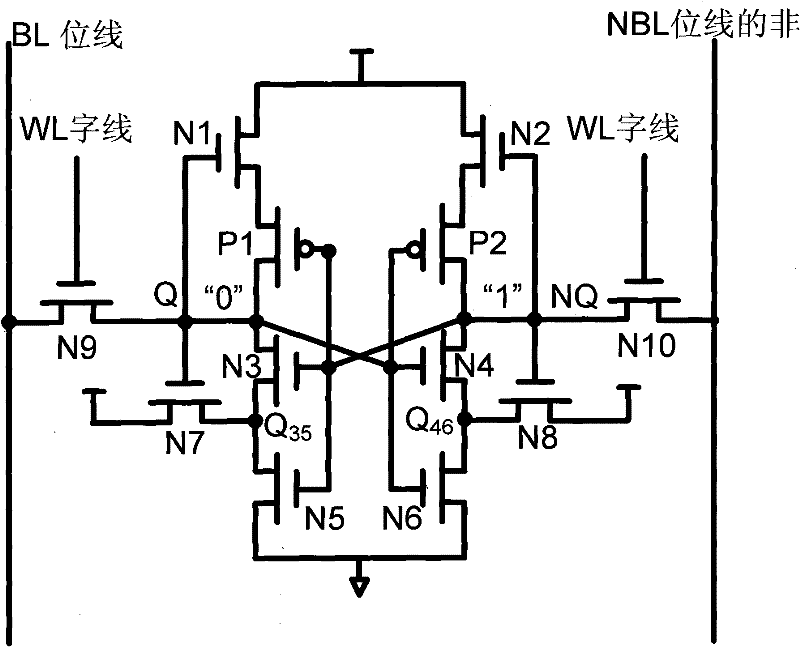

[0029] see figure 2 :

[0030] A. Write operation

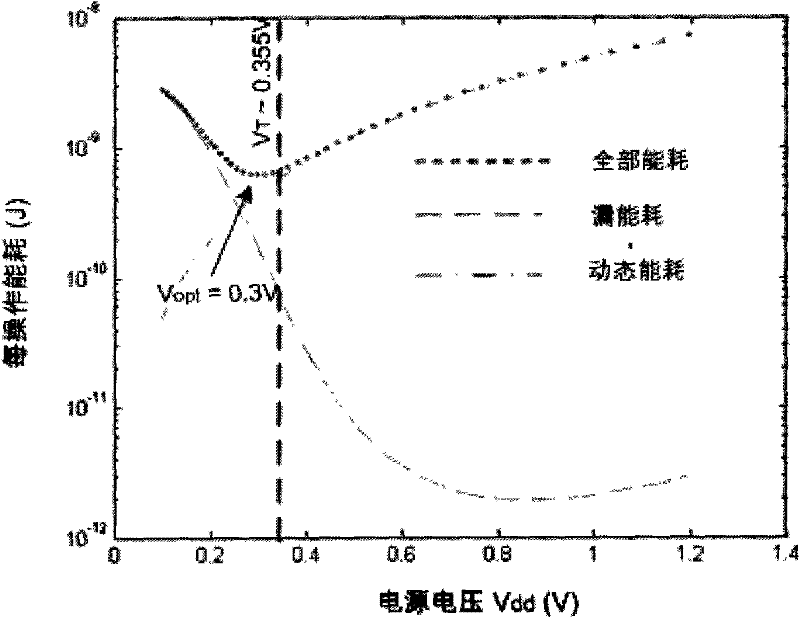

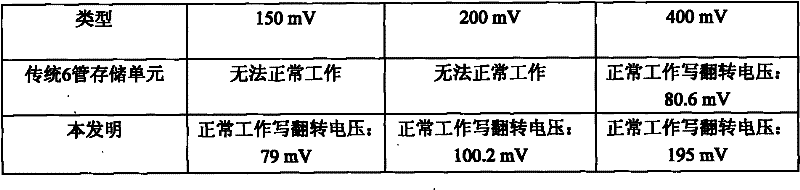

[0031] Due to the decrease of the overdrive voltage of the circuit in the sub-threshold region, the increase of the load capacitance and the instability of the process, it is difficult for the sub-threshold memory cell to maintain sufficient write noise margin. The subthreshold memory cell designed in this paper can effectively improve the writability of the memory cell by utilizing the internal positive feedback of the memory cell destroyed during the writing process and weakening the pull-down ability.

[0032] Let the initial value of the storage unit be: Q="0", Q is not a point Assuming a "0" is written to the Q NOT node, the bit line BL and the bit line NOT NBL are forced to "1" and "0". The word line WL becomes high level, Q non-dot Discharge until the P1 tube is turned on. In this way, the source terminal of N1 and the potential of point Q, Vgs="0", N1 is turned off. This advantageously breaks the feedback loo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More