Instruction processing method and its applicable superscalar pipeline microprocessor

A microprocessor and pipeline technology, applied in the direction of concurrent instruction execution, machine execution device, etc., can solve the problems of time consumption and a lot of time consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

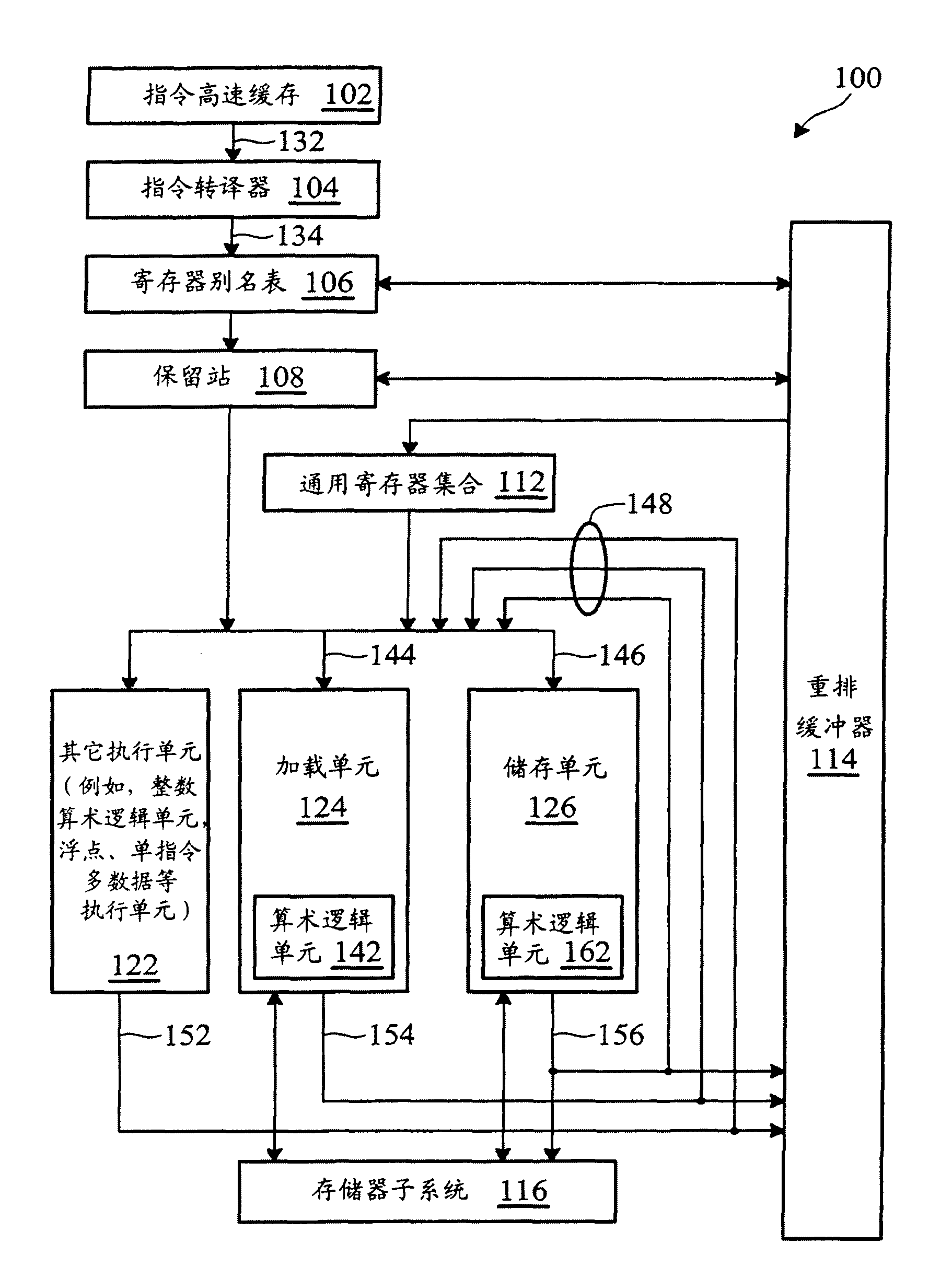

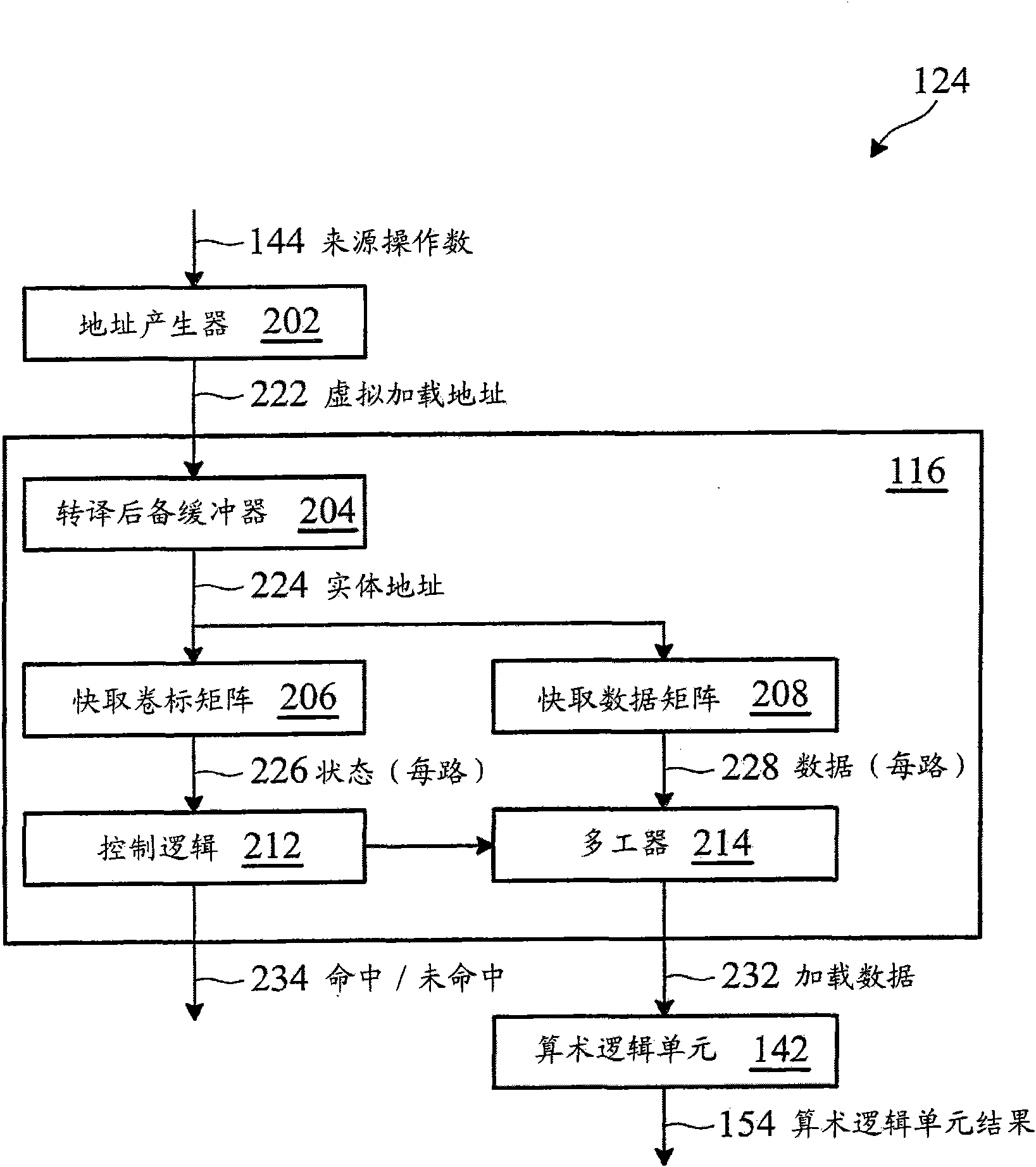

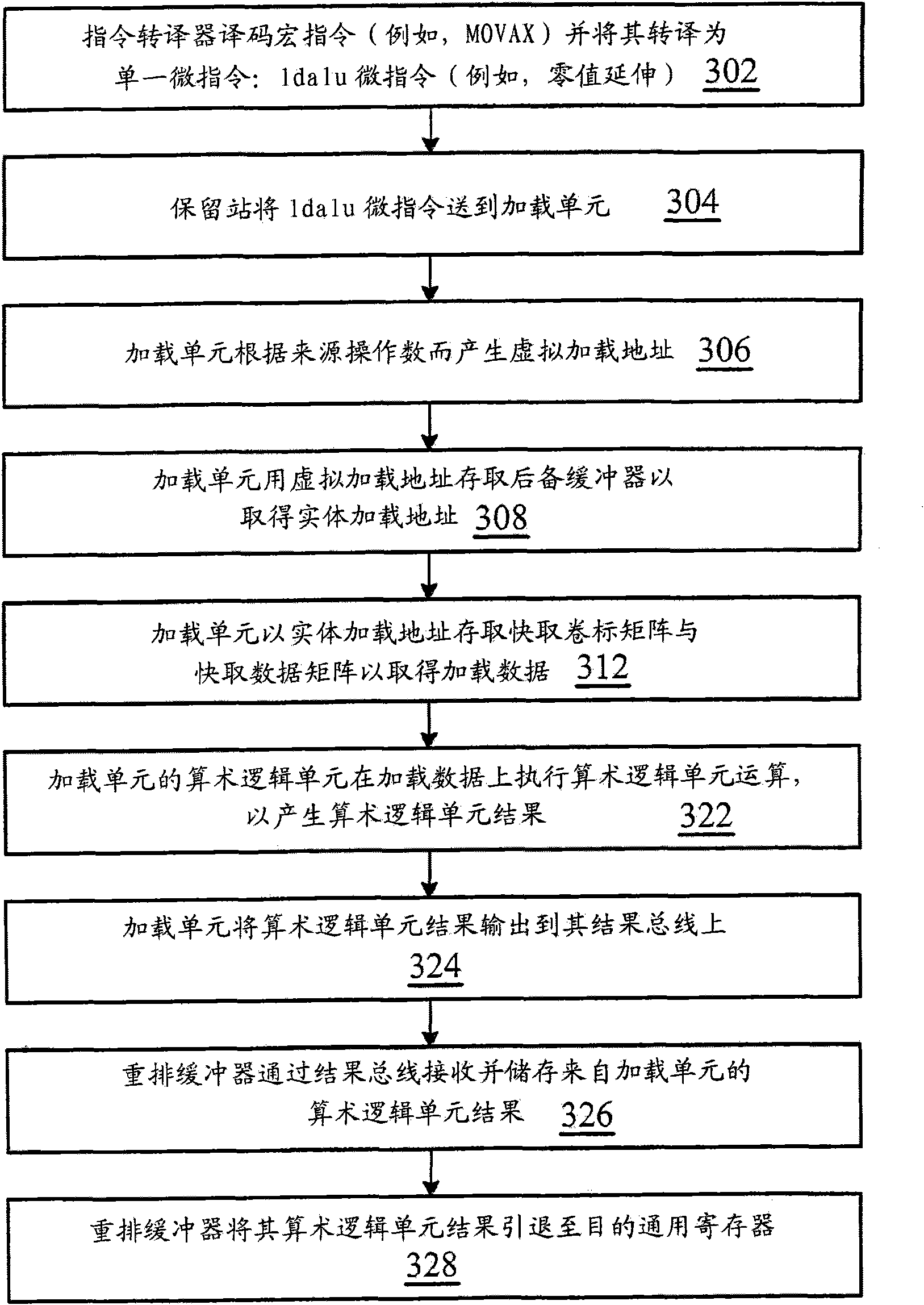

[0053]The inventors of the present invention have found that in the design of a pipeline flow loading unit, a part of frequency cycles may not be used in the last stage, that is to say, the delay time generated by the circuit in the last stage of the loading unit is only A fraction of the frequency cycle time. Therefore, the present invention advantageously integrates an arithmetic logic unit into the last stage of the load unit in an embodiment, so that the load unit can first load the load data extracted from the memory into the destination register. Perform arithmetic logic operations. Through this advantageous design, the time required for transferring the loaded data to another ALU to execute the ALU can be saved. The microprocessor of the present invention uses a load / store microprocessor architecture that implements the non-load / store x86 architecture of the processor (or the macroarchitecture of the processor). The instruction translator generates a special type of l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More