Nonvolatile memory with enhanced efficiency for address asymmetric nvm cells

A technology of magnetic components and access transistors, applied in the direction of static memory, read-only memory, digital memory information, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] overview

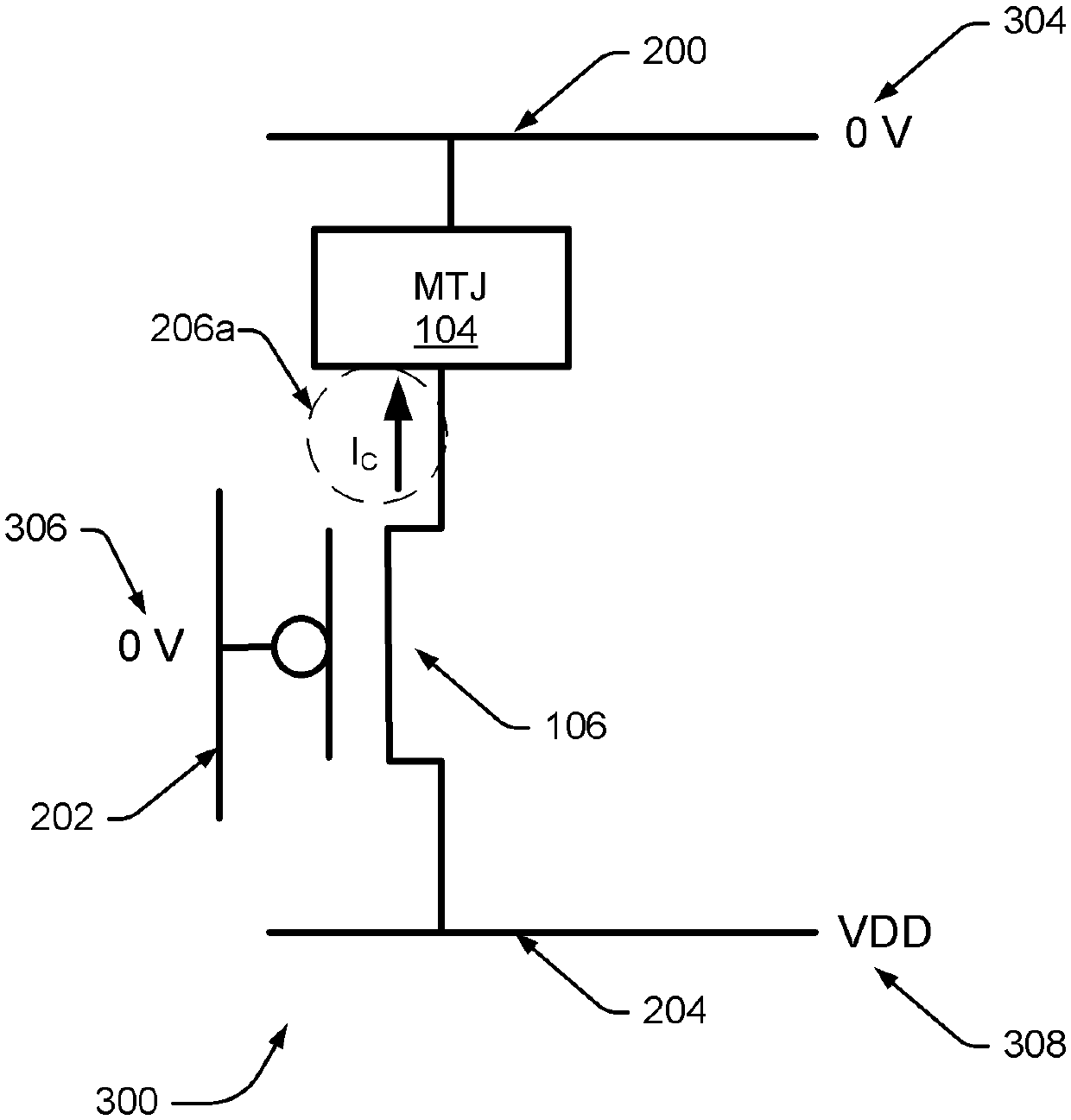

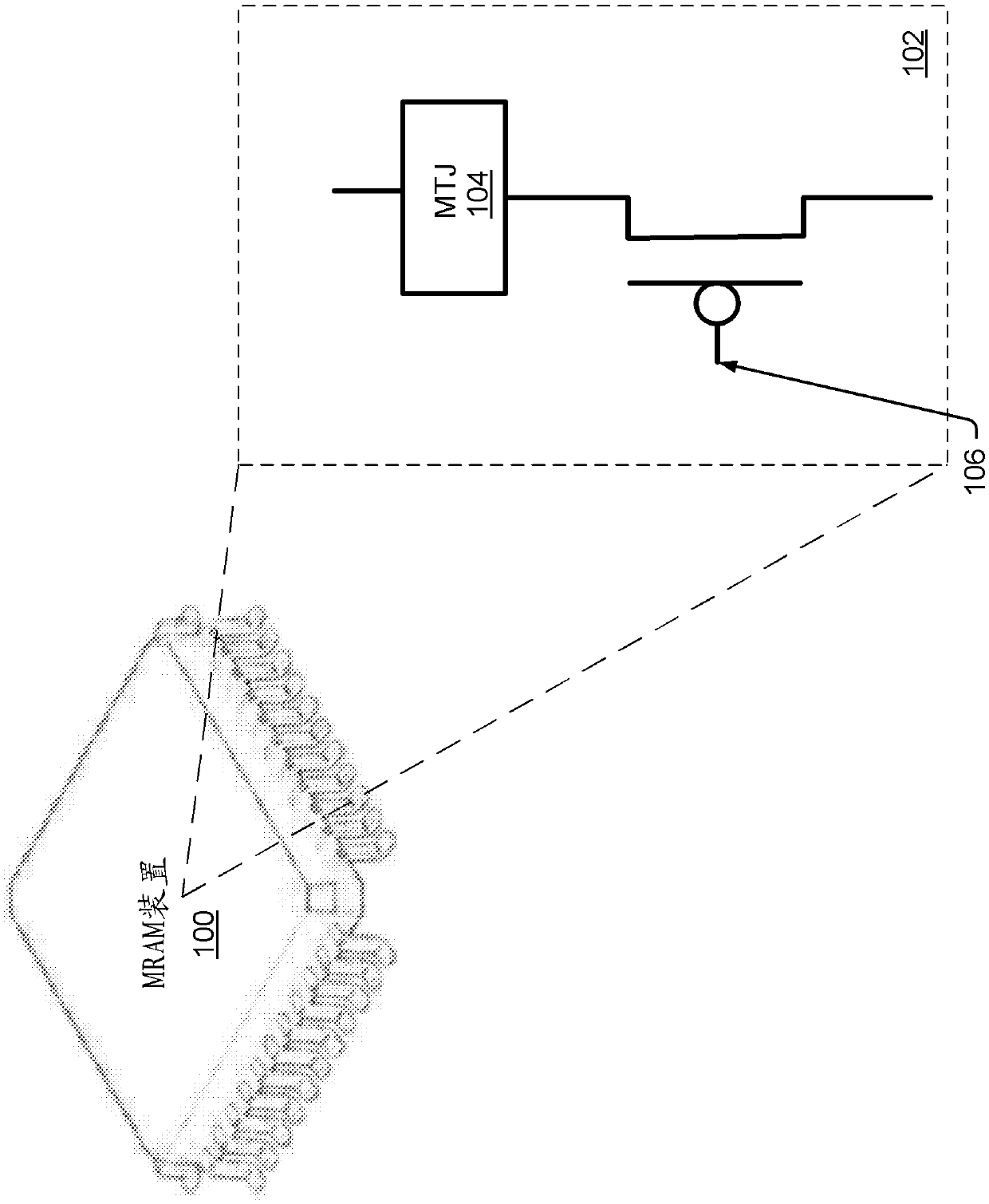

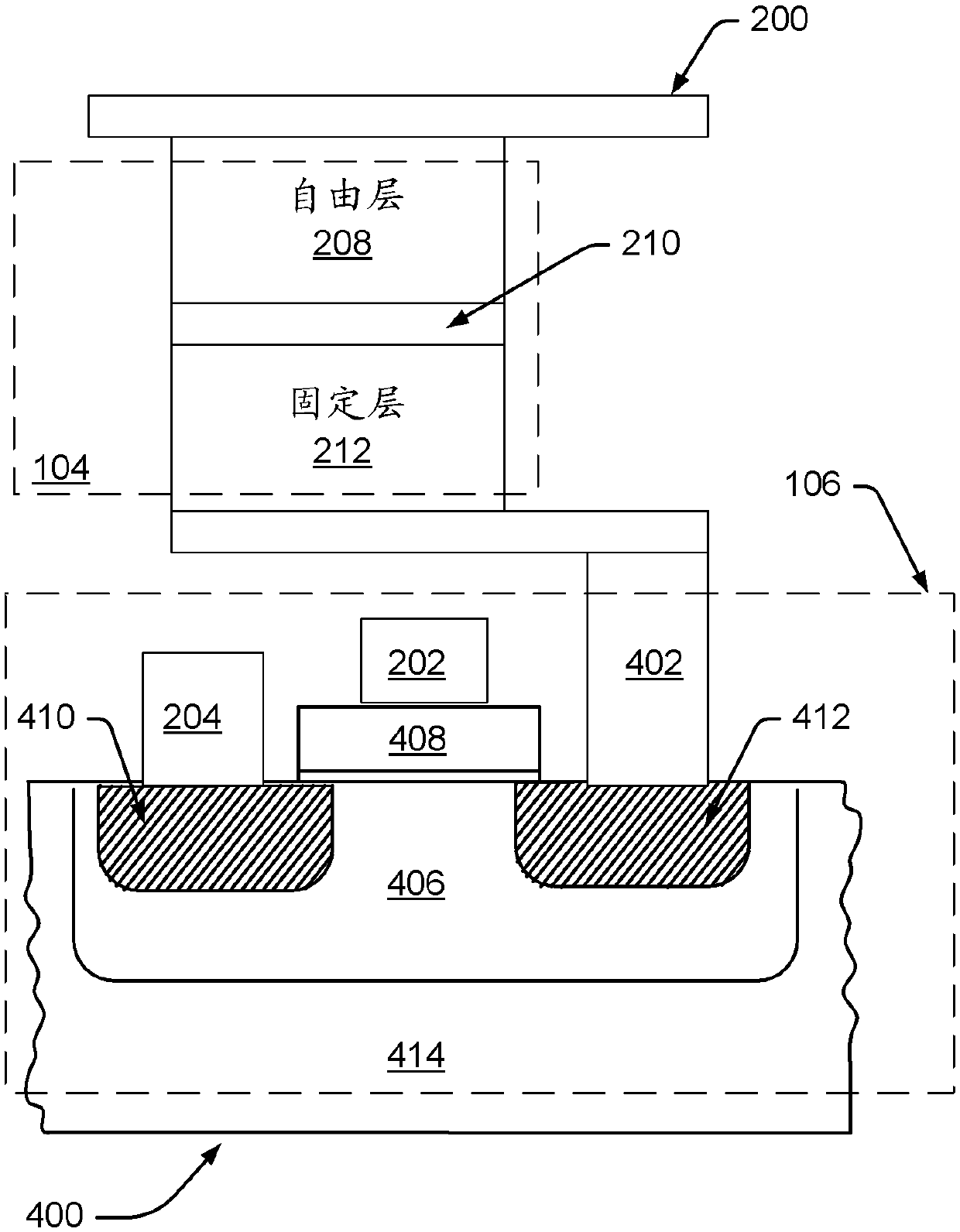

[0014] The present disclosure relates to an STT-MRAM cell that incorporates a PMOS or p-type transistor as an access transistor to control the drive current supplied to the MTJ or magnetic memory element of the STT-MRAM cell. The MTJ switches between two magnetoresistive states based on the drive current provided by the PMOS transistor. In one example, the MTJ requires a higher current level to transition from the first state to the second state than the amount of current required to transition from the first state to the second state.

[0015] At higher current states or transitions, the MTJ operates under sub-optimal conditions due to higher current levels that may cause damage to the MTJ. However, PMOS transistors under higher current conditions are minimally affected by the receptor effect, which depends on the voltage difference between the transistor's source and substrate. Therefore, the PMOS transistor operates at an optimal state or condition dur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More