memory structure

A technology of memory bank and topology structure, applied in the computer field, can solve the problems such as the inability to increase the memory access bandwidth, the reduction of the bandwidth, and the increase of the signal rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

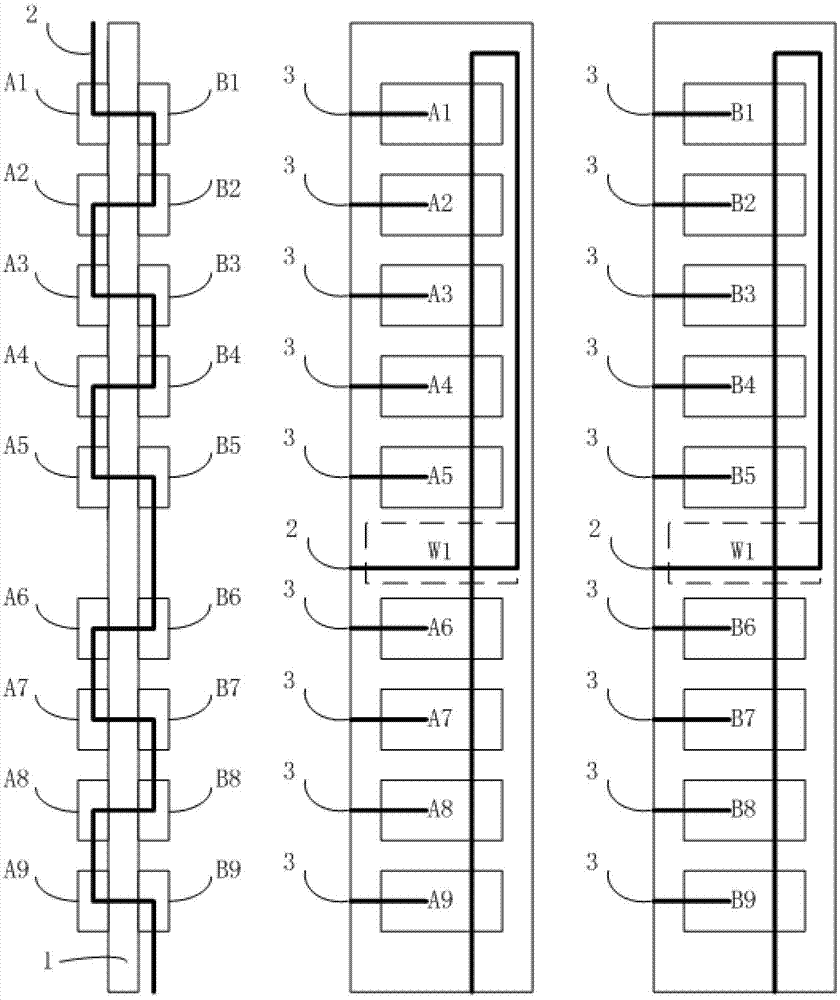

[0035] figure 2 It schematically shows the front arrangement, the back arrangement, and the signal connection relationship of the memory structure according to the embodiment of the present invention.

[0036] Such as figure 2 As shown, nine front storage body units are arranged side by side on the front side of the printed board 1: the first front storage unit A1, the front second storage unit A2, the front third storage unit A3, and the front fourth storage unit A4, the fifth bank unit A5 on the front side, the sixth bank unit A6 on the front side, the seventh bank unit A7 on the front side, the eighth bank unit A8 on the front side, and the ninth bank unit A9 on the front side.

[0037] On the opposite side of the printed board, at positions corresponding to the nine front memory cells, nine reverse memory cells are arranged side by side: the first memory cell unit B1 on the reverse side, the second memory cell unit B2 on the reverse side, and the second memory cell unit...

no. 2 example

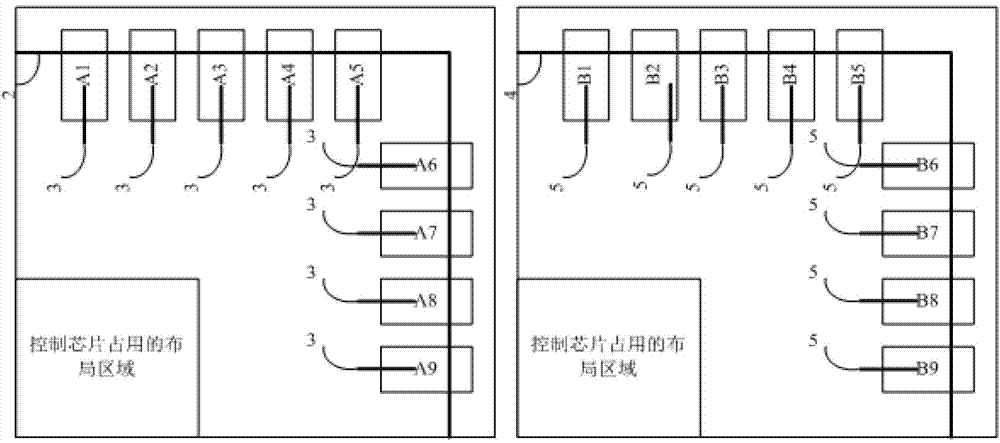

[0047] Preferably, a part of the nine front memory units is arranged in the first front row, and the rest of the nine front memory units are arranged in the second front row, and the arrangement direction of the first front row is the same as that of the front first row. The arrangement direction of the second row of the front side is vertical; and, a part of the nine back memory body units is arranged in the first row of the back side, and the rest of the nine back memory body units are arranged in the second row of the back side, the The arrangement direction of the first row on the reverse side is perpendicular to the arrangement direction of the second row on the reverse side.

[0048] The following will combine image 3 A specific example of such a preferred embodiment will be described.

[0049] image 3 Schematically shows another arrangement of the memory structure according to the embodiment of the present invention; it shows a right-angle turning layout, and its si...

no. 3 example

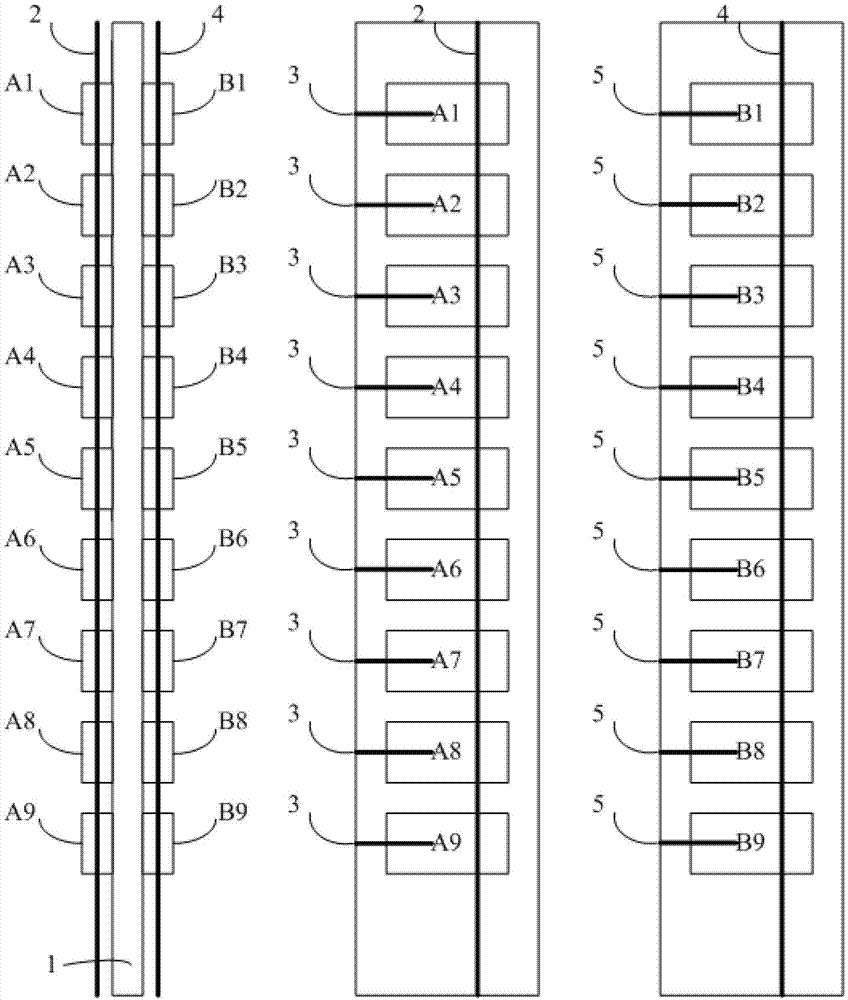

[0059] Preferably, a part of the nine front memory units is arranged in the first front row, and the rest of the nine front memory units are arranged in the second front row, and the arrangement direction of the first front row is the same as that of the front first row. The arrangement direction of the second row of the front side is parallel; and, a part of the nine backside memory cells is arranged in the first row of the backside, and the rest of the nine backside memory body units are arranged in the second row of the backside, and the The arrangement direction of the first row on the opposite side is parallel to the arrangement direction of the second row on the opposite side.

[0060] The following will combine Figure 4 A specific example of such a preferred embodiment will be described. Figure 4 Schematically shows another arrangement of the memory structure according to the embodiment of the present invention; it shows the layout form of the horizontal transition, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More