Array substrate, liquid crystal display panel and driving method

A liquid crystal display panel and array substrate technology, which is applied in the liquid crystal field, can solve the problems of light leakage at the via hole, irregular shape, and reduce the aperture ratio, so as to achieve the effect of uniform appearance, the same opening size, and avoiding horizontal stripes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

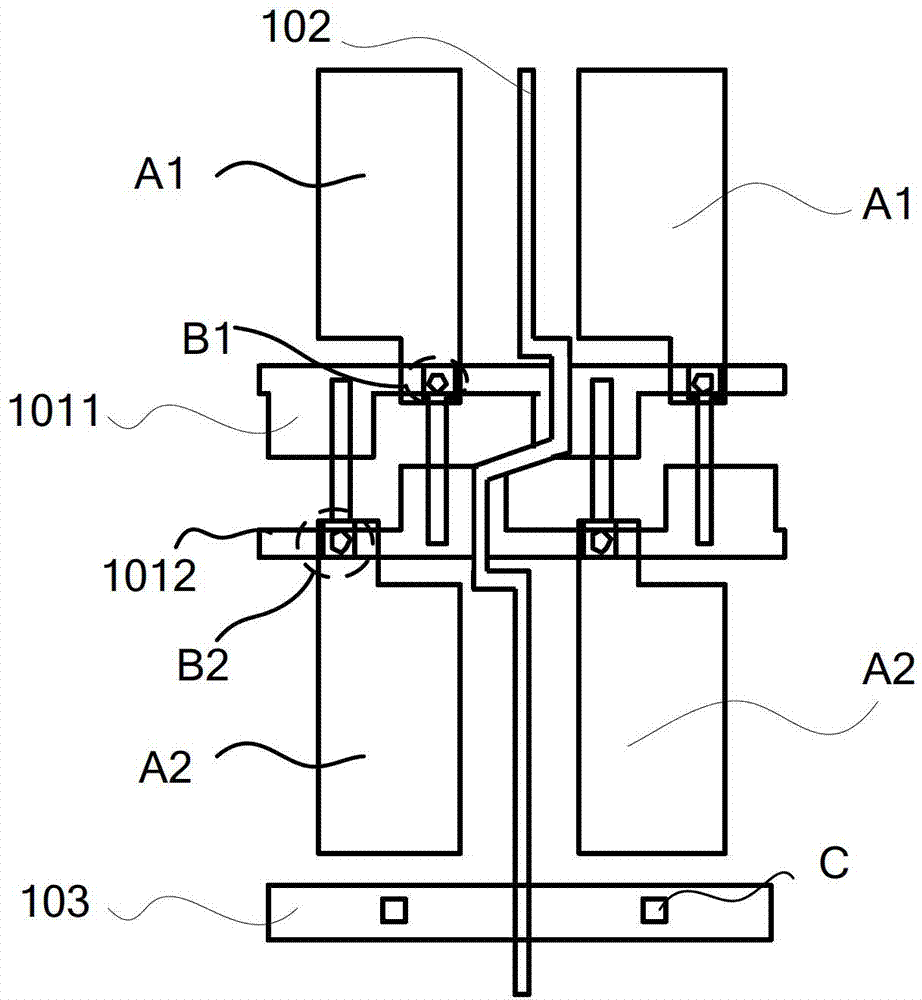

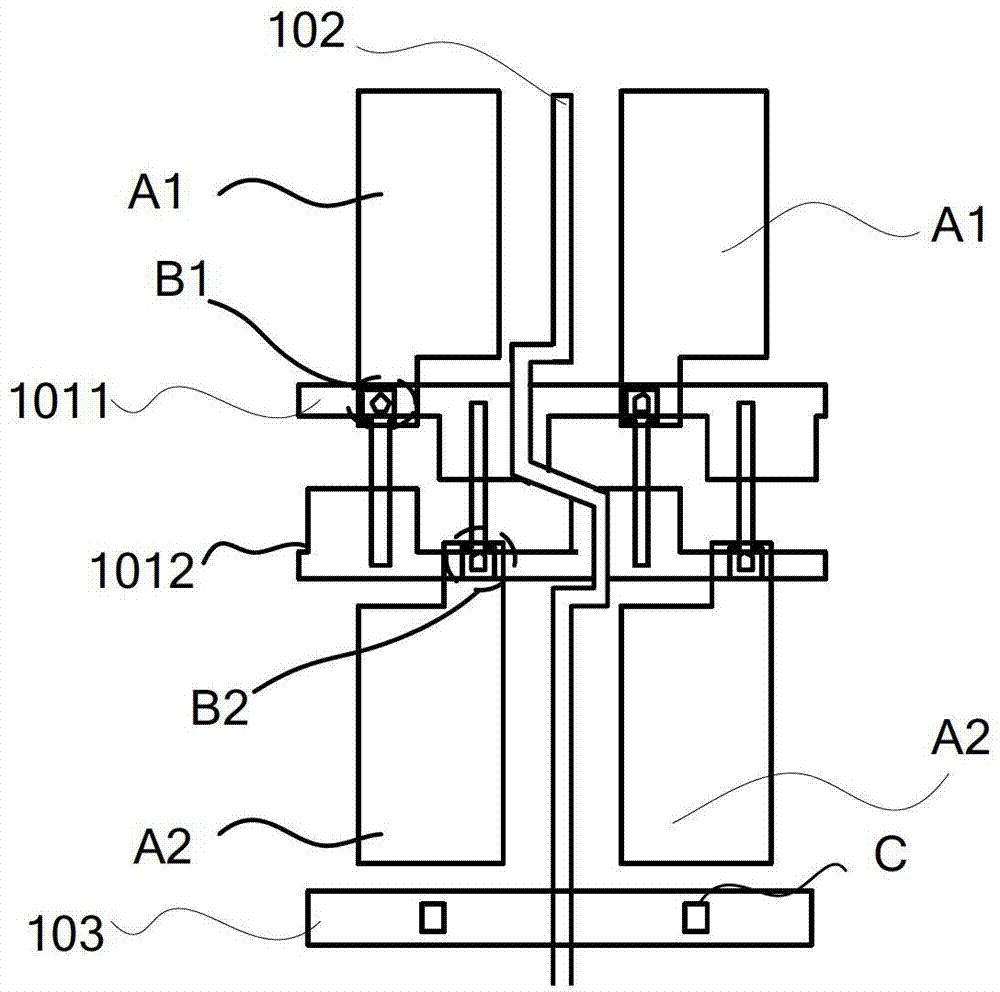

[0021] Embodiments of the present invention provide an array substrate, a liquid crystal display panel and a driving method, which are used to increase the aperture ratio of a pixel unit, avoid horizontal stripes in display caused by different black matrices in adjacent rows, and improve display quality.

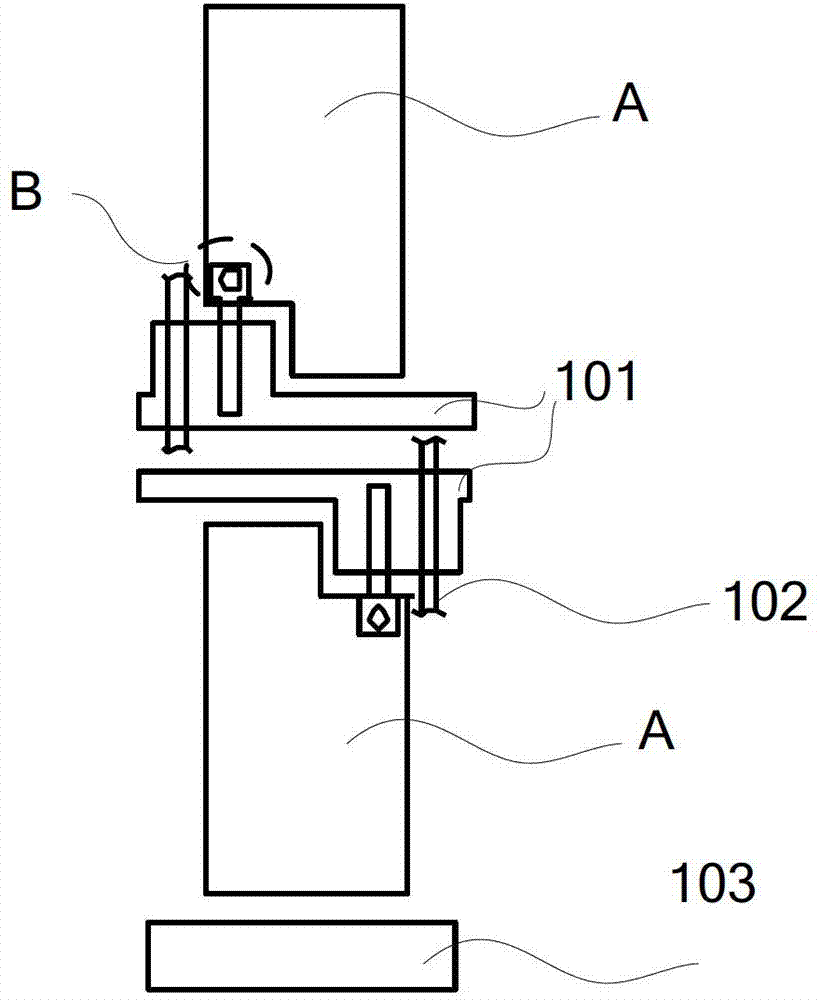

[0022] An array substrate provided by an embodiment of the present invention includes cross-arranged data lines and gate lines, and a pixel unit formed by surrounding the data lines and gate lines. The pixel unit includes a thin film transistor TFT and a pixel electrode. The TFT It includes a gate electrode, a source electrode and a drain electrode, the source electrode is connected to the data line, wherein two adjacent rows of gate lines are located between the driven adjacent two rows of pixel units, and the drain electrode is connected to the pixel unit The connection of the electrodes corresponds to between or on the gate lines of two adjacent rows driving the two adjace...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More