A message buffer management method and device

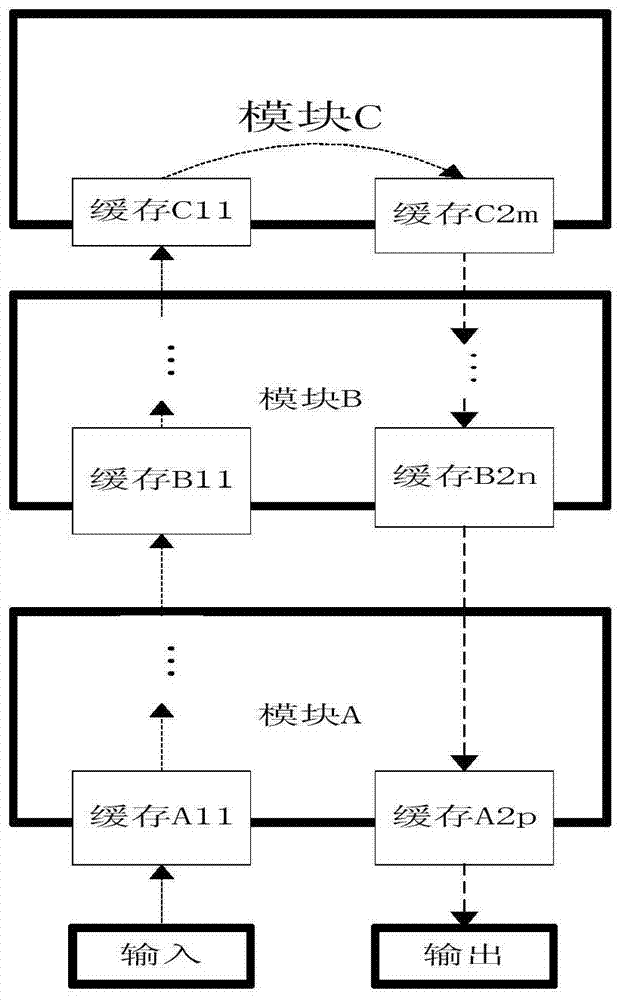

A message cache and management method technology, applied in the field of message cache management methods and devices, can solve problems such as performance bottlenecks, increase usage complexity, increase user memory consumption, etc., to avoid backup, improve packet throughput performance, avoid The effect of data movement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

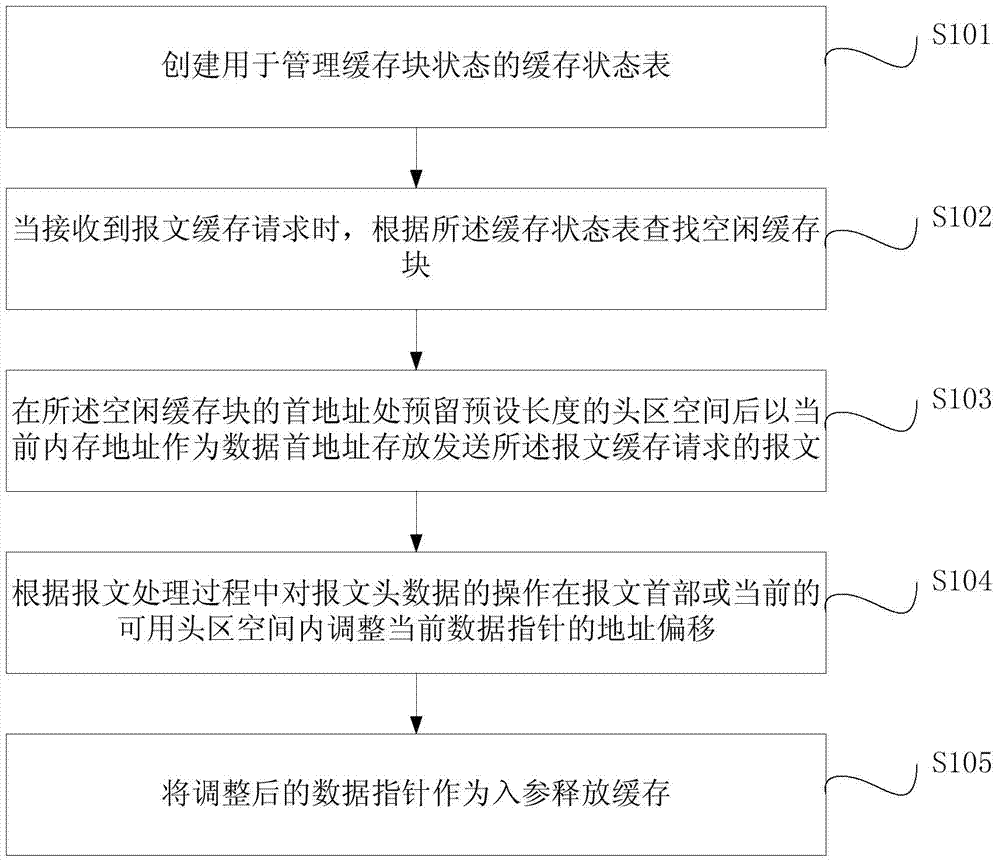

[0037] Embodiment 1 of the present invention provides a message cache management method, such as image 3 shown, including the following steps:

[0038] S101: Create a cache status table for managing cache block status;

[0039] S102: When a packet cache request is received, search for a free cache block according to the cache state table;

[0040] S103: After reserving a header space of a preset length at the first address of the free cache block, the current memory address is used as the first address of the data to store the message for sending the message cache request;

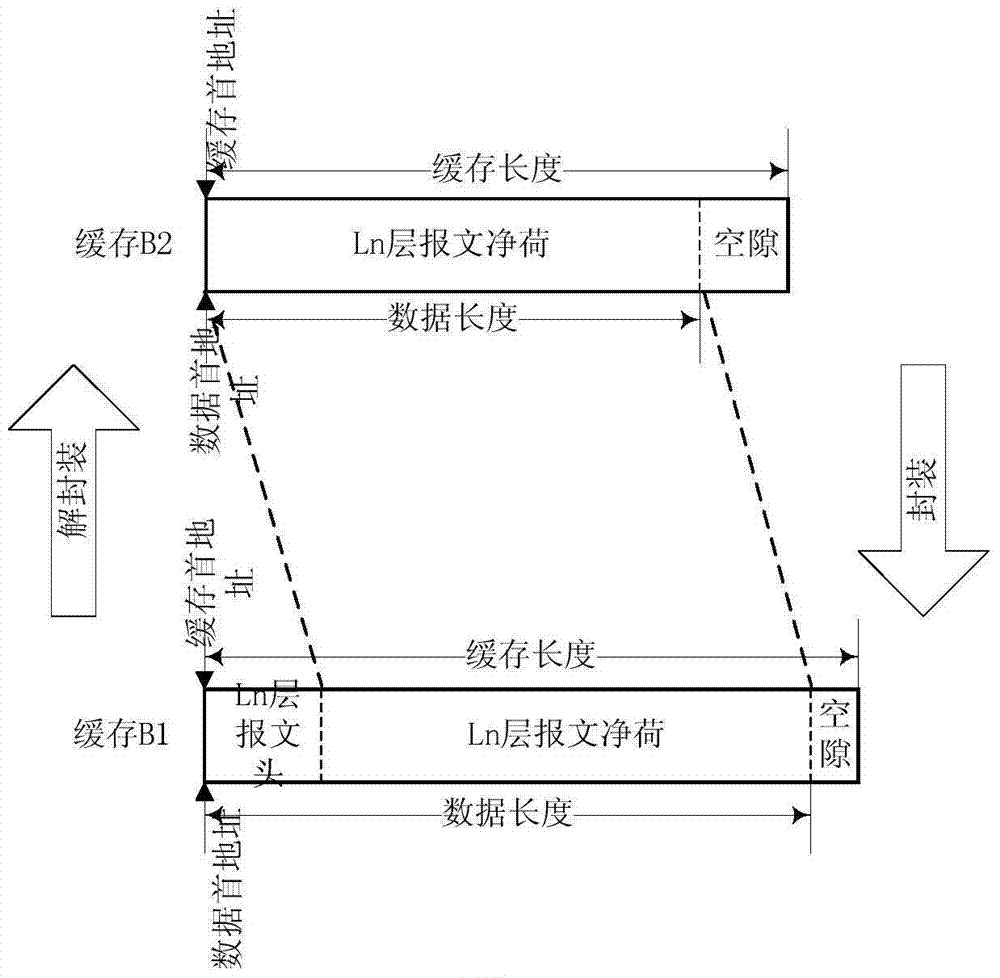

[0041] S104: Adjust the address offset of the current data pointer in the message header or the current available header space according to the operation of the message header data during message processing; where the available header space actually refers to the first address of the cache block The space between the head address of the data and the first address of the data, as the data is encapsulated...

Embodiment 2

[0072] Embodiment 2 of the present invention describes a message buffer management method of the present invention through the specific implementation steps of the message sending and receiving, processing and transmission process, as shown in Figure 8 shown, including:

[0073] Step 1: By analyzing the functions of each module of the whole system, pre-calculate the sum of the maximum stripped header lengths (assumed to be L1 bytes) in the Ingress direction of the messages flowing through the system, and the maximum encapsulation in the Ingress direction The sum of the length of the message header (assumed to be L2 bytes); in order to avoid data movement, it is necessary to reserve header space for the change of the data header length. Here, it is assumed that the ingress message is at the head of the cache when it is first stored in the cache To reserve the header space of PreHdrRoom bytes, the calculation rules of PreHdrRoom are as follows:

[0074] If L2<=L1, then the val...

Embodiment 3

[0082] Embodiment 3 of the present invention provides a packet cache management device, such as Figure 9 As shown, the device includes:

[0083] The cache state table creation module 1 is used to create a cache state table for managing the cache block state;

[0084] A search module 2, configured to search for a free cache block according to the cache state table when a message cache request is received;

[0085] The storage module 3 is configured to reserve a header space of a preset length at the first address of the free cache block and use the current memory address as the first address of the data to store the message sending the message cache request;

[0086] The address offset module 4 is used to adjust the address offset of the current data pointer in the message header or the current available header space according to the operation of the message header data in the message processing process;

[0087] The cache release module 5 is configured to use the adjusted d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More