A pulse clock generation logic with built-in level shifter and programmable rising edge and pulse width

A technology of pulse clock and programming pulse, applied in the field of pulse clock and pulse clock generation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

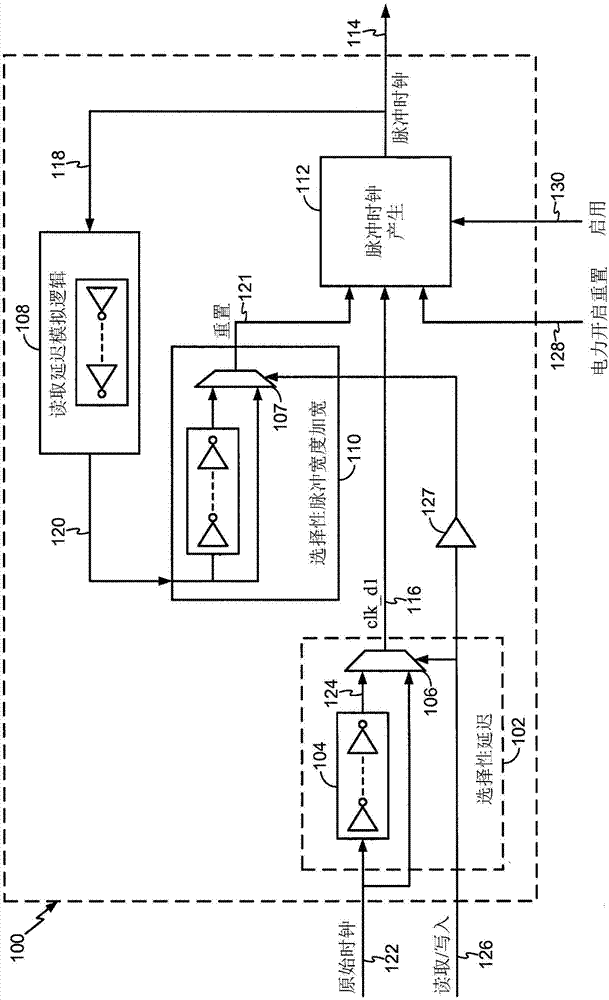

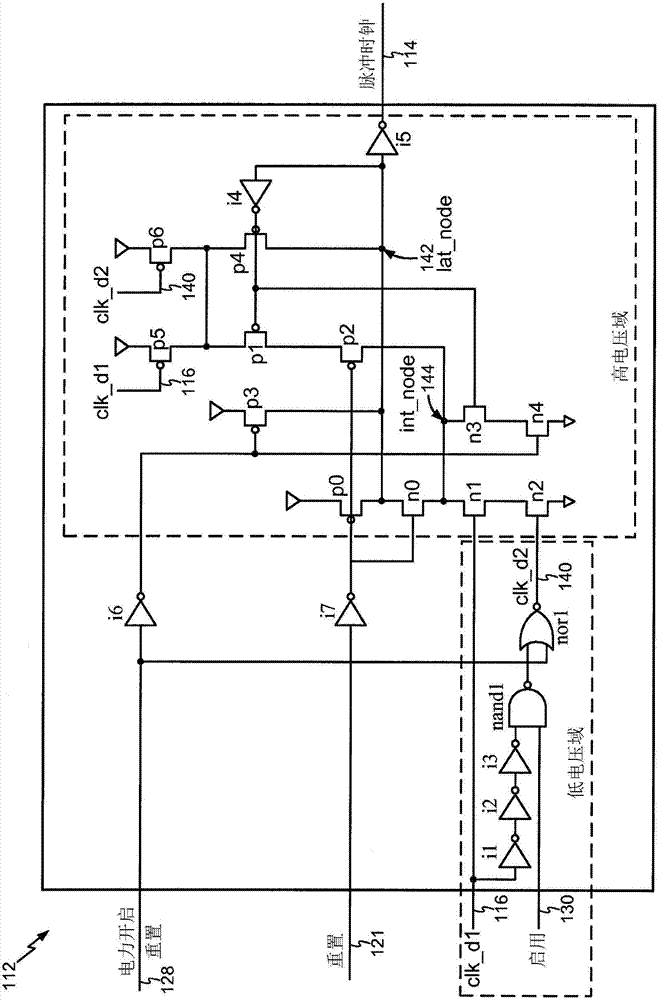

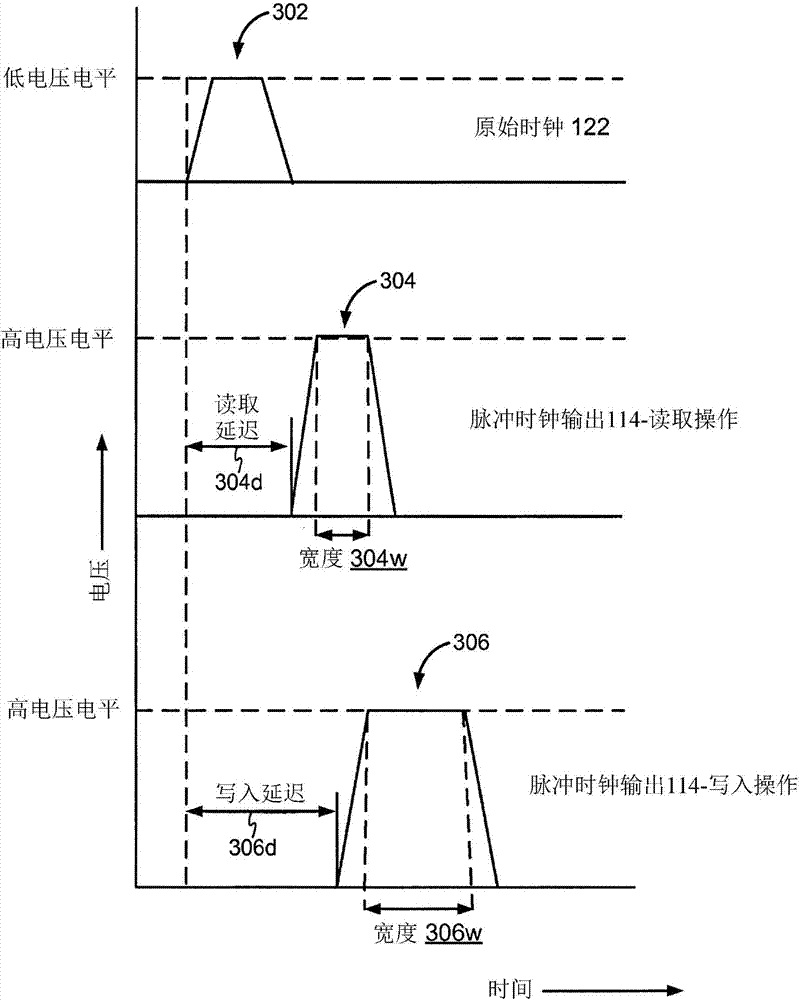

[0019] Several aspects of the invention are disclosed in the following description and related drawings directed to specific embodiments of the invention. Alternative embodiments may be devised without departing from the scope of the present invention. Additionally, well-known elements of the invention will not be described in detail or will be omitted so as not to obscure the relevant details of the invention.

[0020] The word "exemplary" is used herein to mean "serving as an example, instance, or illustration." Any embodiment described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other embodiments. Likewise, the term "embodiments of the invention" does not require that all embodiments of the invention include the discussed feature, advantage or mode of operation.

[0021] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of embodiments of the invention. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More