Digital delay implementation method for integrated circuit and circuit

A technology of digital delay and integrated circuit, which is applied in the field of digital delay realization method and circuit, can solve the problems of delay time limitation, etc., and achieve the effects of reducing the number of adders, shortening logic delay, and reducing logic area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

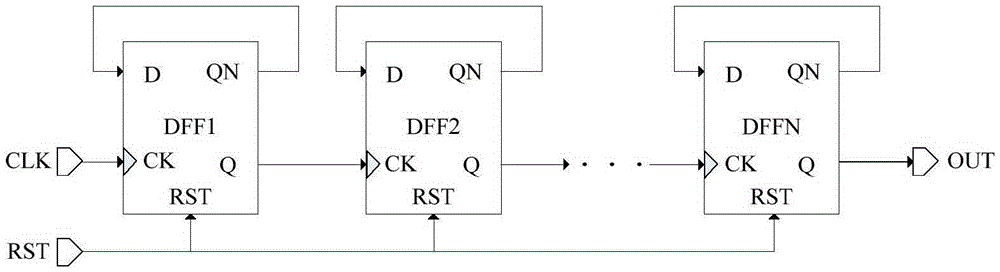

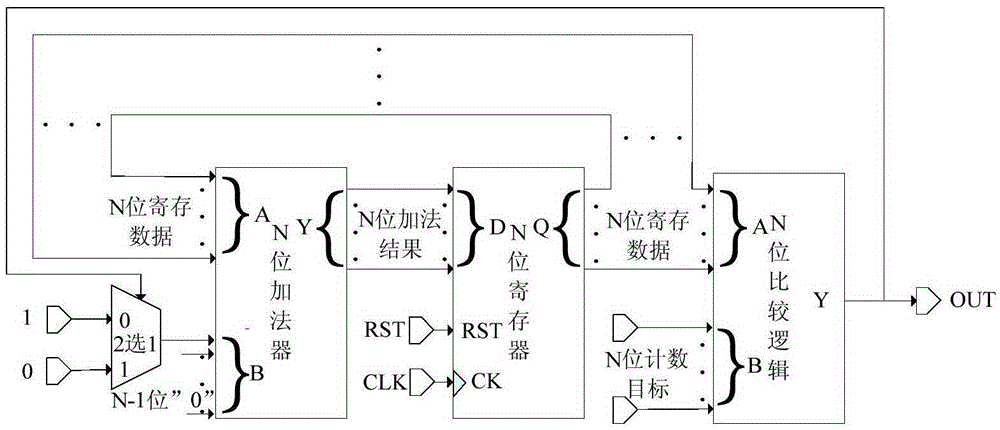

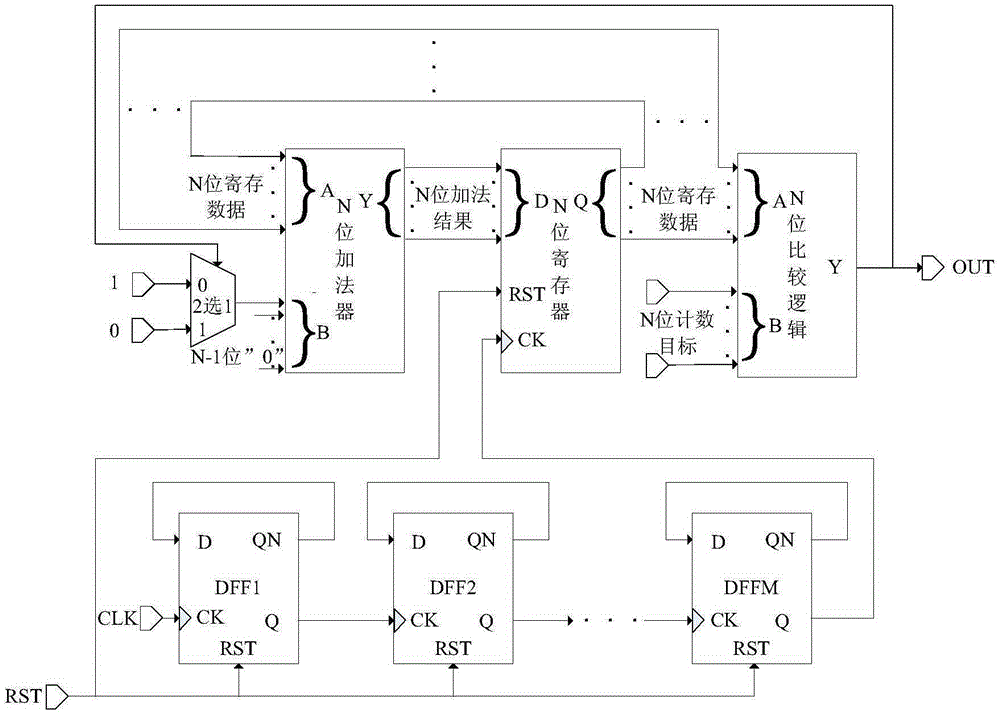

[0030] Embodiments of the present invention will be described in further detail below in conjunction with the accompanying drawings.

[0031] In order to complete the delay function, the digital circuit must be based on the clock. Under the fast clock, simply using the counting method to complete a long time delay will produce a large counting target, which requires combinational logic such as a multi-bit adder. Using frequency division to increase the clock period is an effective way to reduce the number of combinational logic bits such as adders. In order to ensure that the delay time is not limited by the frequency division of the clock, the design idea of the present invention is to use clocks with different frequency division numbers instead of a frequency division clock with a single frequency as required.

[0032] A digital delay implementation method for integrated circuits, comprising the following steps:

[0033] Step 1) According to the delay time T delay with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More