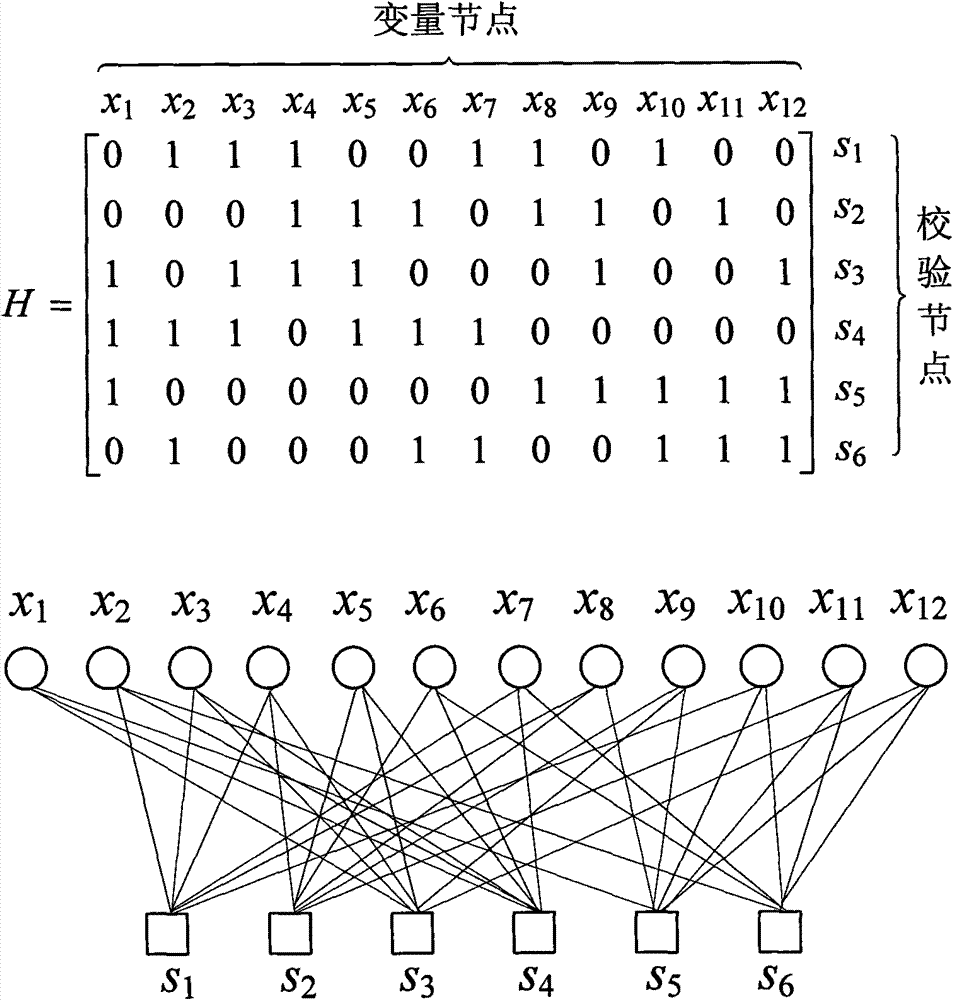

Structured LDPC code decoding method and device for system on explicit memory chip

An LDPC code and memory chip technology, which is applied in error detection coding using multi-bit parity bits, in-line telephone systems, and error correction/detection using block codes, which can solve the problem of large area overhead, complex implementation, and increased Problems such as area overhead of decoding device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described in detail below in conjunction with specific embodiments and accompanying drawings.

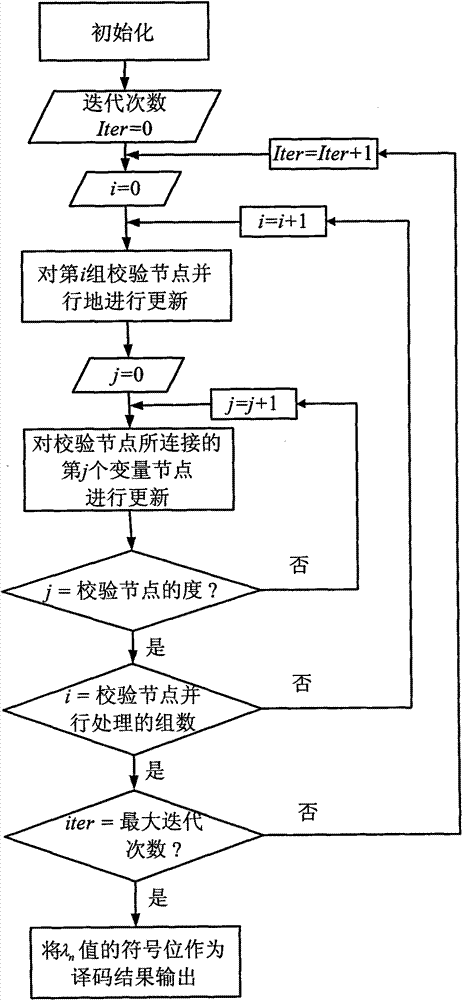

[0044] Such as figure 2 Shown is a schematic diagram of the decoding process of the present invention.

[0045] (1) Initialization of decoding: the initialization process includes storing the received log-likelihood ratio LLR (log-likelihood ratio) into "RAM V" according to a specific storage method, and initializing the value of "RAM C" as 0. Set a maximum number of iterations in advance.

[0046] For n=1, 2, ..., N,

[0047] λ n = λ n ( 0 ) , Λ mn ( 0 ) = 0 , m∈M(n) (Equation 1)

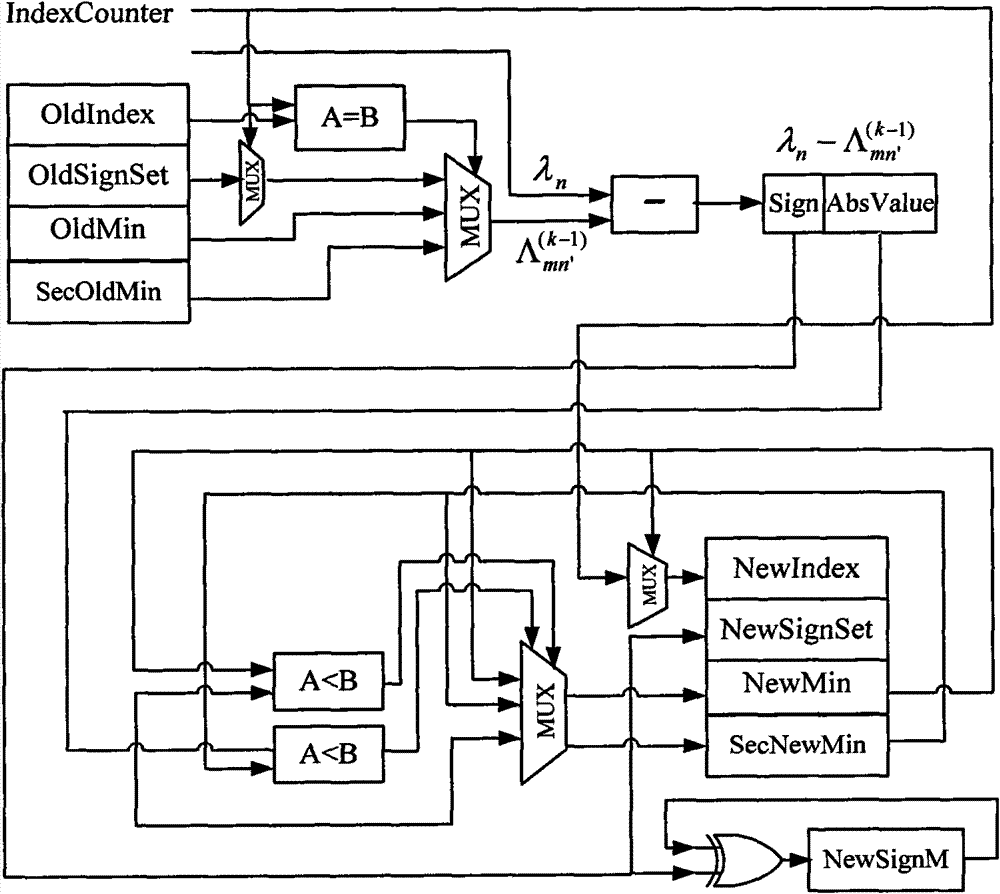

[0048] (2) Iterative process: start the iteration number counter I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More