Current bias circuit

A technology of current bias and current path, applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve the problems of consuming circuit area, increasing cost, and large resistance, and achieve resistance area saving, cost reduction, and resistance saving area effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

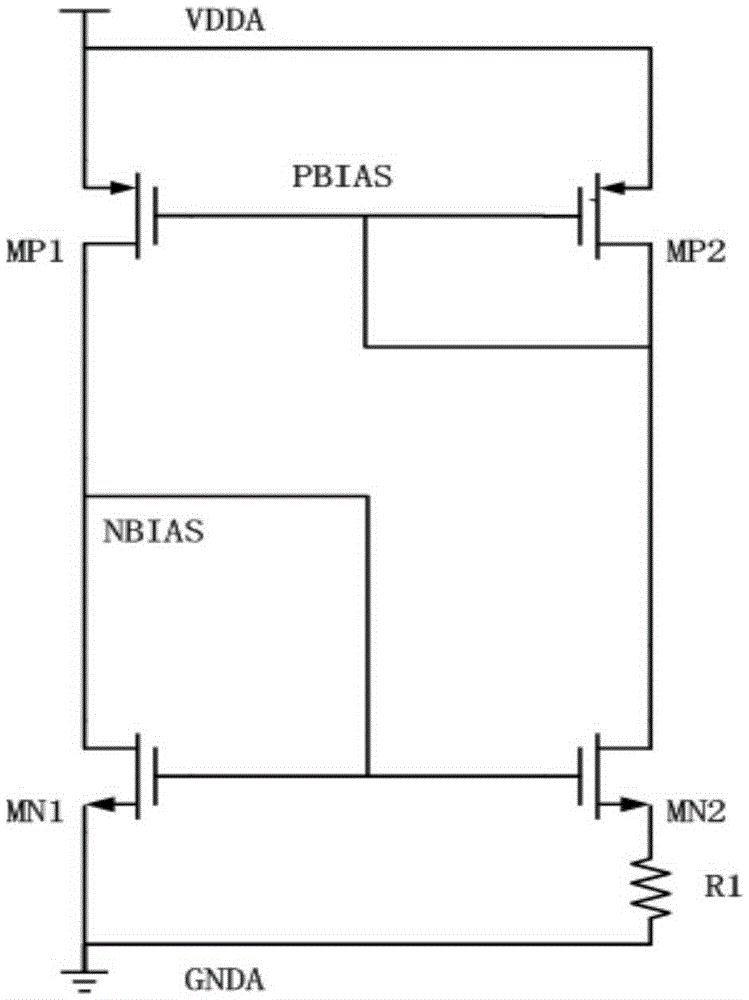

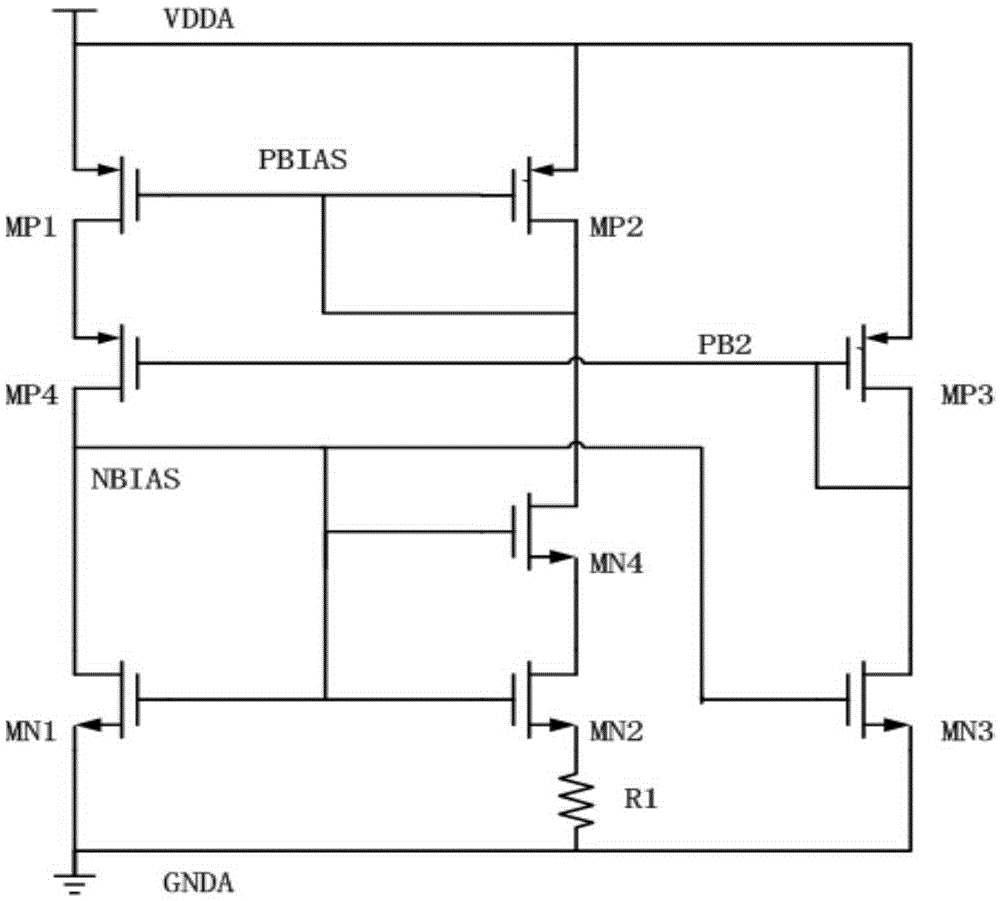

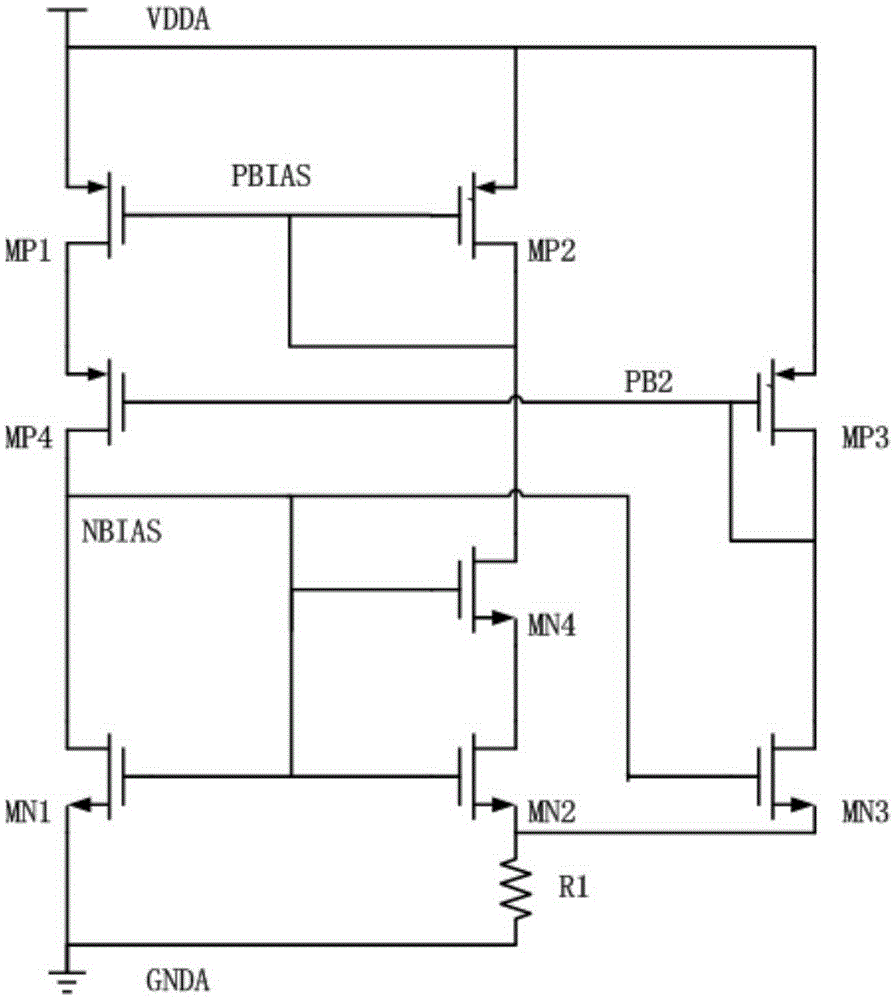

[0028] Such as image 3 Shown is the current bias circuit diagram of the embodiment of the present invention. The current bias circuit in the embodiment of the present invention includes: a first current mirror, a second current mirror and a bias path.

[0029] The first current mirror includes a first PMOS transistor MP1 and a second PMOS transistor MP2 that are mirror images of each other.

[0030] The second current mirror includes a first NMOS transistor MN1 and a second NMOS transistor MN2 that are mirror images of each other.

[0031] The drain current of the first PMOS transistor MP1 is connected to the drain current of the first NMOS transistor MN1 through the third PMOS transistor MP4 to form a first current path.

[0032] The drain current of the second PMOS transistor MP2 is connected to the drain current of the second NMOS transistor MN2 through the third NMOS transistor MN4 to form a second current path.

[0033]The source of the first NMOS transistor MN1 is gr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More