Method for forming grid

A gate and layer-forming technology, applied in the field of gate formation, to achieve the effect of reducing bridging problems, smooth surface, and highly consistent

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

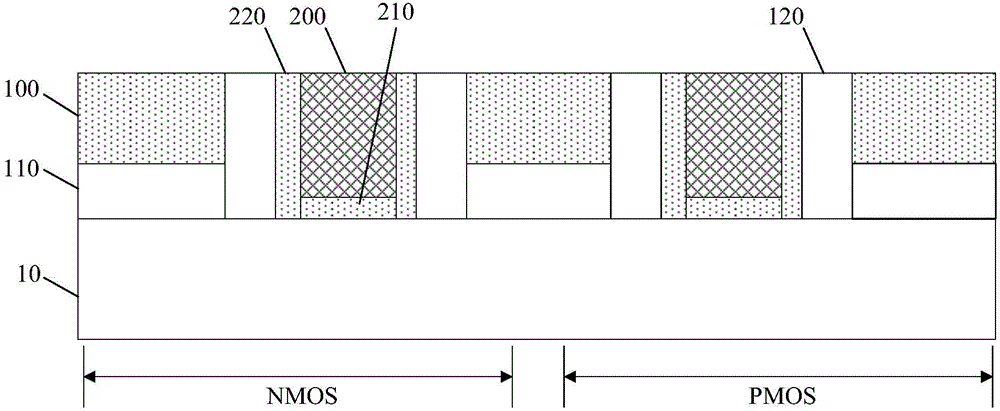

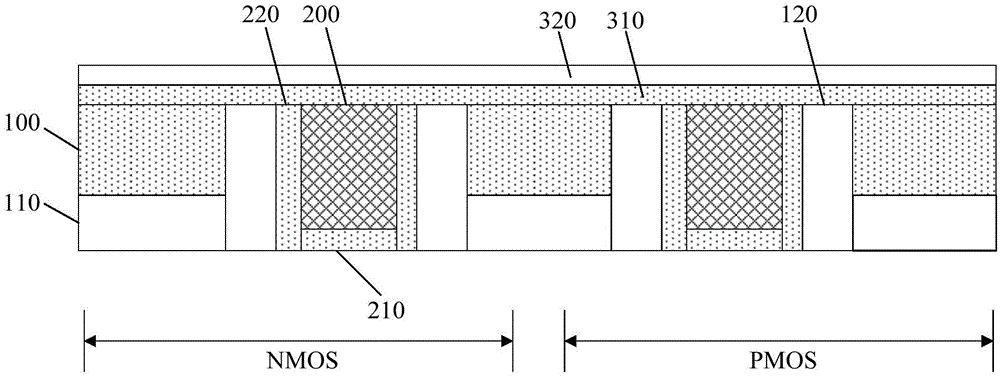

[0041] In order to solve the problem of easy bridging between transistors and other devices, each step of the gate-last process is analyzed. When chemical mechanical polishing (CMP) is used to remove unnecessary parts of the metal layer, due to the (being) polished between different materials There can be large differences in the rate (RR), which can lead to height differences between the different materials after CMP, causing bridging problems.

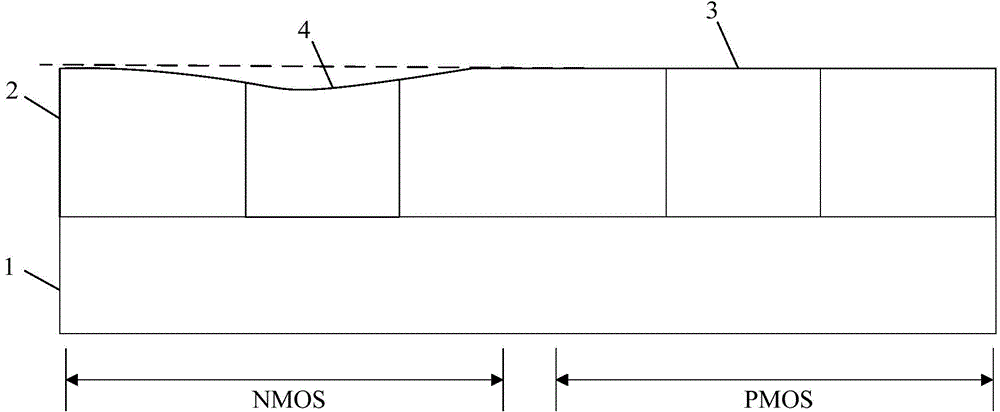

[0042] Specifically, refer to figure 1 , the manufacture of CMOS devices requires the gates of PMOS and NMOS devices to be formed separately. Taking the metal gate 3 of the PMOS device formed first as an example, when the metal gate 3 of the PMOS device is formed by chemical mechanical polishing, there is still a dummy gate 4 to be removed in the NMOS device at this time.

[0043] Although in general, the chemical mechanical polishing of the metal gate 3 of the PMOS device stops when the interlayer dielectric layer 2 is detected, th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More