Method and device for continuously adjusting data transmission clock

A data transmission and adjustment method technology, applied in the field of data transmission, can solve the problems of poor data reception reliability and low data transmission rate, and achieve the effects of improving stability, reducing jitter, and increasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] figure 1 It is a schematic flow chart of the method for continuously adjusting the data transmission clock described in Embodiment 1 of the present invention, as shown in figure 1 As shown, the method may include the following steps:

[0028] Step S101, receiving the data output by the front-end module at a certain rate and storing it in the data buffer unit;

[0029] Step S102, monitoring the current buffering state of the data buffering unit, and determining an error signal according to the current buffering state of the data buffering unit if the current buffering state of the data buffering unit satisfies a preset buffering threshold;

[0030] Step S103, performing second-order filtering on the error signal to generate a filtered clock compensation signal;

[0031] Step S104, determining a new clock frequency according to the clock compensation signal and the preset initial frequency word;

[0032] Step S105, read the data in the data buffer unit according to the...

Embodiment 2

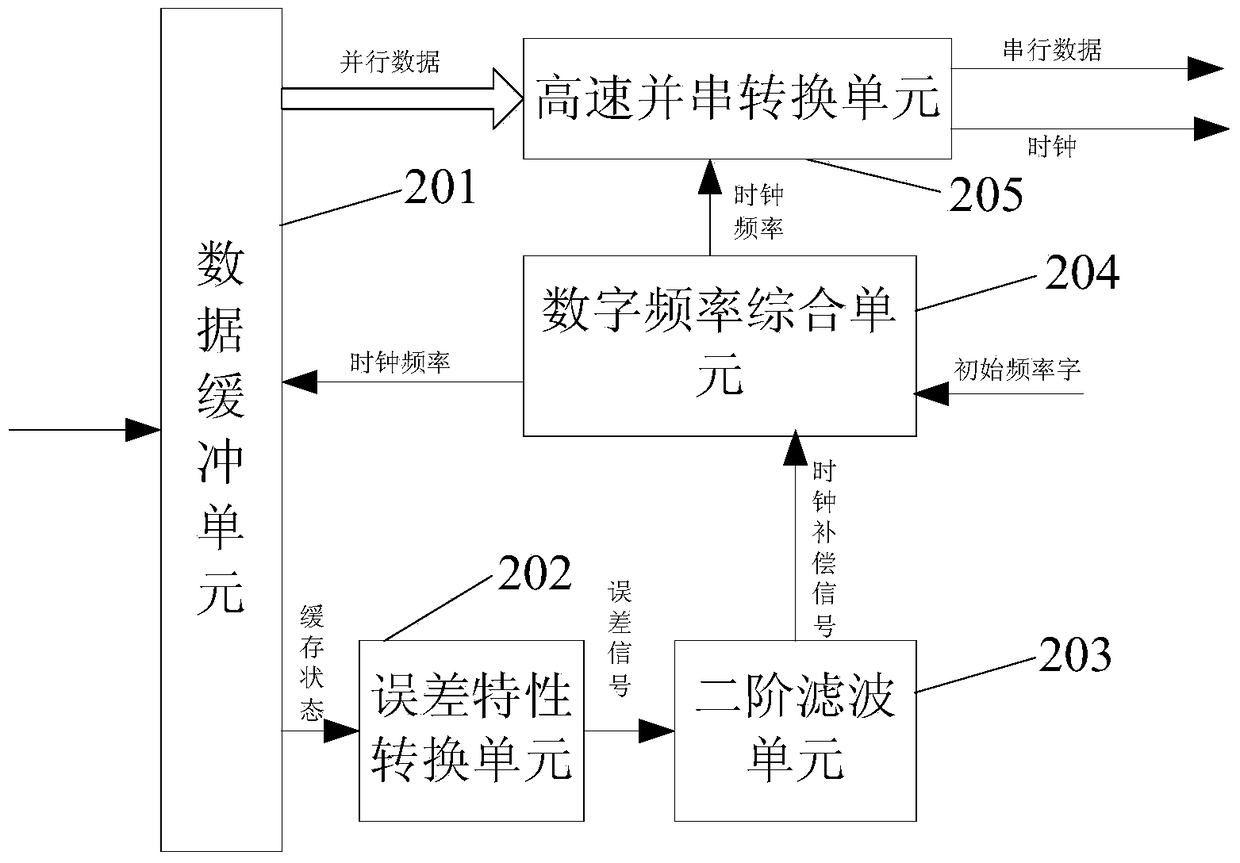

[0041] figure 2 It is a structural block diagram of the data transmission clock continuous adjustment device described in the second embodiment of the present invention, as shown in figure 2 As shown, the data transmission clock continuous adjustment device described in this embodiment may include:

[0042] The data buffer unit 201 is used to receive and store the data output by the previous module at a certain rate;

[0043] An error characteristic conversion unit 202, configured to monitor the current buffer state of the data buffer unit, and determine an error signal according to the current buffer state of the data buffer unit if the current buffer state of the data buffer unit satisfies a preset buffer threshold ;

[0044] A second-order filtering unit 203, configured to perform second-order filtering on the error signal to generate a filtered clock compensation signal;

[0045] A digital frequency synthesis unit 204, configured to determine a new clock frequency acc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More