Self-aligned gate contact structure

A gate and contact technology, applied in the field of self-aligned gate contact structure and its formation, can solve the problem of not preventing short circuit of gate contact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

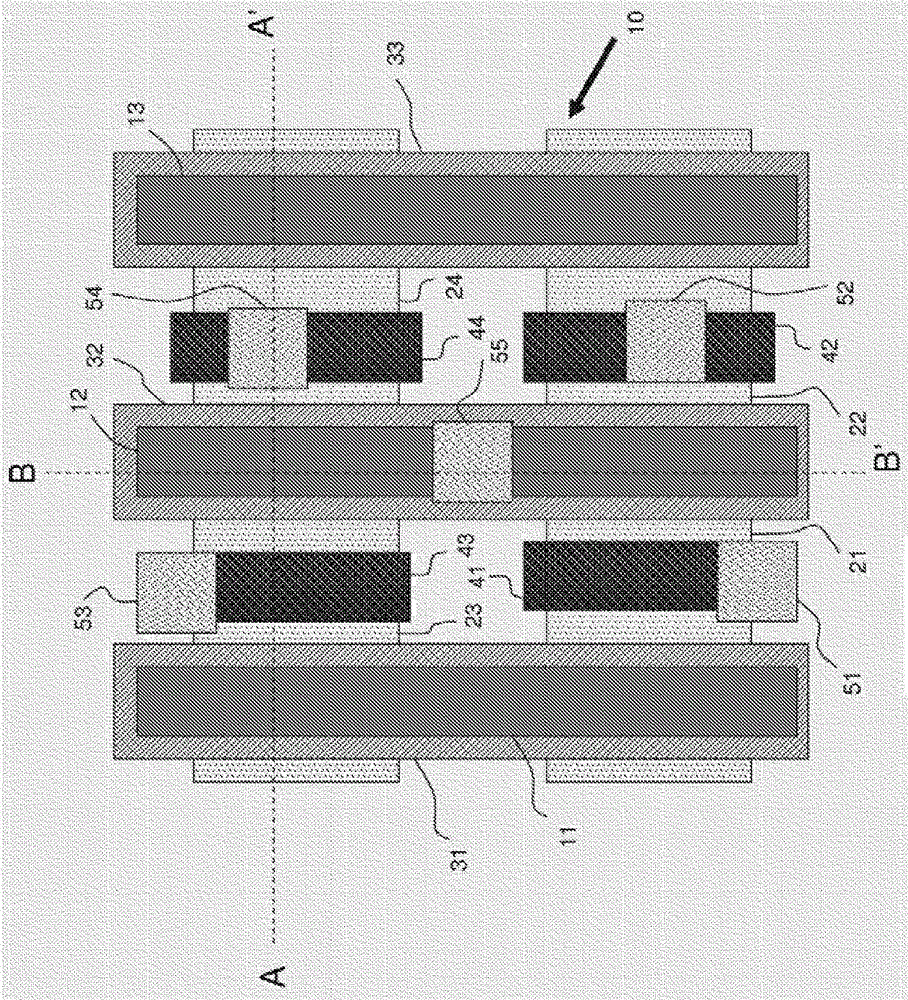

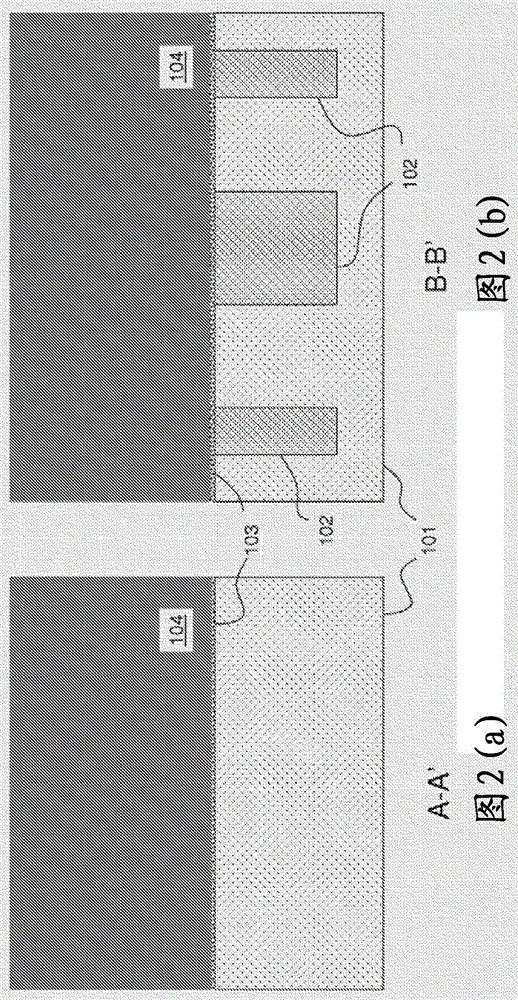

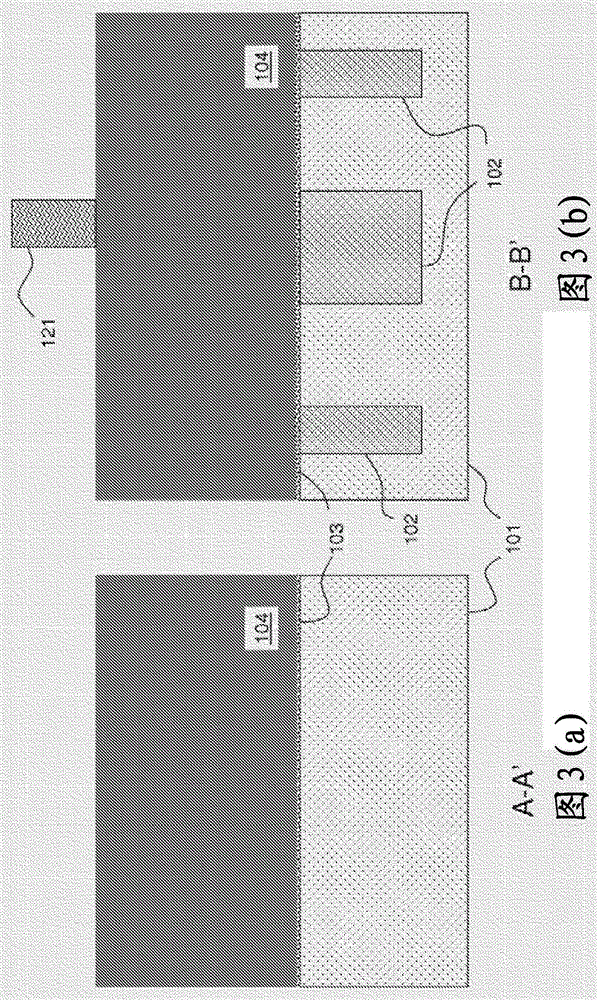

[0024] In the following detailed description, numerous specific details are set forth in order to provide a thorough understanding of various embodiments of the invention. However, it is understood that embodiments of the invention may be practiced without these specific details.

[0025] In order not to obscure the essence of the present invention and / or the expression of the embodiments, in the following detailed description, for expression and / or for illustration, some processing steps and / or operations known in the art may be combined together, and in some instances may not be described in detail. In other instances, some process steps and / or operations known in the art may not be described at all. Additionally, some well-known device processing techniques may not be described in detail, and in some instances other published articles, patents, and / or published patent applications may be referred to by reference so as not to obscure the essence and / or embodiments of the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More