High-speed dynamic loading device and method of multiple FPGA based on Ethernet

A dynamic loading, Ethernet technology, applied in the direction of program control device, program loading/starting, program control design, etc., can solve the problems of long programming time, long programming time, limitation of use flexibility, etc., to improve work efficiency , Improve system flexibility and save programming time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] All features disclosed in this specification, or steps in all methods or processes disclosed, may be combined in any manner, except for mutually exclusive features and / or steps.

[0021] Any feature disclosed in this specification, unless specifically stated, can be replaced by other alternative features that are equivalent or have similar purposes. That is, unless expressly stated otherwise, each feature is one example only of a series of equivalent or similar features.

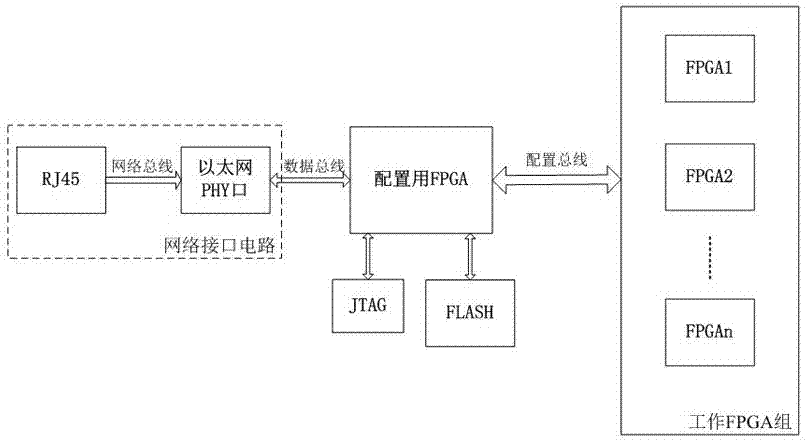

[0022] Such as figure 1 As shown, the device of the present invention includes a network interface circuit and an FPGA for configuration; wherein,

[0023] The network interface circuit has a signal connection with the FPGA for configuration; the FPGA for configuration is connected with each FPGA for work.

[0024] In a specific embodiment, the network interface circuit includes an RJ45 network connector and an Ethernet PHY port, the RJ45 network connector is connected to the Ethernet PHY port throu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More