A unit-line asymmetric memory cell based on finfet device

A storage unit, unit line technology, applied in information storage, static memory, digital memory information and other directions, can solve the problems of small data value, small noise tolerance, large delay, etc., to reduce dynamic power loss and improve Noise margin, effect of reducing circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

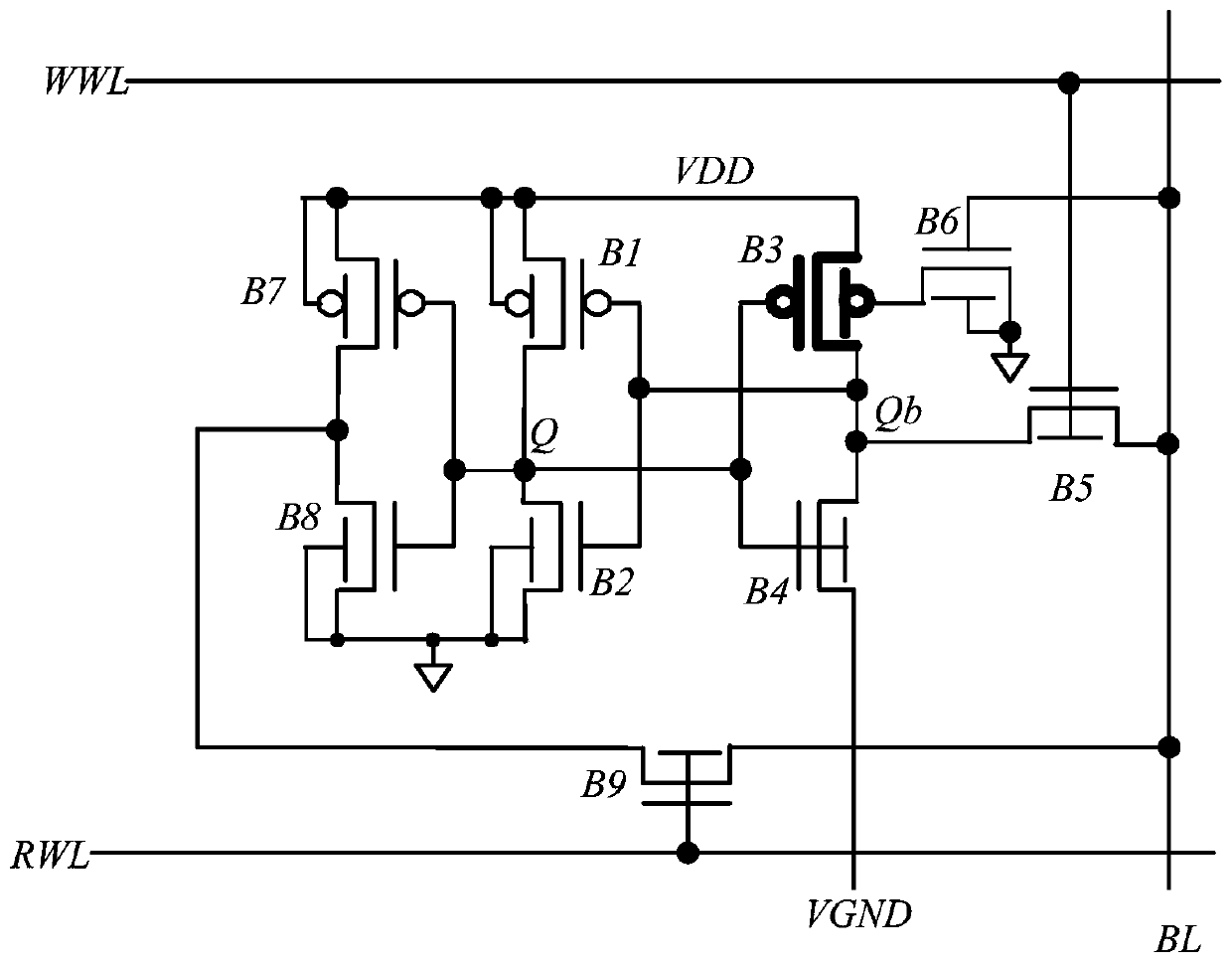

[0016] Embodiment one: if figure 2 As shown, a unit line asymmetric memory cell based on a FinFET device includes a bit line BL, a write word line WWL, a read word line RWL, a first FinFET tube B1, a second FinFET tube B2, a third FinFET tube B3, a fourth FinFET tube FinFET tube B4, fifth FinFET tube B5, sixth FinFET tube B6, seventh FinFET tube B7, eighth FinFET tube B8, and ninth FinFET tube B9; the first FinFET tube B1 and the seventh FinFET tube B7 are respectively low-threshold The P-type FinFET tubes, the second FinFET tube B2, the fourth FinFET tube B4, the fifth FinFET tube B5, the sixth FinFET tube B6, the eighth FinFET tube B8, and the ninth FinFET tube B9 are N-type FinFET tubes with low thresholds, The third FinFET B3 is a high-threshold P-type FinFET; the source of the first FinFET B1, the back gate of the first FinFET B1, the source of the third FinFET B3, the source of the seventh FinFET B7 and The back gate of the seventh FinFET tube B7 is connected and its c...

Embodiment 2

[0017] Embodiment two: if figure 2 As shown, a unit line asymmetric memory cell based on a FinFET device includes a bit line BL, a write word line WWL, a read word line RWL, a first FinFET tube B1, a second FinFET tube B2, a third FinFET tube B3, a fourth FinFET tube FinFET tube B4, fifth FinFET tube B5, sixth FinFET tube B6, seventh FinFET tube B7, eighth FinFET tube B8, and ninth FinFET tube B9; the first FinFET tube B1 and the seventh FinFET tube B7 are respectively low-threshold The P-type FinFET tubes, the second FinFET tube B2, the fourth FinFET tube B4, the fifth FinFET tube B5, the sixth FinFET tube B6, the eighth FinFET tube B8, and the ninth FinFET tube B9 are N-type FinFET tubes with low thresholds, The third FinFET B3 is a high-threshold P-type FinFET; the source of the first FinFET B1, the back gate of the first FinFET B1, the source of the third FinFET B3, the source of the seventh FinFET B7 and The back gate of the seventh FinFET tube B7 is connected and its c...

Embodiment 3

[0019] Embodiment three: as figure 2 As shown, a unit line asymmetric memory cell based on a FinFET device includes a bit line BL, a write word line WWL, a read word line RWL, a first FinFET tube B1, a second FinFET tube B2, a third FinFET tube B3, a fourth FinFET tube FinFET tube B4, fifth FinFET tube B5, sixth FinFET tube B6, seventh FinFET tube B7, eighth FinFET tube B8, and ninth FinFET tube B9; the first FinFET tube B1 and the seventh FinFET tube B7 are respectively low-threshold The P-type FinFET tubes, the second FinFET tube B2, the fourth FinFET tube B4, the fifth FinFET tube B5, the sixth FinFET tube B6, the eighth FinFET tube B8, and the ninth FinFET tube B9 are N-type FinFET tubes with low thresholds, The third FinFET B3 is a high-threshold P-type FinFET; the source of the first FinFET B1, the back gate of the first FinFET B1, the source of the third FinFET B3, the source of the seventh FinFET B7 and The back gate of the seventh FinFET tube B7 is connected and its...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More