Patents

Literature

34 results about "Power–delay product" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital electronics, the power–delay product (PDP) is a figure of merit correlated with the energy efficiency of a logic gate or logic family. Also known as switching energy, it is the product of power consumption P (averaged over a switching event) times the input–output delay or duration of the switching event D. It has the dimension of energy and measures the energy consumed per switching event.

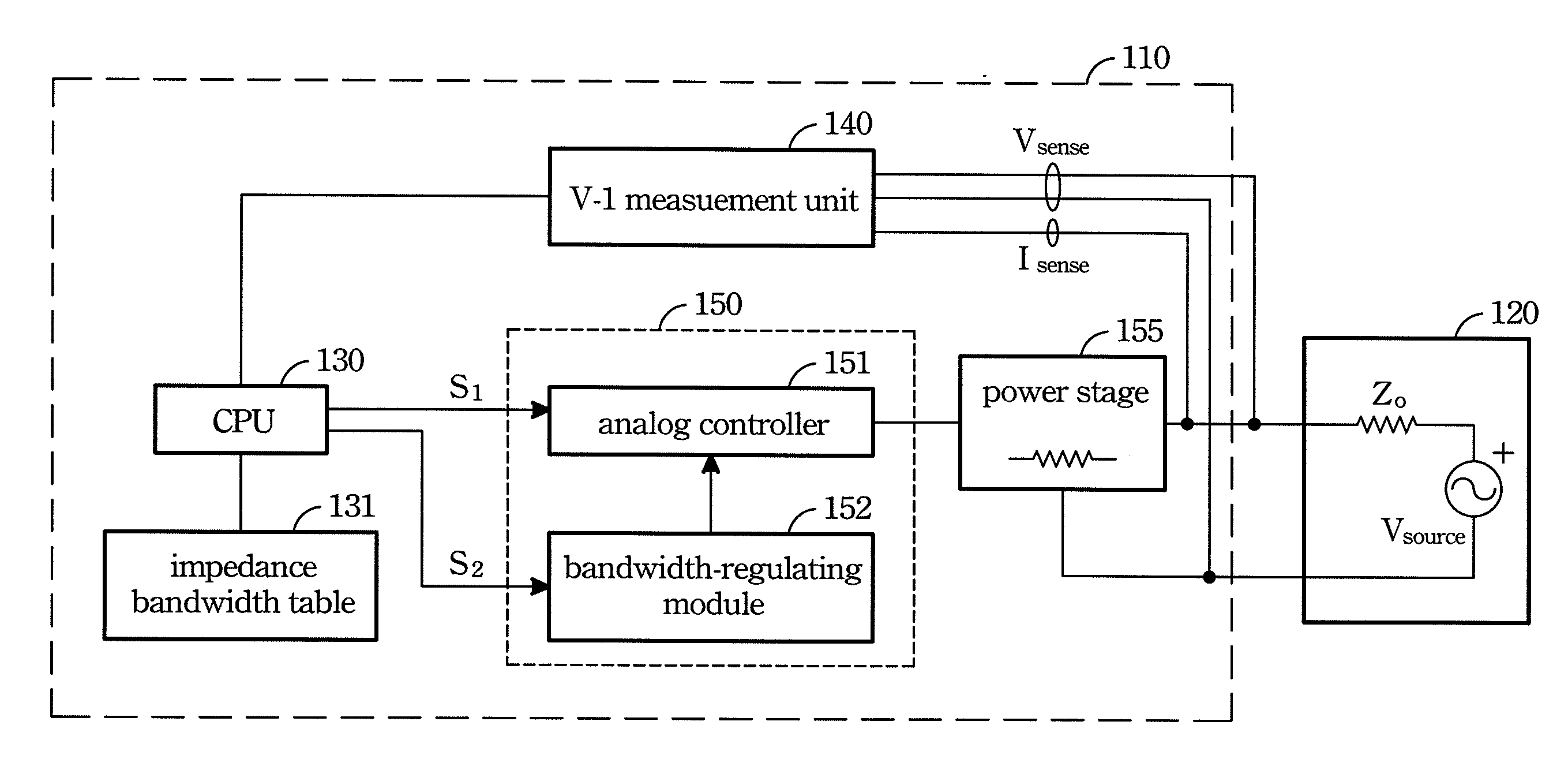

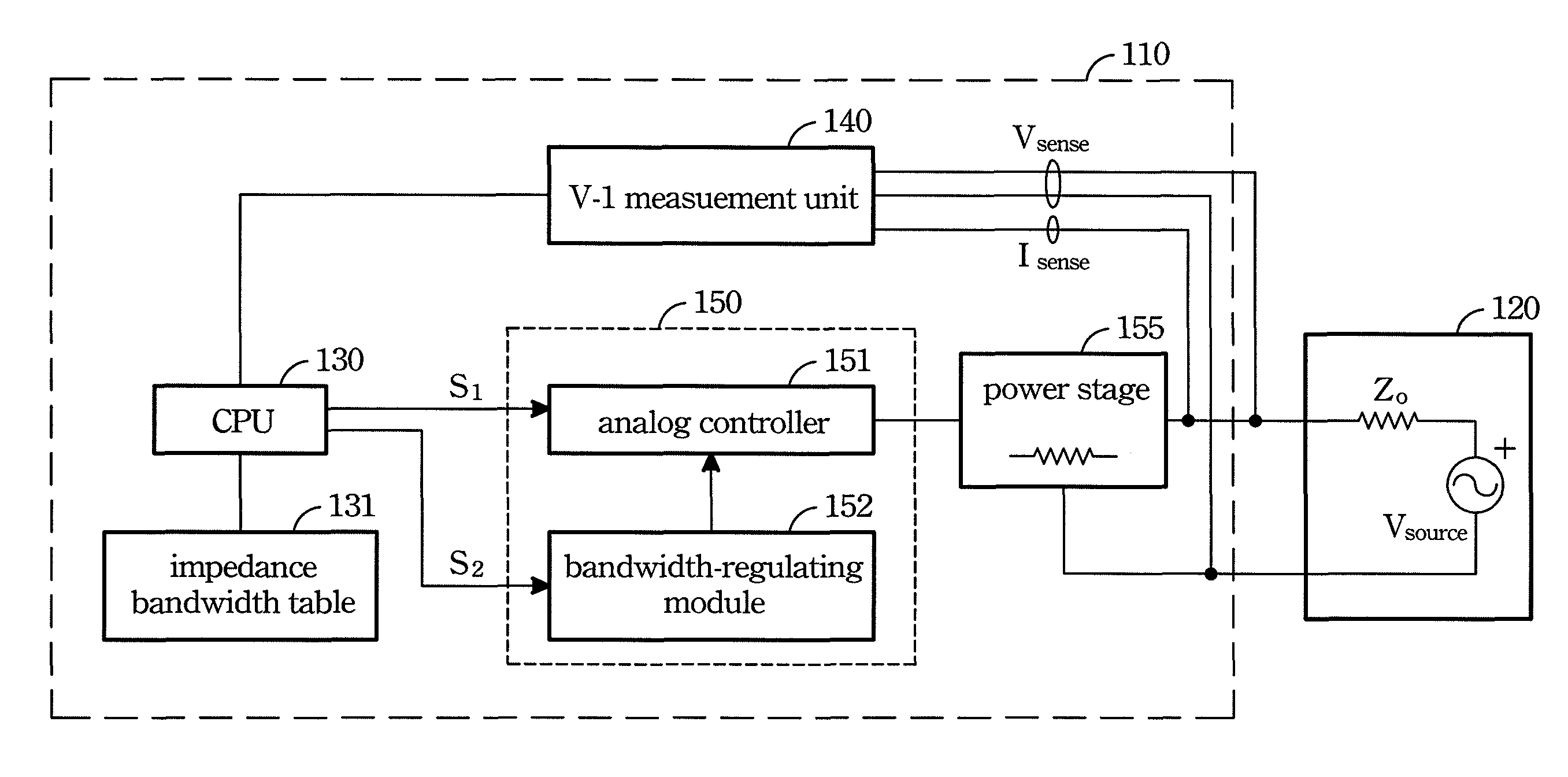

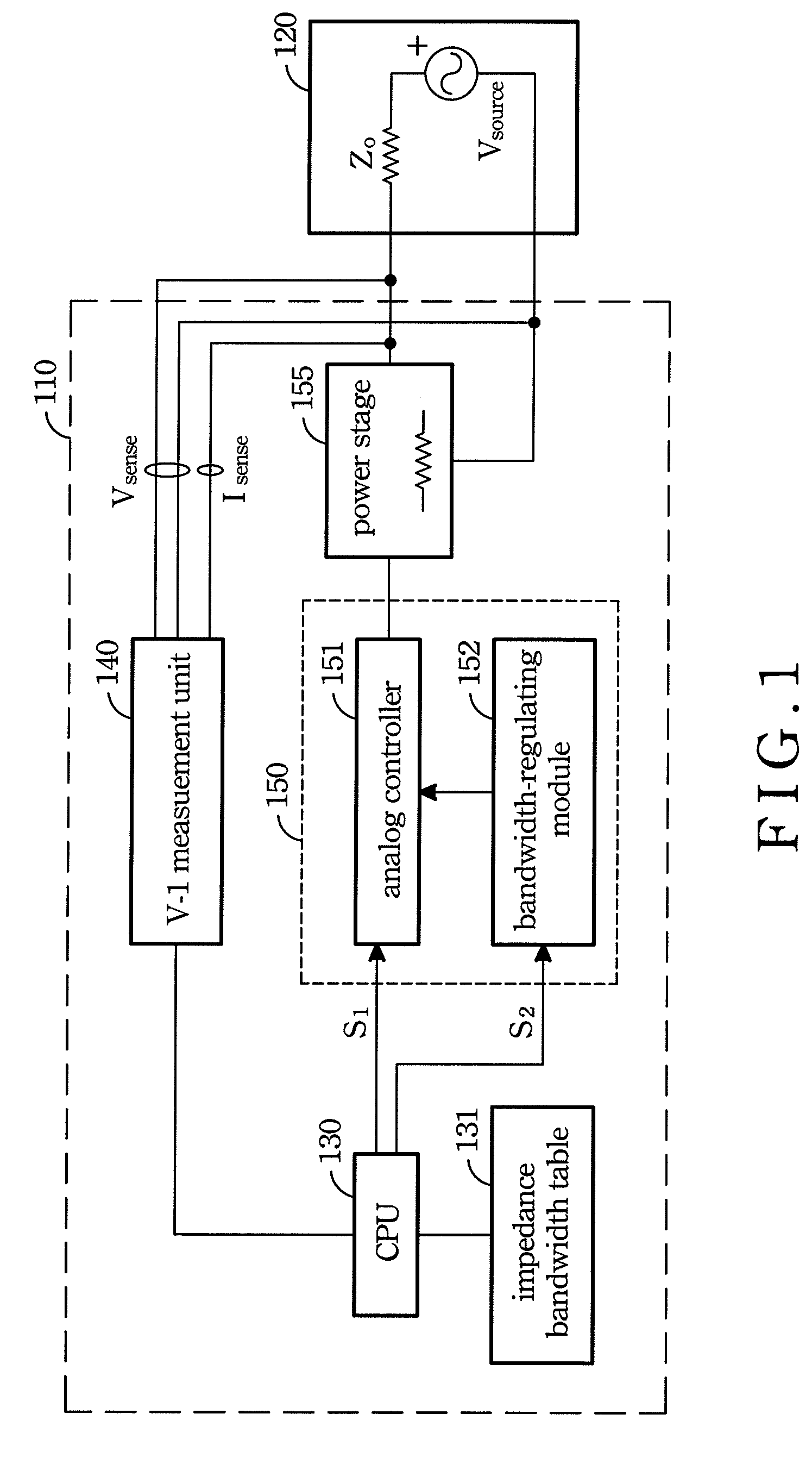

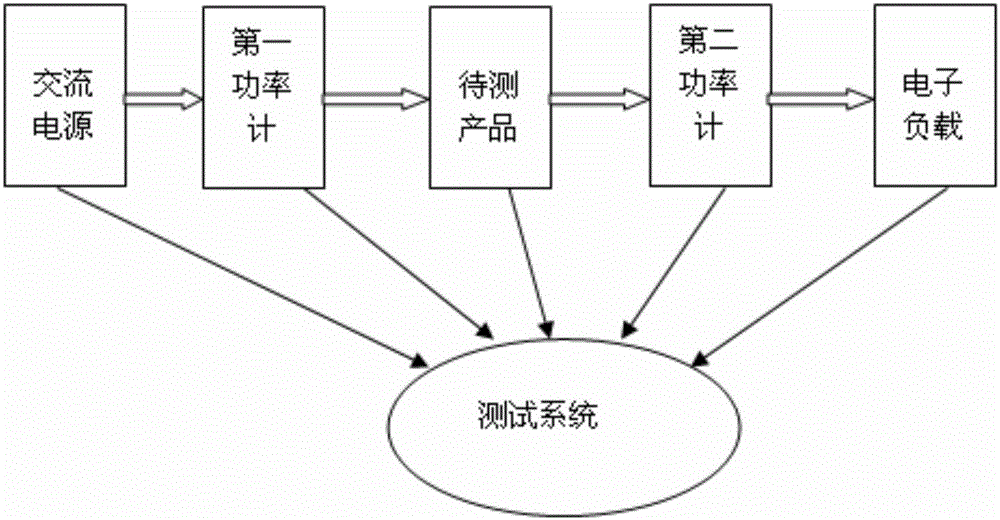

Electronic load device for power supply product to be tested and method for regulating bandwidth thereof

ActiveUS20090187367A1Testing/calibration of speed/acceleration/shock measurement devicesSpecial data processing applicationsElectronic loadOutput impedance

An electronic load device provided for testing an OT (power supply to be tested) and the working bandwidth is regulated and set according to the output impedance of the OT. The electronic load device comprises a CPU, an impedance-bandwidth table, a voltage-current measurement unit, a power stage and a control module. Firstly, a current pulled out from the OT to the power stage is called by the CPU. Thereafter, an output impedance of the OT is measured by the voltage-current measurement unit and analysis by the CPU. Next, a working bandwidth of the electronic load device is regulated and set by the control module according to the output impedance and the impedance-bandwidth table.

Owner:CHROMA ATE

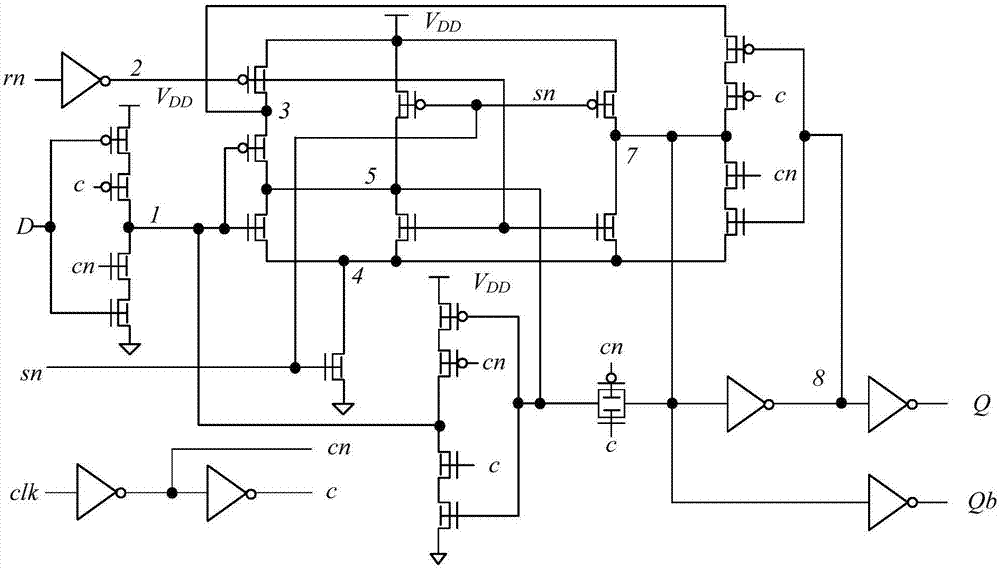

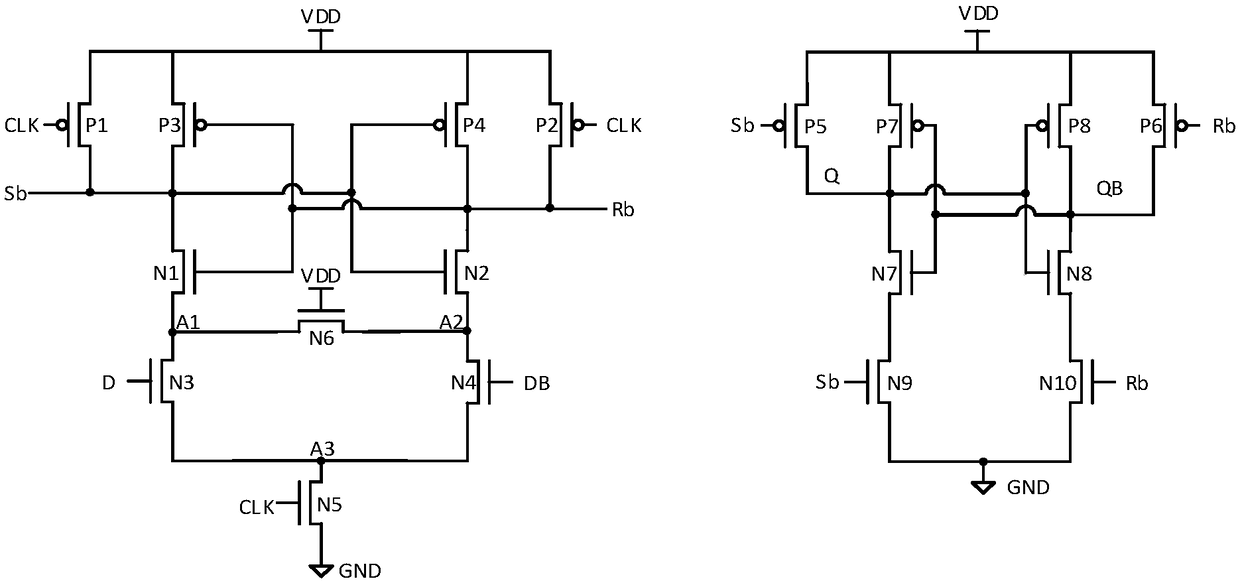

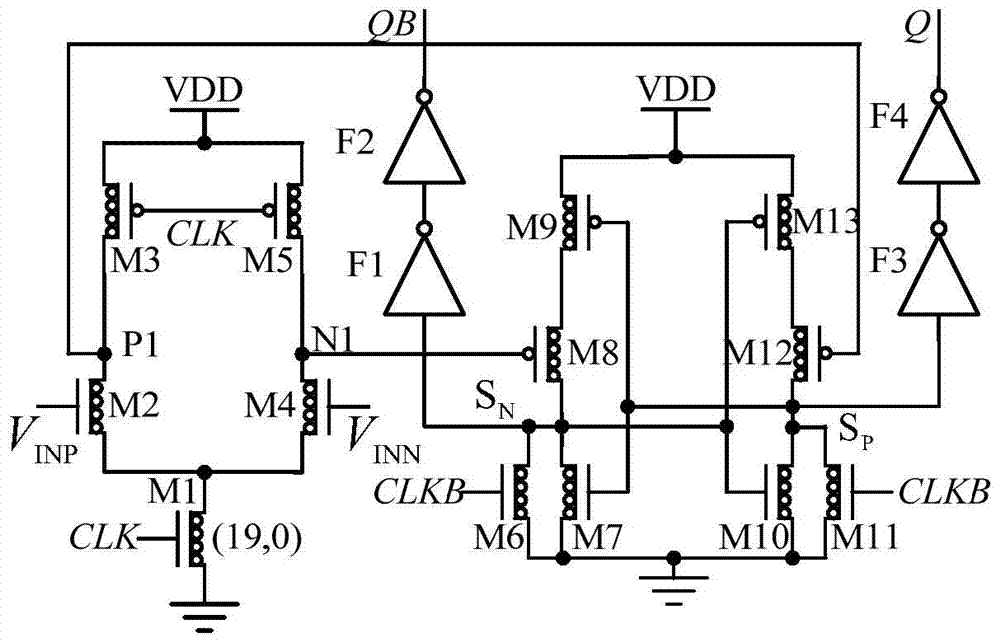

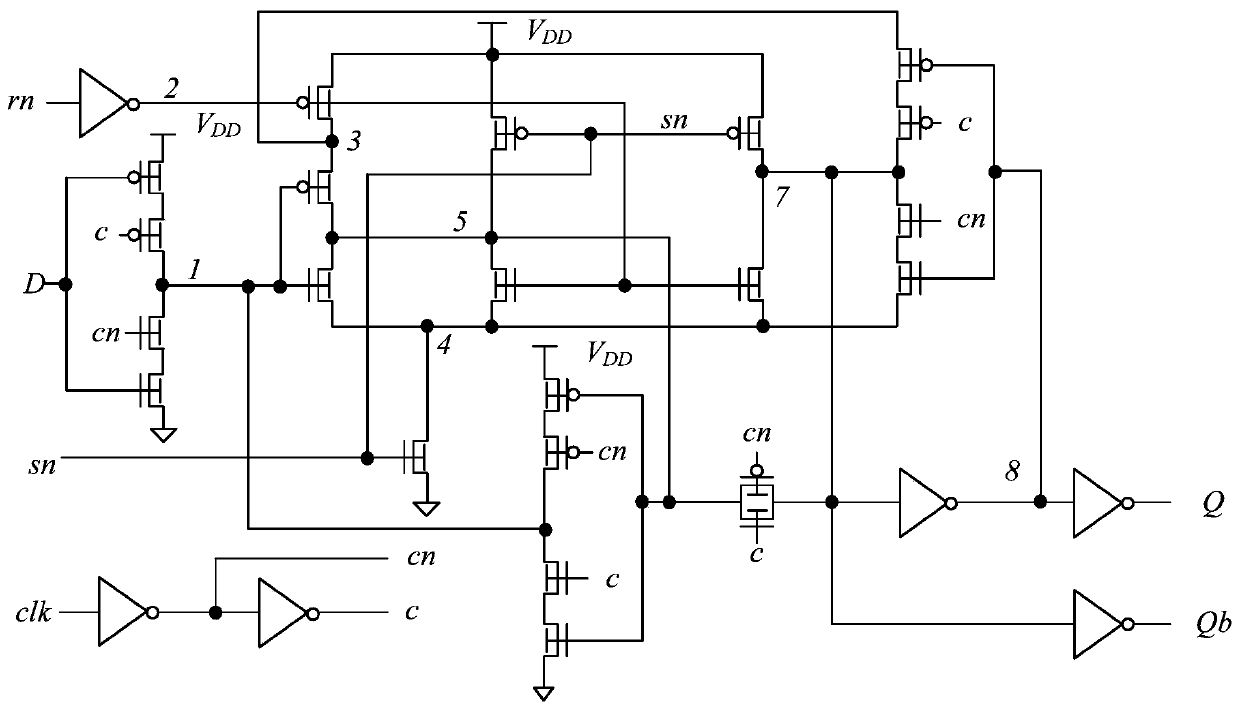

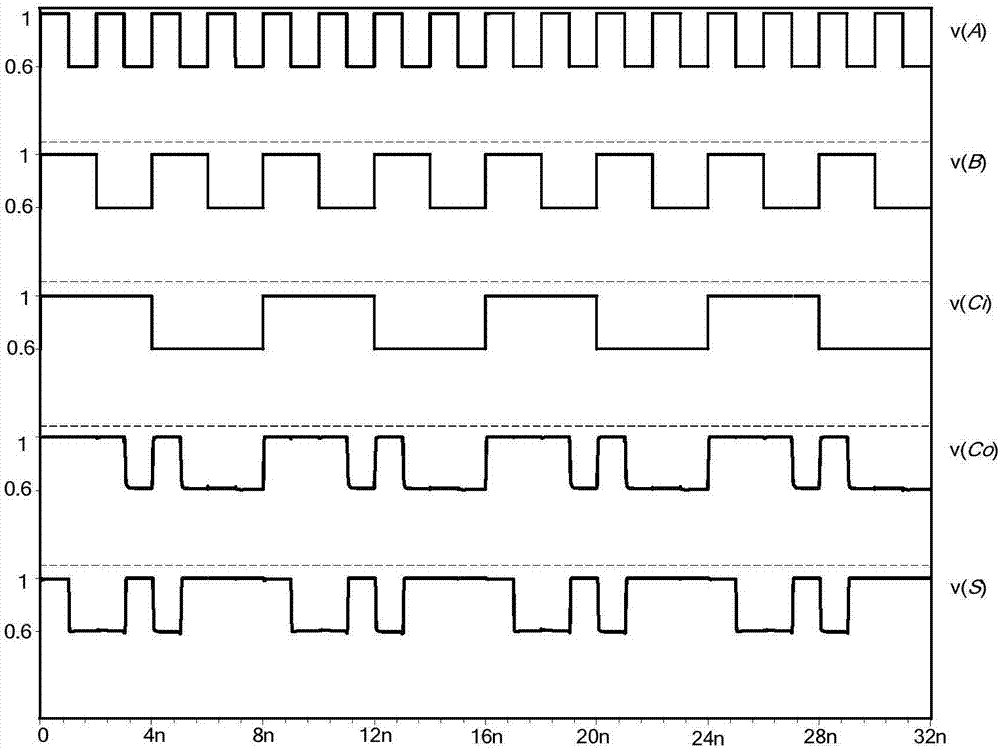

Short-pulse type D trigger based on FinFET device

The invention discloses a short-pulse type D trigger based on FinFET device. The short-pulse type D trigger comprises a first FinFET tube, a second FinFET tube, a third FinFET tube, a fourth FinFET tube, a fifth FinFET tube, a sixth FinFET tube, a first phase inverter, a second phase inverter, a third phase inverter, a fourth phase inverter, a fifth phase inverter, a sixth phase inverter, a seventh phase inverter, a seventh phase inverter, an eighth phase inverter, a ninth phase inverter, a tenth phase inverter, a first two-input NOR gate, a first two-input XOR gate and a second two-input XOR gate, wherein each of the first two-input NOR gate, the first two-input XOR gate and the second two-input XOR gate is provided with a first input, a second input and an output end; the short-pulse type D trigger has the advantages that the number of the FinFET tube is reduced, the circuit delay and the circuit area are further optimized since the series connection of the transistor is reduced; therefore, the circuit area, the time delay, the power consumption and the power delay product are small under the condition of not influencing the circuit performance.

Owner:NINGBO UNIV

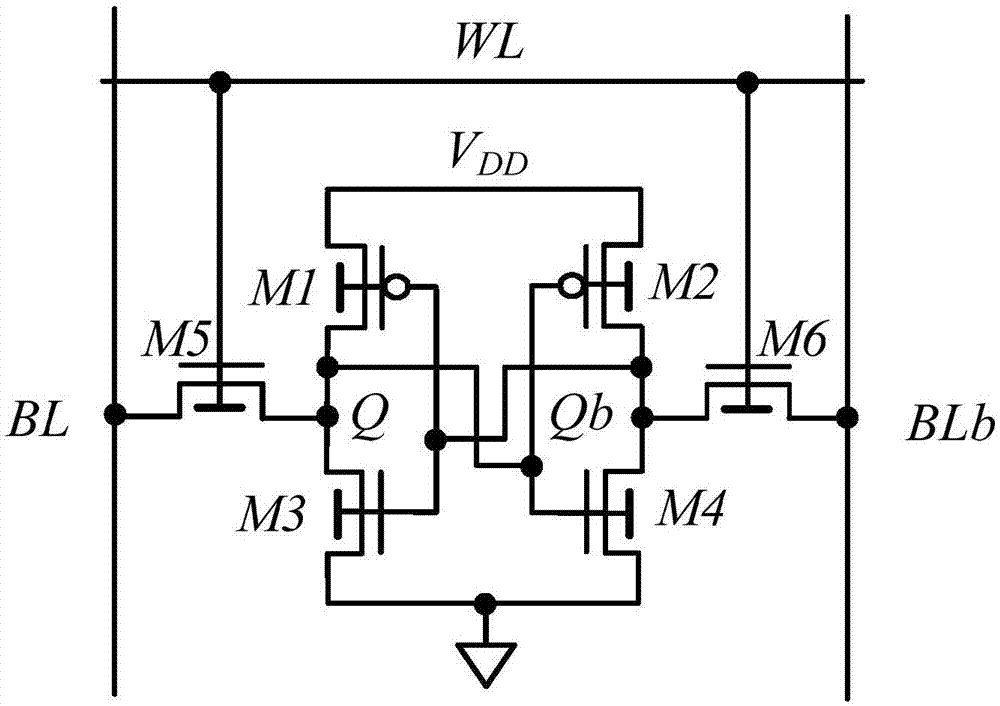

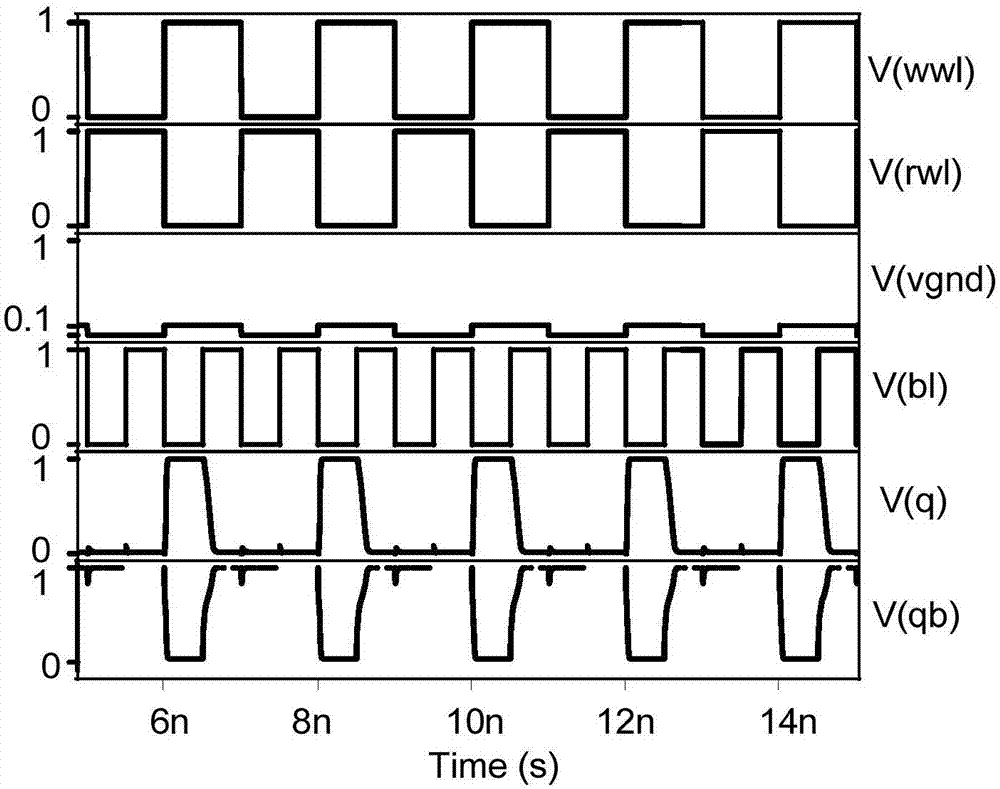

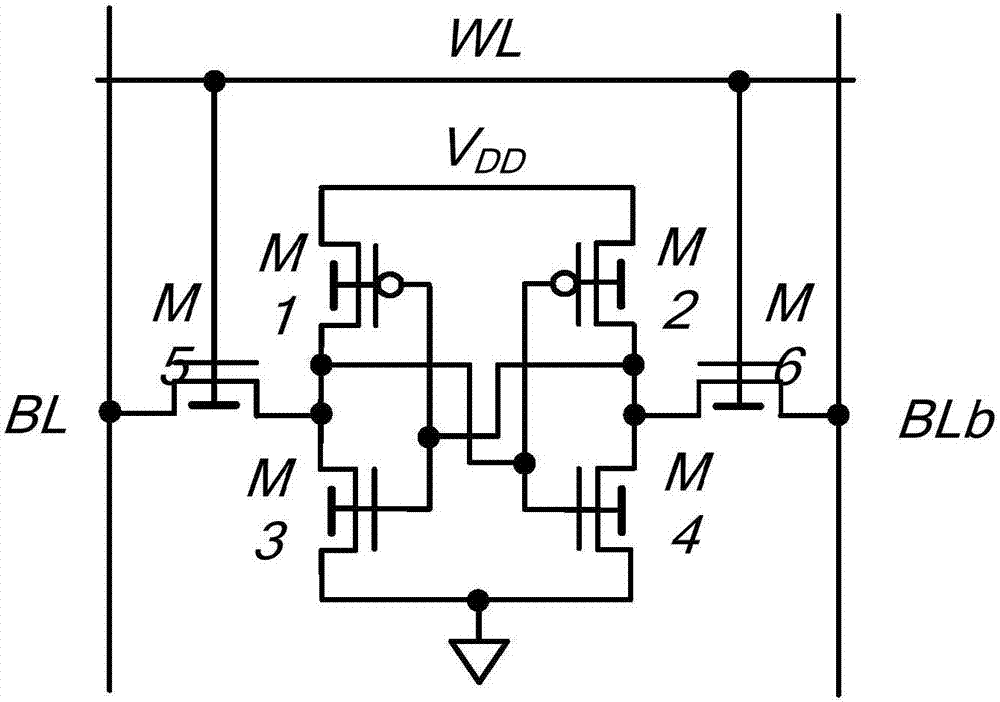

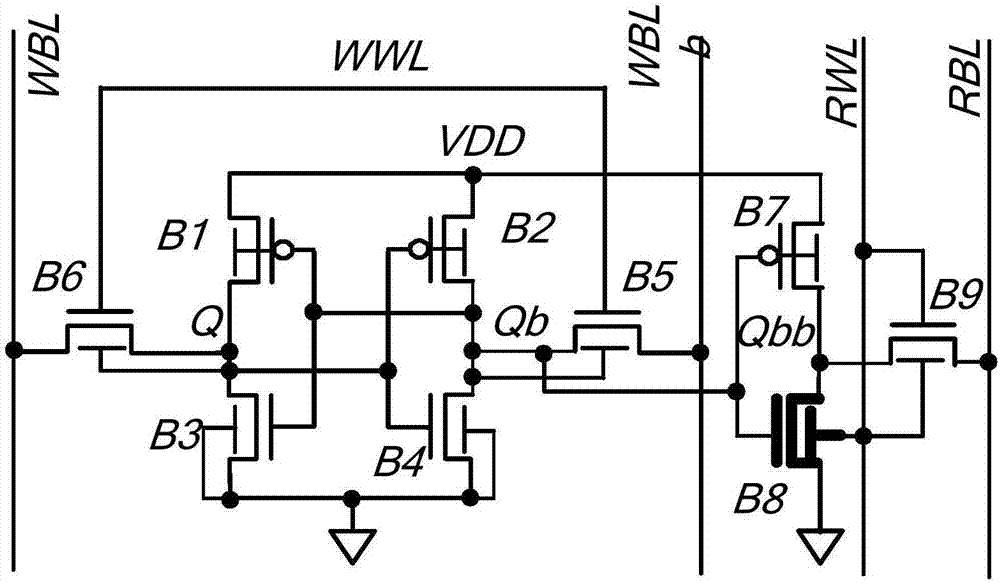

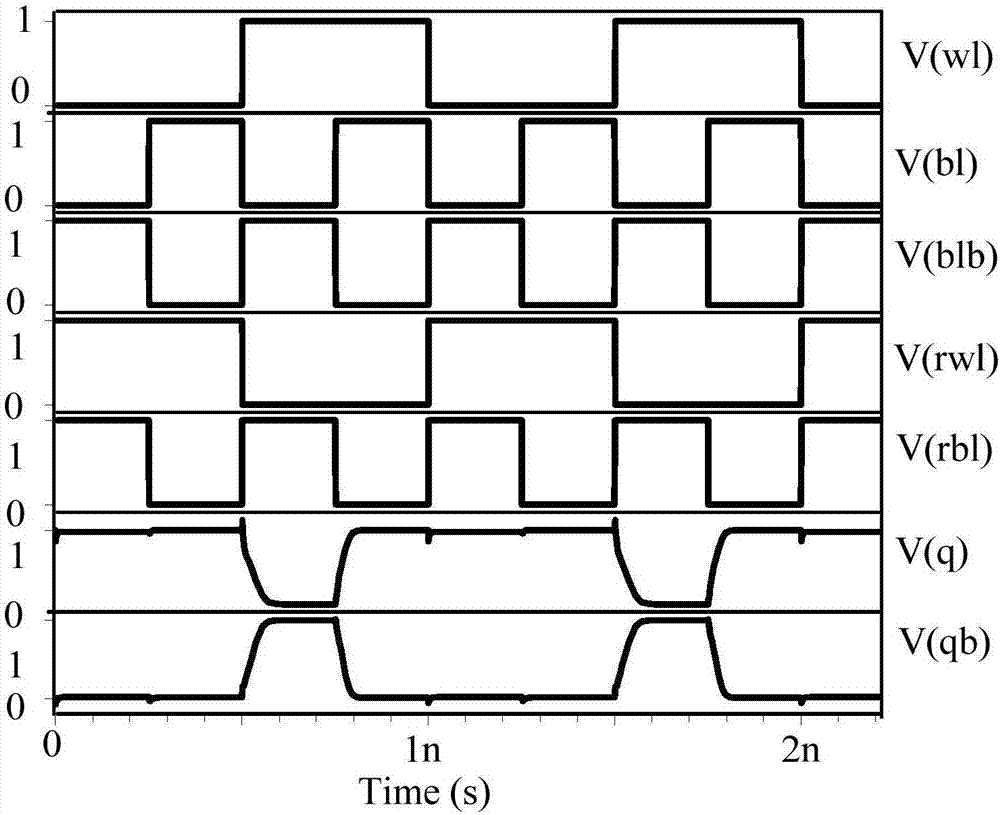

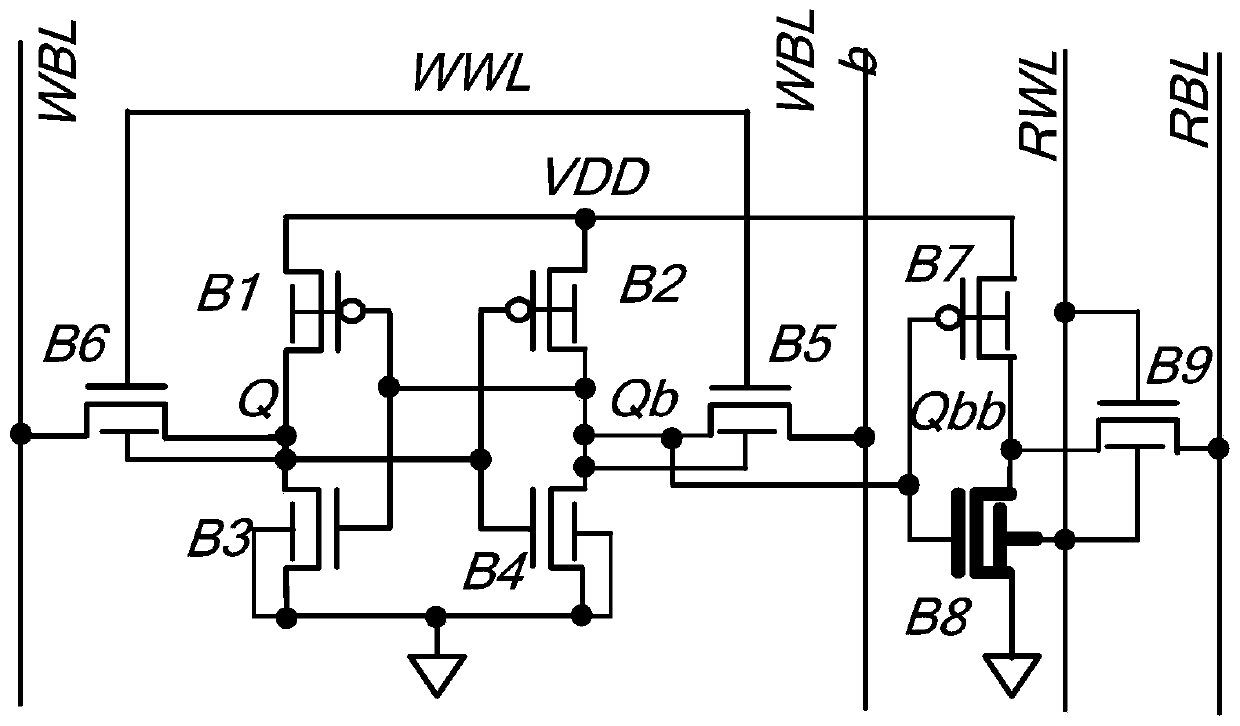

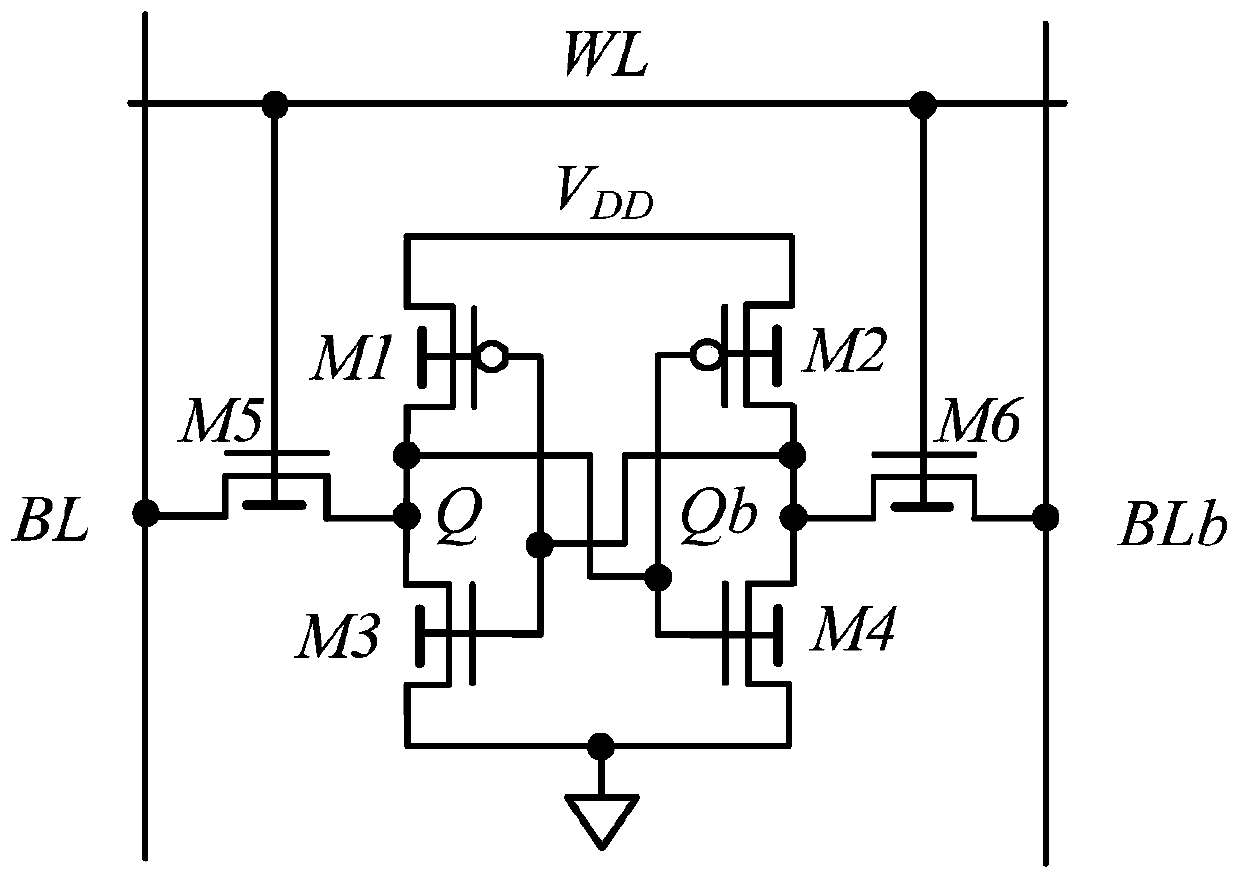

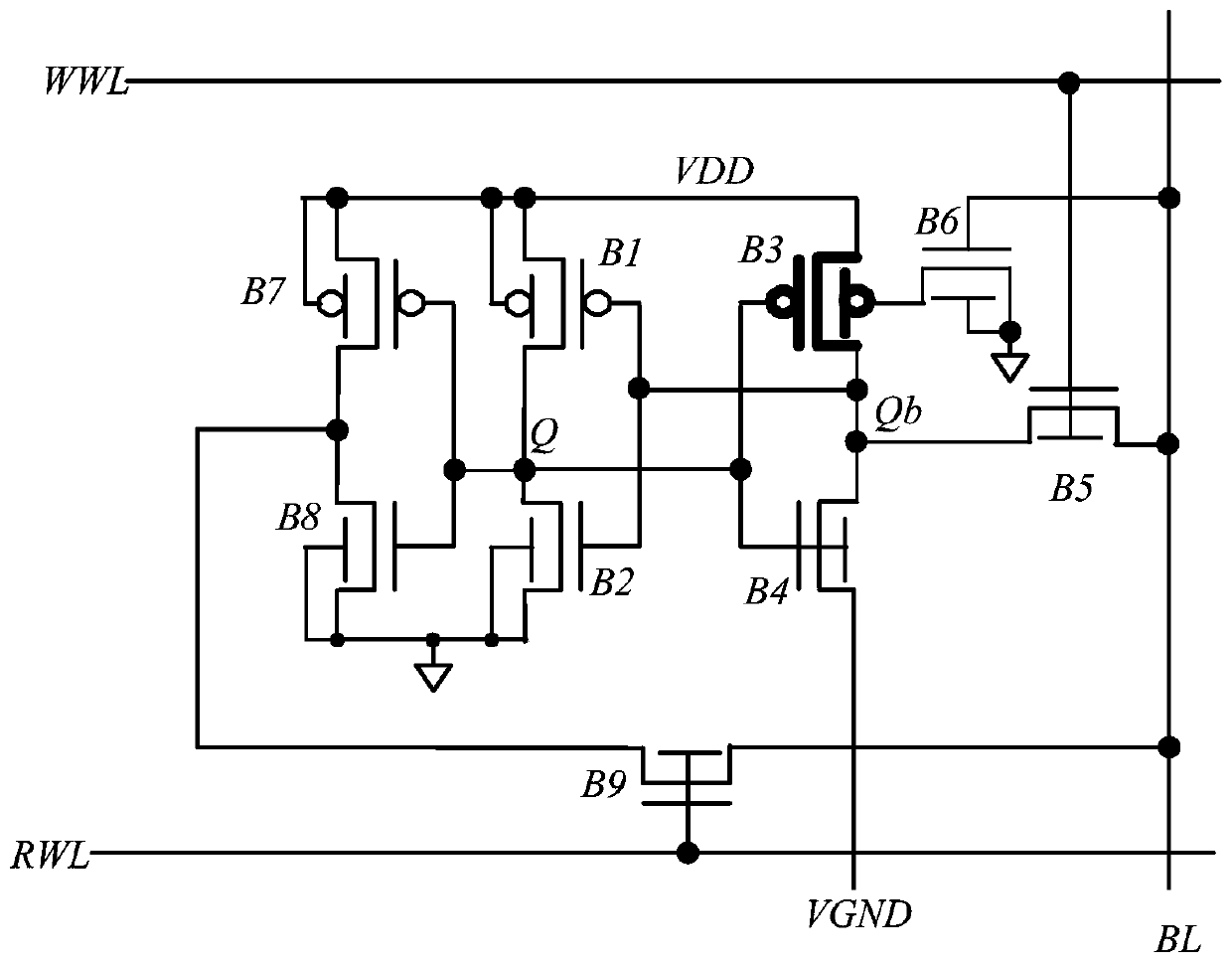

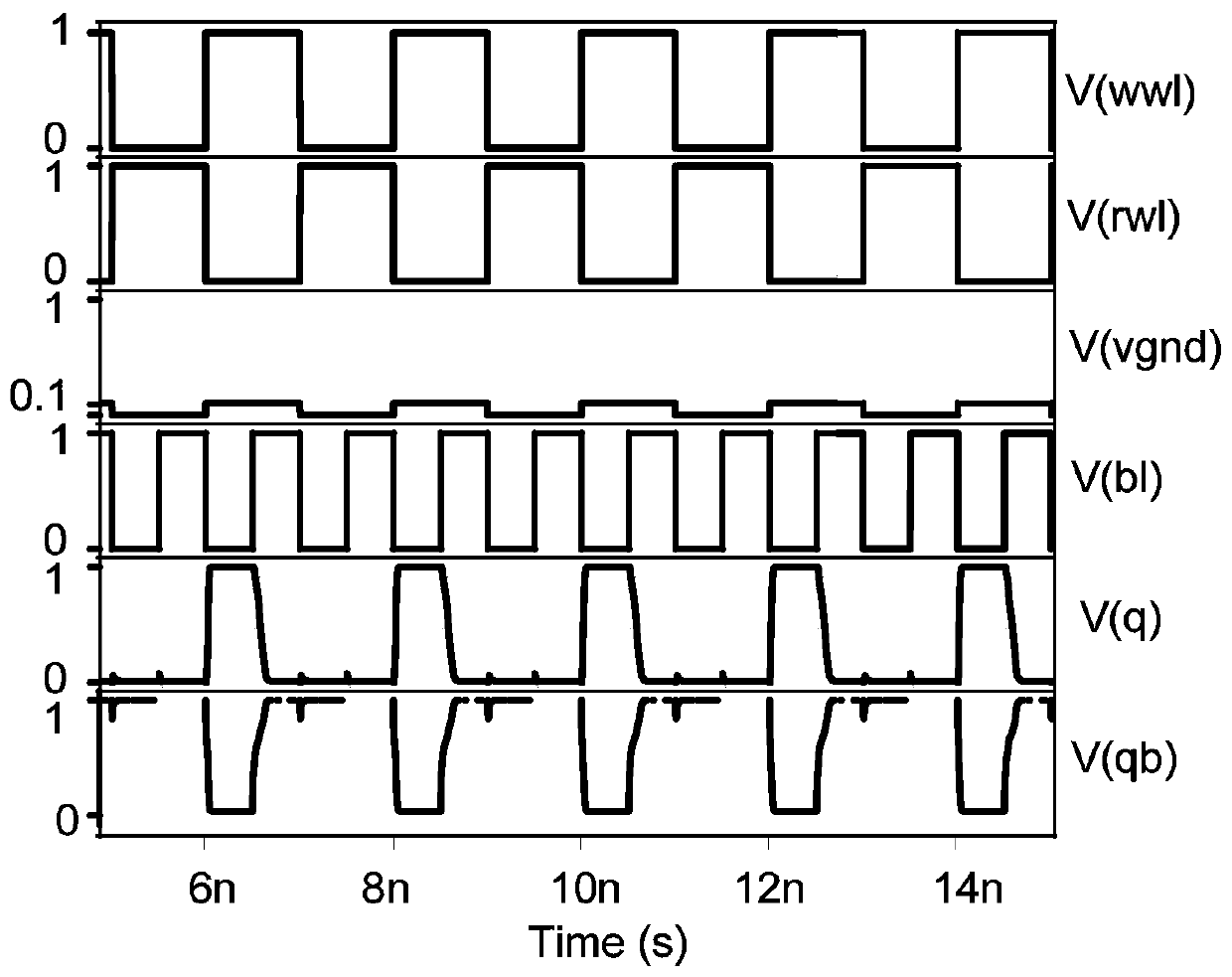

FinFET device-based unit line non-symmetric storage unit

ActiveCN107393581AReduce dynamic power lossesImprove noise marginDigital storageNon symmetricNoise margin

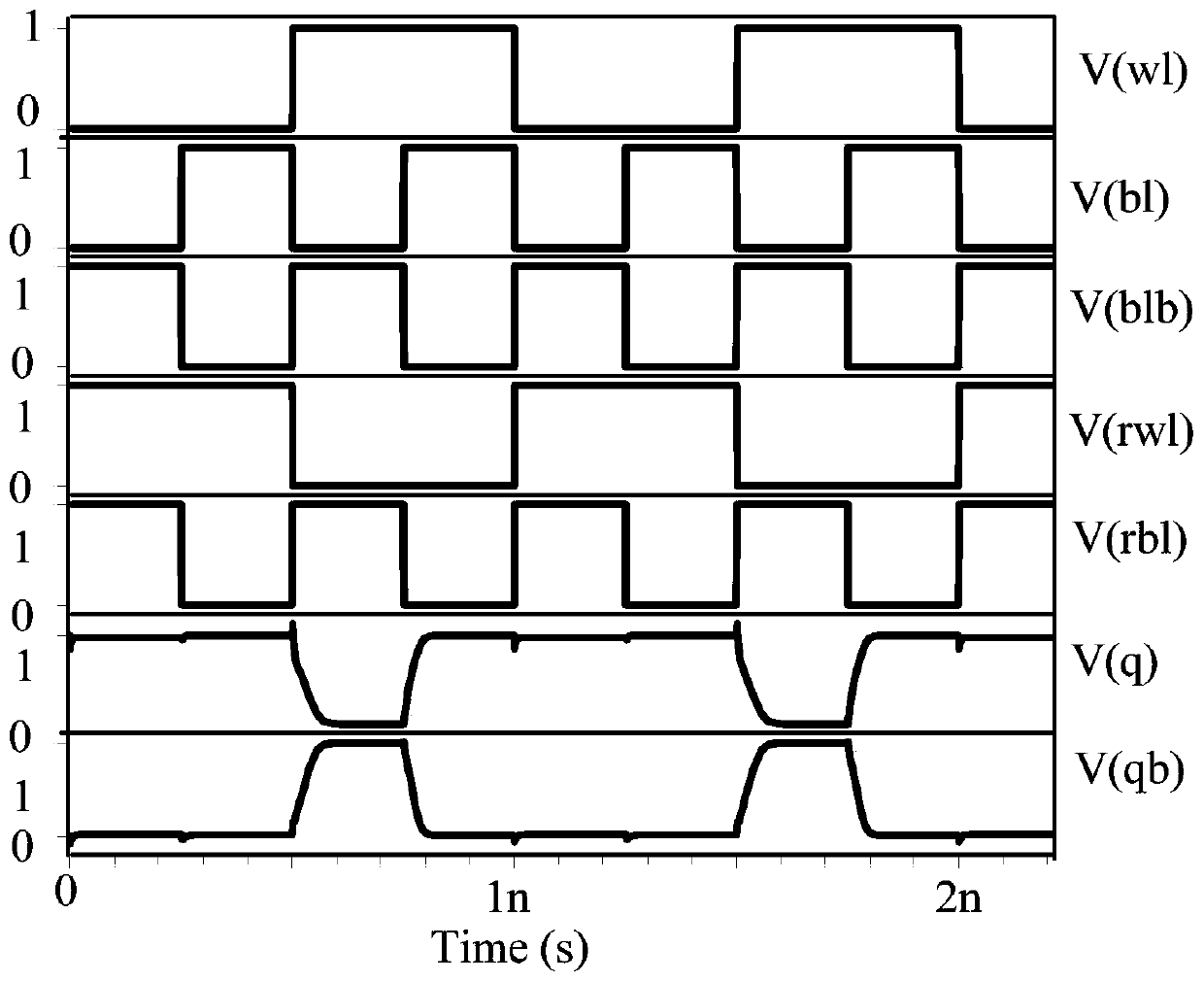

The invention discloses a FinFET device-based unit line non-symmetric storage unit. The unit comprises a bit line, a write word line, a read word line, a first FinFET, a second FinFET, a third FinFET, a fourth FinFET, a fifth FinFET, a sixth FinFET, a seventh FinFET, an eighth FinFET and a ninth FinFET, wherein the first FinFET and the seventh FinFET are low-threshold P-type FinFETs; the second FinFET, the fourth FinFET, the fifth FinFET, the sixth FinFET, the eighth FinFET and the ninth FinFET are all low-threshold N-type FinFETs; and the third FinFET is a high-threshold P-type FinFET. The unit has the advantages that under the condition of not influencing circuit performance, the delay, the power consumption and a power-delay product are all relatively small, the noise margin during write operation is relatively large, and the circuit function stability is relatively high.

Owner:NINGBO UNIV

Electronic load device for power supply product to be tested and method for regulating bandwidth thereof

ActiveUS7933732B2Testing/calibration of speed/acceleration/shock measurement devicesSpecial data processing applicationsElectronic loadPower flow

An electronic load device provided for testing an OT (power supply to be tested) and the working bandwidth is regulated and set according to the output impedance of the OT. The electronic load device comprises a CPU, an impedance-bandwidth table, a voltage-current measurement unit, a power stage and a control module. Firstly, a current pulled out from the OT to the power stage is called by the CPU. Thereafter, an output impedance of the OT is measured by the voltage-current measurement unit and analysis by the CPU. Next, a working bandwidth of the electronic load device is regulated and set by the control module according to the output impedance and the impedance-bandwidth table.

Owner:CHROMA ATE

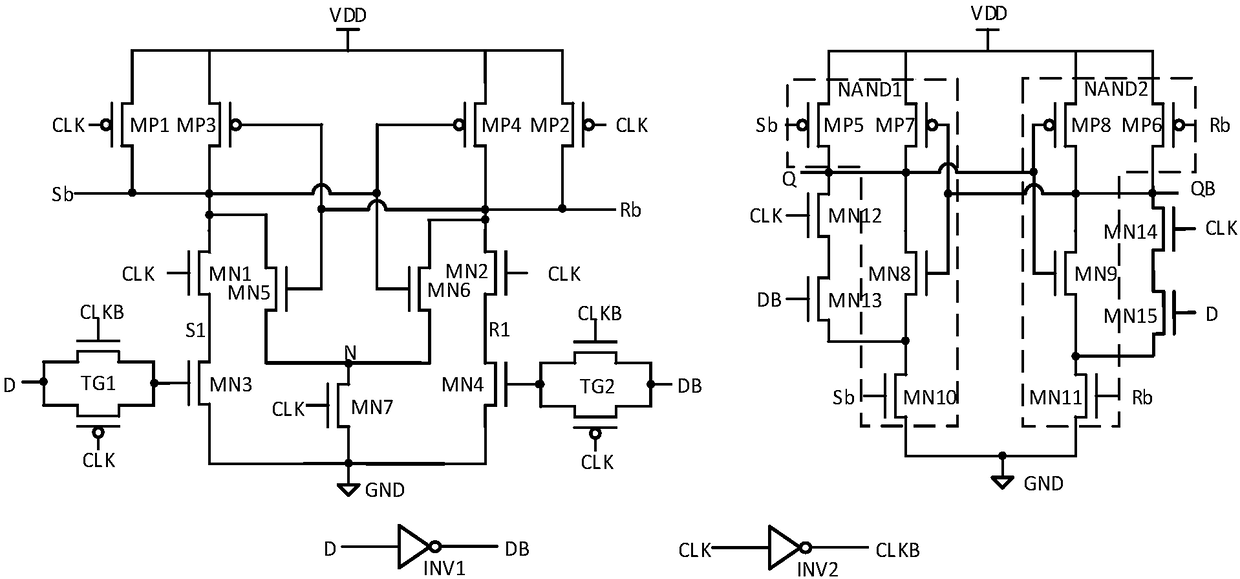

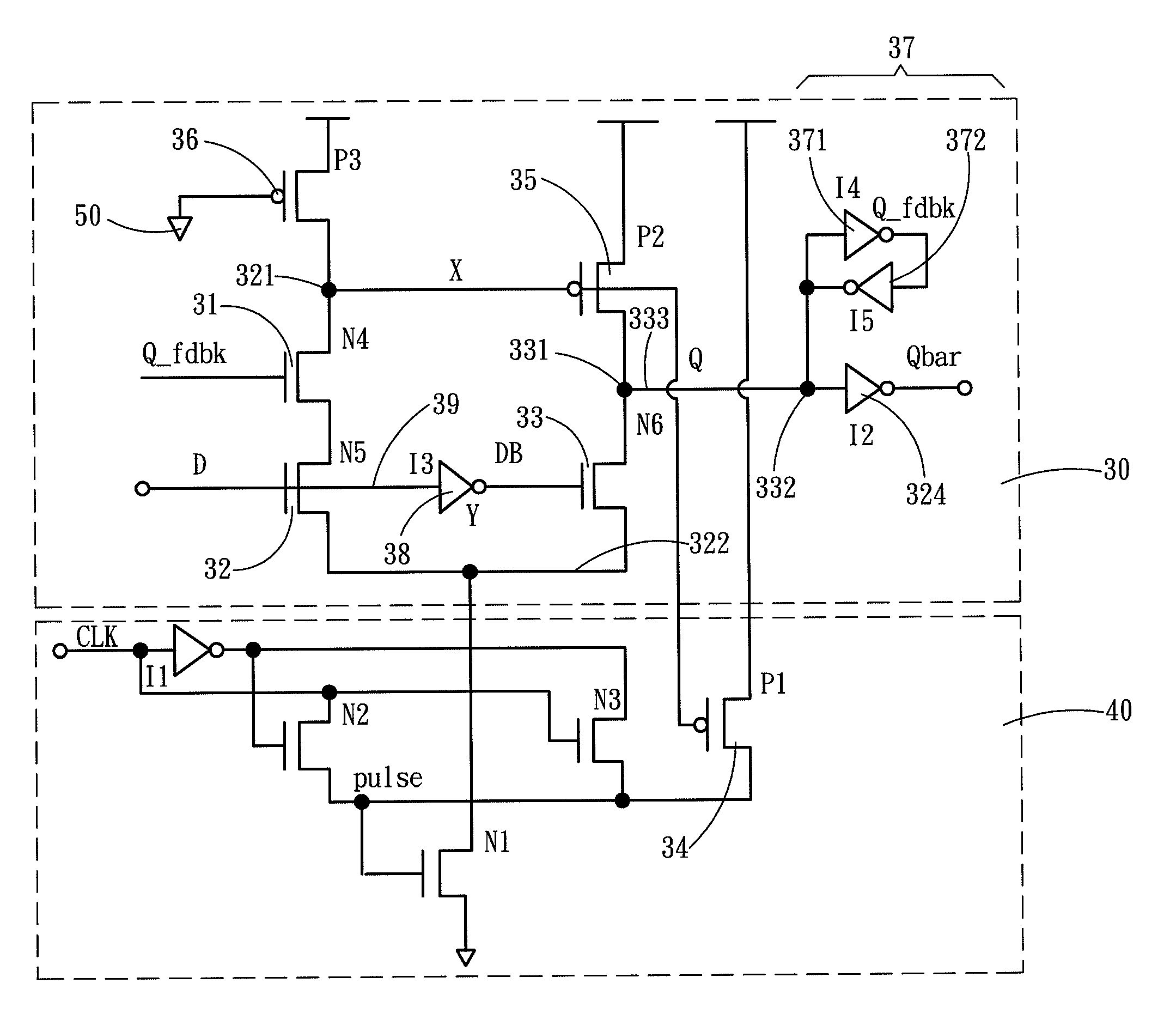

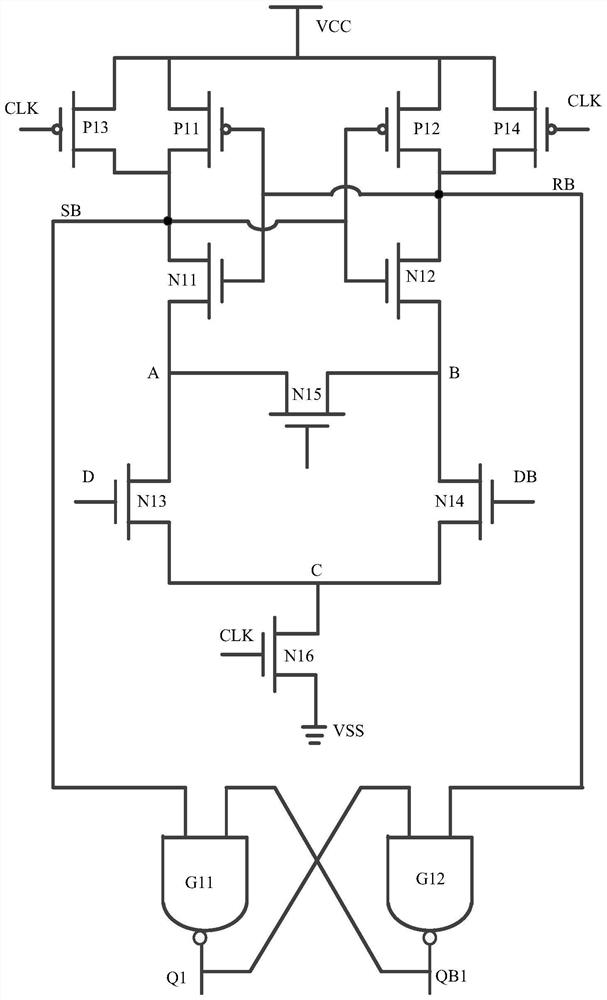

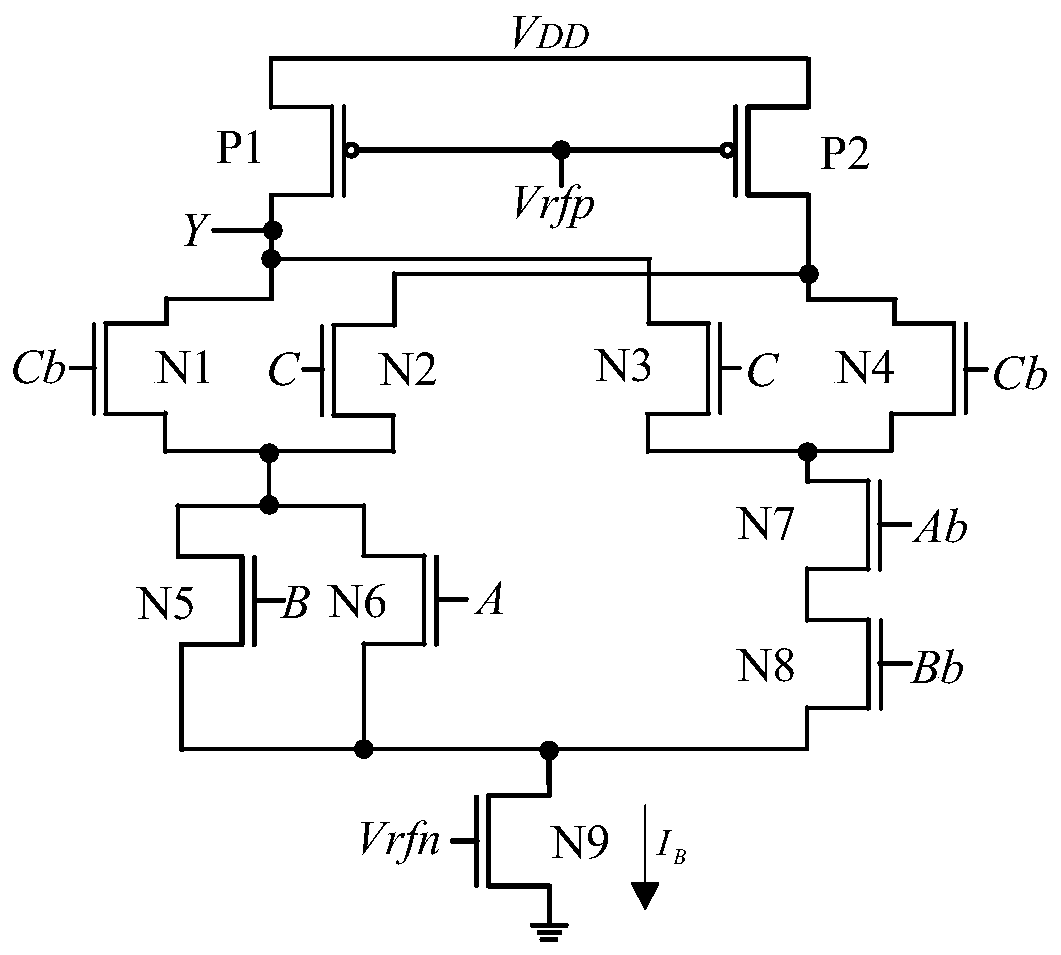

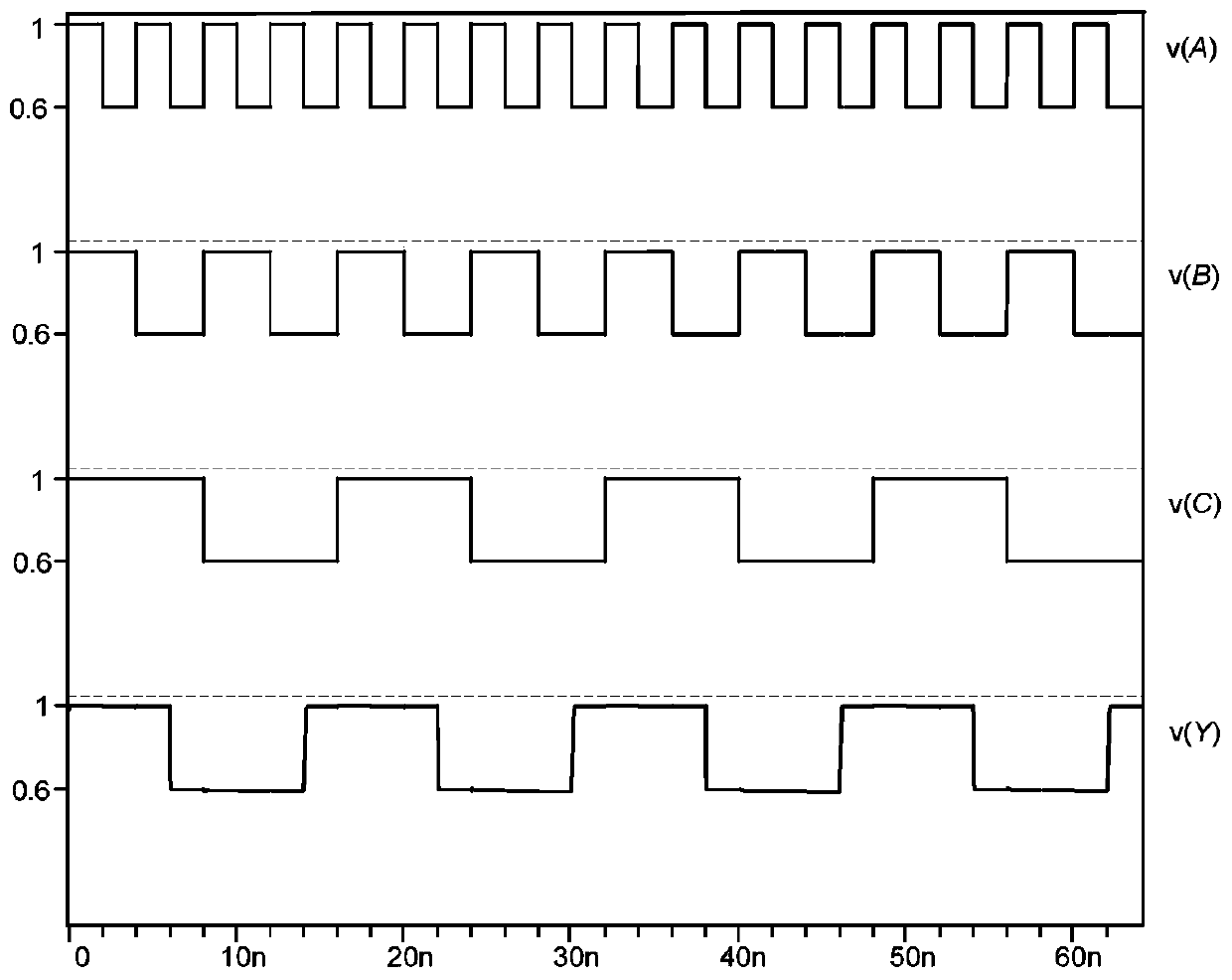

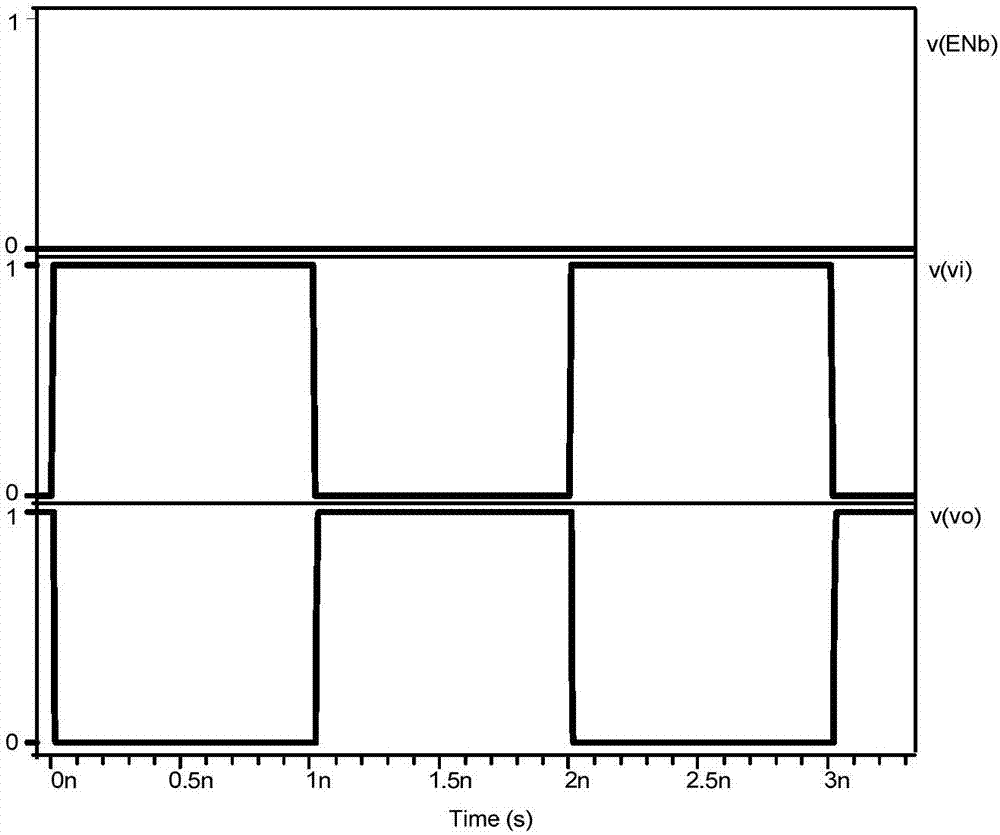

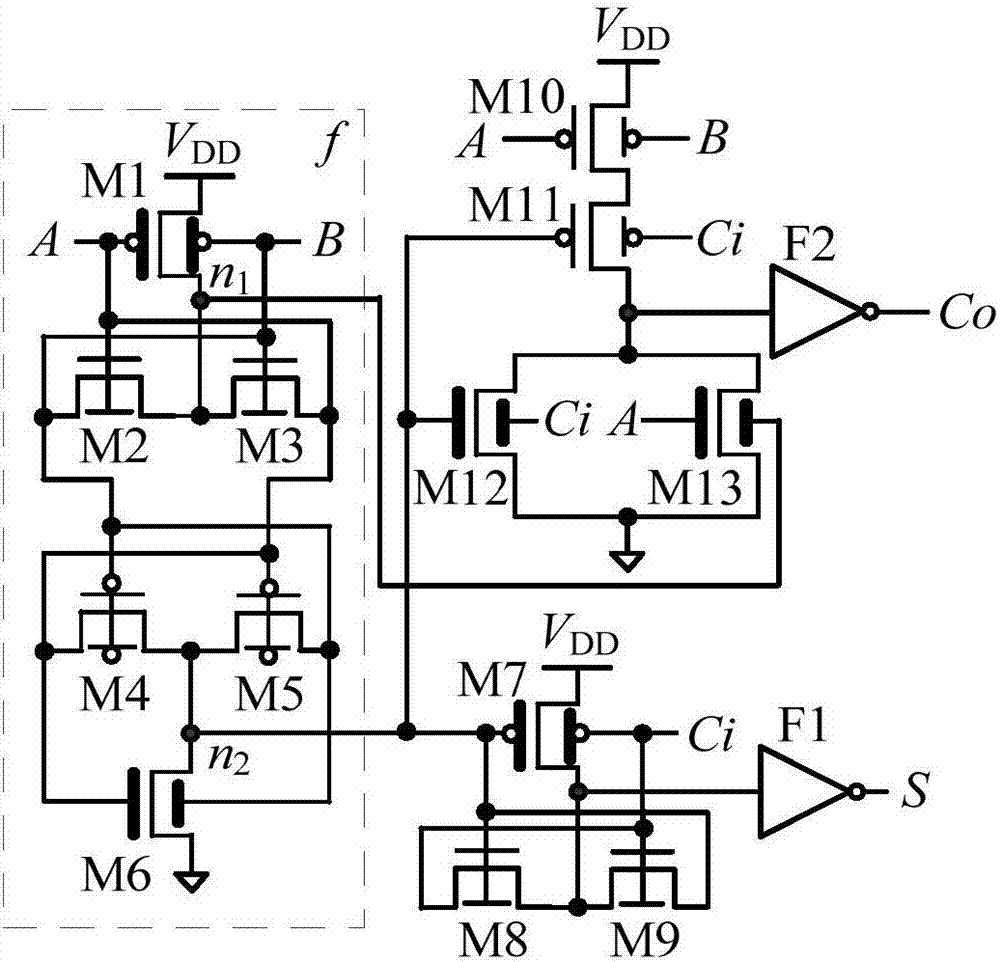

Low-power consumption sensitive amplifier type D-flip flop

InactiveCN108233896AReduce power consumptionIncrease power consumptionElectric pulse generatorNAND gateEngineering

The invention provides a low-power consumption sensitive amplifier type D-flip flop, and belongs to the technical field of integrated circuits. The low-power consumption sensitive amplifier type D-flip flop comprises an input inverting stage, a sensitive amplifier stage and a latch stage; the input inverting stage is used for generating an inverted input data signal and an inverted clock signal; an evaluation pulldown part and a data storage part of the sensitive amplifier stage are independent, evaluation pulldown is achieved through two NMOS transistors which are connected in series, internal charging and discharging nodes are decreased, and by means of transmission gates controlled by the lock signal and the inverted clock signal, the input data signal achieves data transmission and avoids the influence of input data changes generated when the clock signal is in a high level; and the latch stage introduces an independent pulldown path formed by a pair of NMOS transistors which are connected in series and controlled by the clock signal and the input data signal and the clock signal and the inverted input clock signal respectively on the basis of a traditional NAND gate type SR latch, and output pulldown only has one-stage delay. The low-power consumption sensitive amplifier type D-flip flop has the advantages of low power consumption and short delay simultaneously, achieves great improvement on the power delay product (PDP) and is particularly suitable for an application system with the low switch activity.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

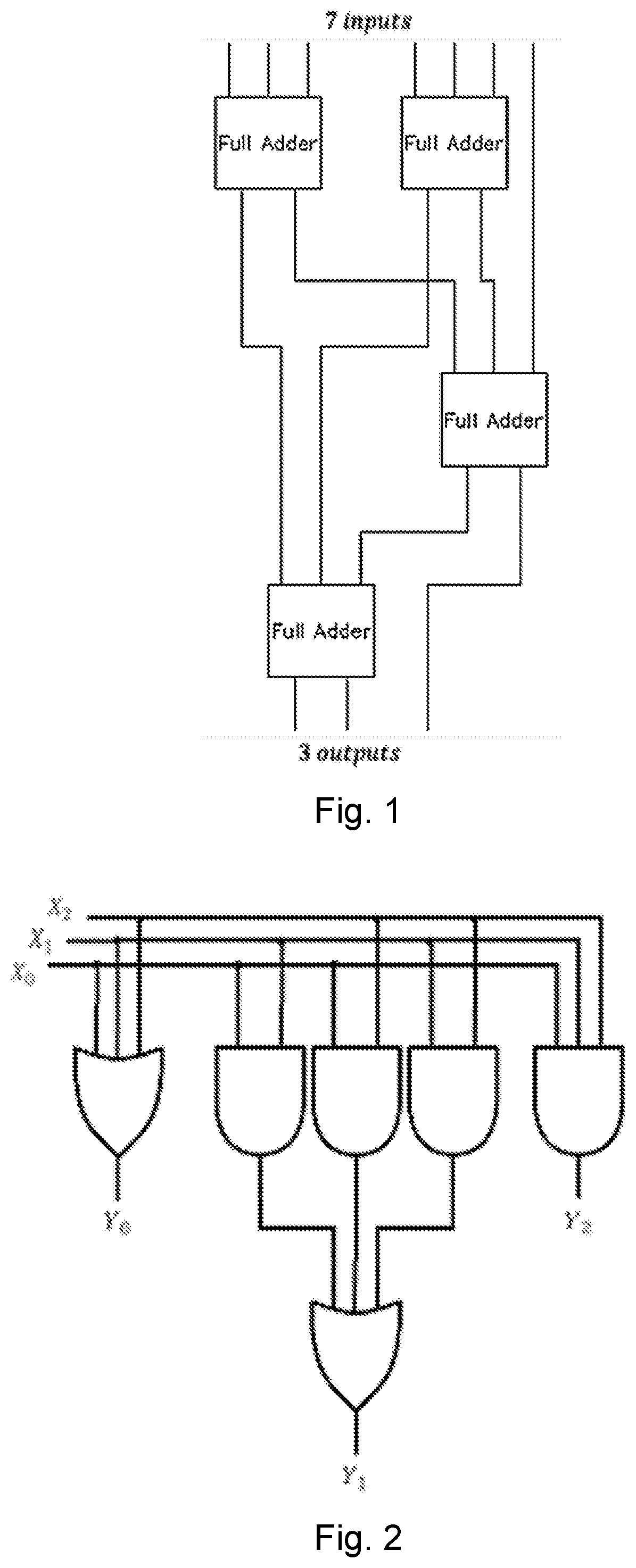

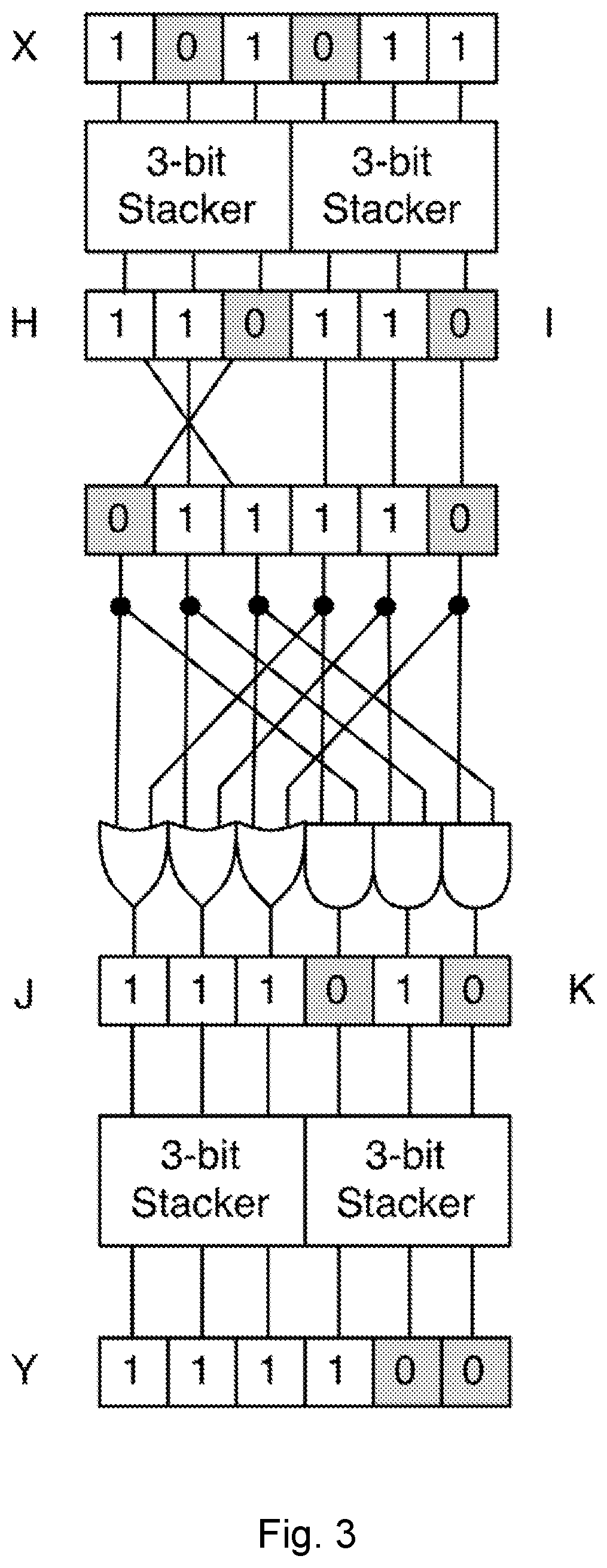

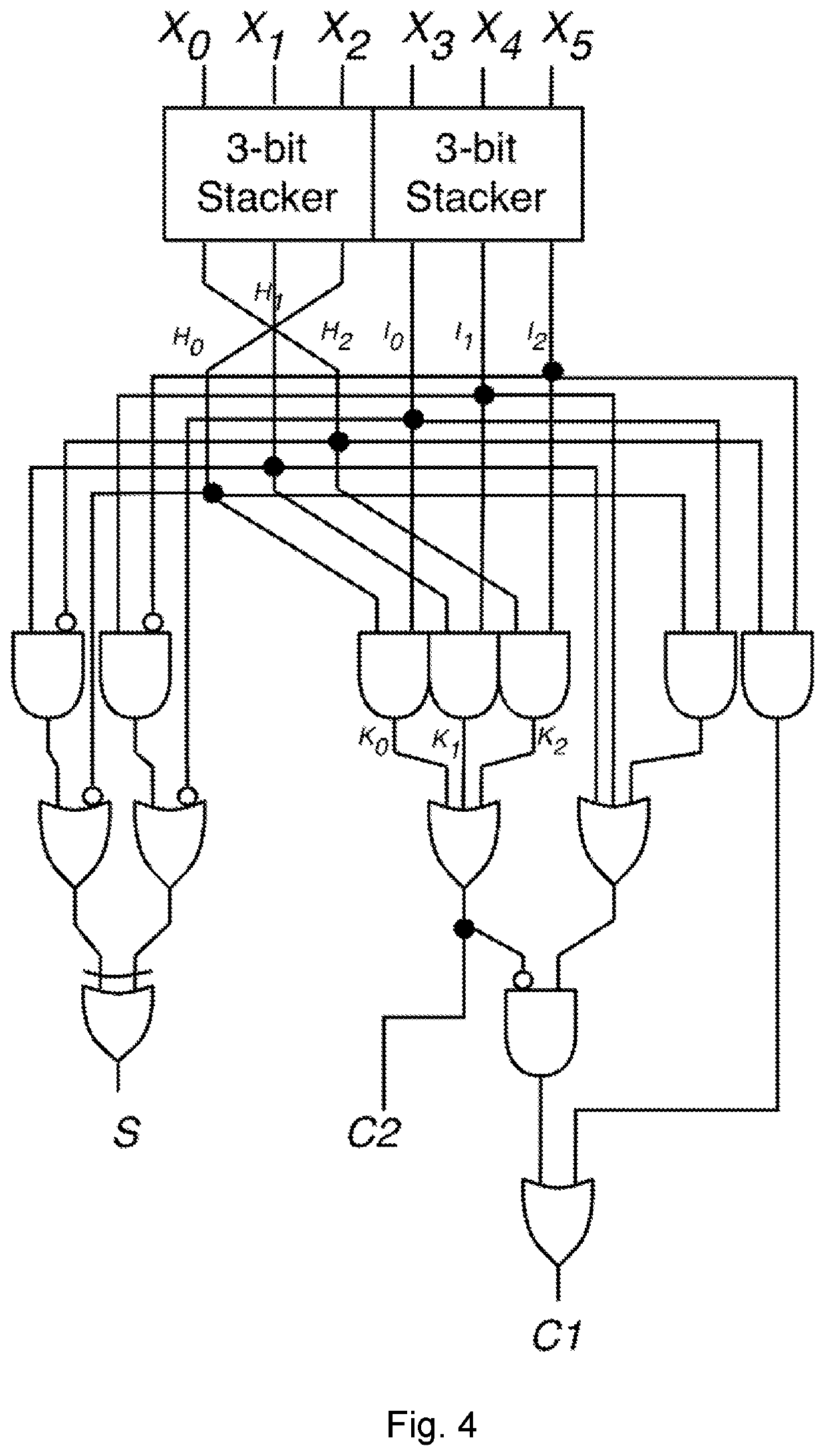

Fast binary counters based on symmetric stacking and methods for same

ActiveUS20200394017A1Increase speedSave powerComputation using non-contact making devicesNumber-of-one countersWallace treeBinary multiplier

In this paper, binary stackers and counters are presented. In an embodiment, a counter uses 3-bit stacking circuits which group the T bits together, followed by a symmetric method to combine pairs of 3-bit stacks into 6-bit stacks. The bit stacks are then converted to binary counts, producing 6:3 and 7:3 Counter circuits with no XOR gates on the critical path. This avoidance of XOR gates results in faster designs with efficient power and area utilization. In VLSI simulations, the presently-disclosed counters were 30% faster and at consumed at least 20% less power than existing parallel counters. Additionally, using the presently-disclosed counter in existing Counter Based Wallace tree multiplier architectures reduces latency and improves efficiency in terms of power-delay product for 64-bit and 128-bit multipliers.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

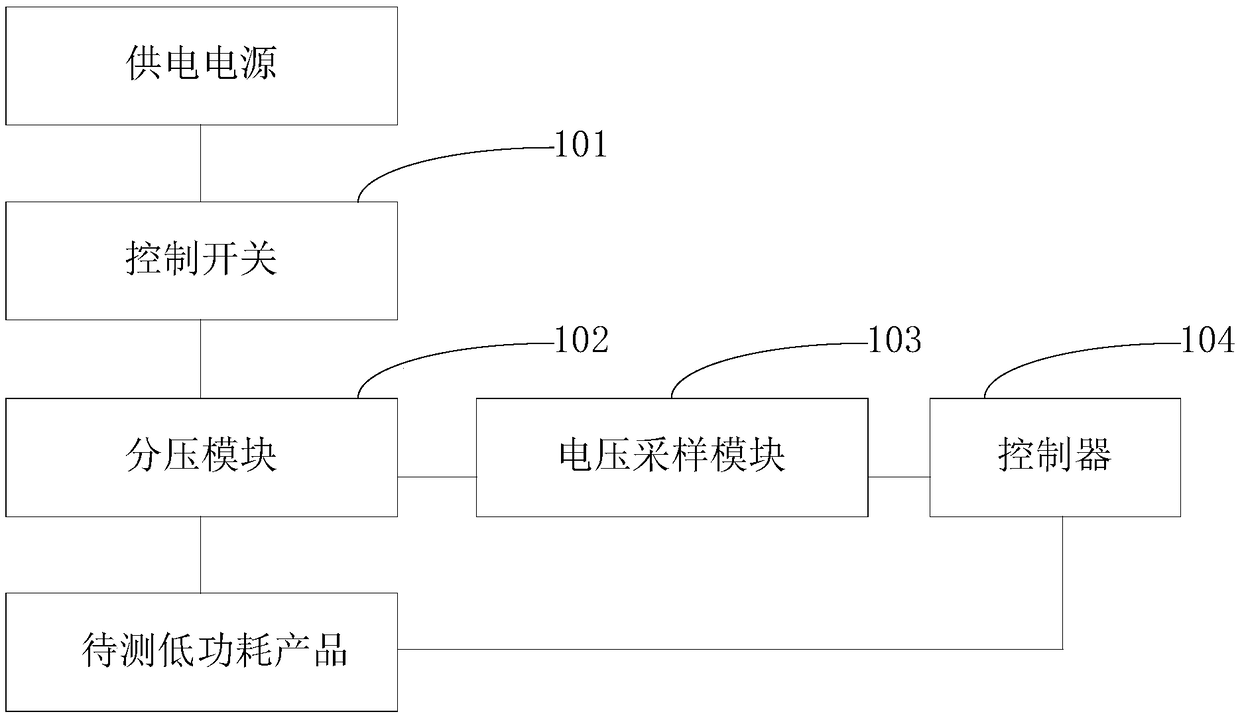

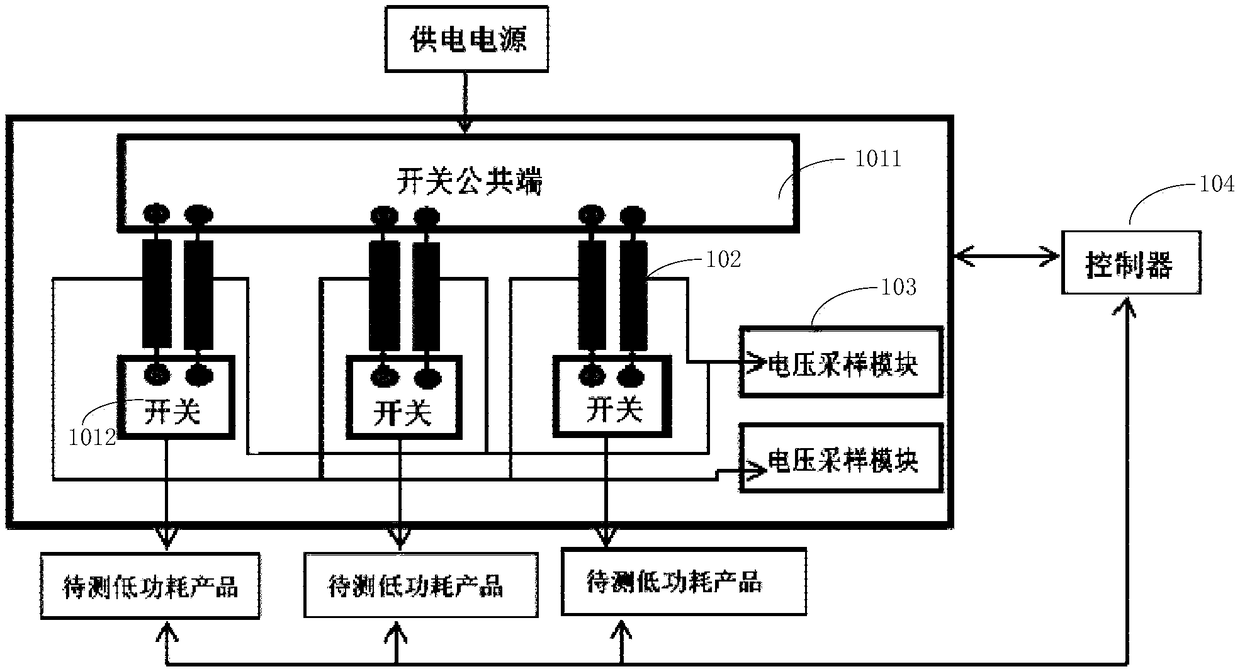

Low-power product detecting device

PendingCN108872748AAdjust the test current valueImplement testElectrical testingCurrent measurements onlyCurrent electricVoltage drop

The invention relates to a low-power product detecting device comprising a control switch, a voltage dividing module, a voltage sampling module and a controller. The control switch is used for controlling the on / off state of the control switch itself according to a control instruction. The voltage dividing module is used for controlling a resistance value between a power supply and a low-power product to be tested according to the on / off state of the control switch. The voltage sampling module is used for acquiring a voltage drop across the voltage dividing module. The controller is used for calculating the present current value of the low-power product to be tested according to the voltage drop and the resistance value of the voltage dividing module after a detection circuit formed by thepower supply, the control switch, the voltage dividing module, and the low-power product to be tested is turned on. The controller is used for determining whether the low-power product to be tested is qualified under a current operating condition according to the present current value. Therefore, it is possible to simultaneously detect a plurality of low-power products to be tested by the controlswitch and the voltage dividing module without adjusting the power supply, thereby improving the detection efficiency of the low-power products to be tested and achieving a simple operation mode.

Owner:SHENZHEN HASWARE TECH DEV CO LTD

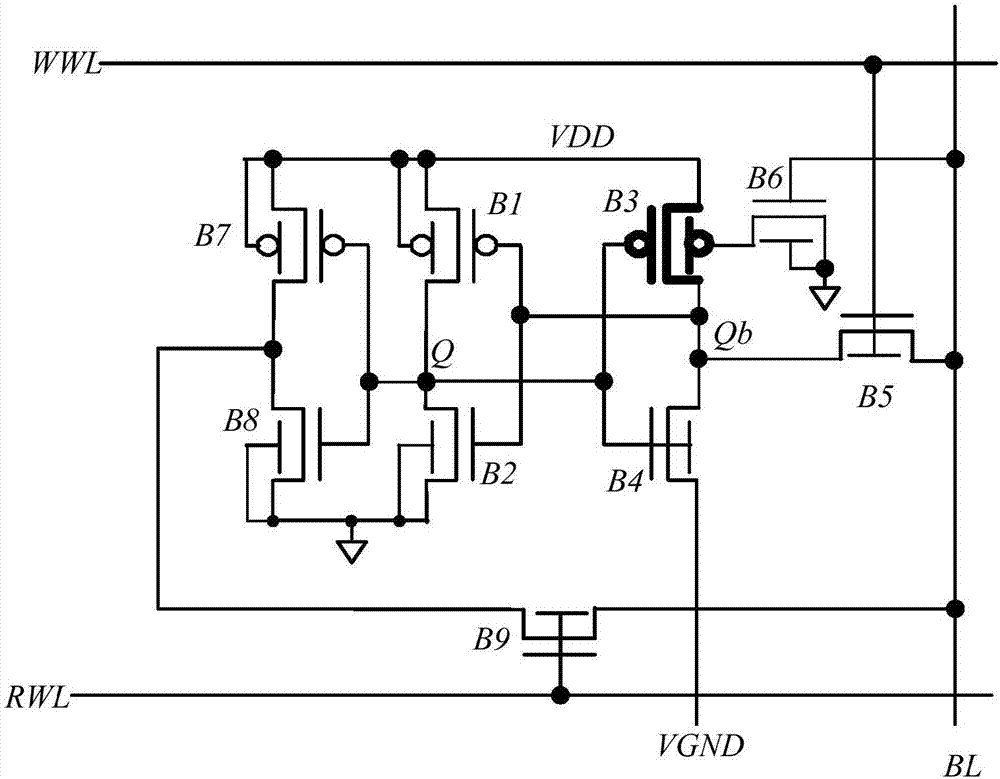

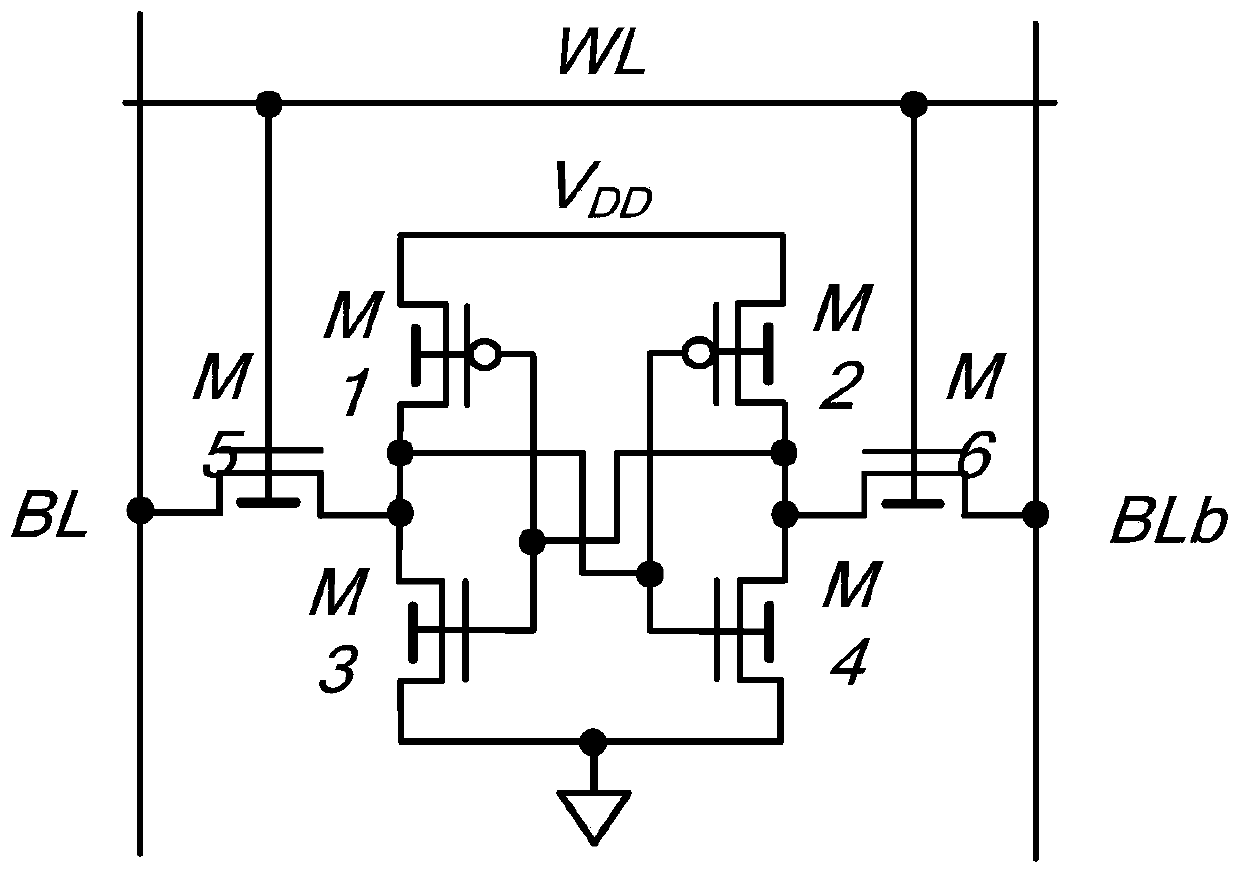

FinFET device-based full-swing single-end read storage unit

ActiveCN107393584AWill not interfere with the valueData will not be affectedDigital storageWrite bitData error

The invention discloses a FinFET device-based full-swing single-end read storage unit. The unit comprises a write word line, a writ bit line, an inverted write bit line, a read word line, a read bit line, a first FinFET, a second FinFET, a third FinFET, a fourth FinFET, a fifth FinFET, a sixth FinFET, a seventh FinFET, an eighth FinFET and a ninth FinFET, wherein the first FinFET, the second FinFET and the seventh FinFET are low-threshold P-type FinFETs; the third FinFET, the fourth FinFET, the fifth FinFET, the sixth FinFET and the ninth FinFET are low-threshold N-type FinFETs; and the eighth FinFET is a high-threshold N-type FinFET. The unit has the advantages that under the condition of not influencing a circuit function, the delay, the power consumption and a power-delay product are all relatively small, a data error does not occur during read operation, and the circuit stability is relatively high.

Owner:NINGBO UNIV

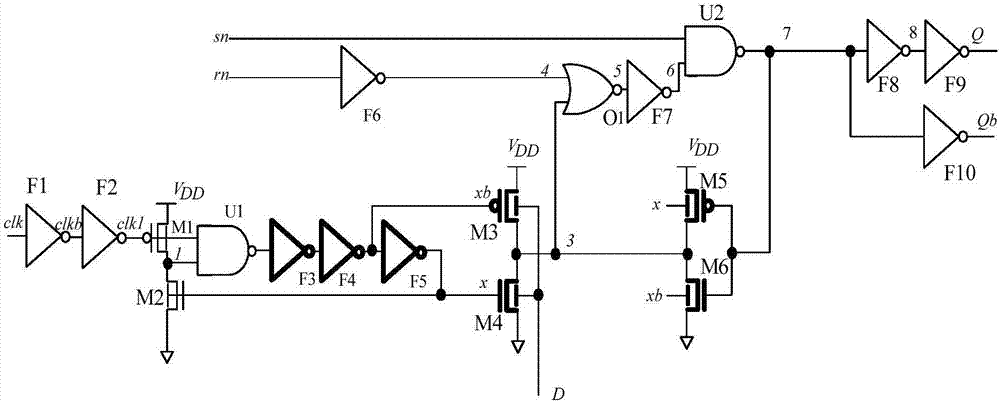

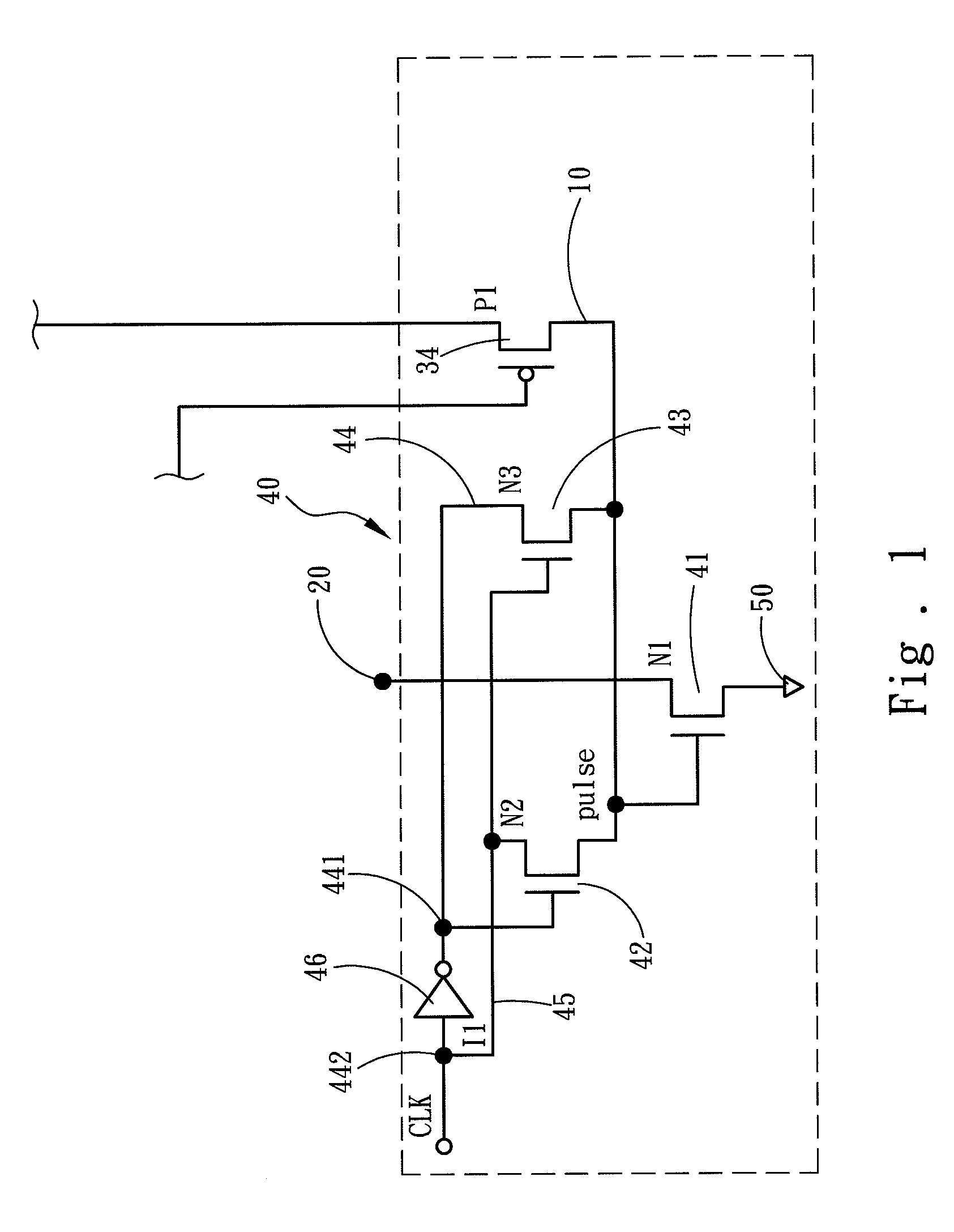

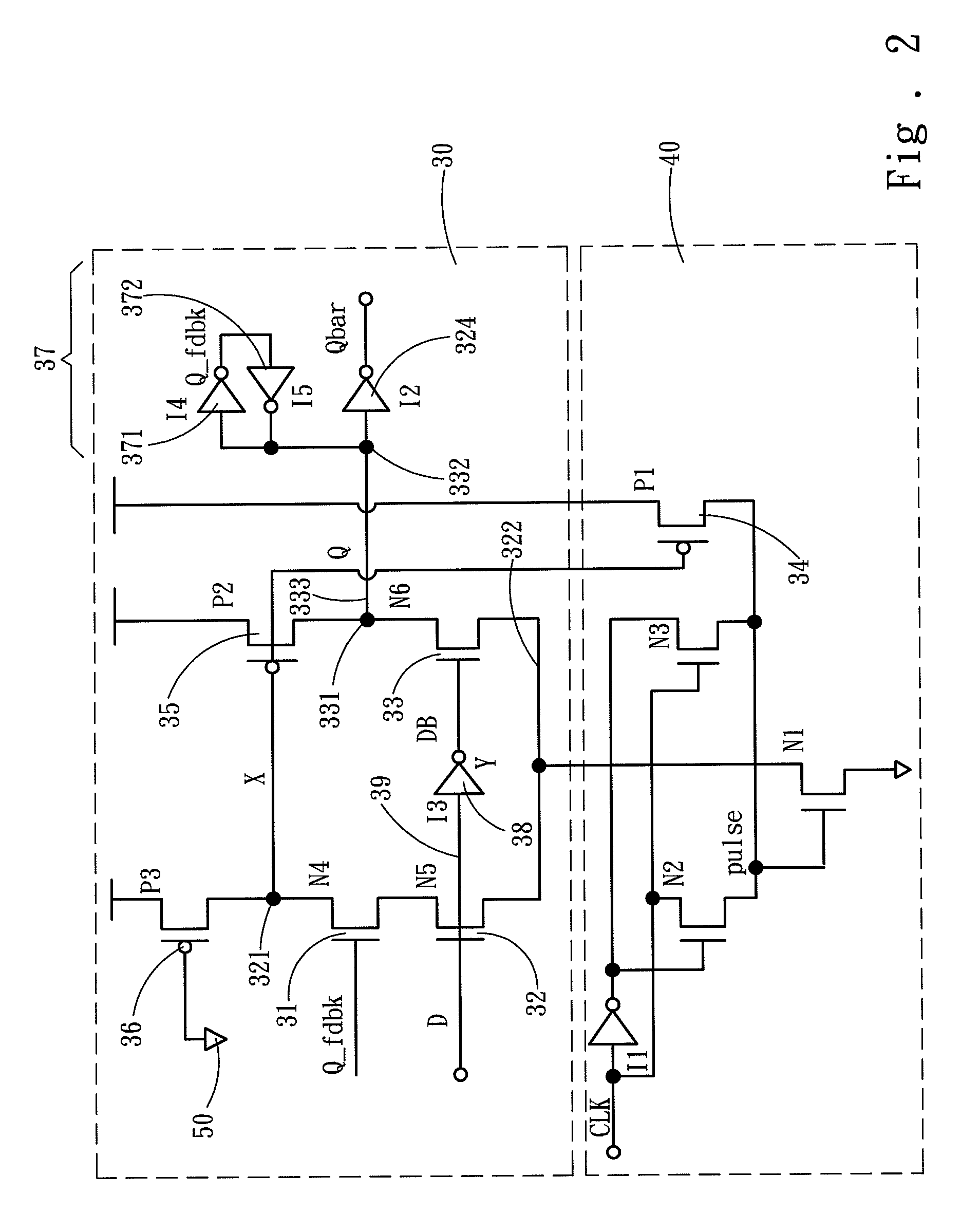

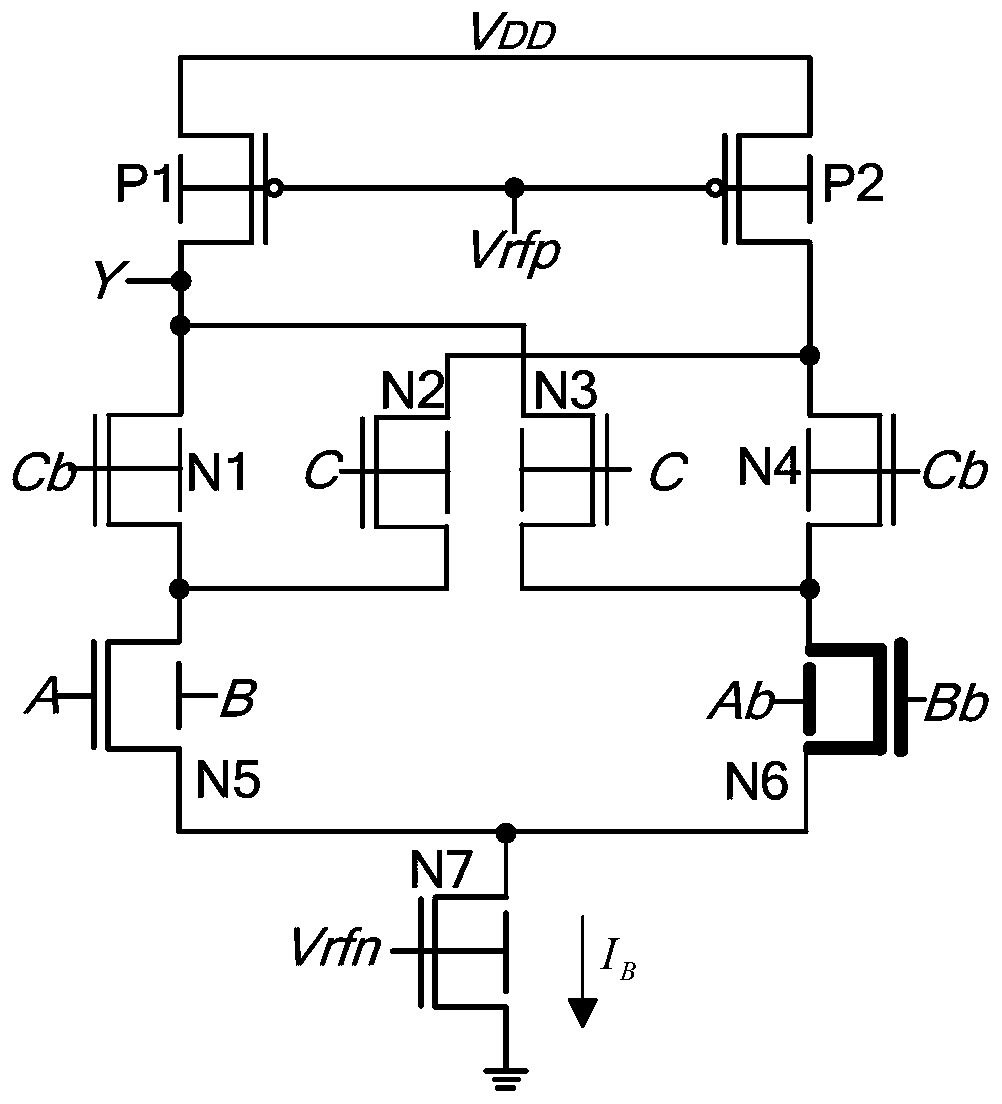

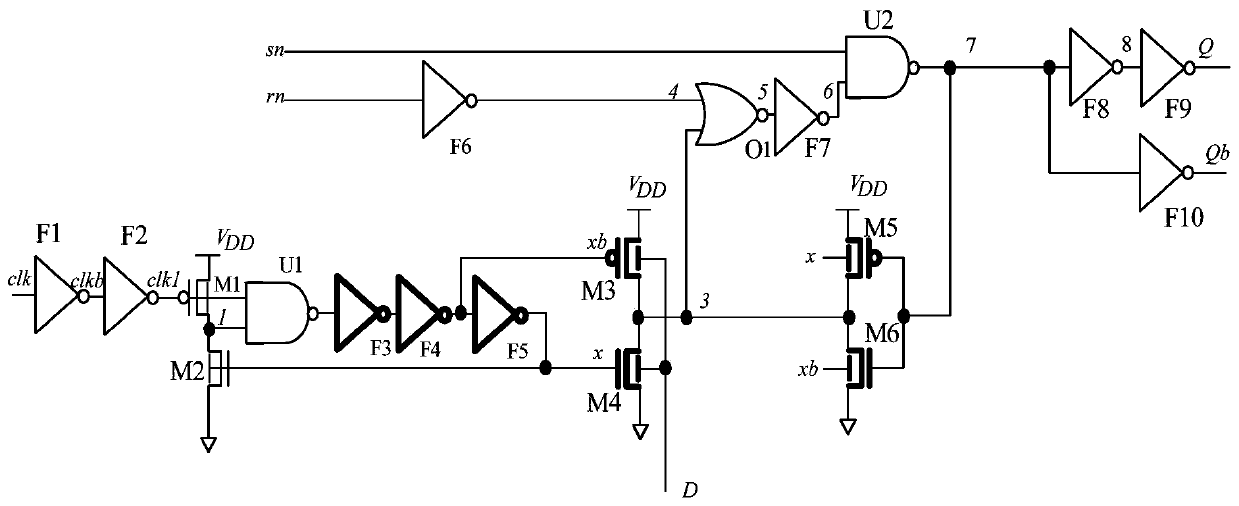

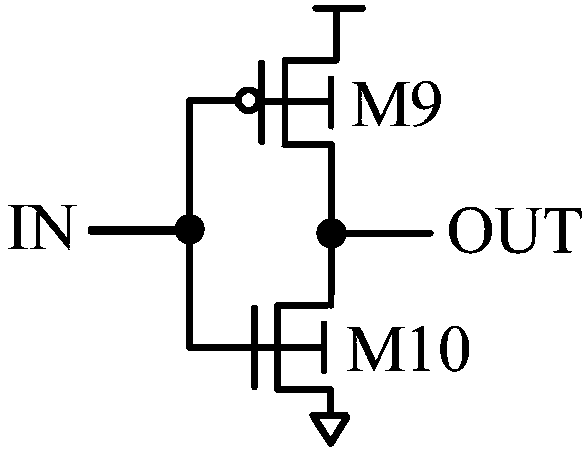

Low power pulse-triggered flip-flop

InactiveUS7961024B1Shorten the discharge pathReduce circuit power consumptionElectric pulse generatorEngineeringDrain current

A low power pulse-triggered flip-flop comprises a latch containing a first conductive line and a first connection point and a pulse generator linking to the latch. The pulse generator includes a first N-transistor, a second N-transistor, a third N-transistor, a first inverter and a first P-transistor located on the first conductive line. The first N-transistor is connected to the first connection point and first conductive line. The second N-transistor and the third N-transistor are connected to the first conductive line, a second conductive line and a third conductive line. The first inverter is connected to the second conductive line. The present invention aims to reduce leakage power in a high level fabrication process, and can save power consumption and power-delay-product more than 17% over the conventional pulse triggered flip-flop, and also provides a smaller size of total transistors to lower average leakage current power consumption by 2.4 times.

Owner:NATIONAL YUNLIN UNIVERSITY OF SCIENCE AND TECHNOLOGY

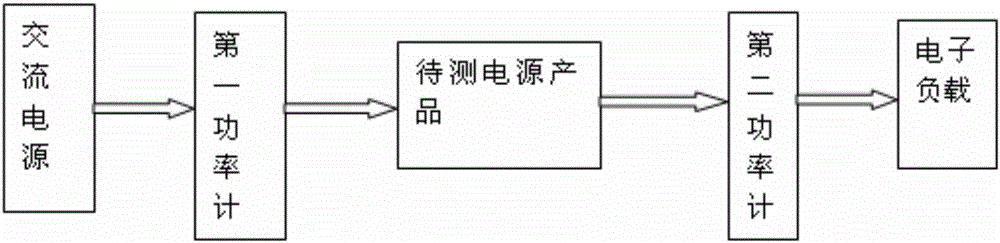

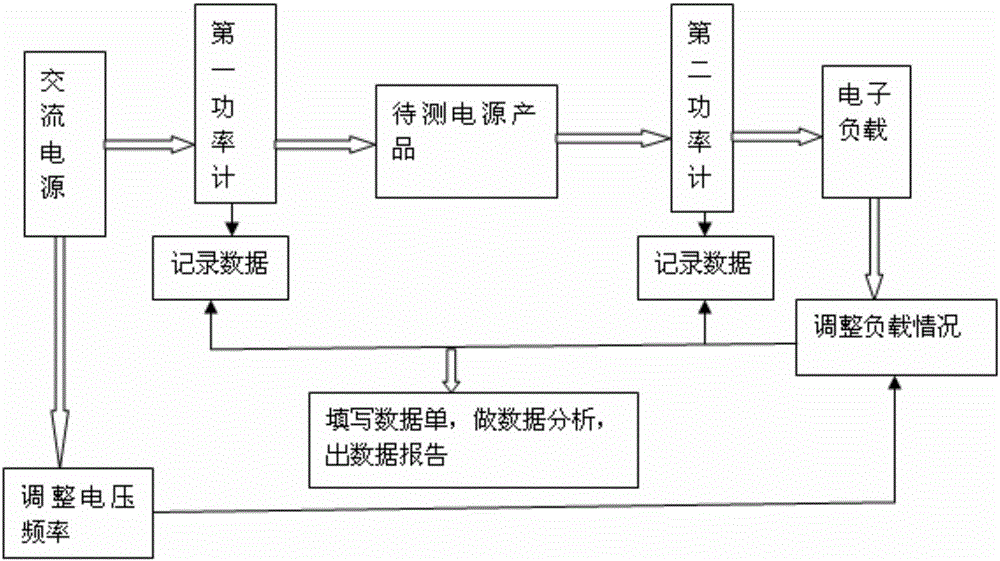

A power supply product energy efficiency automatic test method

InactiveCN105699914AImplement auto-completionReduce artificial adjustment of device status parametersPower supply testingTest efficiencyState parameter

The invention provides an automatic test method for the energy efficiency of power supply products. By setting the rated input voltage, frequency, rated output voltage and current value of the power supply products, and setting the energy efficiency level of the power supply products, the average efficiency value and standby time of the power supply products are obtained. Power value, and compare the obtained average efficiency value and standby power value of the power supply product with the minimum average efficiency value and minimum standby power value required in step 3, and use the values recorded in the above steps and the comparison results through the excel template The form of data report generated according to the requirements realizes the automatic completion of the energy efficiency test of power supply products, reduces the manual adjustment of equipment status parameters, and improves the accuracy and efficiency of the test.

Owner:UNIONTRUST LAB

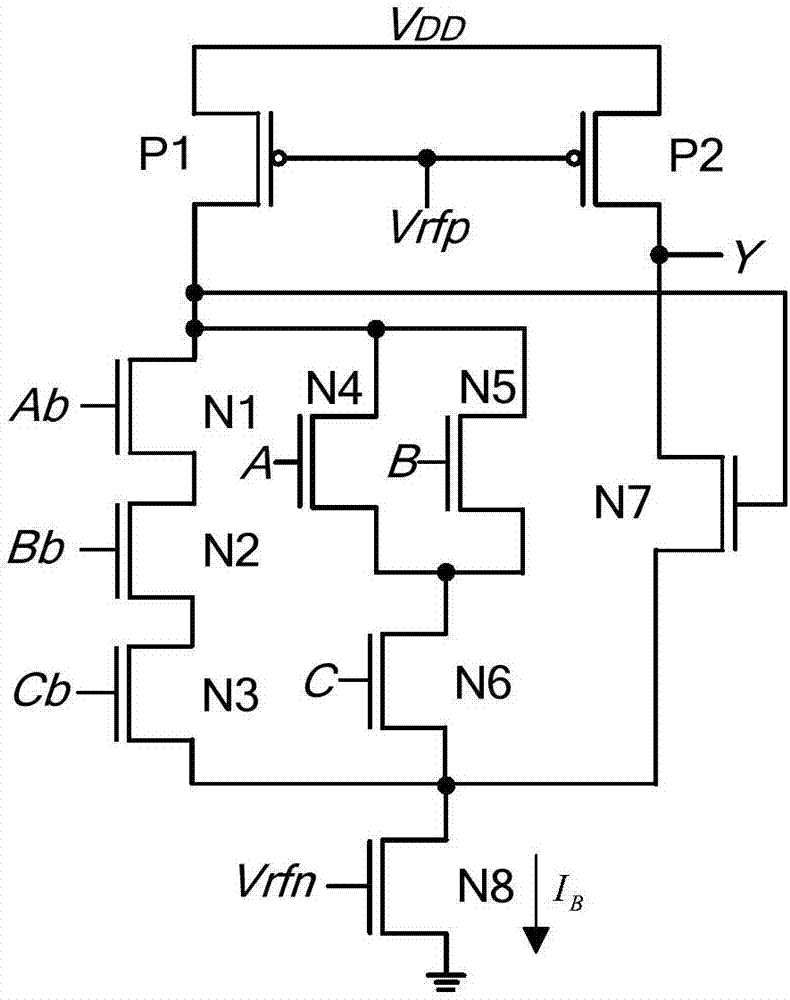

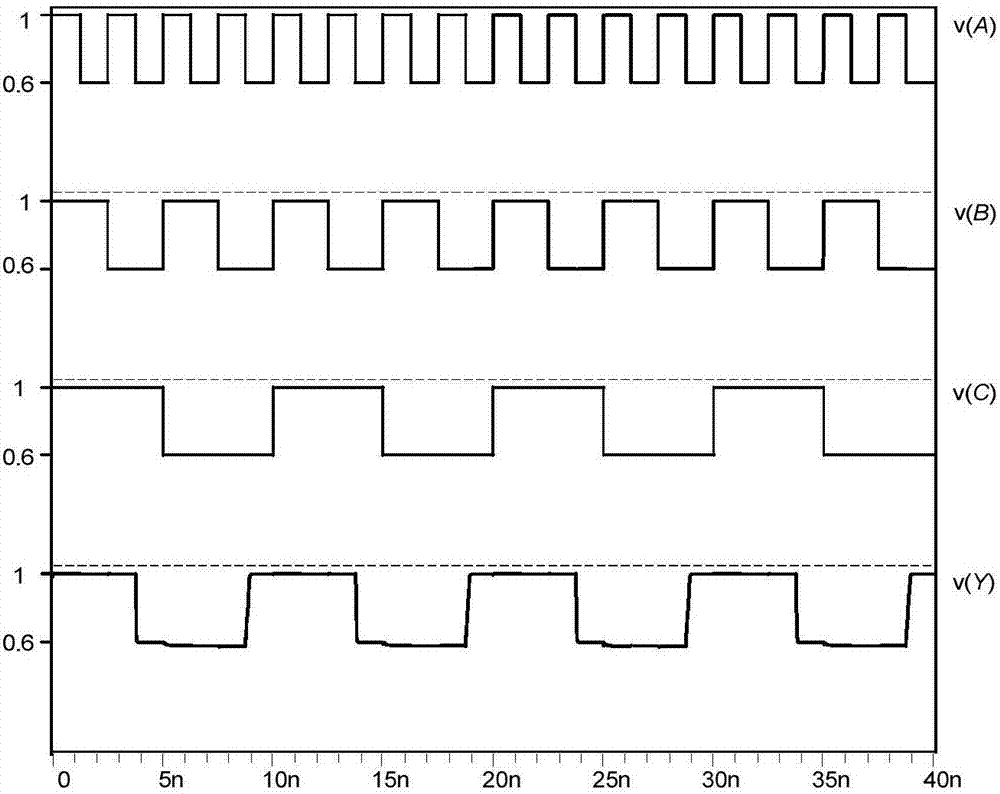

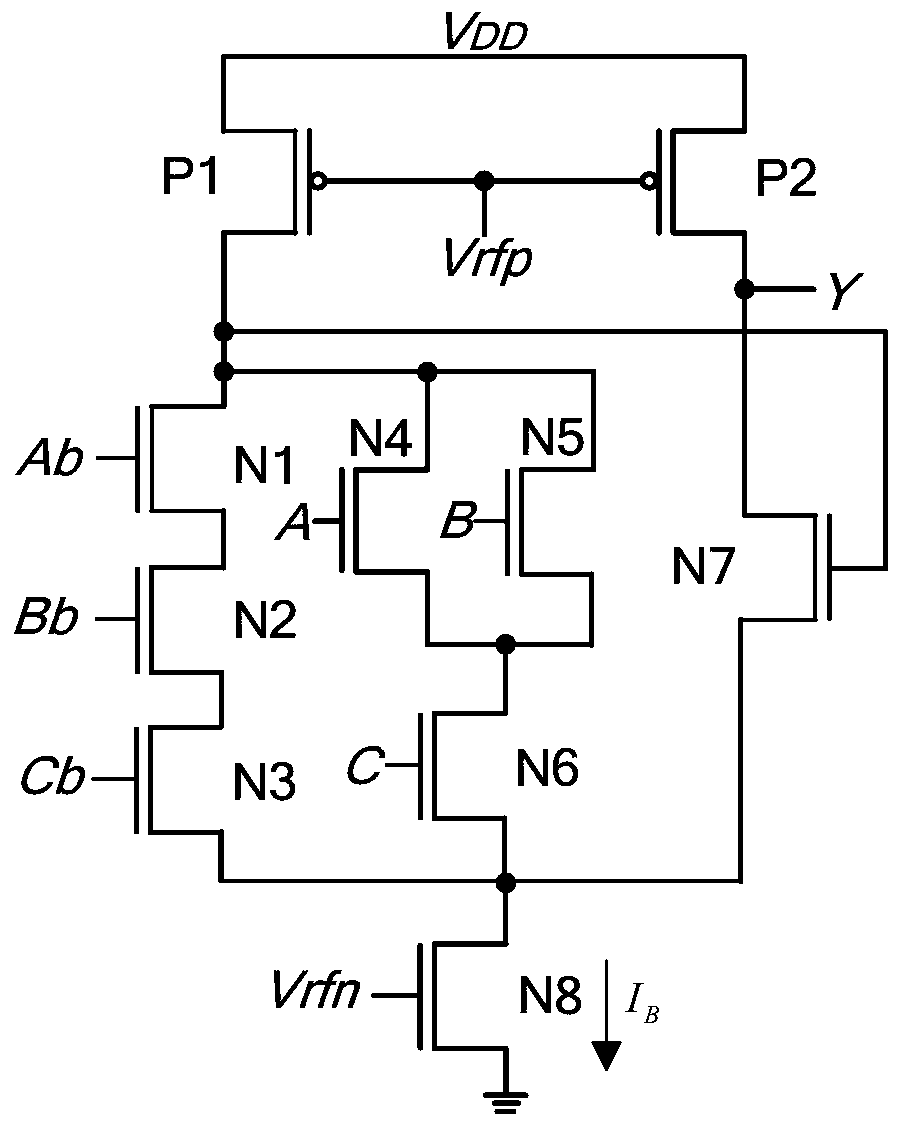

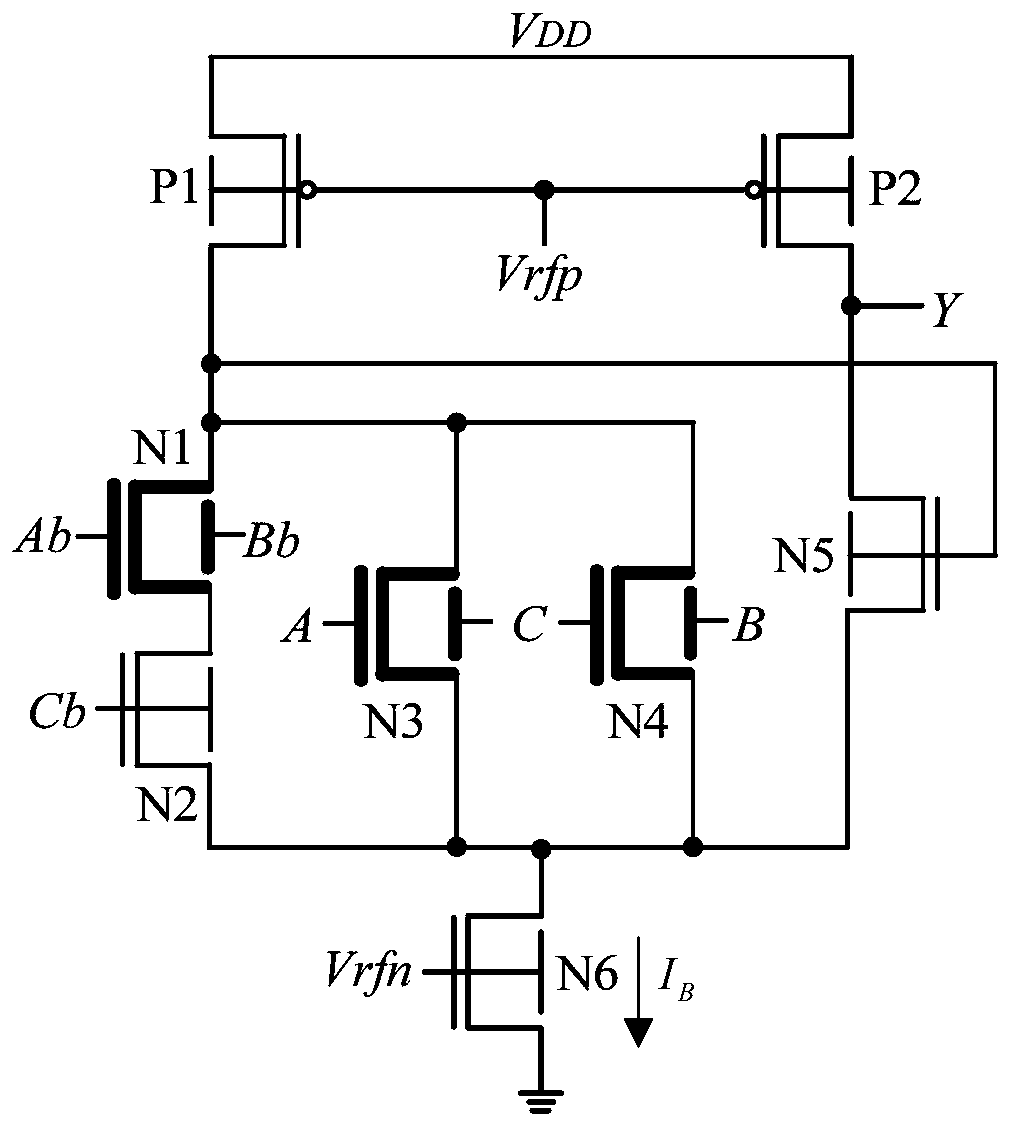

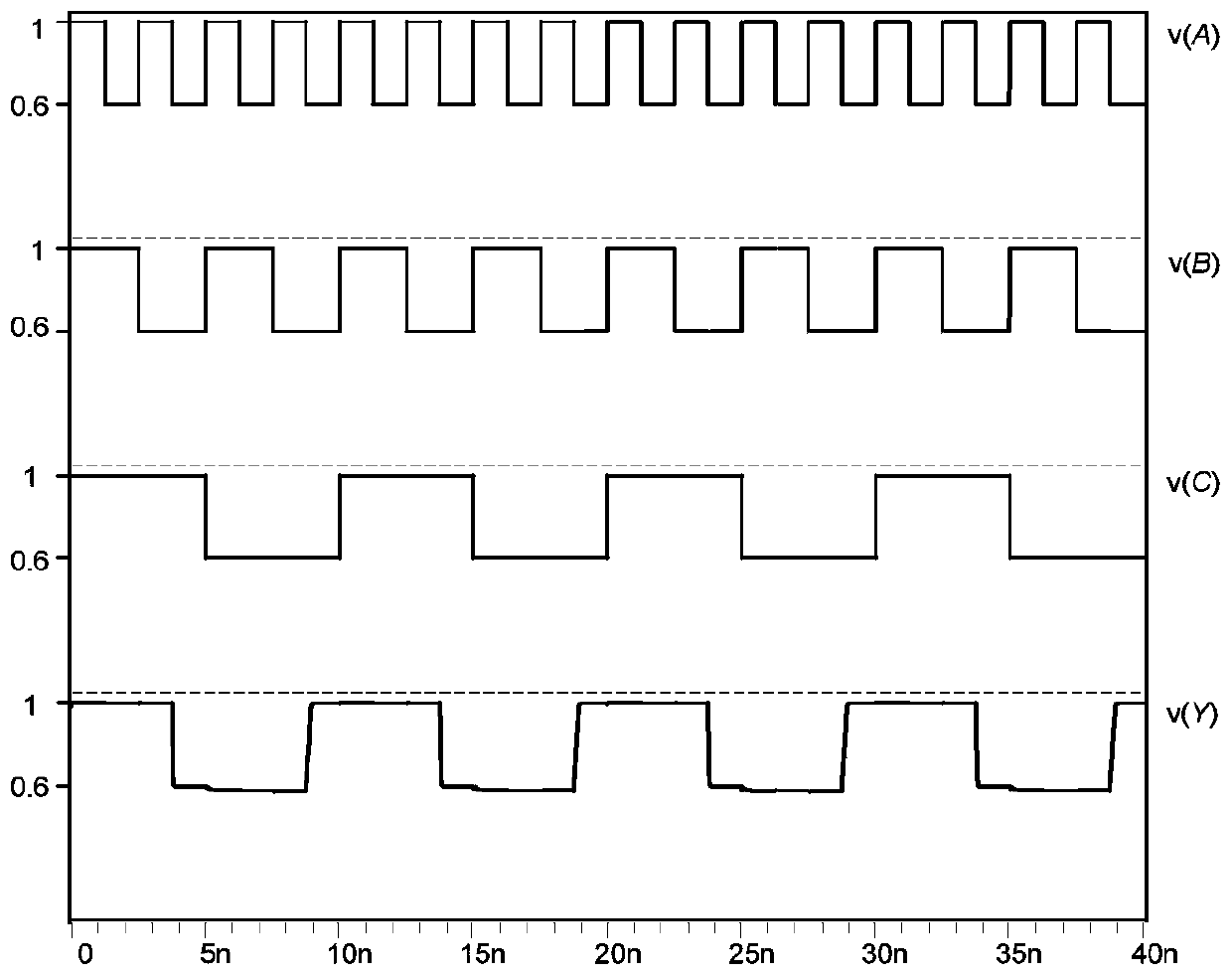

Current-mode RM NOR-XOR unit based on FinFET device

ActiveCN107222200AReduce areaLower latencyLogic circuits characterised by logic functionEngineeringCurrent mode

The invention discloses a current-mode RM NOR-XOR unit based on a FinFET device. The current-mode RM NOR-XOR unit comprises the first P-type FinFET tube, the second P-type FinFET tube, the first N-type FinFET tube, the second N-type FinFET tube, the third N-type FinFET tube, the fourth N-type FinFET tube, the fifth N-type FinFET tube and the sixth N-type FinFET tube, wherein the first P-type FinFET tube and the second P-type FinFET tube are respectively the low-threshold P-type FinFET tube; the first N-type FinFET tube, the third N-type FinFET tube and the fourth N-type FinFET tube are respectively the high-threshold N-type FinFET tube; the second N-type FinFET tube, the fifth N-type FinFET tube and the sixth N-type FinFET tube are respectively the low-threshold N-type FinFET tube. The current-mode RM NOR-XOR unit disclosed by the invention has the advantage that the circuit area, the time delay, the power consumption and the power delay product are small on the basis of the correct logic function.

Owner:NINGBO UNIV

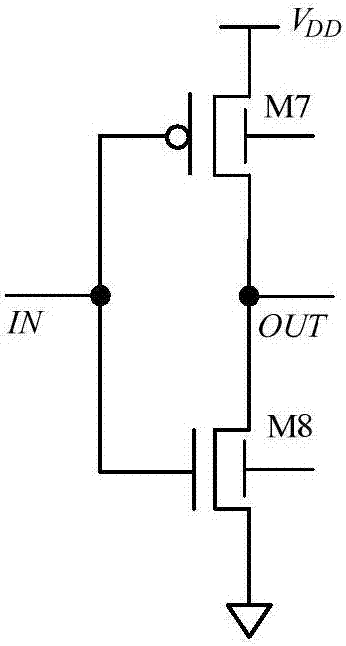

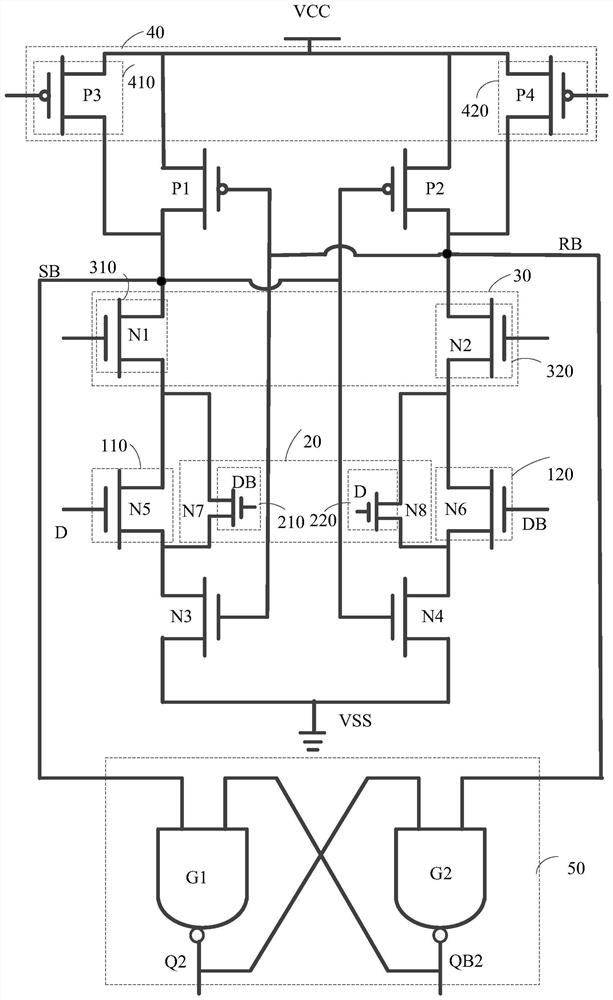

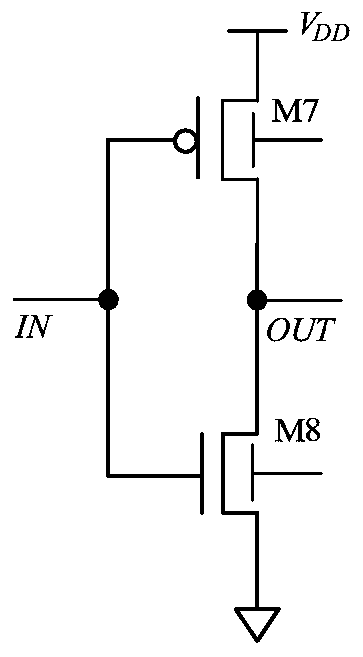

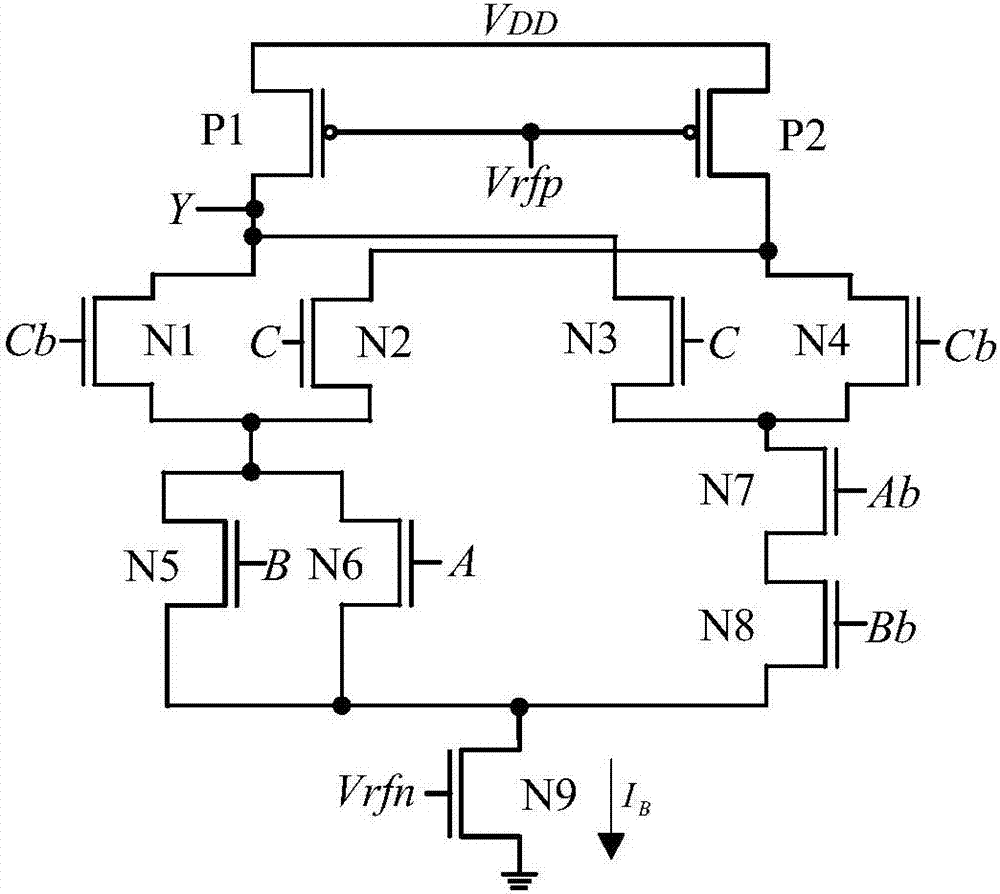

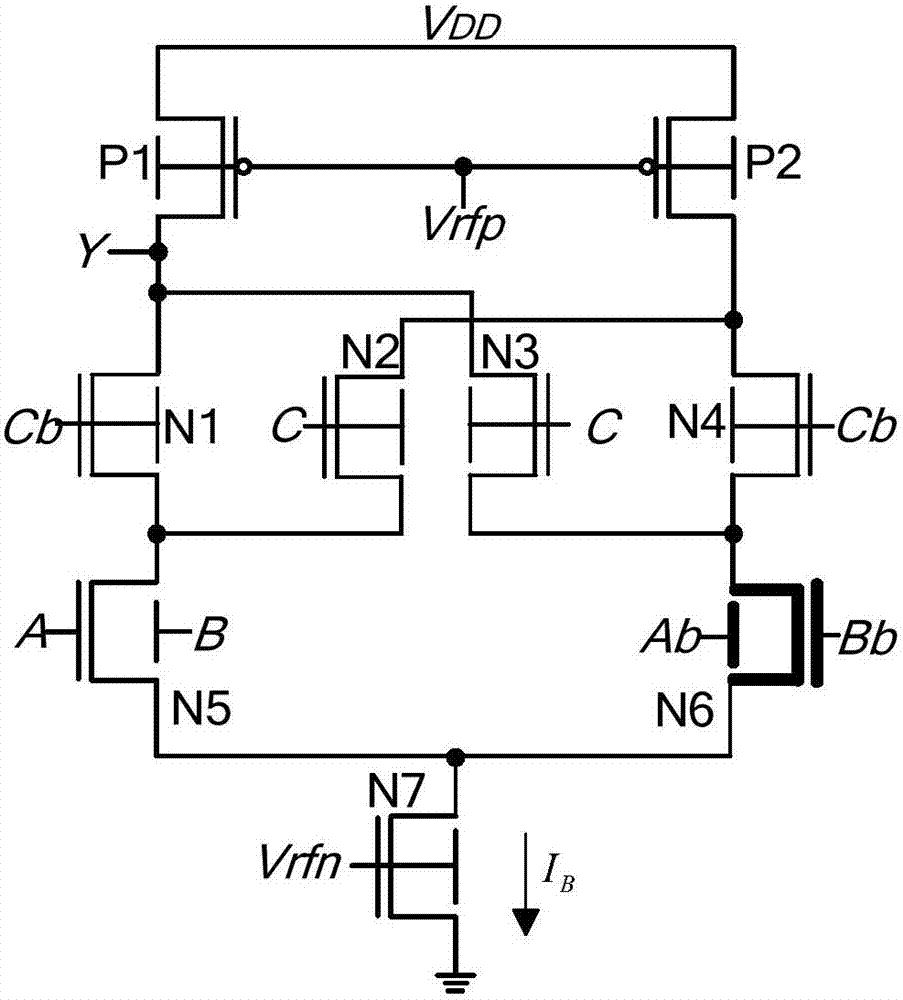

Amplification circuit

PendingCN114583925AReduce power lossReduced Power Delay ProductAmplifier modifications to raise efficiencyDifferential amplifiersControl engineeringHemt circuits

The invention provides an amplification circuit, which comprises an isolation module, a sampling module, a charging module and a sensing module, the isolation module is used for isolating a first power supply end and a second power supply end based on an isolation signal, and the sampling module is used for reading input data; the charging module is used for coupling the first output end and the second output end to a first power supply end based on a charging signal, and charging the first output end and the second output end to initial voltage; and the sensing module is used for amplifying the input data based on the amplification signal, the first output end with the initial voltage, the second output end with the initial voltage and the second power supply end, so that the power loss can be reduced, the discharge rate can be improved, and the power delay product can be reduced.

Owner:CHANGXIN MEMORY TECH INC

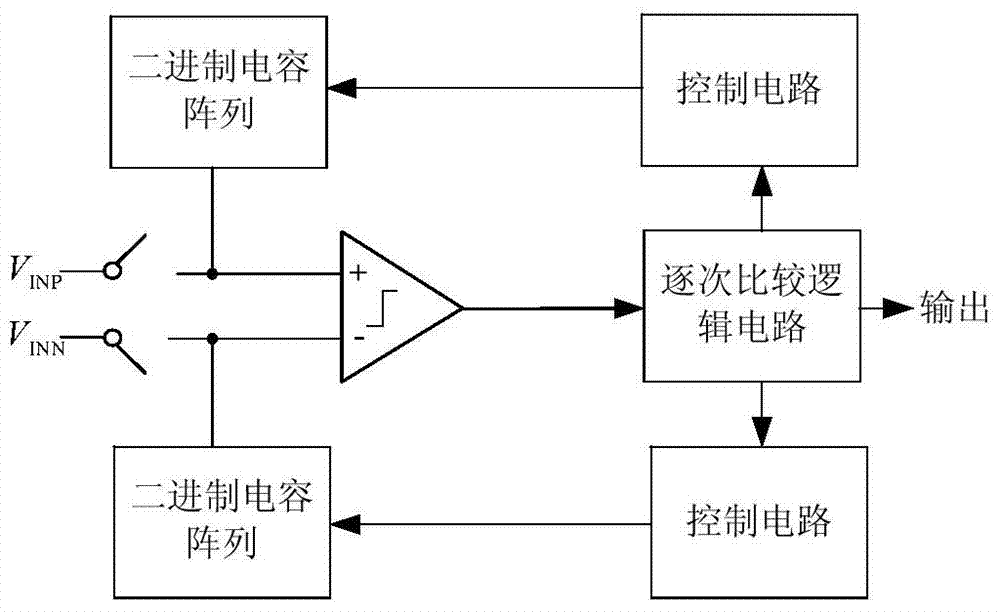

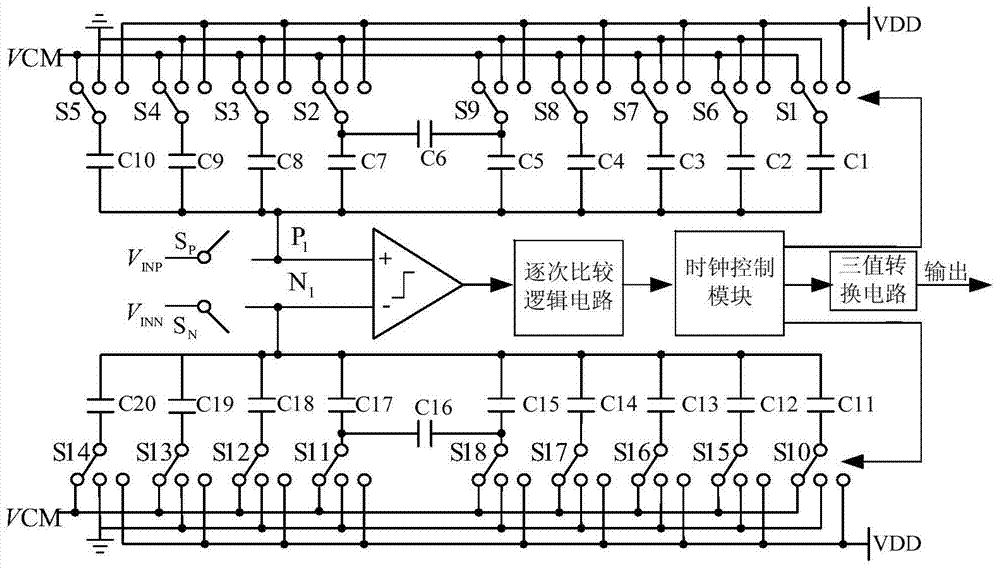

A Ternary Carbon Nanoscale Field-Effect Transistor Successive Approximation Analog-to-Digital Converter

ActiveCN104702288BReduce power consumptionRealize charging and discharging operationAnalogue/digital conversionElectric signal transmission systemsCapacitanceCarbon nanotube

The invention discloses a ternary carbon nanotube successive approximation analog-to-digital converter, which comprises a latch comparator, a successive comparison logic circuit, a control circuit, a first capacitor array and a second capacitor array, and the output of the lock comparator terminal is connected with the input end of the successive comparison logic circuit, and the output end of the successive comparison logic circuit is connected with the control circuit, the first capacitor array and the second capacitor array are three-valued capacitor arrays, and the first capacitor array and the second capacitor array are controlled by the control circuit The capacitor array is connected to three different voltages, which realizes the charging and discharging operation of different capacitor arrays, effectively avoids the invalid operation of the switch, and greatly reduces the power consumption of the circuit. The latch comparator utilizes the high-speed and low-power consumption characteristics of CNFET , use CNFET to design, further reduce energy consumption and power delay product; the advantages of energy consumption and power delay product are small, which is of positive significance for further research on larger-scale low-power three-valued successive approximation analog-to-digital converters.

Owner:NINGBO UNIV

A full-swing single-ended read memory cell based on finfet device

ActiveCN107393584BWill not interfere with the valueData will not be affectedDigital storageData errorPower–delay product

The invention discloses a FinFET device-based full-swing single-end read storage unit. The unit comprises a write word line, a writ bit line, an inverted write bit line, a read word line, a read bit line, a first FinFET, a second FinFET, a third FinFET, a fourth FinFET, a fifth FinFET, a sixth FinFET, a seventh FinFET, an eighth FinFET and a ninth FinFET, wherein the first FinFET, the second FinFET and the seventh FinFET are low-threshold P-type FinFETs; the third FinFET, the fourth FinFET, the fifth FinFET, the sixth FinFET and the ninth FinFET are low-threshold N-type FinFETs; and the eighth FinFET is a high-threshold N-type FinFET. The unit has the advantages that under the condition of not influencing a circuit function, the delay, the power consumption and a power-delay product are all relatively small, a data error does not occur during read operation, and the circuit stability is relatively high.

Owner:NINGBO UNIV

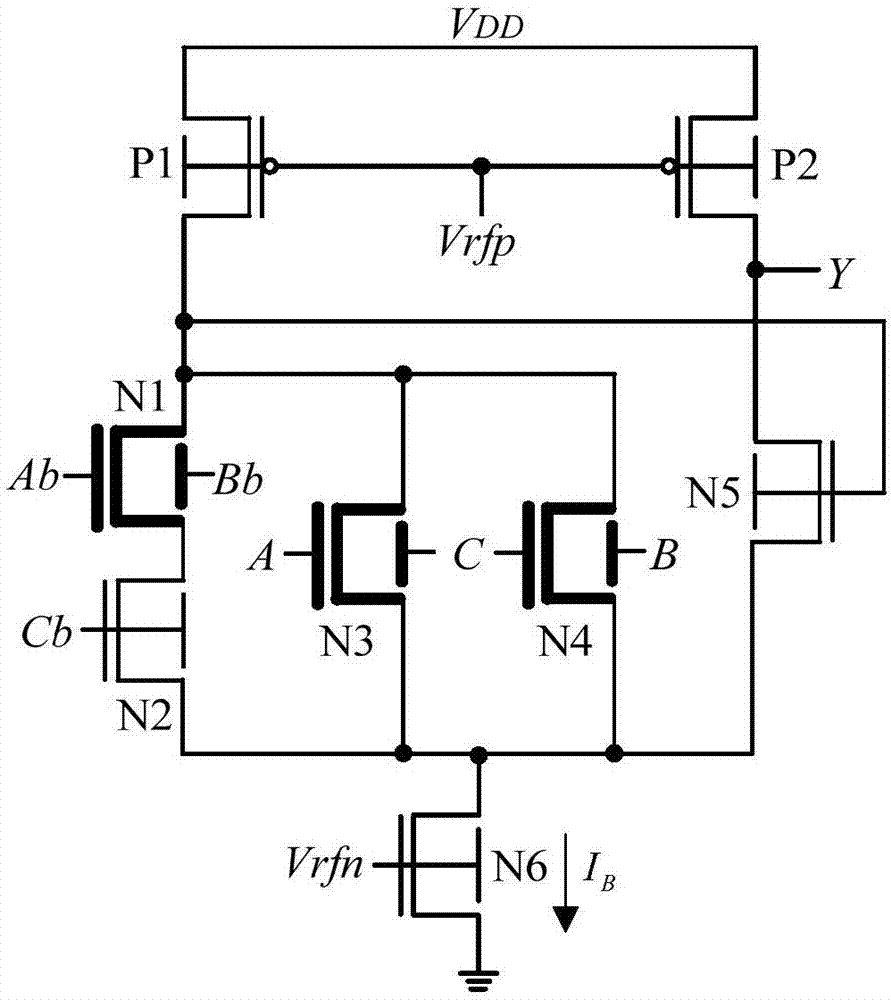

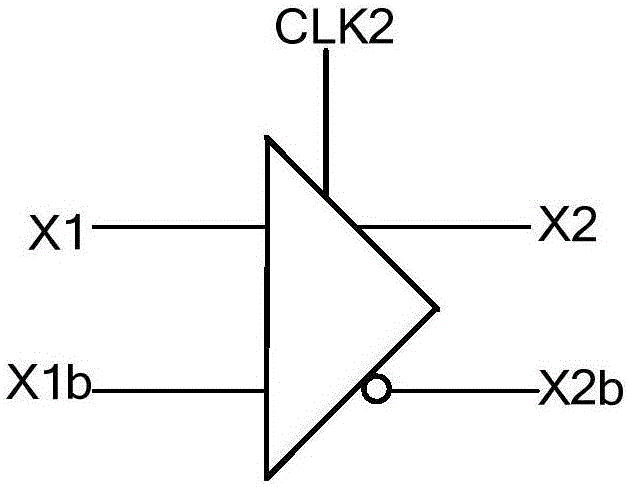

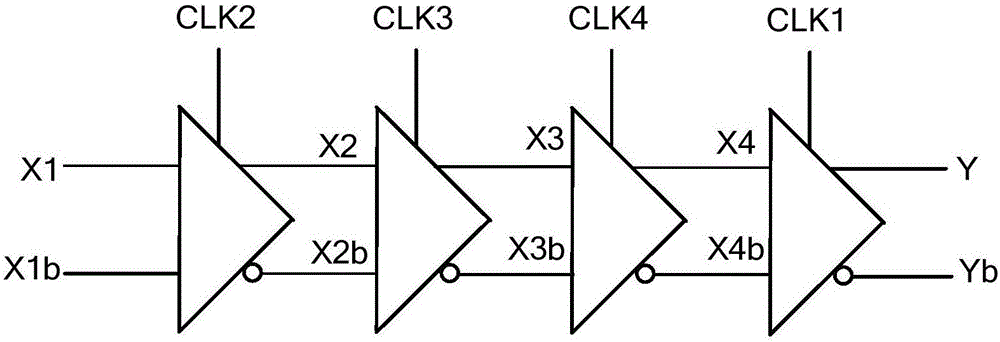

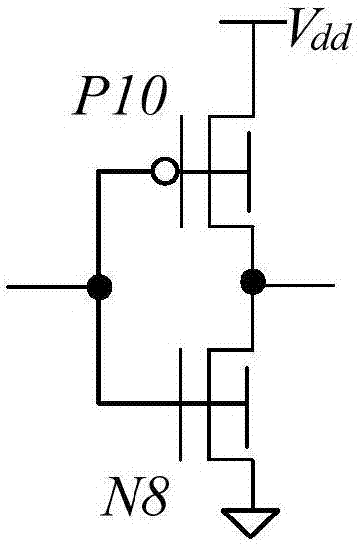

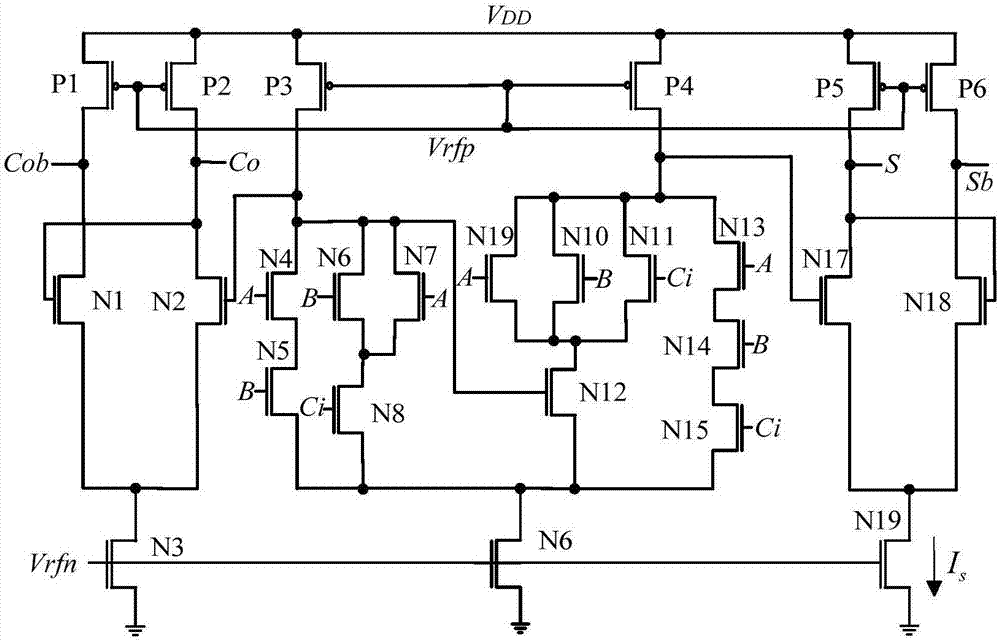

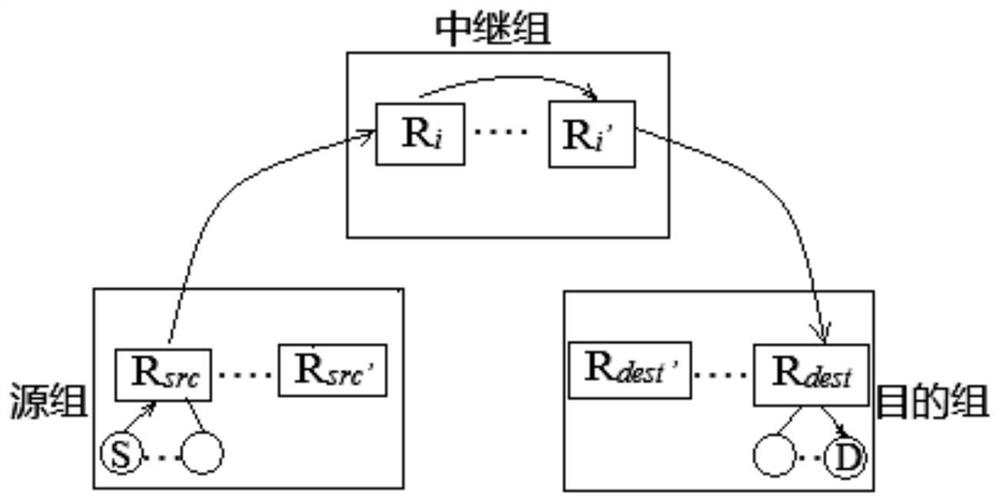

A controllable diode bootstrap adiabatic circuit and four-stage inverter/buffer

The invention discloses a controllable diode bootstrap adiabatic circuit and a four-level inverter / buffer. The controllable diode bootstrap adiabatic circuit comprises a first PMOS tube, a second PMOS tube, a first NMOS tube, a second NMOS tube, a third NMOS tube, a fourth NMOS tube, a fifth NMOS tube, and a sixth NMOS tube. The four-level inverter / buffer comprises four controllable diode bootstrap adiabatic circuits. The advantages are as follows: a smaller number of MOS tubes are used, the circuit structure is simple, and the time delay and power consumption are reduced; and the fifth NMOS tube and the sixth NMOS tube constitute a controllable diode feedback path between the output end and the clock end of the controllable diode bootstrap adiabatic circuit, so that energy can be fully recycled, and the time delay, power consumption and power-delay product are smaller on the basis that the circuit performance is not affected.

Owner:NINGBO UNIV

Current mode rm or non-exclusive or unit circuit based on finfet transistor

ActiveCN107222204BReduce areaLower latencyLogic circuits characterised by logic functionHemt circuitsEngineering

The invention discloses a current mode RM or non- xor unit based on a FinFET transistor. The current mode RM or non- xor unit comprises a first P type FinFET tube, a second P type FinFET tube, a first N type FinFET tube, a second N type FinFET tube, a third N type FinFET tube, a fourth N type FinFET tube, a fifth N type FinFET tube, a sixth N type FinFET tube and a seventh N type FinFET tube, wherein the first P type FinFET tube and the second P type FinFET tube are low-threshold P type FinFET tubes, the first N type FinFET tube, the second N type FinFET tube, the third N type FinFET tube, the fourth N type FinFET tube, the fifth N type FinFET tube, the sixth N type FinFET tube and the seventh N type FinFET tube are high-threshold N type FinFET tubes. The current mode RM or non- xor unit has the advantages that the circuit area, the delay, the power consumption and the power delay product are smaller on the basis of a current logic function.

Owner:NINGBO UNIV

Controllable diode bootstrap adiabatic circuit and four-level inverter/buffer

The invention discloses a controllable diode bootstrap adiabatic circuit and a four-level inverter / buffer. The controllable diode bootstrap adiabatic circuit comprises a first PMOS tube, a second PMOS tube, a first NMOS tube, a second NMOS tube, a third NMOS tube, a fourth NMOS tube, a fifth NMOS tube, and a sixth NMOS tube. The four-level inverter / buffer comprises four controllable diode bootstrap adiabatic circuits. The advantages are as follows: a smaller number of MOS tubes are used, the circuit structure is simple, and the time delay and power consumption are reduced; and the fifth NMOS tube and the sixth NMOS tube constitute a controllable diode feedback path between the output end and the clock end of the controllable diode bootstrap adiabatic circuit, so that energy can be fully recycled, and the time delay, power consumption and power-delay product are smaller on the basis that the circuit performance is not affected.

Owner:NINGBO UNIV

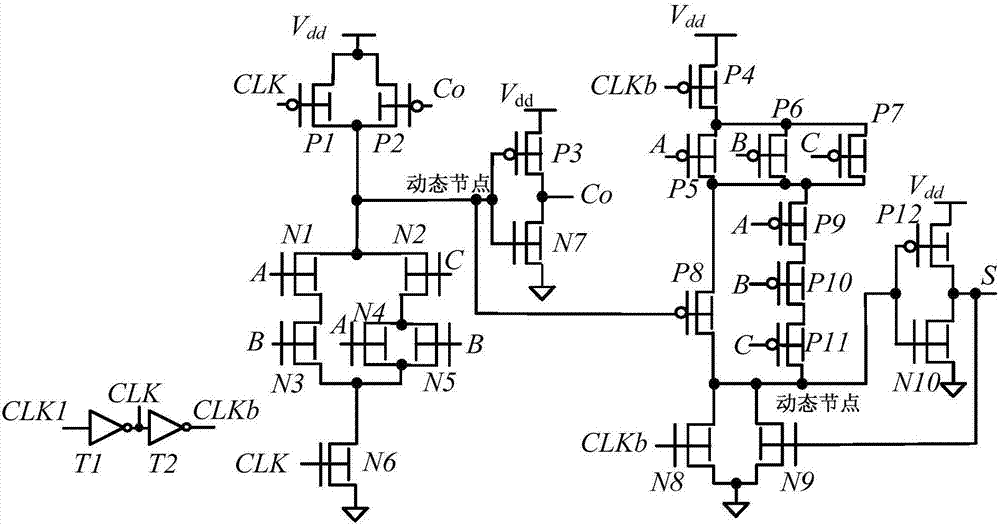

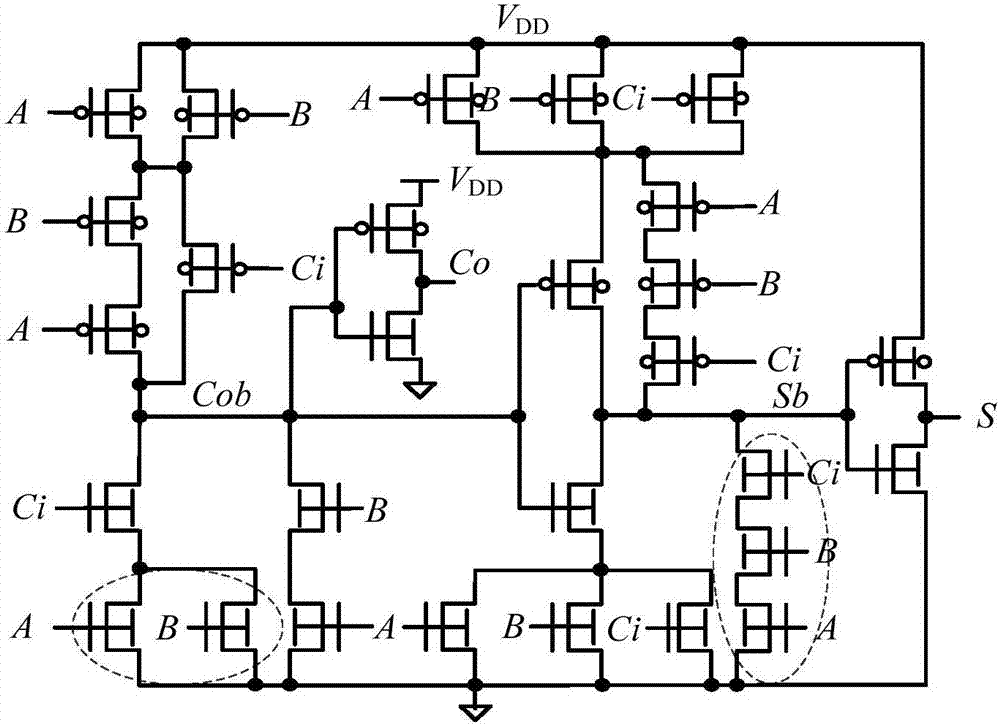

Full adder based on FinFET device

InactiveCN107222202AReduce stack heightLower latencyLogic circuits characterised by logic functionDigital data processing detailsEngineeringPower–delay product

The invention discloses a full adder based on a FinFET device. The full adder comprises a first N type FinFET tube, a second N type FinFET tube, a third N type FinFET tube, a fourth N type FinFET tube, a fifth N type FinFET tube, a sixth N type FinFET tube, a seventh N type FinFET tube, a first P type FinFET tube, a second P type FinFET tube, a third P type FinFET tube, a fourth P type FinFET tube, a fifth P type FinFET tube, a sixth P type FinFET tube, a seventh P type FinFET tube, an eighth P type FinFET tube, a ninth P type FinFET tube, a first inverter and a second inverter. The full adder has the advantages that the circuit area, the delay, the power consumption and the power delay product are smaller without affecting the circuit performance.

Owner:NINGBO UNIV

A short-pulse d flip-flop based on finfet device

The invention discloses a short-pulse type D trigger based on FinFET device. The short-pulse type D trigger comprises a first FinFET tube, a second FinFET tube, a third FinFET tube, a fourth FinFET tube, a fifth FinFET tube, a sixth FinFET tube, a first phase inverter, a second phase inverter, a third phase inverter, a fourth phase inverter, a fifth phase inverter, a sixth phase inverter, a seventh phase inverter, a seventh phase inverter, an eighth phase inverter, a ninth phase inverter, a tenth phase inverter, a first two-input NOR gate, a first two-input XOR gate and a second two-input XOR gate, wherein each of the first two-input NOR gate, the first two-input XOR gate and the second two-input XOR gate is provided with a first input, a second input and an output end; the short-pulse type D trigger has the advantages that the number of the FinFET tube is reduced, the circuit delay and the circuit area are further optimized since the series connection of the transistor is reduced; therefore, the circuit area, the time delay, the power consumption and the power delay product are small under the condition of not influencing the circuit performance.

Owner:NINGBO UNIV

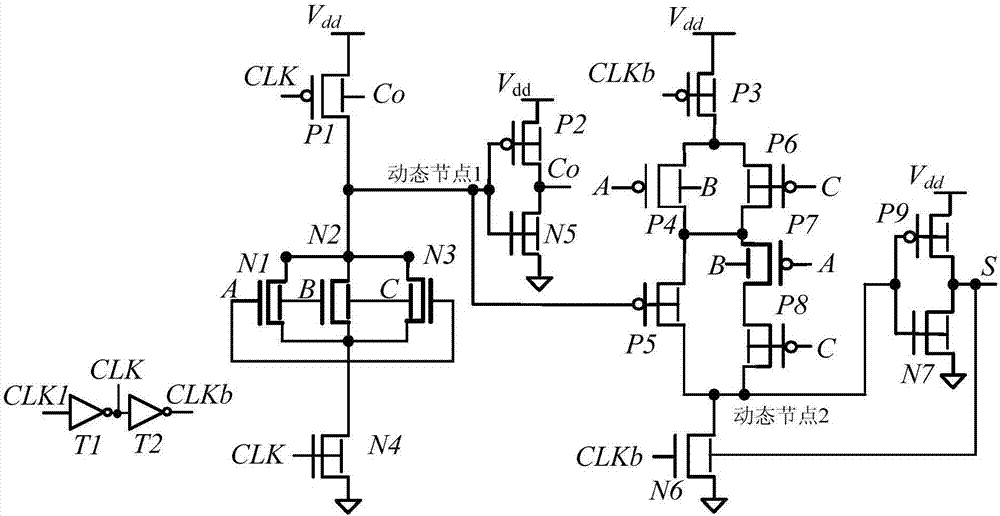

Current mode single-digit full adder based on FinFET transistor

InactiveCN107222203AReduce the numberReduce areaLogic circuits characterised by logic functionDigital data processing detailsEngineeringCurrent mode

The invention discloses a current mode single-digit full adder based on a FinFET transistor. The current mode single-digit full adder comprises a first P type FinFET tube, a second P type FinFET tube, a third P type FinFET tube, a fourth P type FinFET tube, a first N type FinFET tube, a second N type FinFET tube, a third N type FinFET tube, a fourth N type FinFET tube, a fifth N type FinFET tube, a sixth N type FinFET tube, a seventh N type FinFET tube, an eighth N type FinFET tube, a ninth N type FinFET tube, a tenth N type FinFET tube and an eleventh N type FinFET tube. The current mode single-digit full adder has the advantages that the circuit area, the delay, the power consumption and the power delay product are smaller.

Owner:NINGBO UNIV

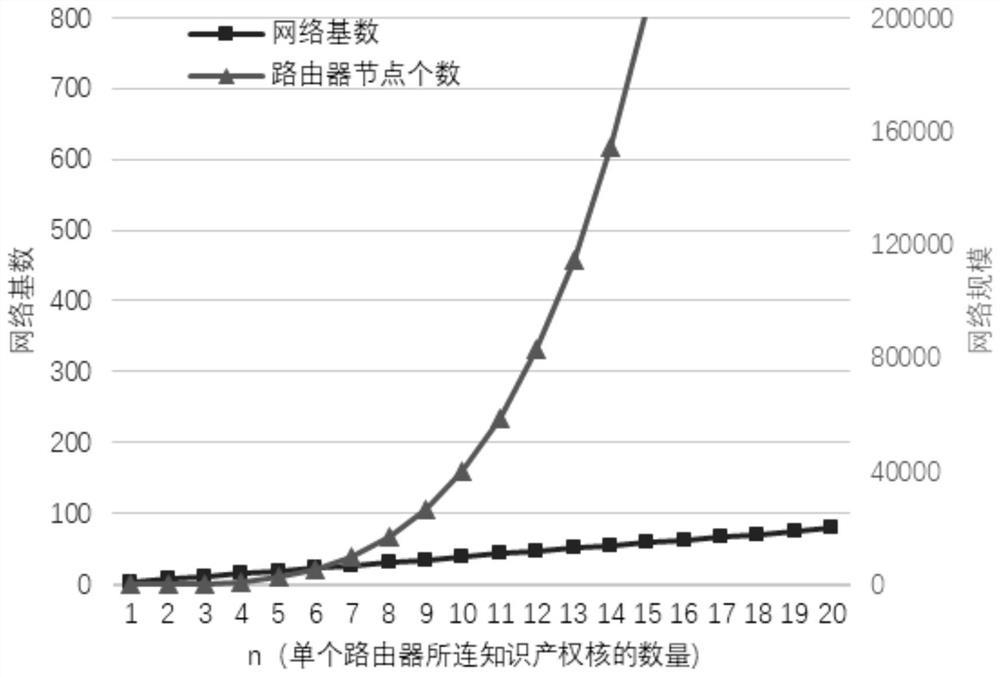

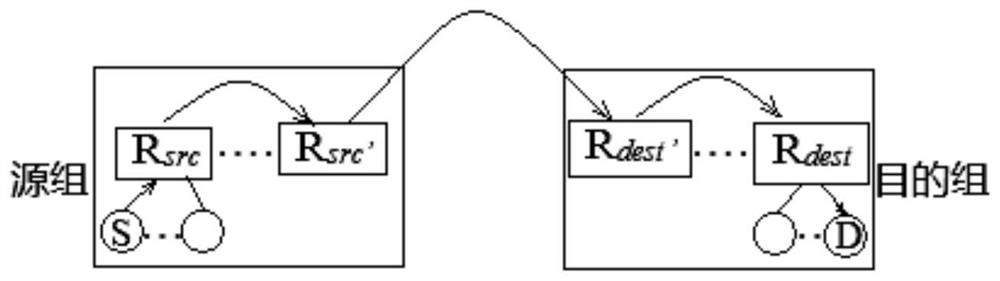

Power-aware dynamic adaptive on-chip network threshold routing method

ActiveCN110784406BAvoid energy consumptionControl speedData switching networksEngineeringRouting algorithm

The invention relates to a power-aware dynamic adaptive on-chip network threshold routing method, which predicts the load status of the on-chip network by using the adaptive threshold and the corresponding dynamic threshold step size. By adopting the adaptive threshold variable, the non-minimum route is selected only when needed, and the over-selection of non-minimum routes by the algorithm will cause a large amount of additional energy consumption; the application threshold step size variable will be adjusted according to the global network situation Change in order to control the magnitude and speed of threshold change; provide a reasonable routing algorithm for the development and application of dragonfly topology. Experimental results confirm that compared with the UGAL‑LVC‑H routing algorithm, the method of the present invention can save an average of 6.53% (n=4) and 5.93% (n=8) respectively on the power delay product, indicating that the dynamic self-adaptation of the power perception The network-on-chip threshold routing algorithm is a potential alternative to the dragonfly topology routing algorithm.

Owner:UNIV OF SHANGHAI FOR SCI & TECH +1

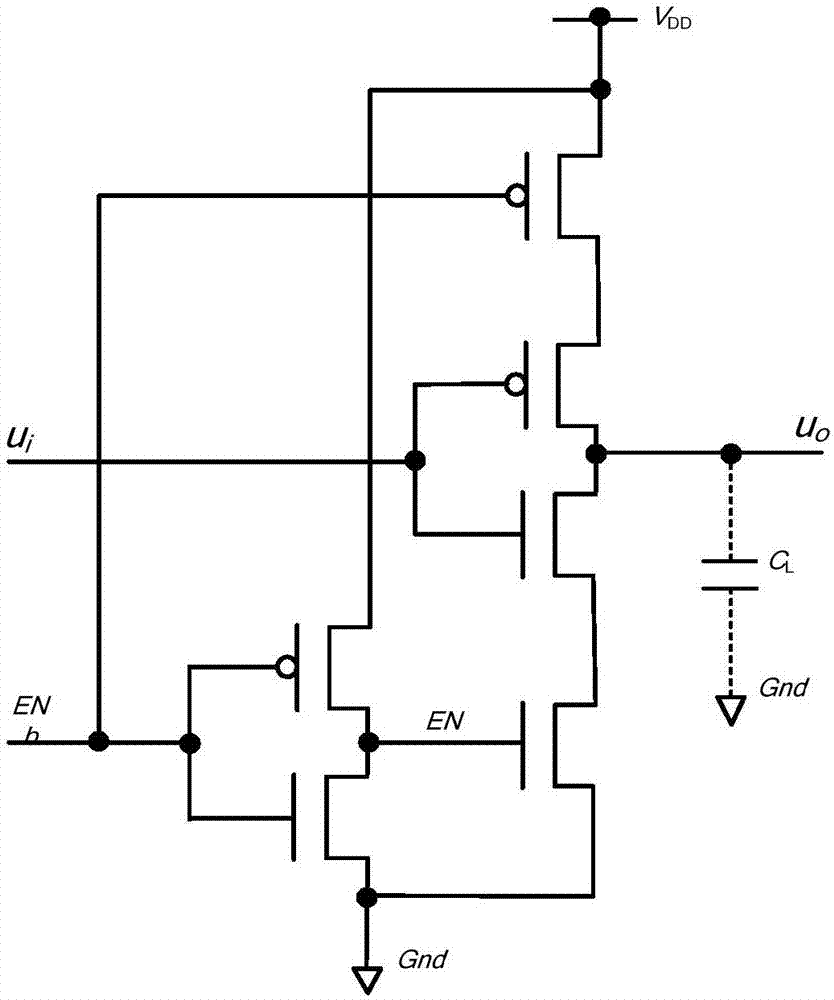

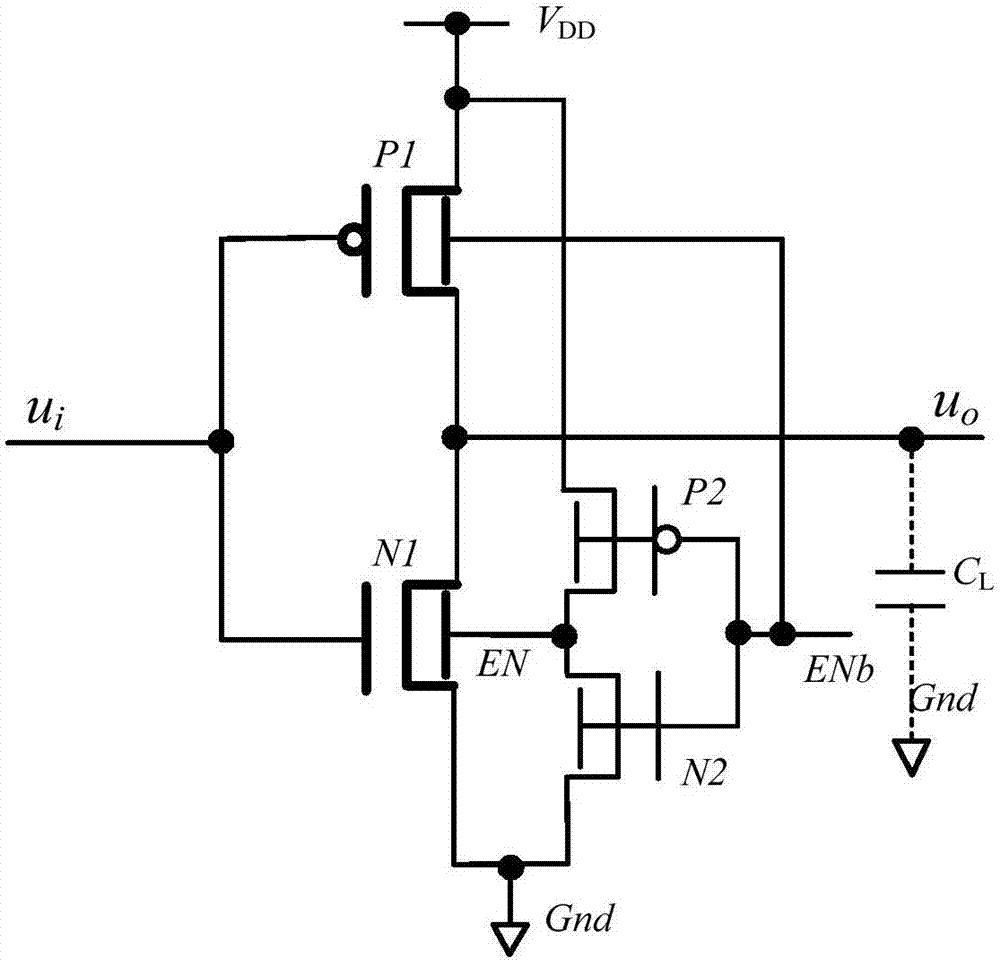

Tristate phase inverter based on FinFET device

InactiveCN107222199ATo achieve the effect of joint controlReduce power consumptionLogic circuits characterised by logic functionEngineeringPower–delay product

The invention discloses a tristate phase inverter based on a FinFET device. The tristate phase inverter comprises the first N-type FinFET tube, a second N-type FinFET tube, the first P-type FinFET tube and the second P-type FinFET tube, wherein the first P-type FinFET tube is the high-threshold P-type FinFET tube, the first N-type FinFET tube is the high-threshold N-type FinFET tube; the second P-type FinFET tube is the low-threshold P-type FinFET tube, and the second N-type FinFET tube is the low-threshold N-type FinFET tube; the advantage is that the functions of two P-type FinFET tubes of a phase-reversing tube and an enabling tube are realized through the first P-type FinFET tube, the first N-type FinFET tube further realizes the effect of integrating the joint control of the input end and the enabling end; the functions of two N-type FinFET tubes of the phase-revering tube and the enabling tube are realized through the first N-type FinFET tube, and the circuit area, the time delay, the power consumption, and the power delay product are greatly optimized.

Owner:NINGBO UNIV

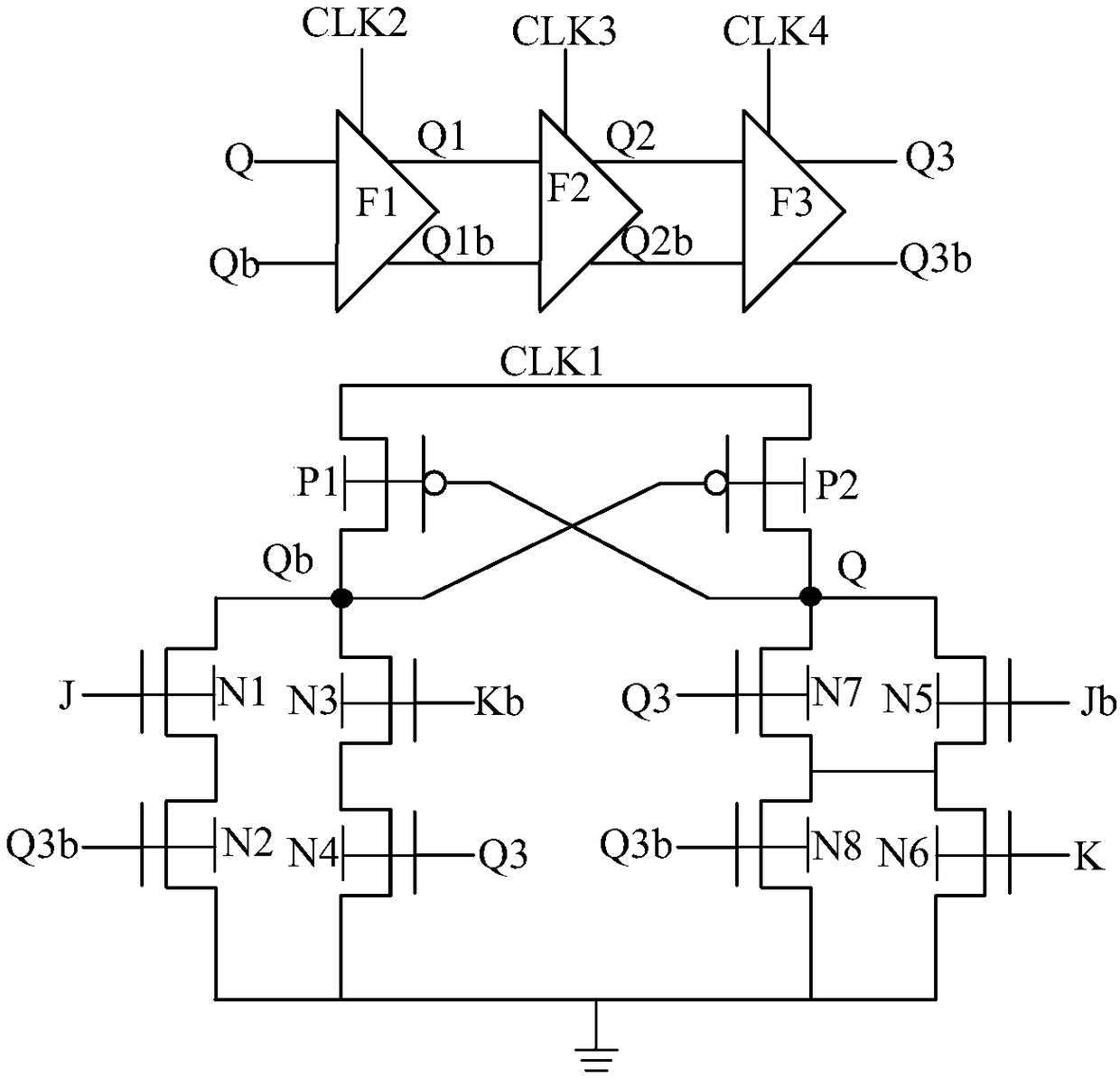

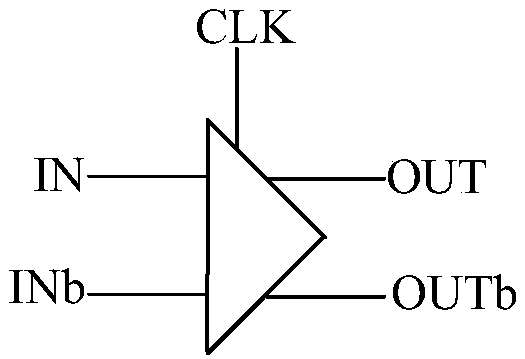

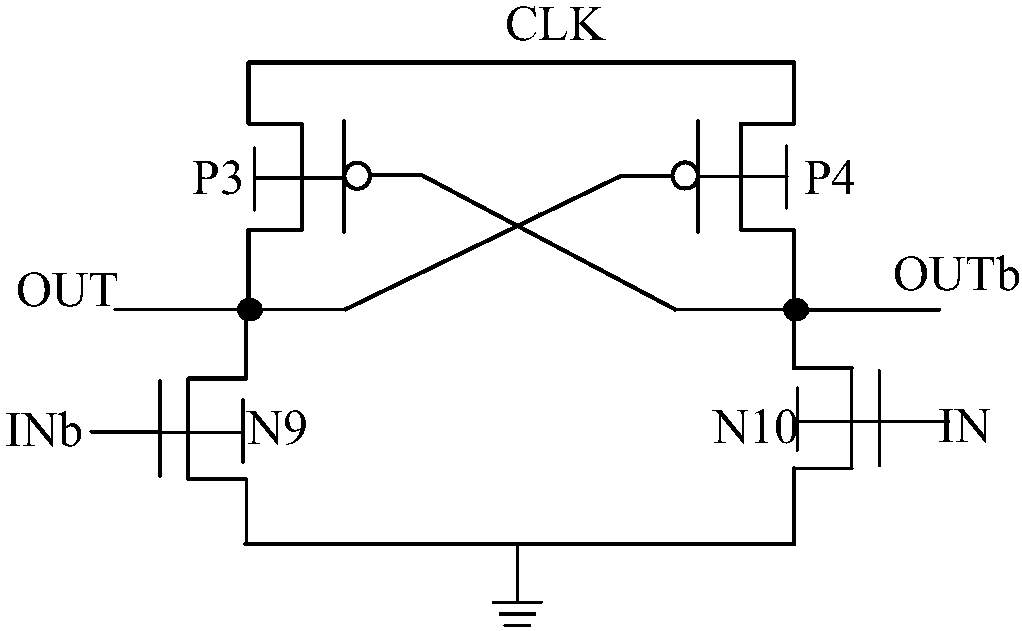

An adiabatic pal-2n jk flip-flop based on finfet device

ActiveCN105978534BEasy to chargeEasy to recycleElectric pulse generatorEngineeringPower–delay product

The invention discloses an adiabatic PAL-2N structure type JK flip-flop based on Fin-FET devices, comprising a first P-type Fin-FET, a second P-type Fin-FET, a third P-type Fin-FET, a fourth P-type Fin-FET, a first N-type Fin-FET, a second N-type Fin-FET, a third N-type Fin-FET, a fourth N-type Fin-FET, a fifth N-type Fin-FET, a sixth N-type Fin-FET, a seventh N-type Fin-FET, an eighth N-type Fin-FET, a ninth N-type Fin-FET, a tenth N-type Fin-FET and an eleventh N-type Fin-FET. The advantage is that under the condition that the circuit performance of the adiabatic PAL-2N structure type JK flip-flop is not affected, the number of Fin-FETs is reduced, the circuit area is reduced significantly, and the time delay, power consumption and power-delay product are reduced significantly.

Owner:NINGBO UNIV

A unit-line asymmetric memory cell based on finfet device

ActiveCN107393581BGuaranteed running speedReduce power consumptionDigital storageNon symmetricNoise margin

Owner:NINGBO UNIV

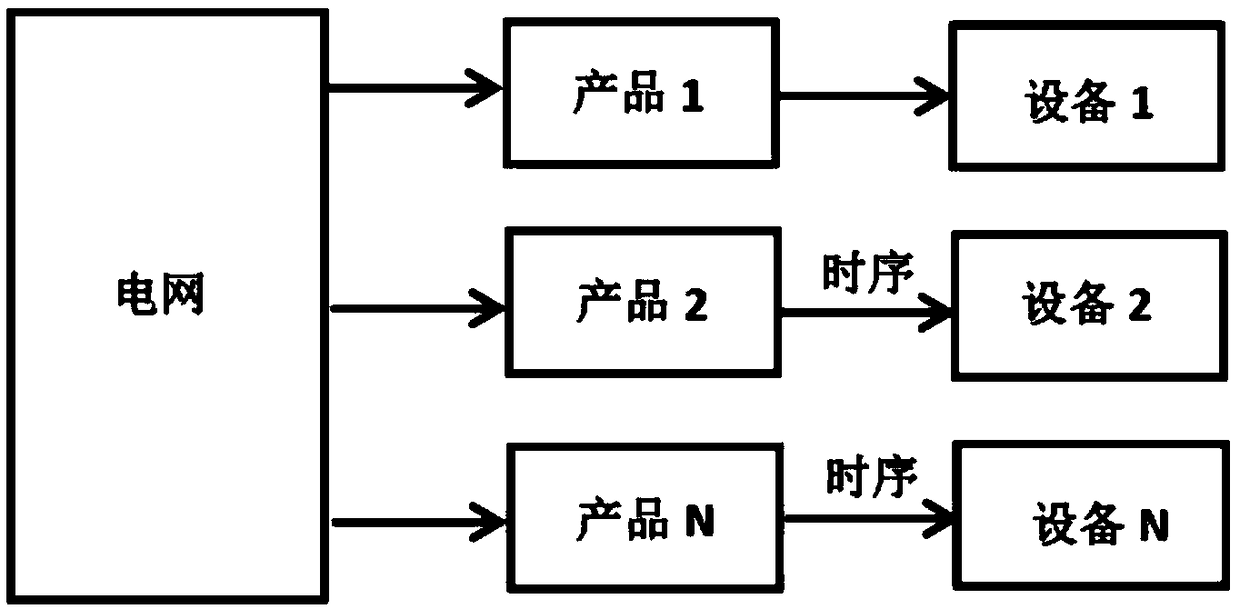

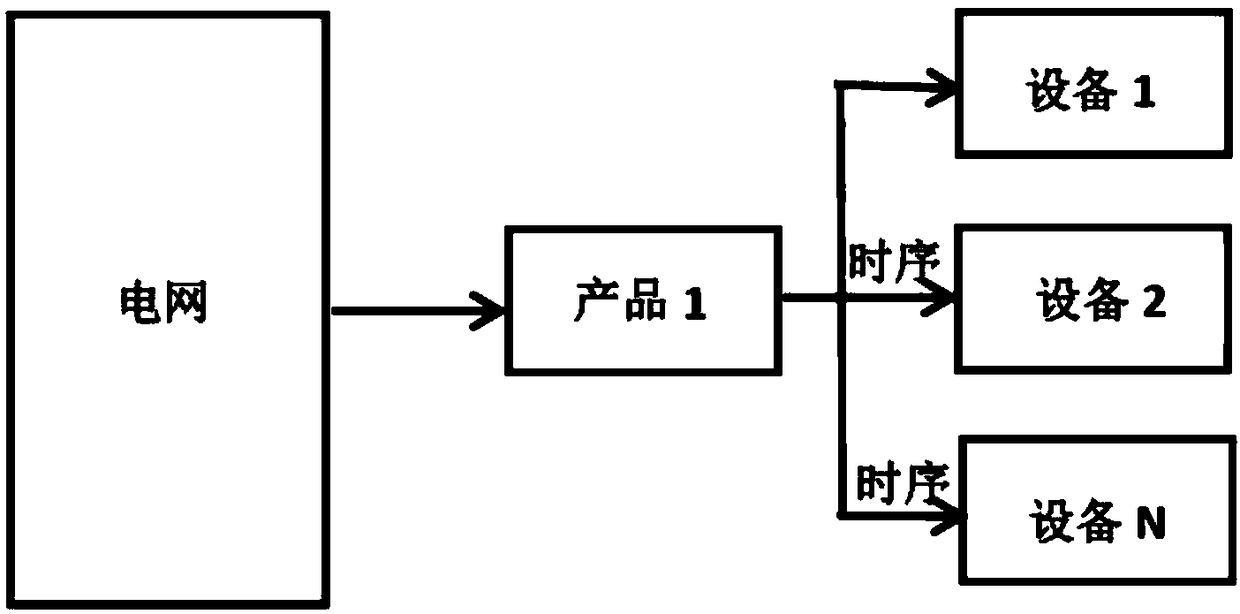

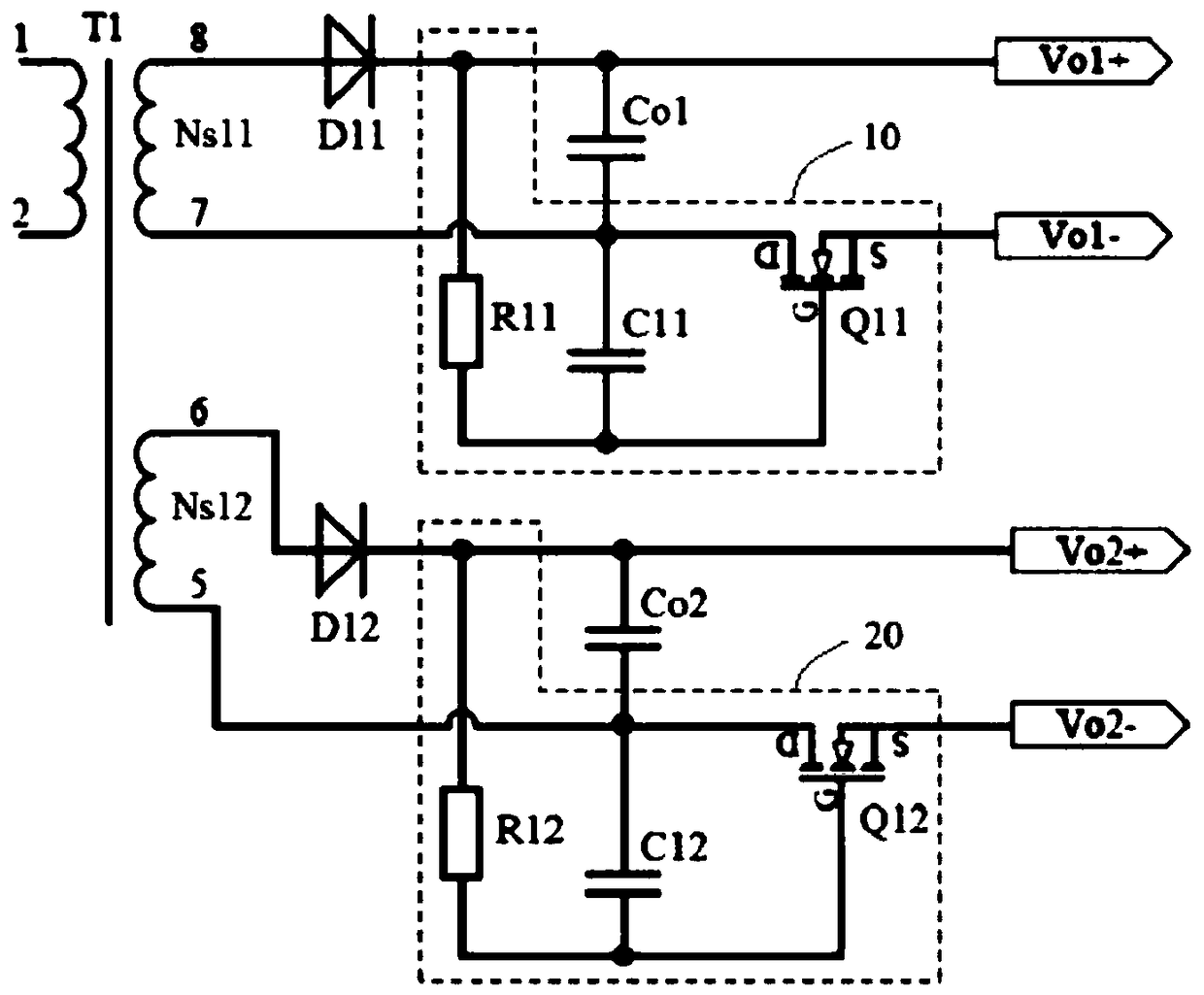

Multiplex output power supply

PendingCN109067171ASimple designEasy to debugApparatus without intermediate ac conversionPower–delay productAuxiliary circuit

The invention provides a multi-output power supply comprising at least one sequential control circuit. Multiple sequential outputs can be achieved and the settling time of each output voltage can be set as needed. It is used to control the auxiliary circuit delay turn-on output of the switching power supply product, so as to solve the sequential start-up application requirements of multiple devices of the customer, reduce the cost and occupy small space. When this circuit can be used in the switching power supply with more than two outputs, the effect is the most obvious.

Owner:MORNSUN GUANGZHOU SCI & TECH

Current mode RM or non- xor unit based on FinFET transistor

ActiveCN107222204AReduce areaLower latencyLogic circuits characterised by logic functionEngineeringCurrent mode

The invention discloses a current mode RM or non- xor unit based on a FinFET transistor. The current mode RM or non- xor unit comprises a first P type FinFET tube, a second P type FinFET tube, a first N type FinFET tube, a second N type FinFET tube, a third N type FinFET tube, a fourth N type FinFET tube, a fifth N type FinFET tube, a sixth N type FinFET tube and a seventh N type FinFET tube, wherein the first P type FinFET tube and the second P type FinFET tube are low-threshold P type FinFET tubes, the first N type FinFET tube, the second N type FinFET tube, the third N type FinFET tube, the fourth N type FinFET tube, the fifth N type FinFET tube, the sixth N type FinFET tube and the seventh N type FinFET tube are high-threshold N type FinFET tubes. The current mode RM or non- xor unit has the advantages that the circuit area, the delay, the power consumption and the power delay product are smaller on the basis of a current logic function.

Owner:NINGBO UNIV

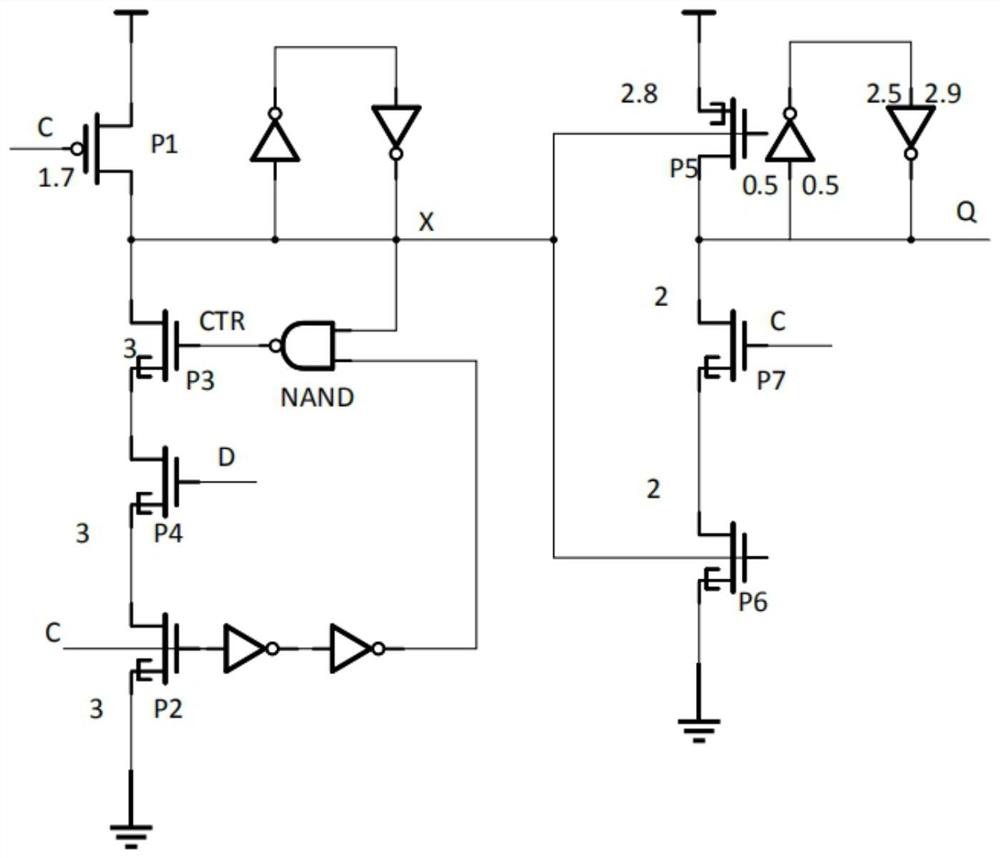

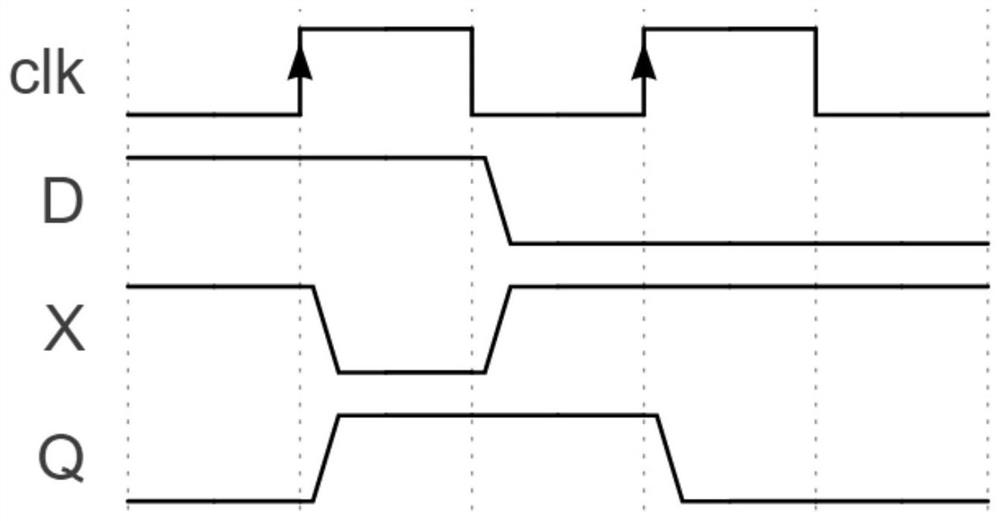

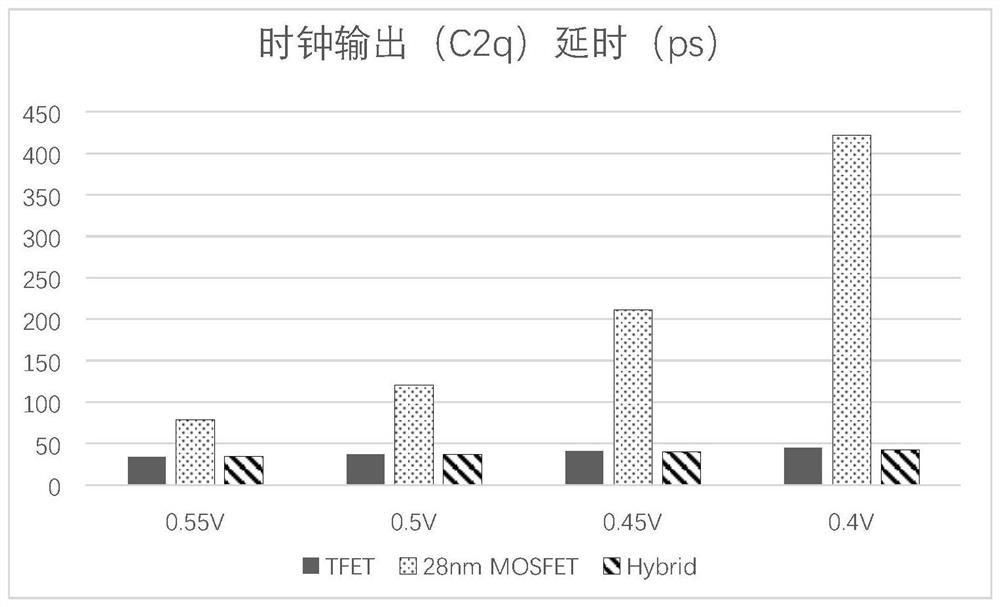

Low-delay semi-dynamic trigger based on tunneling field effect transistor hybrid integration

The invention discloses a low-delay semi-dynamic flip-flop based on tunneling field effect transistor hybrid integration. The flip-flop comprises a dynamic front-end circuit and a static rear-end circuit, the dynamic front-end circuit is composed of a pull-up circuit, a pull-down circuit and a latch, the pull-up circuit is a P-type metal insulated gate transistor. The pull-down circuit comprises three N-type TFET transistors, two TFET phase inverters and a TFET NAND gate; the static output circuit uses a pull-up P-type TFET and two pull-down N-type TFETs and then is connected with a CMOS latch. Under the working voltages of 0.55 V, 0.5 V, 0.45 V and 0.4 V, the clock output (C2q) delay and retention time are remarkably reduced compared with a full MOSFET circuit, the clock output (C2q) delay and retention time are most remarkable under the voltage of 0.4 V and are reduced by 90% and 147% respectively, and the power delay product is reduced compared with a full TFET circuit.

Owner:SOUTHEAST UNIV

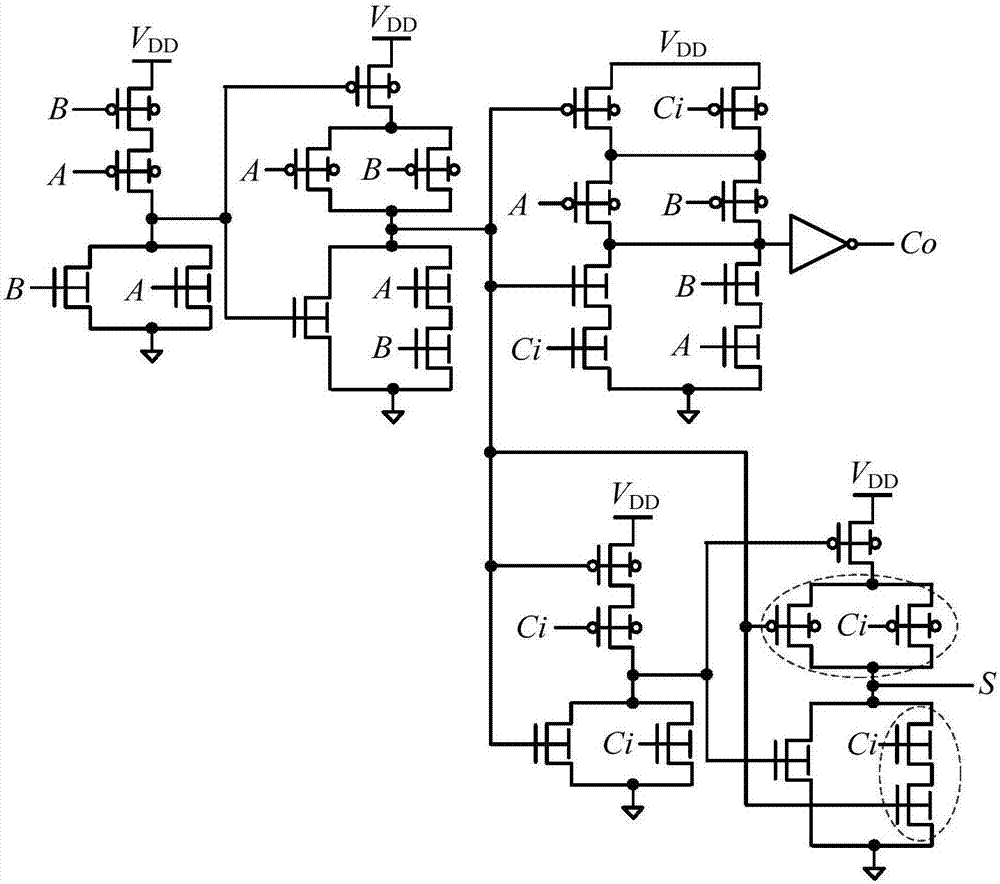

One-bit full-adder based on FinFET transistors

InactiveCN107204769AFew tubesReduce power consumptionLogic circuits characterised by logic functionDigital data processing detailsEngineeringPower–delay product

The invention discloses a one-bit full-adder based on FinFET transistors. The one-bit full-adder comprises a first FinFET transistor, a second FinFET transistor, a third FinFET transistor, a fourth FinFET transistor, a fifth FinFET transistor, a sixth FinFET transistor, a seventh FinFET transistor, an eighth FinFET transistor, a ninth FinFET transistor, a tenth FinFET transistor, an eleventh FinFET transistor, a twelfth FinFET transistor, a thirteenth FinFET transistor, a first inverter and a second inverter. The first FinFET transistor, the fourth FinFET transistor, the fifth FinFET transistor, the seventh FinFET transistor, the tenth FinFET transistor and the eleventh FinFET transistor are P-type FinFET transistors. The second FinFET transistor, the third FinFET transistor, the sixth FinFET transistor, the eighth FinFET transistor, the ninth FinFET transistor, the twelfth FinFET transistor and the thirteenth FinFET transistor are N-type FinFET transistors. The one-bit full-adder has an advantage of realizing relatively small area, relatively short time delay, relatively low power consumption and relatively low power delay product on the condition of no circuit performance reduction.

Owner:NINGBO UNIV

Current mode rm or non-exclusive or unit circuit based on finfet device

ActiveCN107222200BReduce areaLower latencyLogic circuits characterised by logic functionHemt circuitsCurrent mode

Owner:NINGBO UNIV

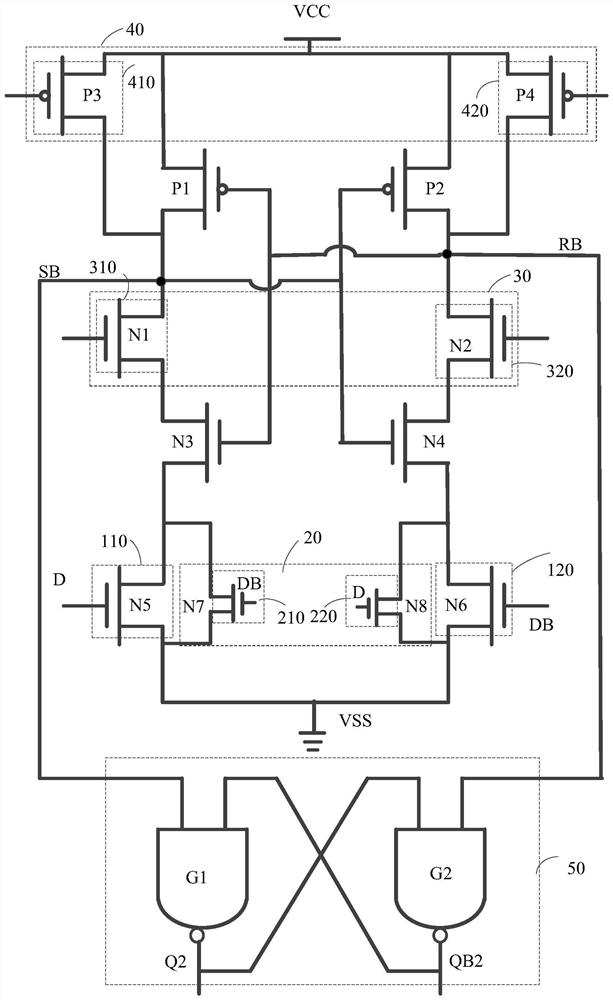

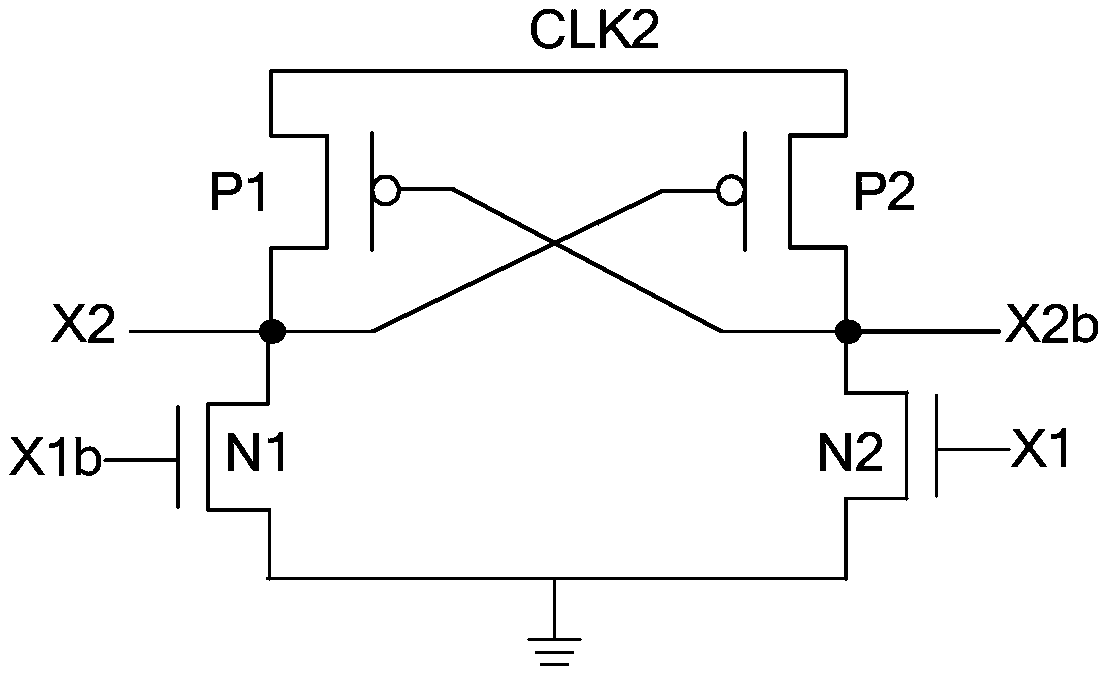

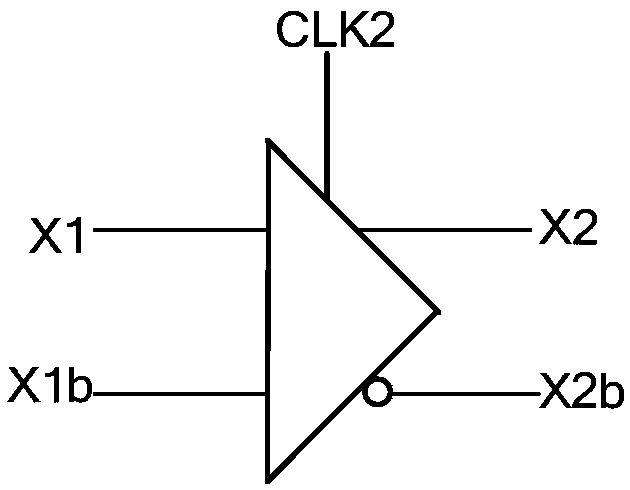

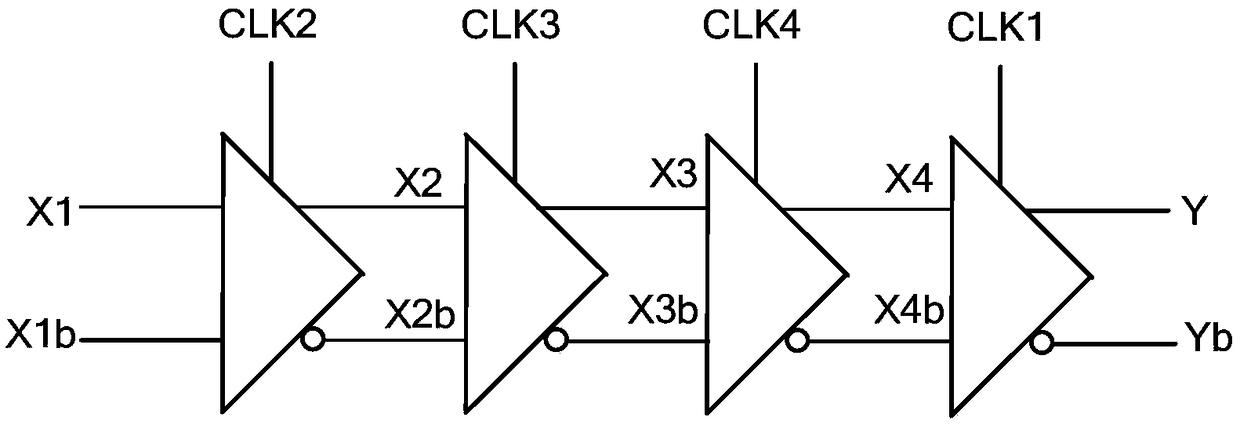

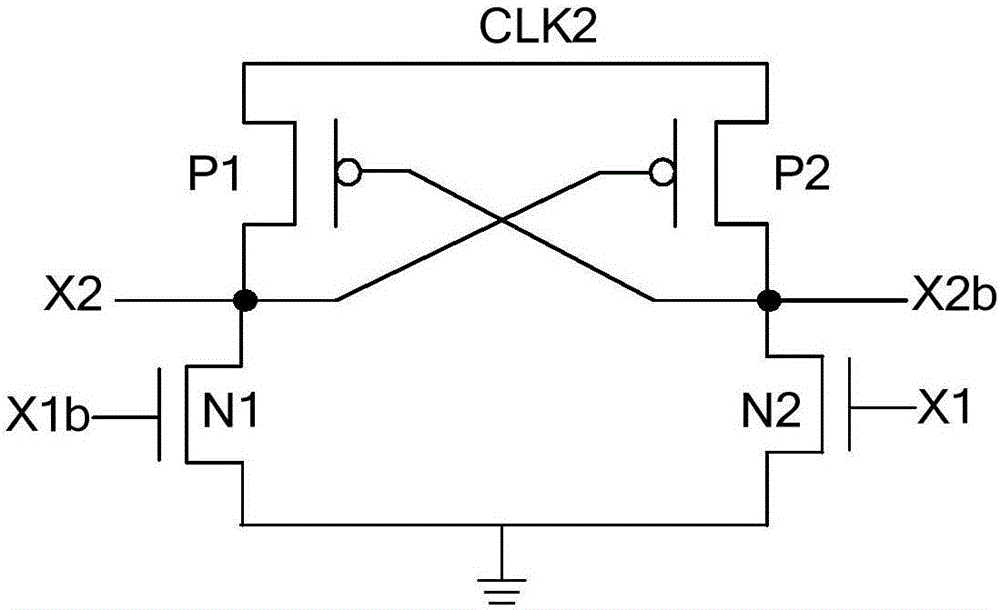

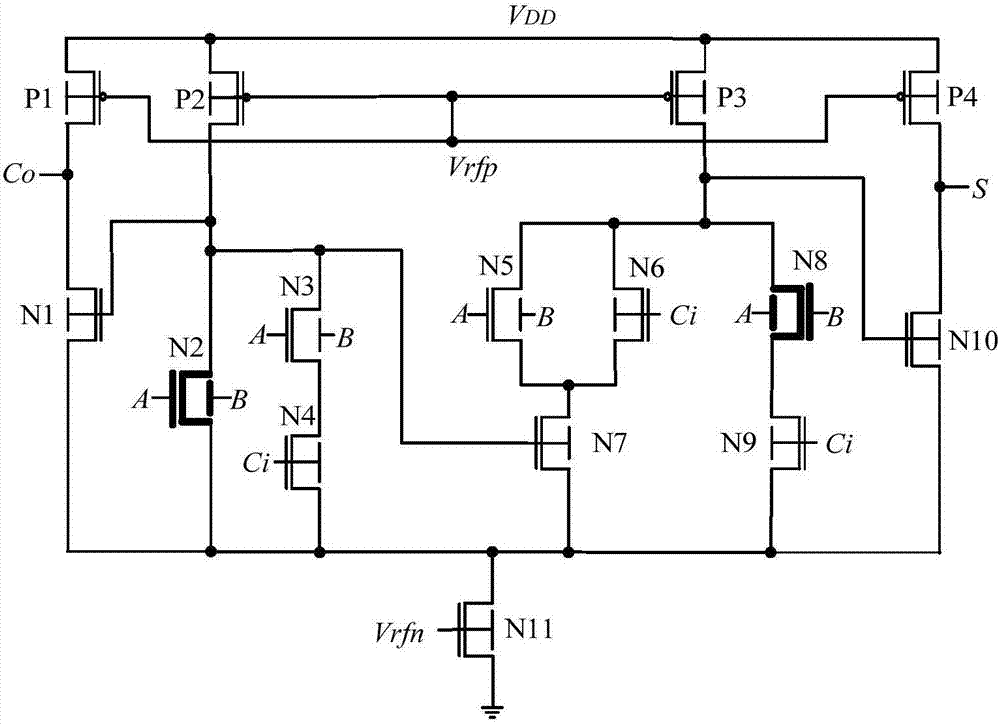

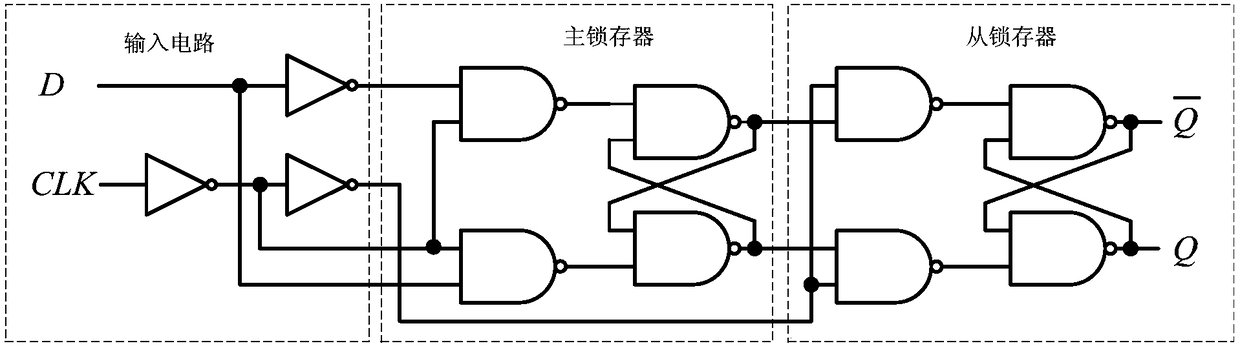

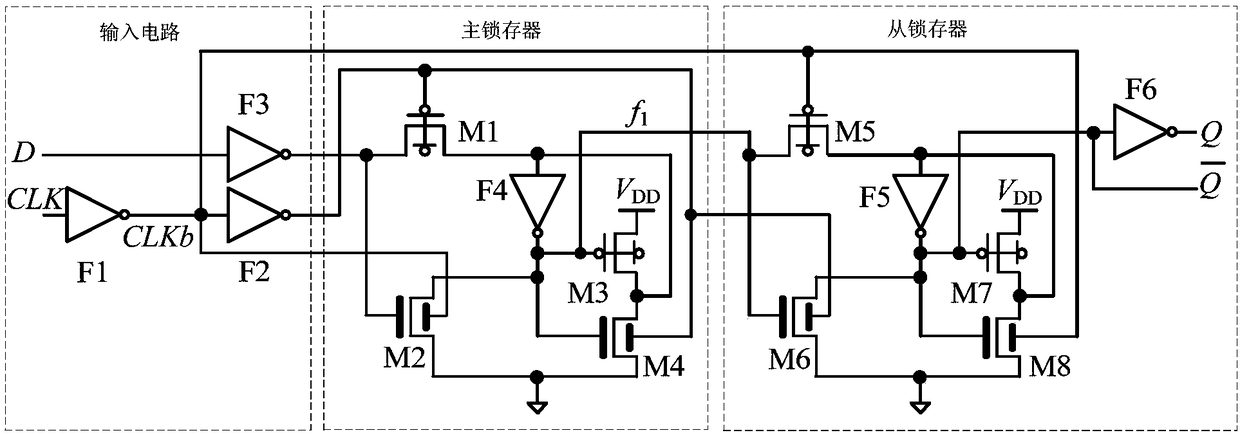

FinFET-based master-slave flip-flop

ActiveCN108494386ACompensation for transmission threshold lossGuaranteed dataElectric pulse generatorEngineeringPower–delay product

The invention discloses a FinFET-based master-slave flip-flop, comprising an input circuit, a master latch and a slave latch, wherein the input circuit comprises a first inverter, a second inverter and a third inverter, the master latch comprises a first FinFET transistor, a second FinFET transistor, a third FinFET transistor, a fourth FinFET transistor and a fourth inverter, and the slave latch comprises a fifth FinFET transistor, a sixth FinFET transistor, a seventh FinFET transistor, an eighth FinFET transistor, a fifth inverter and a sixth inverter. The scheme of the invention has the advantages that on the basis of realizing the correct working logic, a simple circuit structure is realized, a trigger function is achieved by adopting a small number of transistors, and in the working state, the working current is mainly composed of the current in the master latch and the current in the slave latch, the master latch and the slave latch work alternately, and thus without affecting thecircuit performance, the circuit area, power consumption and power-delay product are all small.

Owner:NINGBO UNIV