Full adder based on FinFET device

A full adder and device technology, applied in the field of full adder based on FinFET devices, can solve the problems of long path, large delay, high height, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

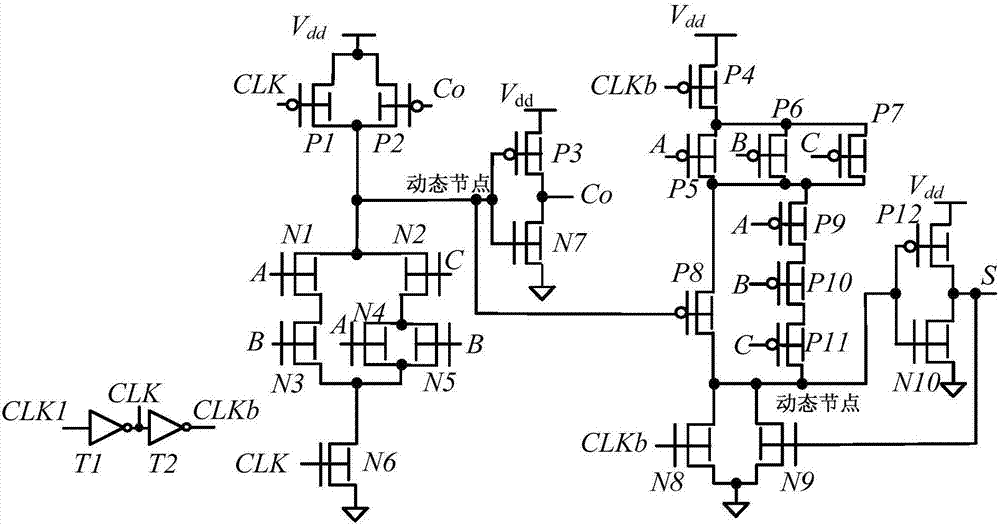

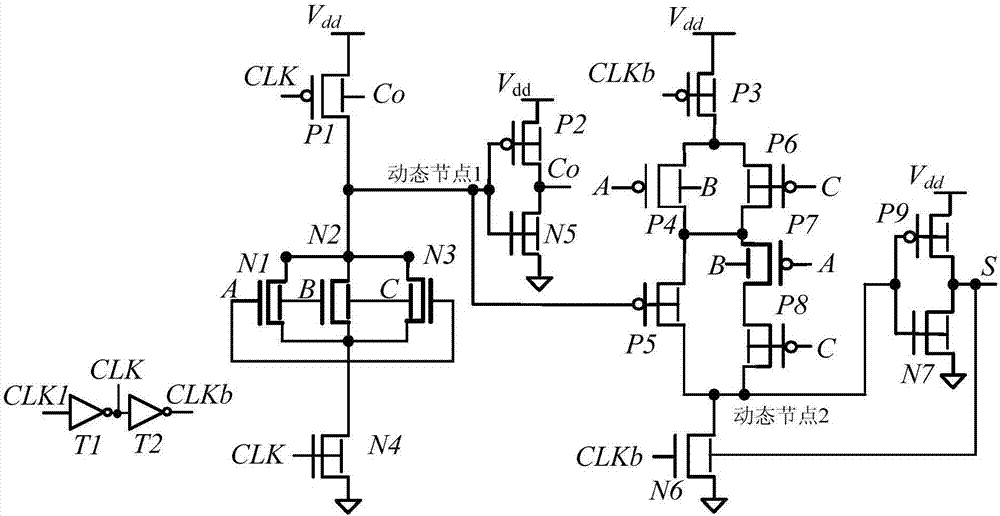

[0019] Embodiment one: if figure 2 As shown, a full adder based on FinFET devices includes a first N-type FinFET tube N1, a second N-type FinFET tube N2, a third N-type FinFET tube N3, a fourth N-type FinFET tube N4, and a fifth N-type FinFET tube N4. FinFET tube N5, sixth N-type FinFET tube N6, seventh N-type FinFET tube N7, first P-type FinFET tube P1, second P-type FinFET tube P2, third P-type FinFET tube P3, fourth P-type FinFET tube P4, the fifth P-type FinFET tube P5, the sixth P-type FinFET tube P6, the seventh P-type FinFET tube P7, the eighth P-type FinFET tube P8, the ninth P-type FinFET tube P9, the first inverter T1 and the The second inverter T2, the first N-type FinFET N1, the second N-type FinFET N2 and the third N-type FinFET N3 are all high-threshold N-type FinFETs, and the seventh P-type FinFET P7 is a high-threshold P-type FinFET tubes, the fourth N-type FinFET tube N4, the fifth N-type FinFET tube N5, the sixth N-type FinFET tube N6 and the seventh N-type...

Embodiment 2

[0020] Embodiment two: if figure 2As shown, a full adder based on FinFET devices includes a first N-type FinFET tube N1, a second N-type FinFET tube N2, a third N-type FinFET tube N3, a fourth N-type FinFET tube N4, and a fifth N-type FinFET tube N4. FinFET tube N5, sixth N-type FinFET tube N6, seventh N-type FinFET tube N7, first P-type FinFET tube P1, second P-type FinFET tube P2, third P-type FinFET tube P3, fourth P-type FinFET tube P4, the fifth P-type FinFET tube P5, the sixth P-type FinFET tube P6, the seventh P-type FinFET tube P7, the eighth P-type FinFET tube P8, the ninth P-type FinFET tube P9, the first inverter T1 and the The second inverter T2, the first N-type FinFET N1, the second N-type FinFET N2 and the third N-type FinFET N3 are all high-threshold N-type FinFETs, and the seventh P-type FinFET P7 is a high-threshold P-type FinFET tubes, the fourth N-type FinFET tube N4, the fifth N-type FinFET tube N5, the sixth N-type FinFET tube N6 and the seventh N-type ...

Embodiment 3

[0022] Embodiment three: as figure 2As shown, a full adder based on FinFET devices includes a first N-type FinFET tube N1, a second N-type FinFET tube N2, a third N-type FinFET tube N3, a fourth N-type FinFET tube N4, and a fifth N-type FinFET tube N4. FinFET tube N5, sixth N-type FinFET tube N6, seventh N-type FinFET tube N7, first P-type FinFET tube P1, second P-type FinFET tube P2, third P-type FinFET tube P3, fourth P-type FinFET tube P4, the fifth P-type FinFET tube P5, the sixth P-type FinFET tube P6, the seventh P-type FinFET tube P7, the eighth P-type FinFET tube P8, the ninth P-type FinFET tube P9, the first inverter T1 and the The second inverter T2, the first N-type FinFET N1, the second N-type FinFET N2 and the third N-type FinFET N3 are all high-threshold N-type FinFETs, and the seventh P-type FinFET P7 is a high-threshold P-type FinFET tubes, the fourth N-type FinFET tube N4, the fifth N-type FinFET tube N5, the sixth N-type FinFET tube N6 and the seventh N-typ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More