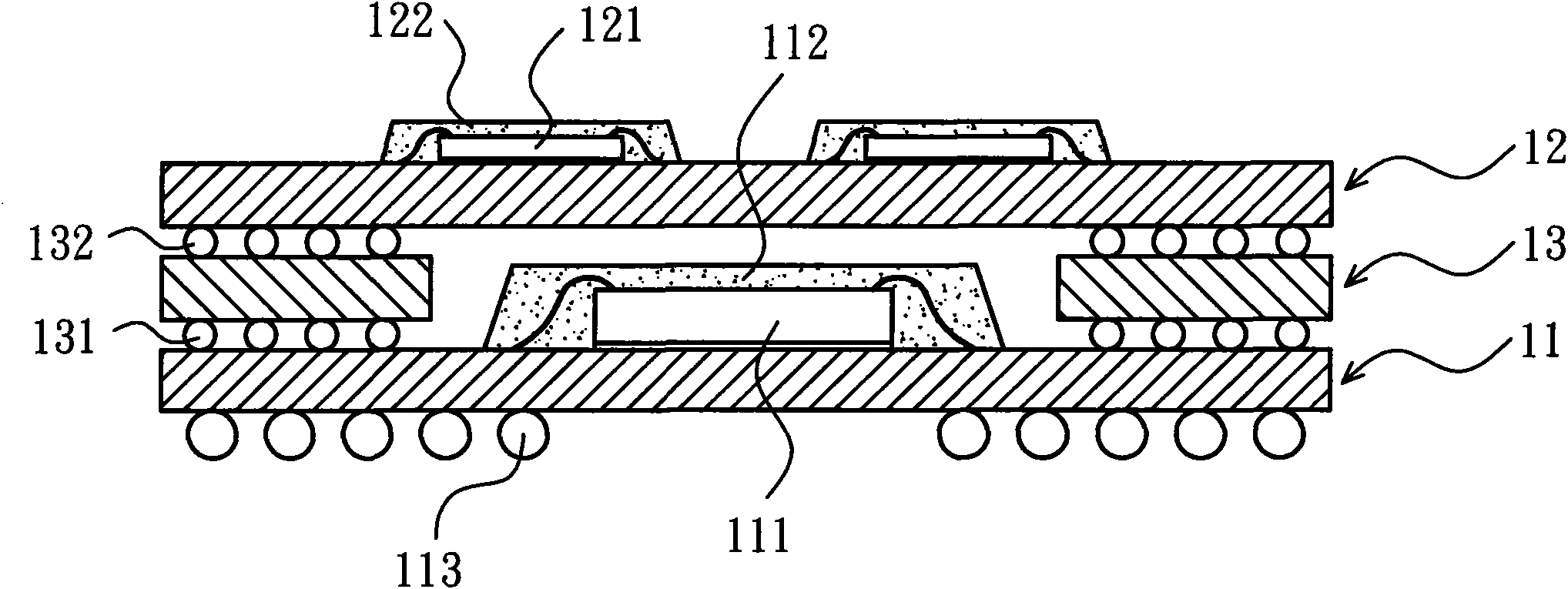

Stacking structure of semiconductor packages

A package and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of increasing the cost of assembly materials, increasing the yield rate, and unfavorable overall stacking height

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the above-mentioned purposes, features and advantages of the present invention more obvious and understandable, the preferred embodiments of the present invention will be specifically cited below, together with the accompanying drawings, for a detailed description as follows:

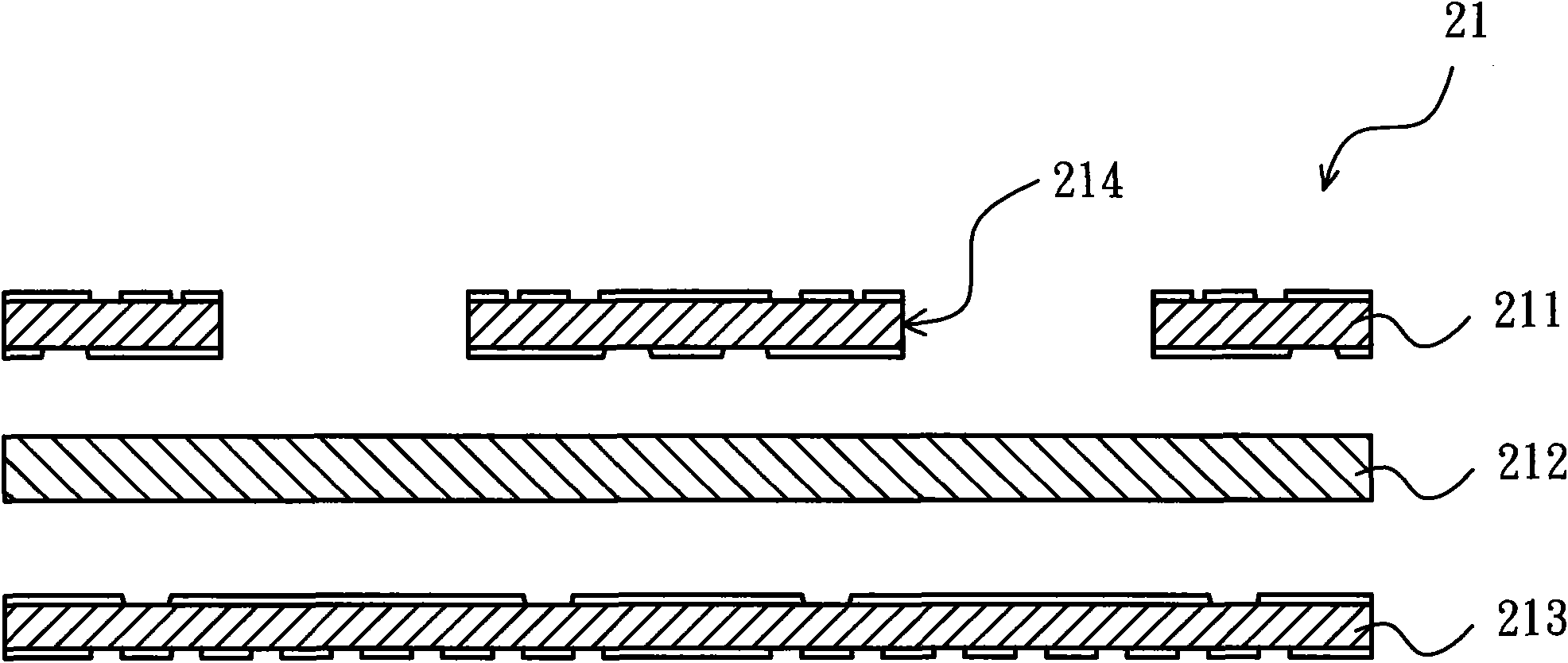

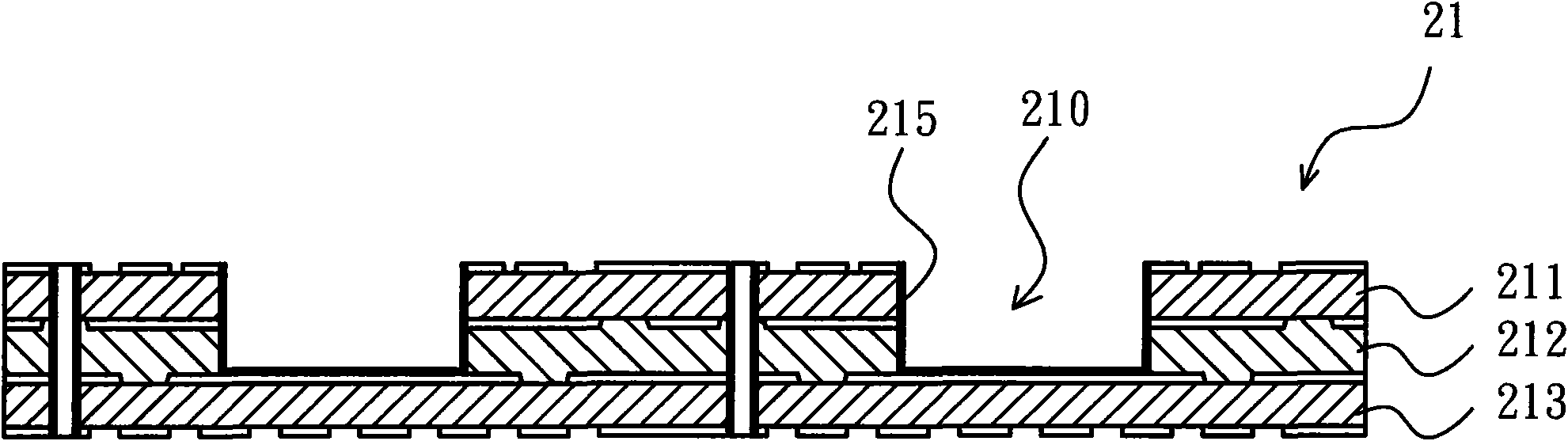

[0026] Please refer to Figure 2A , 2B , 2C, 2D, 2E and 2F, which disclose the manufacturing method flow of the stacked structure of the semiconductor package according to the first embodiment of the present invention, wherein as Figure 2A , 2B As shown in and 2C, the first step of the manufacturing method is: providing a first circuit board 21 provided with at least one cavity 210 and several transfer pads 218 . In this step, if Figure 2A As shown, first, a plurality of substrate units are combined by a lamination process, for example, a first substrate unit 211, a second substrate unit 212 and a third substrate unit 213 are combined, wherein the first substrate unit 211 is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More