Low-power consumption sensitive amplifier type D-flip flop

A sensitive amplifier and sensitive amplification technology, applied in pulse generation, electrical components, generating electrical pulses, etc., can solve the problems of asymmetric rise and fall delay, slow evaluation speed, fast speed, etc., to improve the power consumption delay product , the evaluation speed is fast, the power consumption is small

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

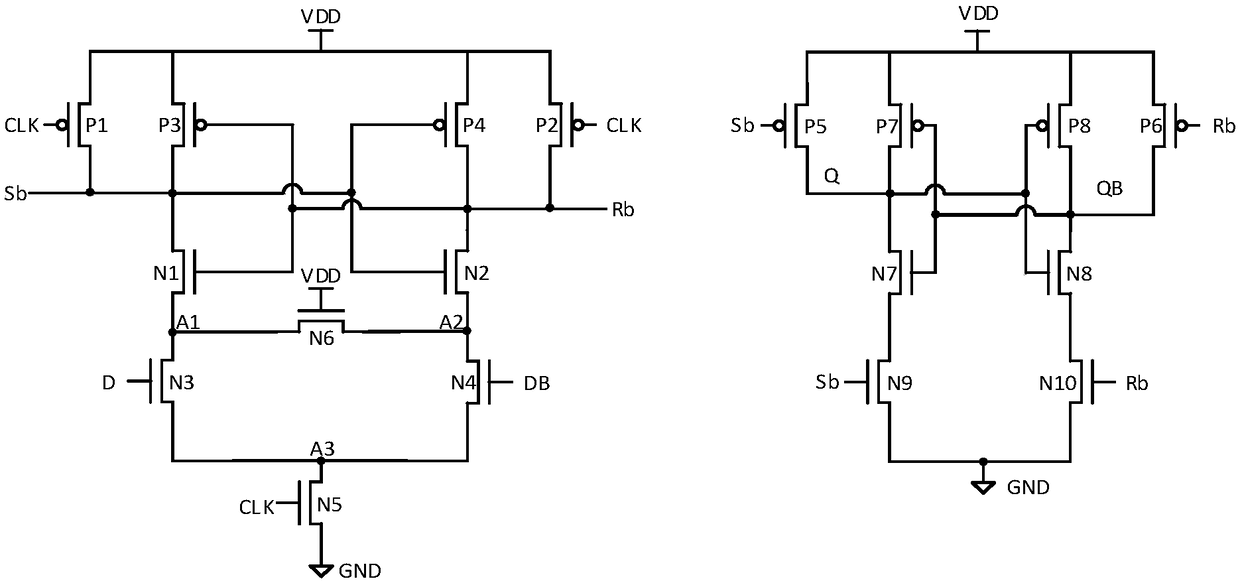

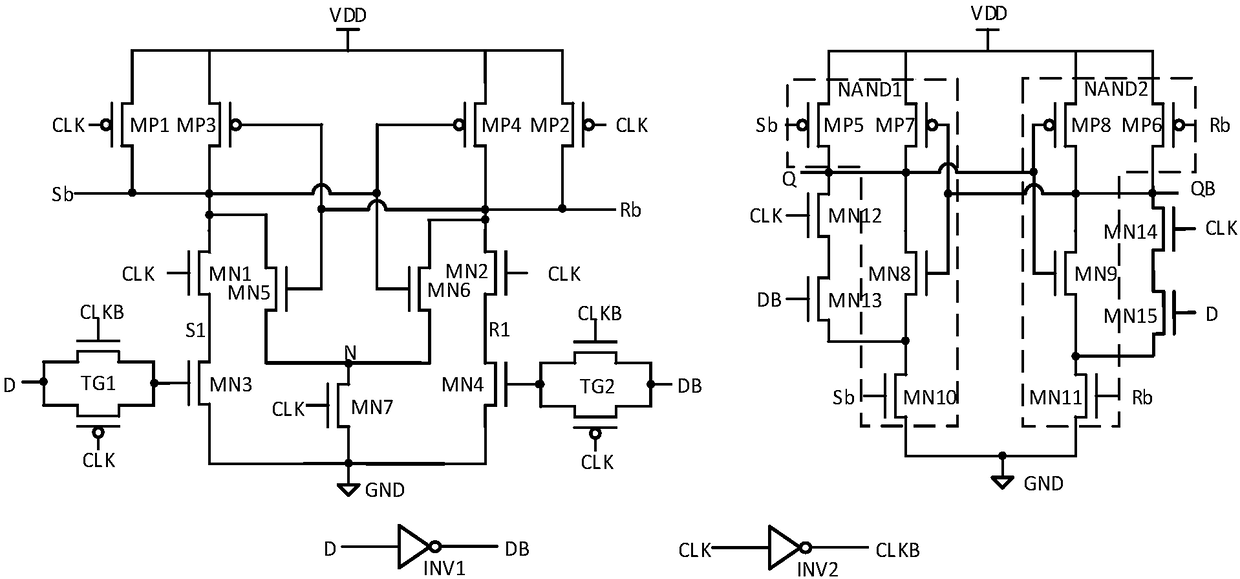

[0031] Such as figure 2 Shown is the circuit structure diagram of the low-power sensitive amplifier type D flip-flop proposed by the present invention, which has an independent evaluation path, including an input inverting stage, a sensitive amplifier stage and a latch stage.

[0032] Among them, in order to reduce the problem that there are many transistors in the evaluation path of the sensitive amplifier stage in the traditional sensitive amplifier type D flip-flop, the D flip-flop provided by the invention has adopted a sensitive amplifier stage with an independent evaluation path; the sensitive amplifier stage includes input control Module, pre-charging module, data holding module and evaluation module, the third PMOS transistor MP3 and the fifth NMOS transistor MN5 in the data holding module constitute an inverter, the input end of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More