semiconductor manufacturing method

A manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve problems such as uneven stress distribution, reflecting the overlay position of the cell array area, overlay alignment deviation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

[0035] According to an embodiment of the present invention, a method for overlay alignment (OVL) in a semiconductor manufacturing process is proposed.

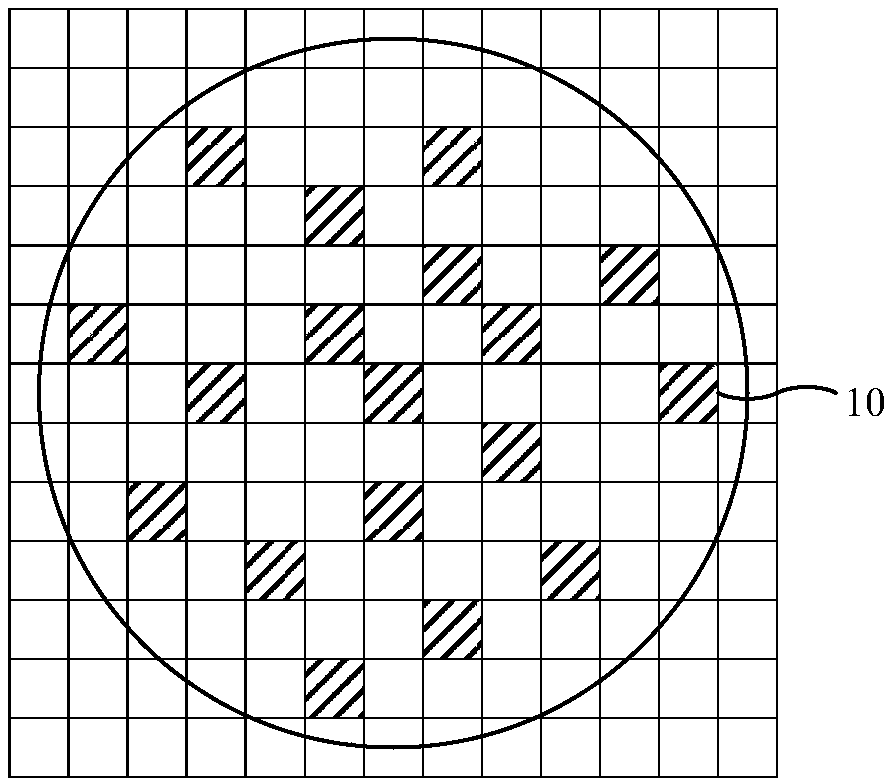

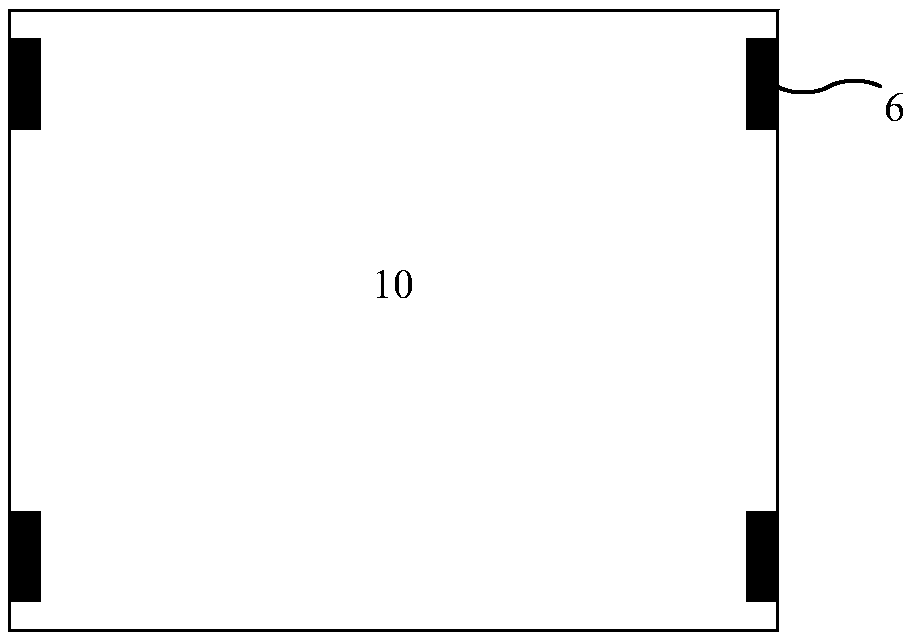

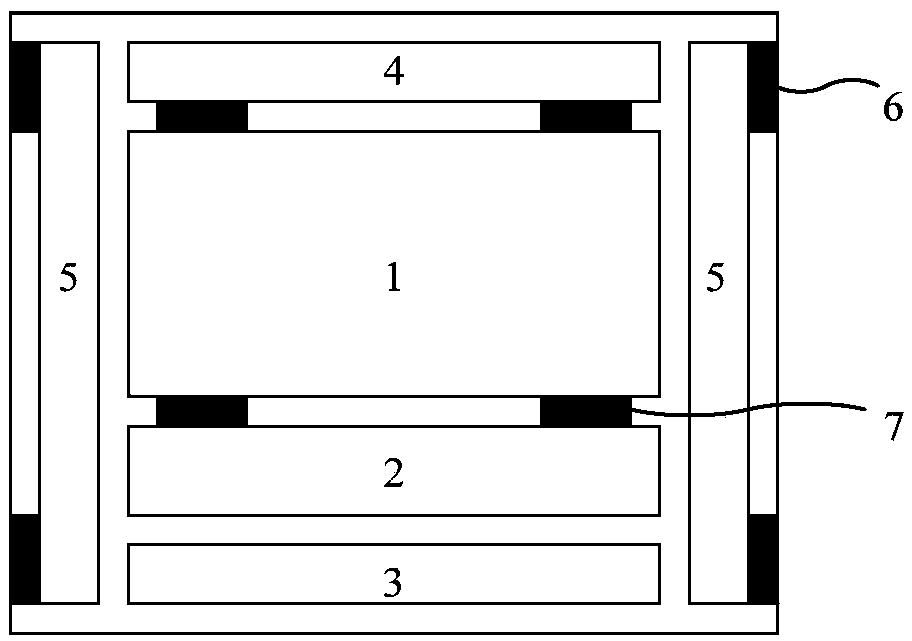

[0036] Firstly, two sets of overlay alignment (OVL) marks at different positions are set in each exposure area, that is, the OVL marks in the cell array area and the OVL marks in the scribe tape. Wherein the cell array area OVL mark 7 is close to the cell array area 1 and is locate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com