Fault attack detection method based on power consumption analysis

A technology of fault attack and detection method, applied in the field of information security, can solve the problems of large number of key candidate spaces required for calculation complexity, affecting bit value, affecting cryptography, etc., so as to reduce the number of key candidate sets and computational complexity. degree of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

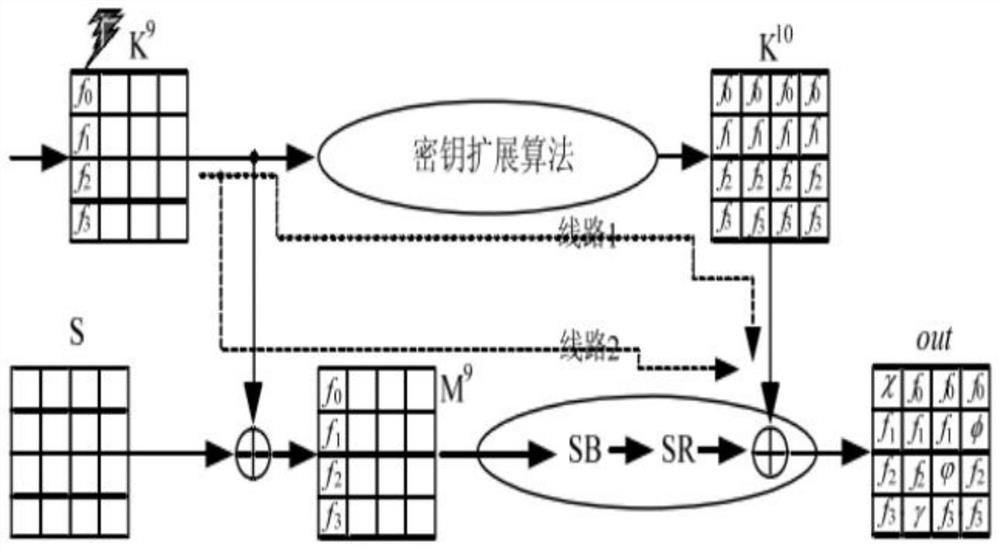

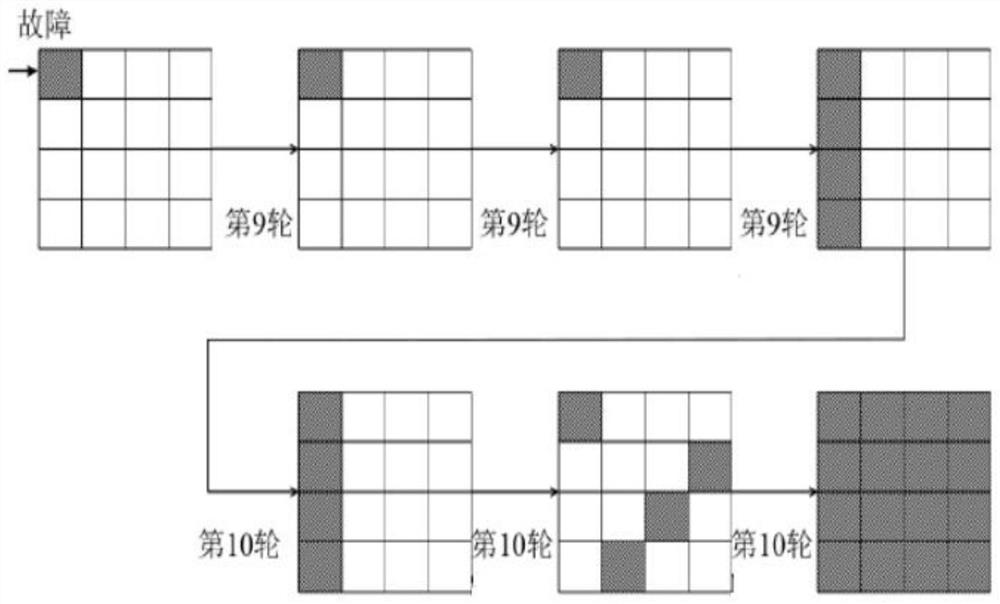

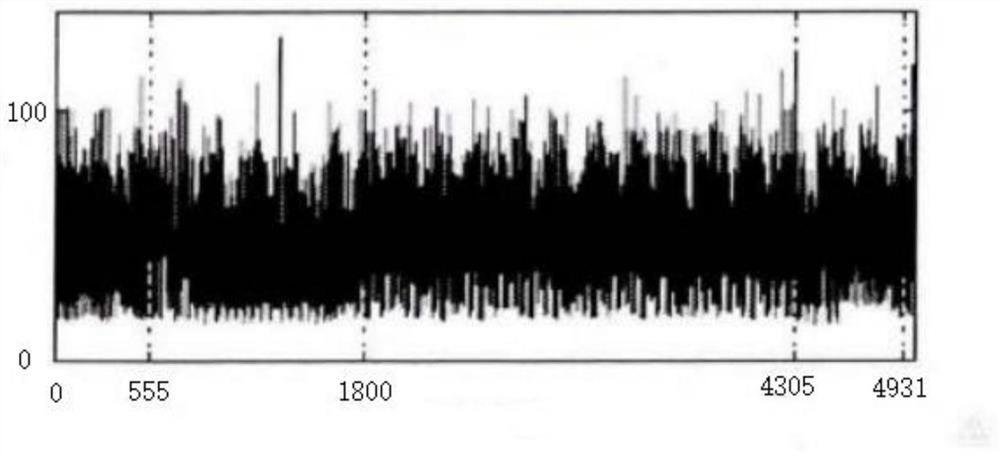

Embodiment Construction

[0021] The following will clearly and completely describe the technical solutions in the embodiments of the present invention in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Unless otherwise specified, the technical means used in the embodiments are conventional means well known to those skilled in the art.

[0022] In describing the present invention, it should be understood that the terms "longitudinal", "transverse", "upper", "lower", "front", "rear", "left", "right", "vertical", The orientations or positional relationships indicated by "horizontal", "top", "bottom", "inner", "outer", etc. are based on the orientations or positional relationships shown in the drawings, and are only for the convenience of describing the present invention, rather than indicating or It should not be construed as limiting the invention by im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More