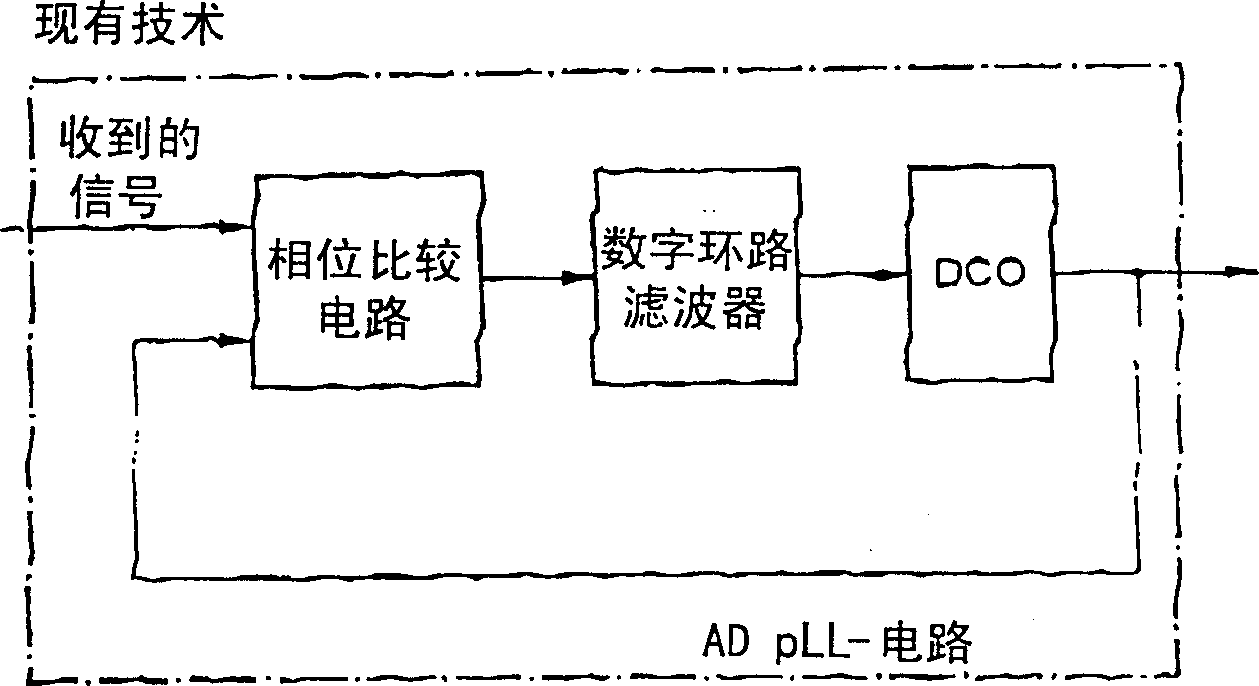

Phase-locked loop circuit of eliminating self-shaking in signals received by control circuit

A technology for controlling circuits and signals, applied in the field of self-jitter, and can solve problems such as data loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

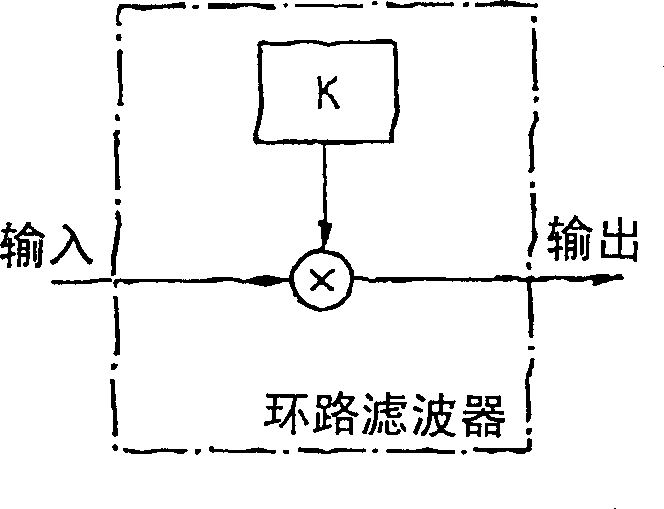

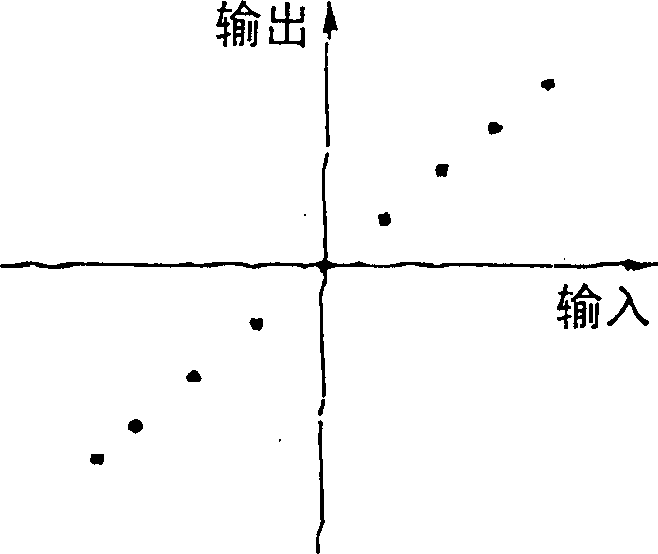

[0035] Fig. 3a shows a first embodiment of a loop filter with a non-linear transfer function for a PLL circuit according to the invention for canceling self-jitter in a received signal. The loop filter 1 depicted in Fig. 3 is digital. In an alternative embodiment, the loop filter is analog.

[0036] The digital loop filter 1 depicted in Fig. 3a is a non-linear P-regulator used in a PLL circuit according to the invention. The digital loop filter has a signal input 2 for receiving a digital data deviation signal via a signal line 3 . The phase difference signal applied to the signal input 2 is passed to the branch node 5 via the internal line 4 and controls the multiplexer 7 contained in the loop filter 1 via the internal control line 6 . The branch node 5 is also connected to a multiplier 9 via an internal line 8 . The output of multiplexer 7 is likewise connected via line 10 to multiplier 9 . Multiplier 9 multiplies the output value from multiplexer 7 by the phase differen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More