Insulating grid type semiconductor device

An insulated gate, semiconductor technology, used in semiconductor devices, electrical components, circuits, etc., can solve problems such as cost increase, and achieve the effect of suppressing sharp rise and suppressing voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

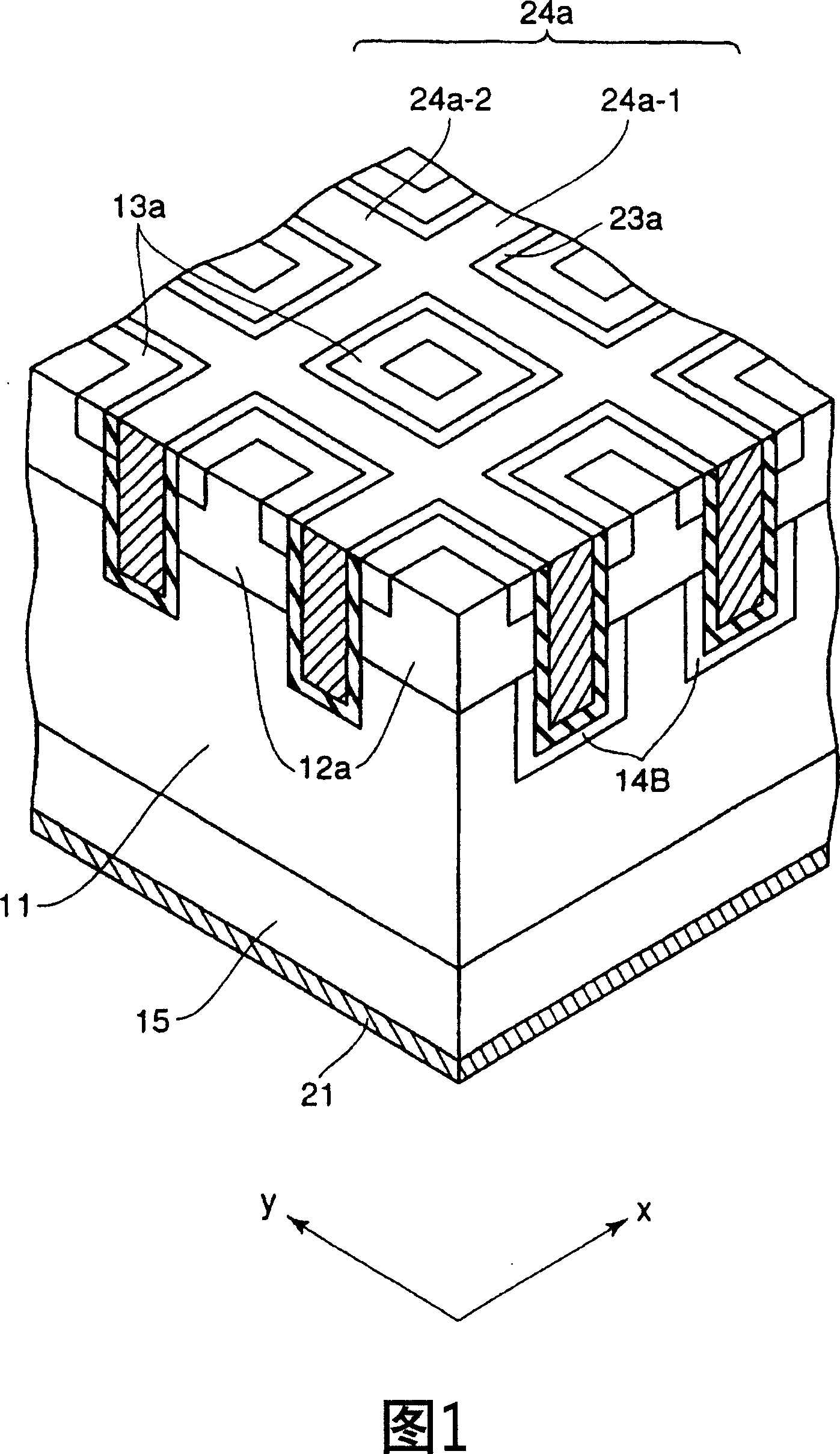

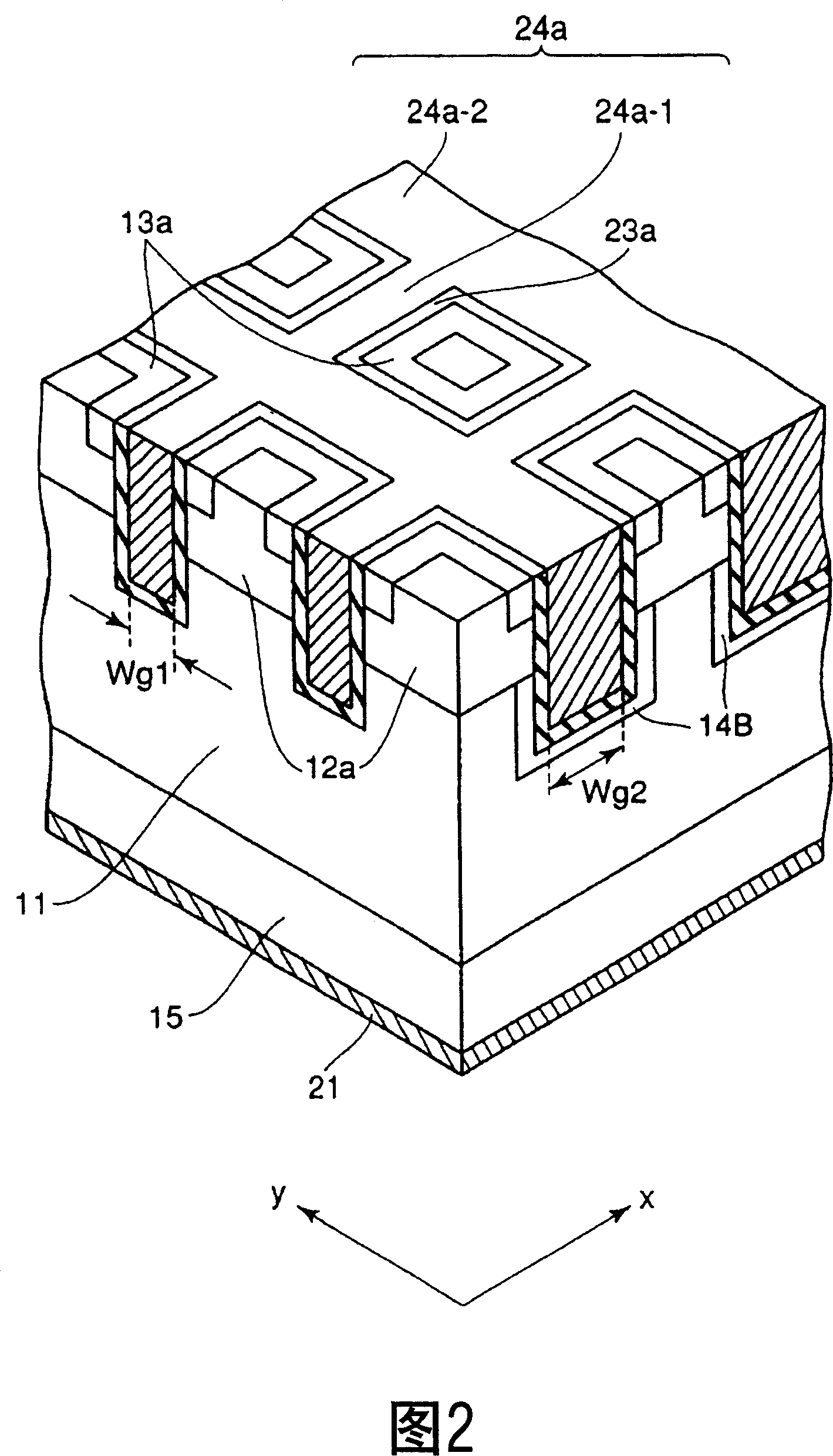

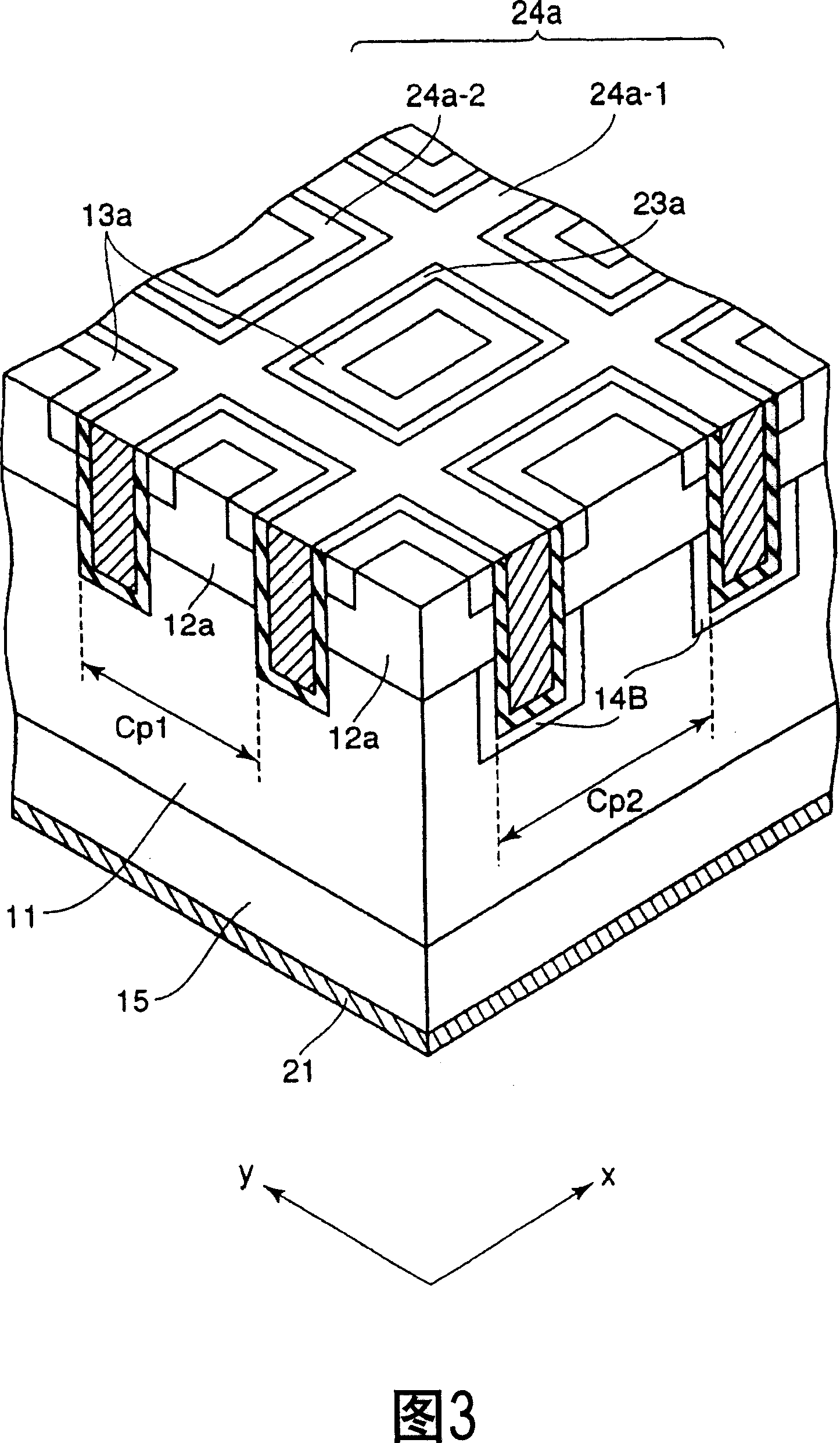

[0042] FIG. 1 is a diagram showing a configuration example of a vertical power MOSFET according to a first embodiment of the present invention. Here, an arbitrary cross section in the x direction (first direction) and an arbitrary cross section in the y direction (second direction) with respect to the vertical power MOSFET are respectively shown. In addition, this embodiment is an example in the case where the gate electrode of the trench structure is formed in a lattice shape.

[0043] In Figure 1, in the n as the first semiconductor layer - On one surface portion of the drift layer 11, a plurality of p base layers 12a are selectively formed as the second semiconductor layer by diffusion. Each p base layer 12a has a rectangular shape and is arranged in a matrix (or zigzag shape). In addition, on the surface portion of each of the above-mentioned p base layers 12a, an n base layer as a third semiconductor layer is selectively formed by diffusion. + source layer 13a. For ex...

no. 2 Embodiment approach

[0063] 10 is a diagram showing a configuration example of a vertical power MOSFET according to a second embodiment of the present invention. Here, an arbitrary cross section in the x direction and an arbitrary cross section in the y direction of the vertical power MOSFET are respectively shown. In addition, this embodiment is an example in the case where the gate electrode of the trench structure is formed in a stripe shape.

[0064] In Fig. 10, in the n as the first semiconductor layer - On one surface portion of the drift layer 11, a plurality of p base layers 12 are selectively formed as the second semiconductor layer by diffusion. The p base layers 12 are arranged in a strip shape with a certain interval (pitch) in the x direction, for example. In addition, on the surface portion of each of the p base layers 12 described above, an n p base layer as a third semiconductor layer is selectively formed by diffusion. + source layer 13. Each n + For example, the source layer...

no. 3 Embodiment approach

[0077] 18 is a diagram showing a configuration example of a vertical power MOSFET according to a third embodiment of the present invention. Here, for example, in n - A case where the n-low resistance layer 11 a is formed on the surface portion of the drift layer 11 .

[0078] The MOSFET of this embodiment passes n - The pn diode (built-in diode) formed by the drift layer and the p base layer can improve the loss and noise when switching from the on state to the off state (recovery time). For example, when MOSFETs are used in power supply circuits such as small inverter circuits (single phase) and bridge circuits, it is known that the loss and noise during recovery of built-in diodes have a large influence on the loss and noise of the power supply circuit.

[0079] That is, in FIG. 18, n as the first semiconductor layer - The drift layer 11 has, on one surface portion thereof, an n low-resistance layer 11a provided by diffusion. In the surface portion of the n low-resistanc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More