Data alignment circuit in receiving channel of billion Ethernet receiver

A Gigabit Ethernet, data alignment technology, applied in the direction of line transmission parts and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in detail below in conjunction with the accompanying drawings.

[0022] The invention provides a method for aligning receiving channel data in a 1000BASE-T transceiver.

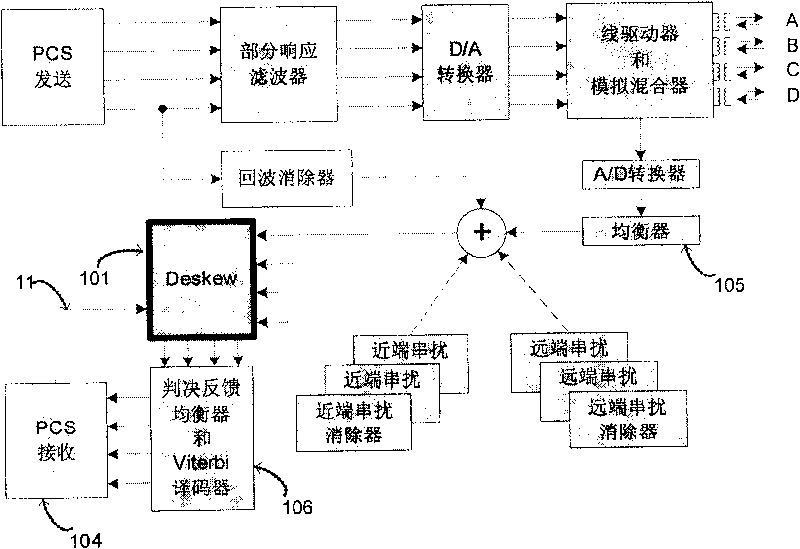

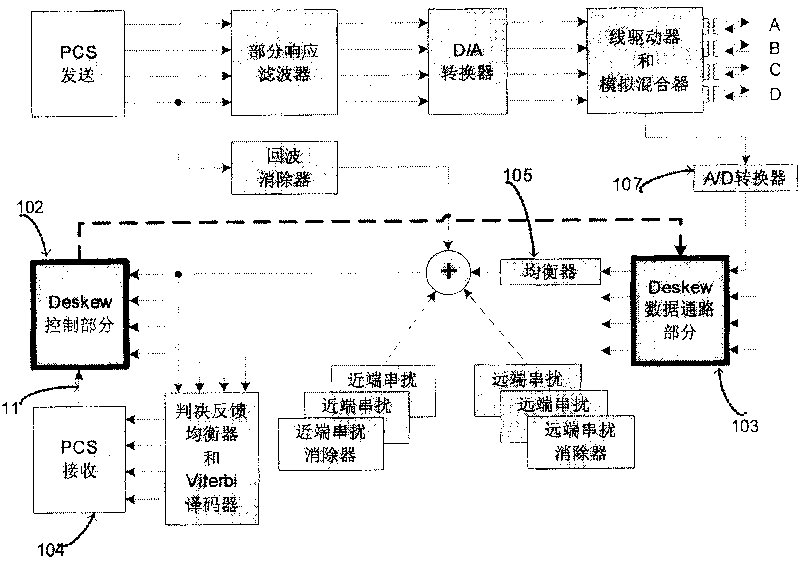

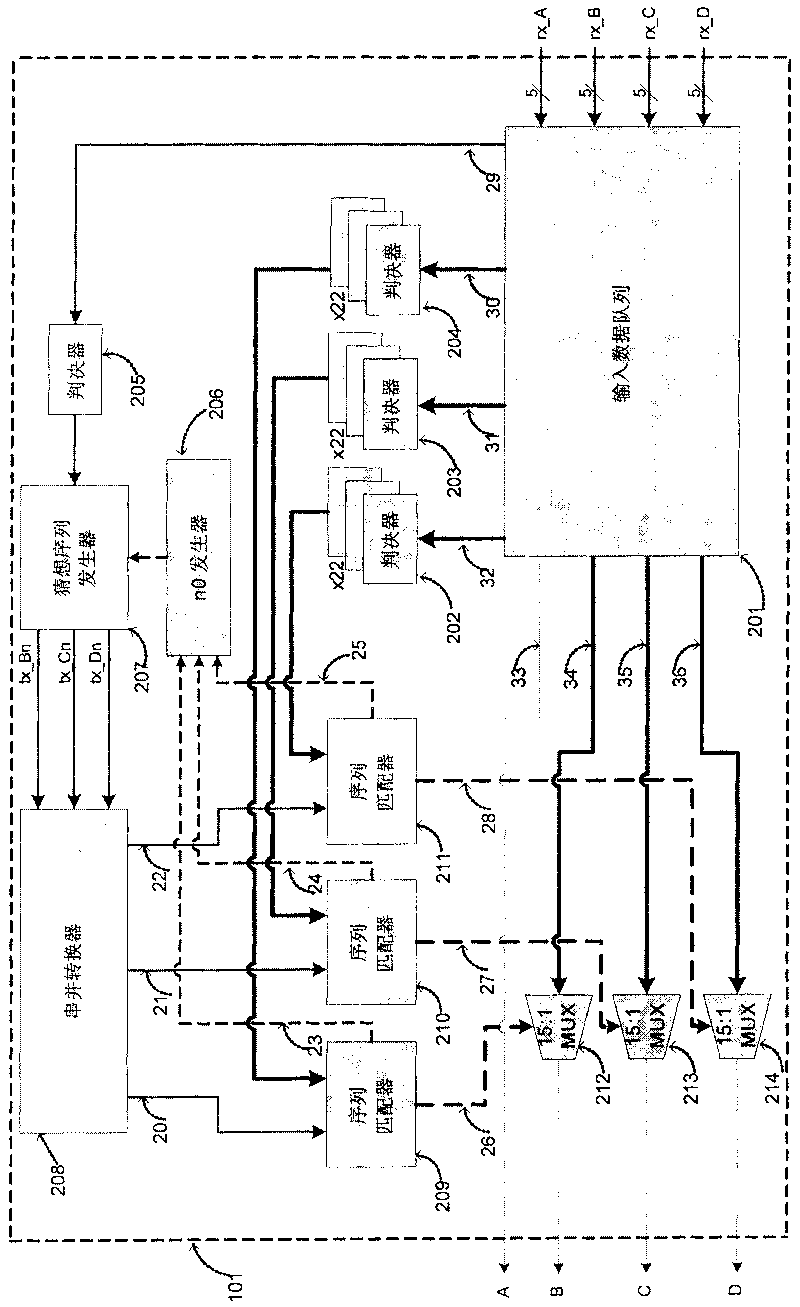

[0023] The present invention provides two schemes for data alignment. figure 1 The Deskew module 101 in belongs to the first kind of scheme, and it is composed of input data queue 201, decider 202, 203, 204, 205, n0 generator 206, conjecture sequence generator 207, serial-to-parallel converter 208, sequence matcher 209, 210, 211 and output multiplexers 212, 213, 214, and its structural block diagram is as follows image 3 shown.

[0024] image 3The middle input data queue (FIFO) 201 is made up of 405 D flip-flops, and its structure is as follows Figure 5 shown. These 405 D flip-flops form 4 FIFOs with a word width of 5, which are used as data buffers for the four channels of A, B, C and D respectively. The FIFO used for channel A has a depth of 15, and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com