Memory test circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011]Several embodiments are provided in following descriptions to explain the concept of the present invention. Each component in following descriptions can be implemented by hardware (e.g. a device or a circuit) or hardware with software (e.g. a program installed to a processor). It will be understood that, although the terms first, second, third, etc. may be used herein to describe various elements, these elements should not be limited by these terms. These terms may be used to distinguish one element from another. For example, a first element may be termed a second element and a second element may be termed a first element without departing from the scope of the present invention.

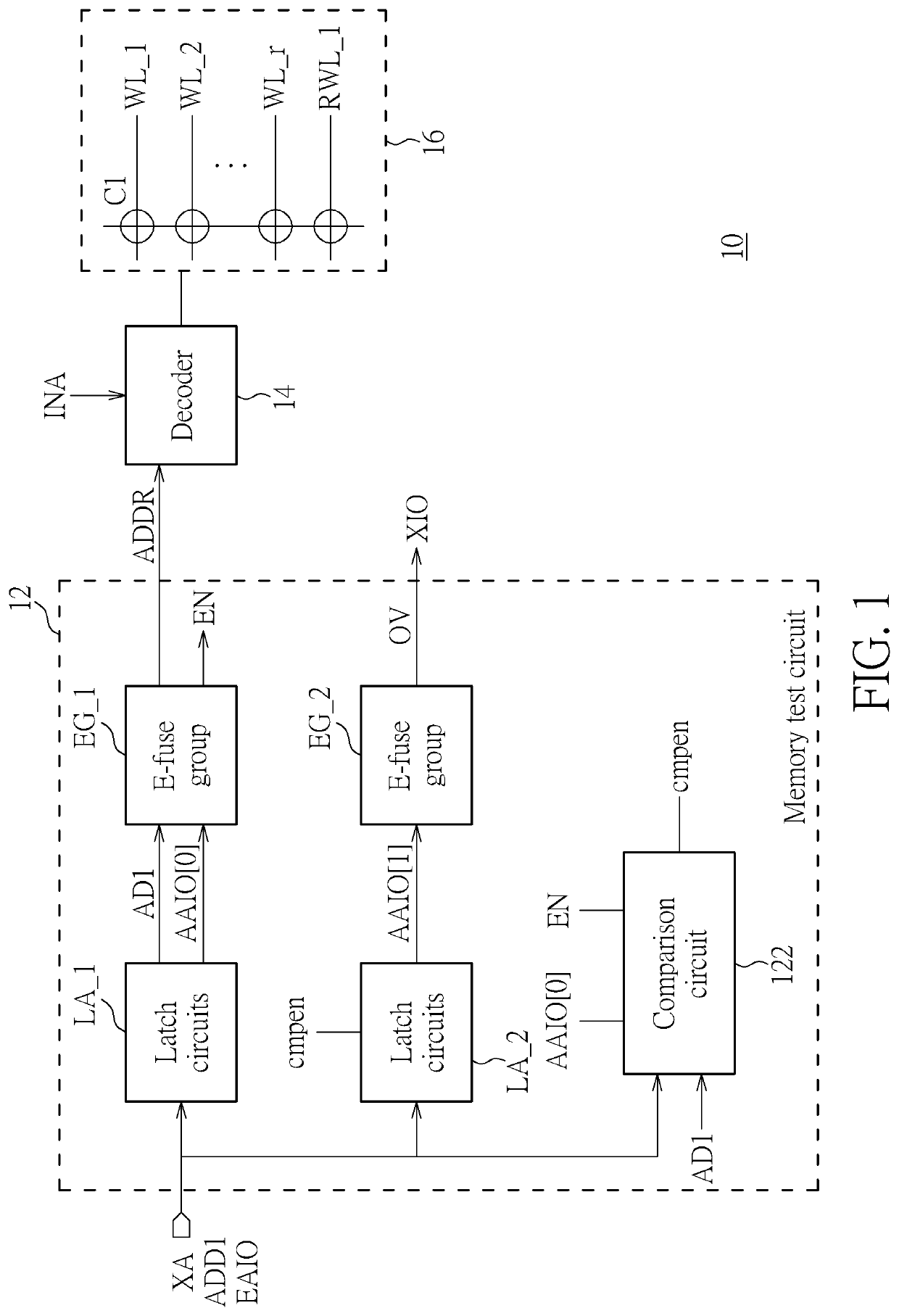

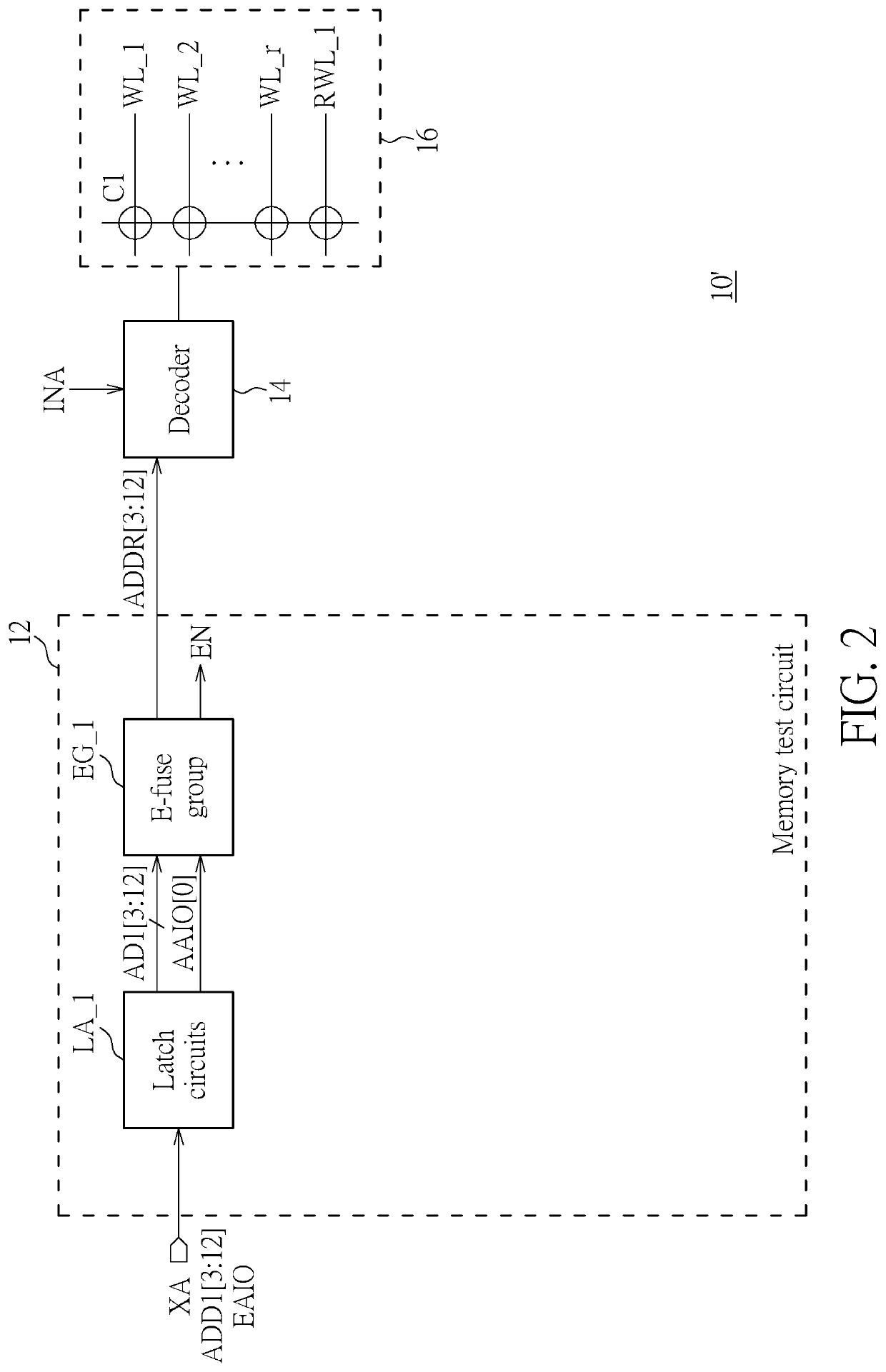

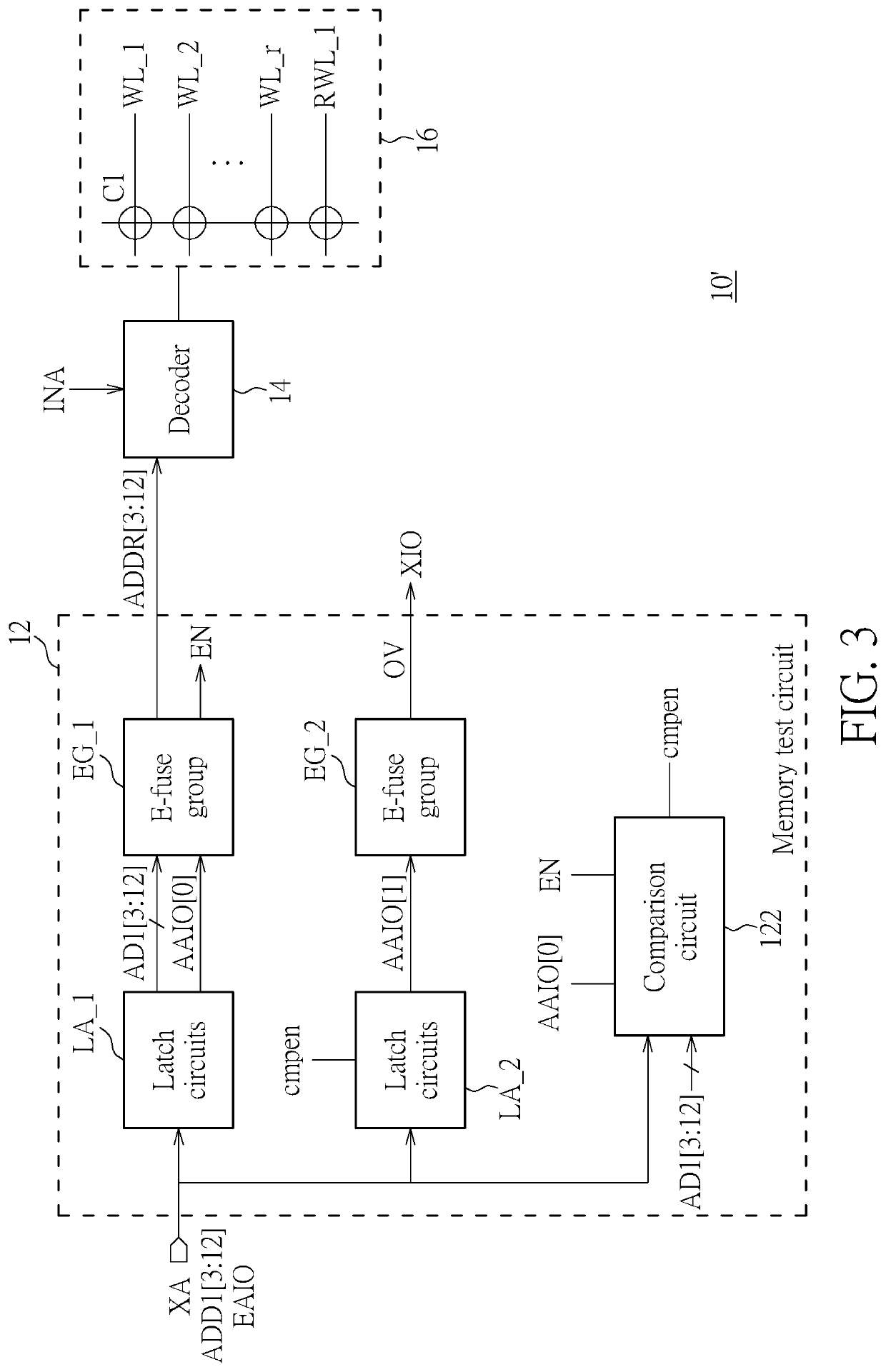

[0012]FIG. 1 is a block diagram illustrating a memory test circuit according to one embodiment of the present invention. The detailed operations will be illustrated below. Moreover, the memory test circuit described in the following embodiments is used in the FT mode, but the memory test circuit provid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More